One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

### **Register Map Reference Manual for the AD9546**

#### INTRODUCTION

This reference manual is supplemental to the AD9546 data sheet and contains the complete register map of the AD9546 with detailed bit descriptions. This reference manual has two main sections. The Register Address Map section includes Table 2, which provides a general overview of the entire register map and shows register address groups relating to the various functional features of the AD9546. The Register Bit Details section contains details associated with an individual register or a group of registers having consecutive addresses (see Table 3 to Table 111).

Table 3 to Table 111 in the Register Bit Details section include a reset column. The reset column shows the default value of a register bit (or group of bits). The value appears as hexadecimal notation with a 0x prefix or decimal notation (decimal notation only applies for a single bit or for a group of up to three bits). The last three columns in Table 3 to Table 111 (R/W, IO Update, and Autoclear) indicate the following access attributes of a bit or group of bits:

- Read/write capability

- Input/output (IO) update dependence

- Autoclear functionality

Table 1 lists these bit access attributes. For the IO update attribute,  $f_s$  is the frequency at the output of the VCO of the system clock PLL (~2.33 GHz), and the significance of serial port clock vs. core clock is how the device transfers data to the affected register. Registers or bits with access designated as serial port clock update via the serial port clock (SCLK or SCL) in conjunction with the assertion of an IO update. Thus, the register and bit contents update virtually coincident with the serial clock edge that makes Register 0x000F, Bit 0 = 1. Registers and bits with access designated as core clock update via the core clock ( $f_s/96$ ). As such, unless the system PLL is locked, these registers/bits do not update. Thus, for an IO update asserted while the system clock PLL is unlocked, data read from (or written to) registers or bits with IO update = core clock access may not be valid.

| Attribute         | Description                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------------------------------|

| Read/Write        |                                                                                                             |

| R                 | Read only                                                                                                   |

| W                 | Write only                                                                                                  |

| R/W               | Both read and write                                                                                         |

| IO Update         |                                                                                                             |

| Live              | IO update not required                                                                                      |

| Serial Port Clock | IO update qualified by the serial port clock                                                                |

| Core Clock        | IO update qualified by the core clock (f <sub>s</sub> /96) and requires that the system clock PLL be locked |

| Autoclear         |                                                                                                             |

| No                | Not autoclearing                                                                                            |

| Yes               | Autoclearing                                                                                                |

#### Table 1. Bit Access Attributes

### TABLE OF CONTENTS

| Introduction 1                                                                     |

|------------------------------------------------------------------------------------|

| Revision History 4                                                                 |

| Clock Output Nomenclature 5                                                        |

| Register Address Map 6                                                             |

| Register Bit Details                                                               |

| Serial Port—Register 0x0000 to Register 0x002311                                   |

| Mx Pin Mode—Register 0x0100 to Register 0x010113                                   |

| Mx Pin Status or Control Select—Register 0x0102 to Register<br>0x0108              |

| Serial Port and Mx pin Output Drive Current—Register<br>0x010921                   |

| Watchdog Timer—Register 0x010A to Register 0x010B 22                               |

| IRQ Enable—Register 0x010C to Register 0x011F22                                    |

| M0 Pin Function—Register 0x018234                                                  |

| M1 to CSB/M6 Pin Functions—Register 0x0183 to Register<br>0x0188                   |

| System Clock PLL—Register 0x0200 to Register 0x0209 41                             |

| System Clock Compensation—Register 0x0280 to Register<br>0x029C                    |

| Reference Input Configuration—Register 0x0300 to Register<br>0x030F                |

| Reference Input Parameters: REFA—Register 0x0400 to<br>Register 0x041458           |

| Reference Input Parameters: REFAA—Register 0x0420 to<br>Register 0x043460          |

| Reference Input Parameters: REFB—Register 0x0440 to<br>Register 0x045462           |

| Reference Input Parameters: REFBB—Register 0x0460 to<br>Register 0x047464          |

| Reference Input Parameters: Auxiliary REF0—Register<br>0x0480 to Register 0x049466 |

| Reference Input Parameters: Auxiliary REF1—Register<br>0x04A0 to Register 0x04B469 |

| Reference Input Parameters: Auxiliary REF2—Register<br>0x04C0 to Register 0x04D472 |

| Reference Input Parameters: Auxiliary REF3—Register<br>0x04E0 to Register 0x04F475 |

| Source Profile: REFA—Register 0x0800 to Register 0x0811 78                         |

| Source Profile: REFAA—Register 0x0820 to Register 0x0831<br>                       |

| Source Profile: REFB—Register 0x0840 to Register 0x0851 84                         |

| Source Profile: REFBB—Register 0x0860 to Register 0x0871<br>                       |

| Source Profile: Auxiliary NCO 0—Register 0x0880 to<br>Register 0x0891                    |

|------------------------------------------------------------------------------------------|

| Source Profile: Auxiliary NCO 1—Register 0x08A0 to<br>Register 0x08B1                    |

| Source Profile: DPLL0—Register 0x08C0 to Register 0x08D1<br>                             |

| Source Profile: DPLL1—Register 0x08E0 to Register 0x08F1<br>                             |

| Source Profile: IUTS 0—Register 0x0900 to Register 0x0911                                |

| Source Profile: IUTS 1—Register 0x0920 to Register 0x0931                                |

| 105<br>Source Profile: Auxiliary REF0—Register 0x0940 to Register<br>0x0951              |

| Source Profile: Auxiliary REF1—Register 0x0960 to Register 0x0971111                     |

| Source Profile: Auxiliary REF2—Register 0x0980 to Register 0x0991114                     |

| Source Profile: Auxiliary REF3—Register 0x09A0 to Register 0x09B1                        |

| DPLL Loop Filter 0 (LF0) Coefficients—Register 0x0C00 to<br>Register 0x0C0B              |

| DPLL Loop Filter 1 (LF1) Coefficients—Register 0x0C0C to<br>Register 0x0C17121           |

| Common Clock DPLL Lock Detector Parameters—Register<br>0x0D00 to Register 0x0D05         |

| Common Clock DPLL/Synchronizer Source 0 (CCR0)—<br>Register 0x0D10 to Register 0x0D1D123 |

| Common Clock DPLL/Synchronizer Source 1 (CCR1)—<br>Register 0x0D20 to Register 0x0D2D125 |

| Common Clock Synchronizer Parameters—Register 0x0D30<br>to Register 0x0D3C               |

| Digitized Clocking Status—Register 0x0D40 129                                            |

| User Time Stamper Control: UTS 0—Register 0x0E00 to<br>Register 0x0E04                   |

| User Time Stamper Control: UTS 1—Register 0x0E05 to<br>Register 0x0E09                   |

| User Time Stamper Control: UTS 2—Register 0x0E0A to<br>Register 0x0E0E134                |

| User Time Stamper Control: UTS 3—Register 0x0E0F to<br>Register 0x0E13                   |

| User Time Stamper Control: UTS 4—Register 0x0E14 to<br>Register 0x0E18                   |

| User Time Stamper Control: UTS 5—Register 0x0E19 to<br>Register 0x0E1D                   |

| -                                                                                        |

| User Time Stamper Control: UTS 6—Register 0x0E1E to<br>Register 0x0E22             |

|------------------------------------------------------------------------------------|

| User Time Stamper Control: UTS 7—Register 0x0E23 to<br>Register 0x0E27             |

| User Time Stamper Control: UTS 8—Register 0x0E28 to<br>Register 0x0E2C             |

| User Time Stamper FIFO—Register 0x0E2D to Register<br>0x0E3A                       |

| Inverse User Time Stamper Parameters: IUTS 0—Register<br>0x0F00 to Register 0x0F03 |

| Inverse User Time Stamper Parameters: IUTS 1—Register<br>0x0F04 to Register 0x0F07 |

| Inverse User Time Stamper: IUTS Control—Register 0x0F08<br>to Register 0x0F15152   |

| DPLL0 Parameters-Register 0x1000 to Register 0x102A. 153                           |

| APLL0 Parameters—Register 0x1080 to Register 0x1083 160                            |

| Distribution Control: PLL Channel 0—Register 0x10C0 to<br>Register 0x10DC          |

| Distribution Parameters: Q0A—Register 0x1100 to Register 0x1108                    |

| Distribution Parameters: Q0AA—Register 0x1109 to Register 0x1111                   |

| Distribution Parameters: Q0B—Register 0x1112 to Register 0x111A                    |

| Distribution Parameters: Q0BB—Register 0x111B to Register 0x1123                   |

| Distribution Parameters: Q0C—Register 0x1124 to Register 0x112C                    |

| Distribution Parameters: Q0CC—Register 0x112D to<br>Register 0x1135                |

| Translation Profile 0.0 Parameters—Register 0x1200 to<br>Register 0x1217           |

| Translation Profile 0.1 Parameters—Register 0x1220 to<br>Register 0x1237           |

| Translation Profile 0.2 Parameters—Register 0x1240 to<br>Register 0x1257           |

| Translation Profile 0.3 Parameters—Register 0x1260 to<br>Register 0x1277           |

| Translation Profile 0.4 Parameters—Register 0x1280 to<br>Register 0x1297           |

| Translation Profile 0.5 Parameters—Register 0x12A0 to<br>Register 0x12b7           |

| DPLL1 Parameters—Register 0x1400 to Register 0x142A. 217                           |

| APLL1 Parameters—Register 0x1480 to Register 0x1483 224                            |

| Distribution Control: PLL Channel 1—Register 0x14C0 to<br>Register 0x14DC          |

| Distribution Parameters: Q1A—Register 0x1500 to Register 0x1508                            |

|--------------------------------------------------------------------------------------------|

| Distribution Parameters: Q1AA—Register 0x1509 to Register<br>0x1511                        |

| Distribution Parameters: Q1B—Register 0x1512 to Register 0x151A                            |

| Distribution Parameters: Q1BB—Register 0x151B to Register 0x1523                           |

| Translation Profile 1.0 Parameters—Register 0x1600 to<br>Register 0x1617243                |

| Translation Profile 1.1 Parameters—Register 0x1620 to<br>Register 0x1637                   |

| Translation Profile 1.2 Parameters—Register 0x1640 to<br>Register 0x1657                   |

| Translation Profile 1.3 Parameters—Register 0x1660 to<br>Register 0x1677                   |

| Translation Profile 1.4 Parameters—Register 0x1680 to<br>Register 0x1697                   |

| Translation Profile 1.5 Parameters—Register 0x16A0 to<br>Register 0x16B7268                |

| Operational Control: General—Register 0x2000 to Register 0x2004                            |

| IRQ Clear—Register 0x2005 to Register 0x2019277                                            |

| Operational Control: PLL Channel 0—Register 0x2100 to<br>Register 0x2107                   |

| Operational Control: PLL Channel 1—Register 0x2200 to<br>Register 0x2207                   |

| Auxiliary NCO 0 Parameters—Register 0x2800 to Register<br>0x281E                           |

| Auxiliary NCO 1 Parameters—Register 0x2840 to Register<br>0x285E                           |

| Temperature Sensor Parameters—Register 0x2900 to Register 0x2906                           |

| User Time Stamp Processor (UTSP) Control Parameters—<br>Register 0x2A12 to Register 0x2A13 |

| Skew Measurement Processor Control Parameters—Register<br>0x2A14 to Register 0x2A16        |

| Analog Loopback Control Parameters—Register 0x2D02310                                      |

| EEPROM Control Parameters—Register 0x2E00 to Register<br>0x2E03                            |

| EEPROM Upload Instruction Space—Register 0x2E10 to<br>Register 0x2E1E                      |

| EEPROM Status—Register 0x3000                                                              |

| PLL Status—Register 0x3001312                                                              |

| Miscellaneous Status—Register 0x3002                                                       |

| Temperature Sensor Output—Register 0x3003 to Register      |

|------------------------------------------------------------|

| 0x3004                                                     |

| REFx Status—Register 0x3005 to Register 0x3008             |

| DPLL Profile Status—Register 0x3009 to Register 0x300A 316 |

| IRQ Status—Register 0x300B to Register 0x301E              |

| Auxiliary REFx Status—Register 0x301F to Register 0x3022   |

|                                                            |

| IUTS Status—Register 0x3023                                |

| PLL Channel 0 Status—Register 0x3100 to Register 0x310E    |

|                                                            |

| PLL Channel 1 Status—Register 0x3200 to Register 0x320E    |

|                                                            |

### **REVISION HISTORY**

5/2021—Revision 0: Initial Version

| Auxiliary NCO 0 Time Scale Output—Register 0x3A00 to<br>Register 0x3A09       |

|-------------------------------------------------------------------------------|

| Auxiliary NCO 1 Time Scale Output—Register 0x3A0A to<br>Register 0x3A13       |

| User Time Stamp Processor Output: UTSP0—Register<br>0x3A14 to Register 0x3A1F |

| User Time Stamp Processor Output: UTSP1—Register<br>0x3A20 to Register 0x3A2B |

| Skew Measurement Processor Output—Register 0x3A2C to<br>Register 0x3A3B       |

### **CLOCK OUTPUT NOMENCLATURE**

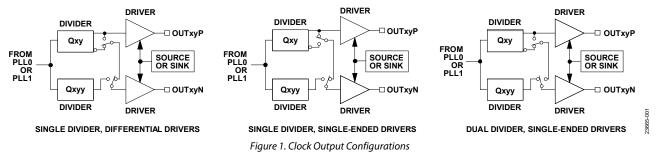

This reference manual makes use of specific nomenclature regarding the clock outputs of the AD9546, which constitute five 2-pin pairs. Each output pin has a dedicated output driver and the drivers can receive clock signals from one or two distribution dividers, depending on the output configuration (see Figure 1). The output pin pairs can be configured as follows:

- One differential output associated with a single distribution divider (single divider, differential drivers)

- Two single-ended outputs associated with a single distribution divider (single divider, single-ended drivers)

- Two single-ended outputs associated with independent distribution dividers (dual divider, single-ended drivers)

The clock output pin names follow the naming convention of OUTxyP and OUTxyN, where

- x is 0 or 1 (corresponding to PLL Channel 0 or PLL Channel 1)

- y is the output number (0, 1, or 2 for PLL Channel 0; and 0 or 1 for PLL Channel 1)

- P denotes the positive (normal) pin of the output pin pair

- N denotes the negative (complementary) pin of the output pin pair

For the single-divider configurations, the distribution dividers follow the naming convention of Qxy, with x and y being the same as for the pin names, where x is 0 or 1 and y is the output number. The dual-divider configuration requires two distribution dividers, one for each pin. In this case, the OUTxyP pin associates with Distribution Divider Qxy, whereas the OUTxyN pin associates with Distribution Divider Qxyy. For example, given the Output 0A pin pair (OUT0A) with dual divider configuration, Pin OUT0AP associates with Distribution Divider Q0A and Pin OUT0AN associates with Distribution Divider Q0AA.

### **REGISTER ADDRESS MAP**

### Table 2. Register Map

| Register Description                                      |

|-----------------------------------------------------------|

| See Table 3                                               |

| Serial port configuration                                 |

| Not applicable                                            |

| Device ID                                                 |

| Not applicable                                            |

| SPI version                                               |

| Vendor ID                                                 |

| Not applicable                                            |

| Address looping and IO update                             |

| Address loop length                                       |

| Scratch pad                                               |

| Not applicable                                            |

|                                                           |

| Mx pin mode (see Table 4)                                 |

| Mx pin status or control select (see Table 5)             |

| Serial port and Mx pin output drive current (see Table 6) |

|                                                           |

| Watchdog timer (see Table 7)                              |

|                                                           |

| IRQ enable (see Table 8)                                  |

| Not applicable                                            |

|                                                           |

| M0 pin function (see Table 9)                             |

| M1 pin function (see Table 10)                            |

| M2 pin function (see Table 10)                            |

| M3 pin function (see Table 10)                            |

| M4 pin function (see Table 10)                            |

| SDO/M5 pin function (see Table 10)                        |

| CSB/M6 pin function (see Table 10)                        |

| Not applicable                                            |

|                                                           |

| System clock PLL (see Table 11)                           |

| Not applicable                                            |

|                                                           |

| System clock compensation (see Table 12)                  |

| Not applicable                                            |

|                                                           |

| Reference input configuration (see Table 13)              |

| Not applicable                                            |

| Reference input parameters: REFA (see Table 14)           |

| Not applicable                                            |

| Reference input parameters: REFAA (see Table 15)          |

| Not applicable                                            |

| Reference input parameters: REFB (see Table 16)           |

| Not applicable                                            |

| Reference input parameters: REFBB (see Table 17)          |

| Not applicable                                            |

|                                                           |

| Reference input parameters: Auxiliary REF0 (see Table 18) |

|                                                           |

|                                                           |

Rev. 0 | Page 6 of 337

| Register Address                           | Register Description                                                              |

|--------------------------------------------|-----------------------------------------------------------------------------------|

| Register 0x04B5 to Register 0x04BF         | Not applicable                                                                    |

| Register 0x04C0 to Register 0x04D4         | Reference input parameters: Auxiliary REF2 (see Table 20)                         |

| Register 0x04D5 to Register 0x04DF         | Not applicable                                                                    |

| Register 0x04E0 to Register 0x04F4         | Reference input parameters: Auxiliary REF3 (see Table 21)                         |

| Register 0x04F5 to Register 0x07FF         | Not applicable                                                                    |

| Source Profiles                            |                                                                                   |

| Register 0x0800 to Register 0x0811         | Source profile: REFA (see Table 22)                                               |

| Register 0x0812 to Register 0x081F         | Not applicable                                                                    |

| Register 0x0820 to Register 0x0831         | Source profile: REFAA (see Table 23)                                              |

| Register 0x0832 to Register 0x083F         | Not applicable                                                                    |

| Register 0x0840 to Register 0x0851         | Source profile: REFB (see Table 24)                                               |

| Register 0x0852 to Register 0x085F         | Not applicable                                                                    |

| Register 0x0860 to Register 0x0871         | Source profile: REFBB (see Table 25)                                              |

| Register 0x0872 to Register 0x087F         | Not applicable                                                                    |

| Register 0x0880 to Register 0x0891         | Source profile: Auxiliary NCO 0 (see Table 26)                                    |

| Register 0x0892 to Register 0x089F         | Not applicable                                                                    |

| Register 0x08A0 to Register 0x08B1         | Source profile: Auxiliary NCO 1 (see Table 27)                                    |

| Register 0x08B2 to Register 0x08BF         | Not applicable                                                                    |

| Register 0x08C0 to Register 0x08D1         | Source profile: DPLL0 (see Table 28)                                              |

| Register 0x08D2 to Register 0x08DF         | Not applicable                                                                    |

| Register 0x08E0 to Register 0x08F1         | Source profile: DPLL1 (see Table 29)                                              |

| Register 0x08F2 to Register 0x08FF         | Not applicable                                                                    |

| Register 0x0900 to Register 0x0911         | Source profile: IUTS 0 (see Table 30)                                             |

| Register 0x0912 to Register 0x091F         | Not applicable                                                                    |

| Register 0x0920 to Register 0x0931         | Source profile: IUTS 1 (see Table 31)                                             |

| Register 0x0932 to Register 0x093F         | Not applicable                                                                    |

| Register 0x0940 to Register 0x0951         | Source profile: Auxiliary REF0 (see Table 32)                                     |

| Register 0x0952 to Register 0x095F         | Not applicable                                                                    |

| Register 0x0960 to Register 0x0971         | Source profile: Auxiliary REF1 (see Table 33)                                     |

| Register 0x0972 to Register 0x097F         | Not applicable                                                                    |

| Register 0x0980 to Register 0x0991         | Source profile: Auxiliary REF2 (see Table 34)                                     |

| Register 0x0992 to Register 0x099F         | Not applicable                                                                    |

| Register 0x09A0 to Register 0x09B1         | Source profile: Auxiliary REF3 (see Table 35)                                     |

| Register 0x09B2 to Register 0x0BBF         | Not applicable                                                                    |

| DPLL Loop Filter Coefficients              |                                                                                   |

| Register 0x0C00 to Register 0x0C0B         | Loop Filter 0 (LF0) Coefficient (see Table 36)                                    |

| Register 0x0C0C to Register 0x0C17         | Loop Filter 1 (LF1) Coefficient (see Table 37)                                    |

| Register 0x0C18 to Register 0x0CFF         | Not applicable                                                                    |

| Common Clock DPLL Lock Detector Parameters |                                                                                   |

| Register 0x0D00 to Register 0x0D05         | Common clock DPLL lock detector parameters (see Table 38)                         |

| Register 0x0D06 to Register 0x0D0F         | Not applicable                                                                    |

| Common Clock DPLL/Synchronizer             |                                                                                   |

| Register 0x0D10 to Register 0x0D1D         | Common clock DPLL/Synchronizer Source 0, primary reference, CCR0 (see Table 39)   |

| Register 0x0D1E to Register 0x0D1F         | Not applicable                                                                    |

| Register 0x0D20 to Register 0x0D2D         | Common clock DPLL/Synchronizer Source 1, secondary reference, CCR1 (see Table 40) |

| Register 0x0D2E to Register 0x0D2F         | Not applicable                                                                    |

| Common Clock Synchronizer (CCS) Parameters |                                                                                   |

| Register 0x0D30 to Register 0x0D3C         | Common clock synchronizer parameters (see Table 41)                               |

| Register 0x0D3D to Register 0x0D3F         | Not applicable                                                                    |

|                                            |                                                                                   |

| Register Address                                   | Register Description                                           |

|----------------------------------------------------|----------------------------------------------------------------|

| —————                                              |                                                                |

| Digitized Clocking Status                          | Digitized cleaking status (see Table 42)                       |

| Register 0x0D40                                    | Digitized clocking status (see Table 42)                       |

| User Time Stamper Control                          |                                                                |

| Register 0x0E00 to Register 0x0E04                 | User Time Stamper 0 (UTS 0) control (see Table 43)             |

| Register 0x0E05 to Register 0x0E09                 | User Time Stamper 1 (UTS 1) control (see Table 44)             |

| Register 0x0E0A to Register 0x0E0E                 | User Time Stamper 2 (UTS 2) control (see Table 45)             |

| Register 0x0E0F to Register 0x0E13                 | User Time Stamper 3 (UTS 3) control (see Table 46)             |

| Register 0x0E14 to Register 0x0E18                 | User Time Stamper 4 (UTS 4) control (see Table 47)             |

| Register 0x0E19 to Register 0x0E1D                 | User Time Stamper 5 (UTS 5) control (see Table 48)             |

| Register 0x0E1E to Register 0x0E22                 | User Time Stamper 6 (UTS 6) control (see Table 49)             |

| Register 0x0E23 to Register 0x0E27                 | User Time Stamper 7 (UTS 7) control (see Table 50)             |

| Register 0x0E28 to Register 0x0E2C                 | User Time Stamper 8 (UTS 8) control (see Table 51)             |

| Register 0x0E2D to Register 0x0E3A                 | User time stamper FIFO (see Table 52)                          |

| Register 0x0E3B to Register 0x0EFF                 | Not applicable                                                 |

| Inverse User Time Stamper (IUTS) Parameters        |                                                                |

| Register 0x0F00 to Register 0x0F03                 | Inverse User Time Stamper 0 (IUTS 0) parameters (see Table 53) |

| Register 0x0F04 to Register 0x0F07                 | Inverse user time stamper 1 (IUTS 1) parameters (see Table 54) |

| Register 0x0F08 to Register 0x0F15                 | Inverse user time stamper: IUTS control (see Table 55)         |

| Register 0x0F16 to Register 0x0FFF                 | Not applicable                                                 |

| Digital Phase-Locked Loop 0 (DPLL0) Parameters     |                                                                |

| Register 0x1000 to Register 0x102A                 | DPLL0 parameters (see Table 56)                                |

| Register 0x102B to Register 0x107F                 | Not applicable                                                 |

| Analog Phase-Locked Loop 0 (APLL0) Parameters      |                                                                |

| Register 0x1080 to Register 0x1083                 | APLL0 parameters (see Table 57)                                |

| Register 0x1084 to Register 0x10BF                 | Not applicable                                                 |

| Distribution Control and Parameters                |                                                                |

| Register 0x10C0 to Register 0x10DC                 | Distribution control: PLL Channel 0 (see Table 58)             |

| Register 0x10DD to Register 0x10FF                 | Not applicable                                                 |

| Register 0x1100 to Register 0x1108                 | Distribution parameters: Q0A (see Table 59)                    |

| Register 0x1109 to Register 0x1111                 | Distribution parameters: Q0AA (see Table 60)                   |

| Register 0x1112 to Register 0x111A                 | Distribution parameters: Q0B (see Table 61)                    |

| Register 0x111B to Register 0x1123                 | Distribution parameters: Q0BB (see Table 62)                   |

| Register 0x1124 to Register 0x112C                 | Distribution parameters: Q0C (see Table 63)                    |

| Register 0x112D to Register 0x1135                 | Distribution parameters: Q0CC (see Table 64)                   |

| Register 0x1136 to Register 0x11FF                 | Not applicable                                                 |

| Translation Profile 0.0 to Translation Profile 0.5 |                                                                |

| Register 0x1200 to Register 0x1217                 | Translation Profile 0.0 (see Table 65)                         |

| Register 0x1218 to Register 0x121F                 | Not applicable                                                 |

| Register 0x1220 to Register 0x1237                 | Translation Profile 0.1 (see Table 66)                         |

| Register 0x1238 to Register 0x123F                 | Not applicable                                                 |

| Register 0x1240 to Register 0x1257                 | Translation Profile 0.2 (see Table 67)                         |

| Register 0x1258 to Register 0x125F                 | Not applicable                                                 |

| Register 0x1260 to Register 0x1277                 | Translation Profile 0.3 (see Table 68)                         |

| Register 0x1278 to Register 0x127F                 | Not applicable                                                 |

| Register 0x1280 to Register 0x1297                 | Translation Profile 0.4 (see Table 69)                         |

| Register 0x1298 to Register 0x129F                 | Not applicable                                                 |

| Register 0x12A0 to Register 0x12B7                 | Translation Profile 0.5 (see Table 70)                         |

| Register 0x12B8 to Register 0x13FF                 | Not applicable                                                 |

| Digital Phase-Locked Loop 1 (DPLL1) Parameters     |                                                                |

| Register 0x1400 to Register 0x142A                 | DPLL1 parameters (see Table 71)                                |

| Register 0x142B to Register 0x147F                 | Not applicable                                                 |

| Register Address                                   | Register Description                                    |

|----------------------------------------------------|---------------------------------------------------------|

| Analog Phase-Locked Loop 1 (APLL1) Parameters      |                                                         |

| Register 0x1480 to Register 0x1483                 | APLL1 parameters (see Table 72)                         |

| Register 0x1484 to Register 0x14BF                 | Not applicable                                          |

| Distribution Control and Parameters                |                                                         |

| Register 0x14C0 to Register 0x14DC                 | Distribution control: PLL Channel 1 (see Table 73)      |

| Register 0x14DD to Register 0x14FF                 | Not applicable                                          |

| Register 0x1500 to Register 0x1508                 | Distribution parameters: Q1A (see Table 74)             |

| Register 0x1509 to Register 0x1511                 | Distribution parameters: Q1AA (see Table 75)            |

| Register 0x1512 to Register 0x151A                 | Distribution parameters: Q1B (see Table 76)             |

| Register 0x151B to Register 0x1523                 | Distribution parameters: Q1BB (see Table 77)            |

| Register 0x1524 to Register 0x15FF                 | Not applicable                                          |

| Translation Profile 1.0 to Translation Profile 1.5 |                                                         |

| Register 0x1600 to Register 0x1617                 | Translation Profile 1.0 (see Table 78)                  |

| Register 0x1618 to Register 0x161F                 | Not applicable                                          |

| Register 0x1620 to Register 0x1637                 | Translation Profile 1.1 (see Table 79)                  |

| Register 0x1638 to Register 0x163F                 | Not applicable                                          |

| Register 0x1640 to Register 0x1657                 | Translation Profile 1.2 (see Table 80)                  |

| Register 0x1658 to Register 0x165F                 | Not applicable                                          |

| Register 0x1660 to Register 0x1677                 | Translation Profile 1.3 (see Table 81)                  |

| Register 0x1678 to Register 0x167F                 | Not applicable                                          |

| Register 0x1680 to Register 0x1697                 | Translation Profile 1.4 (see Table 82)                  |

| Register 0x1698 to Register 0x169F                 | Not applicable                                          |

| Register 0x16A0 to Register 0x16B7                 | Translation Profile 1.5 (see Table 83)                  |

| Register 0x16B8 to Register 0x1FFF                 | Not applicable                                          |

| Operational Control: General                       |                                                         |

| Register 0x2000 to Register 0x2004                 | Operational control: general (see Table 84)             |

| IRQ Clear                                          | Exception: Register 0x2005, Bit 7, reset watchdog timer |

| Register 0x2005 to Register 0x2019                 | IRQ clear (see Table 85)                                |

| Register 0x201A to Register 0x20FF                 | Not applicable                                          |

| Operational Control                                |                                                         |

| Register 0x2100 to Register 0x2107                 | Operational control: PLL Channel 0 (see Table 86)       |

| Register 0x2108 to Register 0x21FF                 | Not applicable                                          |

| Register 0x2200 to Register 0x2207                 | Operational control: PLL Channel 1 (see Table 87)       |

| Register 0x2208 to Register 0x27FF                 | Not applicable                                          |

| Auxiliary NCO x Parameters                         |                                                         |

| Register 0x2800 to Register 0x281E                 | Auxiliary NCO 0 parameters (see Table 88)               |

| Register 0x281F to Register 0x283F                 | Not applicable                                          |

| Register 0x2840 to Register 0x285E                 | Auxiliary NCO 1 parameters (see Table 89)               |

| Register 0x285F to Register 0x28FF                 | Not applicable                                          |

| Temperature Sensor                                 |                                                         |

| Register 0x2900 to Register 0x2906                 | Temperature sensor (see Table 90)                       |

| Register 0x2907 to Register 0x2A11                 | Not applicable                                          |

| User Time Stamp Processor (UTSP) Controls          |                                                         |

| Register 0x2A12 to Register 0x2A13                 | UTSP controls (see Table 91)                            |

| Skew Measurement Processor Controls                |                                                         |

| Register 0x2A14 to Register 0x2A16                 | Skew measurement processor controls (see Table 92)      |

| Register 0x2A17 to Register 0x2D01                 | Not applicable                                          |

| Analog Loopback                                    |                                                         |

| Register 0x2D02                                    | Analog loopback (see Table 93)                          |

| Register 0x2D03 to Register 0x2DFF                 | Not applicable                                          |

| Register Address                   | Register Description                                        |  |

|------------------------------------|-------------------------------------------------------------|--|

| EEPROM Controls                    |                                                             |  |

| Register 0x2E00 to Register 0x2E03 | EEPROM controls (see Table 94)                              |  |

| Register 0x2E04 to Register 0x2E0F | Not applicable                                              |  |

| Register 0x2E10 to Register 0x2E1E | EEPROM upload instruction space (see Table 95)              |  |

| Register 0x2E1F to Register 0x2FFF | Not applicable                                              |  |

| Status                             |                                                             |  |

| Register 0x3000                    | EEPROM status (see Table 96)                                |  |

| Register 0x3001                    | PLL (system clock PLL, PLL0 and PLL1) status (see Table 97) |  |

| Register 0x3002                    | Miscellaneous status (see Table 98)                         |  |

| Register 0x3003                    | Temperature sensor output (see Table 99)                    |  |

| Register 0x3005 to Register 0x3008 | REFx status (see Table 100)                                 |  |

| Register 0x3009 to Register 0x300A | DPLL profile status (see Table 101)                         |  |

| Register 0x300B to Register 0x301E | IRQ status (see Table 102)                                  |  |

| Register 0x301F to Register 0x3022 | Auxiliary REFx status (see Table 103)                       |  |

| Register 0x3023                    | IUTS status (see Table 104)                                 |  |

| Register 0x3024 to Register 0x30FF | Not applicable                                              |  |

| Register 0x3100 to Register 0x310E | PLL Channel 0 status (see Table 105)                        |  |

| Register 0x310F to Register 0x31FF | Not applicable                                              |  |

| Register 0x3200 to Register 0x320E | PLL Channel 1 status (see Table 106)                        |  |

| Register 0x320F to Register 0x39FF | Not applicable                                              |  |

| Auxiliary NCO x Time Scale         |                                                             |  |

| Register 0x3A00 to Register 0x3A09 | Auxiliary NCO 0 time scale (see Table 107)                  |  |

| Register 0x3A0A to Register 0x3A13 | Auxiliary NCO 1 time scale (see Table 108)                  |  |

| Processor Outputs                  |                                                             |  |

| Register 0x3A14 to Register 0x3A1F | User time stamp processor output: UTSP0 (see Table 109)     |  |

| Register 0x3A20 to Register 0x3A2B | User time stamp processor output: UTSP1 (see Table 110)     |  |

| Register 0x3A2C to Register 0x3A3B | Skew measurement processor output (see Table 111)           |  |

| Register 0x3A3C to Register 0xFFFF | Not applicable                                              |  |

### **REGISTER BIT DETAILS**

### SERIAL PORT—REGISTER 0x0000 TO REGISTER 0x0023

Table 3. Serial Port Details

| Address | Bits  | Bit Name                        | Settings | Description                                                                                                                                                                                                                                                                                                                                                                      | Reset | R/W | IO<br>Update | Auto<br>clear |

|---------|-------|---------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|--------------|---------------|

| 0x0000  | 7     | Soft reset                      |          | Soft Reset. This bit must be set identical to Bit 0 (see Bit 0 for details).                                                                                                                                                                                                                                                                                                     | 0     | R/W | Live         | No            |

|         | 6     | LSB first (SPI only)            |          | SPI LSB First. This bit must be set identical to Bit 1 (see Bit 1 for details).                                                                                                                                                                                                                                                                                                  | 0     | R/W | Live         | No            |

|         | 5     | Address ascension (SPI only)    |          | SPI Address Ascension. This bit must be set identical to Bit 2 (see Bit 2 for details).                                                                                                                                                                                                                                                                                          | 0     | R/W | Live         | No            |

|         | 4     | SDO active (SPI only)           |          | Enable SPI 4-wire Mode. This bit must be set identical to Bit 3 (see Bit 3 for details).                                                                                                                                                                                                                                                                                         | 0     | R/W | Live         | No            |

|         | 3     | SDO active (SPI only)           |          | This bit selects whether the SPI SDO pin is an active<br>output pin (4-wire SPI mode) or tristate (3-wire SPI<br>mode). This bit has no effect in I <sup>2</sup> C mode.<br>SDO pin tristate (SDIO pin bidirectional), 3-wire SPI<br>mode.<br>SDO pin active output (SDIO pin input only), 4-wire<br>SPI mode.                                                                   | 0     | R/W | Live         | No            |

|         | 2     | Address ascension (SPI<br>only) | 0        | SPI Address Ascension. This bit controls the direction<br>(decrement or increment) that register addressing<br>occurs during multibyte transfers. This bit has no<br>effect in I <sup>2</sup> C mode.<br>Decrement.<br>Increment.                                                                                                                                                | 0     | R/W | Live         | No            |

|         | 1     | LSB first (SPI only)            | 1        | SPI LSB First. Bit order for SPI port. This bit has no effect in I <sup>2</sup> C mode.                                                                                                                                                                                                                                                                                          | 0     | R/W | Live         | No            |

|         |       |                                 | 0        | Most Significant Bit (MSB) First.<br>Least Significant Bit (LSB) First.                                                                                                                                                                                                                                                                                                          |       |     |              |               |

|         | 0     | Soft reset                      |          | Soft Reset. Logic 1 invokes a device reset. Also, if the Mx pins are configured for an automatic EEPROM download, an EEPROM download initiates.                                                                                                                                                                                                                                  | 0     | R/W | Live         | No            |

| )x0001  | [7:6] | Reserved                        |          | Reserved.                                                                                                                                                                                                                                                                                                                                                                        | 0x0   | R   | Live         | No            |

|         | 5     | Read buffer register            | 0        | Read Buffer Register. For buffered registers, this bit<br>controls whether the value read from the serial port<br>is buffered data or active data (active being data<br>transferred to active registers via assertion of an IO<br>update).<br>Reads the register values that are currently active<br>(default).<br>Reads buffered values that take effect on next I/O<br>update. | 0     | R/W | Live         | No            |

|         |       | Reserved                        |          | Reserved.                                                                                                                                                                                                                                                                                                                                                                        | 0x0   | R   | Live         | No            |

|         | 2     | Reset sans registers            |          | Reset Sans Register Map. Writing Logic 1 resets the device while maintaining the current settings.                                                                                                                                                                                                                                                                               | 0     | R/W | Live         | No            |

|         |       | Reserved                        |          | Reserved.                                                                                                                                                                                                                                                                                                                                                                        | 0x0   | R   | Live         | No            |

| )x0003  |       | Reserved                        |          | Reserved.                                                                                                                                                                                                                                                                                                                                                                        | 0x0   | R   | Live         | No            |

|         | [3:0] | Chip type                       | 0x5      | Chip Type. This register is a part of the Analog<br>Devices unified SPI protocol, and is used to identify<br>this chip as a clock IC.<br>clock chip.                                                                                                                                                                                                                             | 0x5   | R   | Live         | No            |

| )x0004  | [7:0] | Device Code[7:0]                |          | Device Code. This read only register contains device identification details.                                                                                                                                                                                                                                                                                                     | 0x21  | R   | Live         | No            |

| 0x0005  | [7:0] | Device Code[15:8]               |          | Continuation of the device code bit field. See the Device Code[7:0] description.                                                                                                                                                                                                                                                                                                 | 0x01  | R   | Live         | No            |

| Address | Bits  | Bit Name               | Settings | Description                                                                                                                                                                                                         | Reset | R/W | IO<br>Update | Auto-<br>clear |

|---------|-------|------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|--------------|----------------|

| 0x0006  | [7:0] | Device Code[23:16]     |          | Continuation of the device code bit field. See the Device Code[7:0] description.                                                                                                                                    | 0x04  | R   | Live         | No             |

| 0x000B  | [7:0] | SPI version            |          | Version of Analog Devices Unified SPI Protocol.                                                                                                                                                                     | 0x00  | R   | Live         | No             |

| 0x000C  | [7:0] | Vendor ID[7:0]         |          | Analog Devices Unified SPI Vendor ID.                                                                                                                                                                               | 0x56  | R   | Live         | No             |

| 0x000D  | [7:0] | Vendor ID[15:8]        |          | Continuation of the vendor ID bit field. See the Vendor ID[7:0] description.                                                                                                                                        | 0x04  | R   | Live         | No             |

| 0x000F  | [7:2] | Reserved               |          | Reserved.                                                                                                                                                                                                           | 0x00  | R   | Live         | No             |

|         | 1     | Address loop IO update |          | Address Loop IO Update. An IO update is<br>automatically issued each time the address field<br>loops. This is useful when polling a range of registers<br>and an I/O update needs to be issued after each<br>cycle. | 0     | R/W | Live         | No             |

|         | 0     | IO update              |          | IO Update. Setting this autoclearing bit transfers values from the buffered to active register space.                                                                                                               | 0     | W   | Live         | Yes            |

| 0x0010  | [7:0] | Address loop length    |          | Address Loop Length. The number of consecutive addresses that are written or read in each cycle in an address loop.                                                                                                 | 0x00  | R/W | Live         | No             |

| 0x0020  | [7:0] | User Scratchpad[7:0]   |          | User Scratchpad. This register has no effect on device operation. It is available for device debugging or register setting revision control.                                                                        | 0x00  | R/W | Live         | No             |

| 0x0021  | [7:0] | User Scratchpad[15:8]  |          | Continuation of the user scratchpad bit field. See the User Scratchpad[7:0] description.                                                                                                                            | 0x00  | R/W | Live         | No             |

| 0x0022  | [7:0] | User Scratchpad[23:16] |          | Continuation of the user scratchpad bit field. See the User Scratchpad[7:0] description.                                                                                                                            | 0x00  | R/W | Live         | No             |

| 0x0023  | [7:0] | User Scratchpad[31:24] |          | Continuation of the user scratchpad bit field. See the User Scratchpad[7:0] description.                                                                                                                            | 0x00  | R/W | Live         | No             |

### Mx PIN MODE—REGISTER 0x0100 TO REGISTER 0x0101

Driver details apply when the corresponding Mx pin is configured as a status pin. Receiver details apply when the corresponding Mx pin is configured as a control pin. To configure an Mx pin for status or control see the Mx Pin Status or Control Select—Register 0x0102 to Register 0x0108 section.

| Table 4 | Mx | Pin | Mode | Details |

|---------|----|-----|------|---------|

|---------|----|-----|------|---------|

| Address | Bits  | Bit Name       | Settings | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Reset | R/W | IO<br>Update            | Auto-<br>clear |

|---------|-------|----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------------------------|----------------|

| 0x0100  | [7:6] | M3 driver      |          | M3 Pin Status Mode (Output). When M3 is configured as a status pin, the user can choose the output polarity (normal (default) or inverted) and output driver type (complementary (default) or open drain).                                                                                                                                                                                                                                                                                                                                                                                | 0x0   | R/W | Serial<br>port<br>clock | No             |

|         |       |                |          | Polarity: relates to how the output pin responds to the true or false<br>state of the selected M3 status function (for example, REFA<br>faulted). With normal polarity, when the selected status function<br>state is true or false, the output pin state is Logic 1 or Logic 0,<br>respectively. With inverted polarity, when the selected status<br>function state is true or false, the output pin state is Logic 0 or<br>Logic 1, respectively.                                                                                                                                       |       |     |                         |                |

|         |       |                |          | Driver type: complementary uses a CMOS output circuit. Open<br>drain uses an NMOS or PMOS output circuit (polarity dependent).<br>Normal polarity uses a PMOS device, which actively drives Logic 1,<br>but is high impedance for Logic 0 (requires an external pull-down<br>resistor). Inverted polarity uses an NMOS device, which actively<br>drives Logic 0, but is high impedance for Logic 1 (requires an<br>external pull-up resistor). The open-drain configuration allows a<br>wire-OR'ed connection to other Mx status pins having an open-<br>drain driver with like polarity. |       |     |                         |                |

|         |       |                | 0        | Complementary normal (default).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |     |                         |                |

|         |       |                | 1        | Complementary inverted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |     |                         |                |

|         |       |                | 2        | Open drain normal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |     |                         |                |

|         |       |                | 3        | Open drain inverted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |     |                         |                |

|         | [7:6] | M3<br>receiver |          | M3 Pin Control Mode (Input). When M3 is configured as a control pin, the user can choose the input polarity (normal (default) or inverted) and logical type (AND (default) or OR).                                                                                                                                                                                                                                                                                                                                                                                                        | 0x0   | R/W | Serial<br>port<br>clock | No             |

|         |       |                |          | Polarity: normal polarity makes no change to the input pin signal.<br>Inverted polarity inverts the input pin signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |     |                         |                |

|         |       |                |          | Logical type: the logical type is only meaningful when the Mx pins<br>other than M3 share a common control function (for example, IO<br>update). In this case, the control function responds to all Mx<br>control pins having the same control function as follows. The OR<br>inputs combine in a logical OR sense to yield a single OR result. The<br>AND inputs, along with the OR result, combine in a logical AND<br>sense to yield a single AND result, which applies to the common<br>control function (for example, IO update).                                                    |       |     |                         |                |

|         |       |                | 0        | AND normal (default).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |     |                         |                |

|         |       |                | 1        | AND inverted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |     |                         |                |

|         |       |                | 2        | OR normal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |     |                         |                |

|         |       |                | 3        | OR inverted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |     |                         |                |

| Address | Bits  | Bit Name       | Settings         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Reset | R/W | IO<br>Update            | Auto-<br>clear |

|---------|-------|----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------------------------|----------------|

|         | [5:4] | M2 driver      |                  | M2 Pin Status Mode (Output). When M2 is configured as a status<br>pin, the user can choose the output polarity (normal (default) or<br>inverted) and output driver type (complementary (default) or open<br>drain).<br>Polarity: relates to how the output pin responds to the true or false<br>state of the selected M2 status function (for example, REFA<br>faulted). With normal polarity, when the selected status function<br>state is true or false, the output pin state is Logic 1 or Logic 0,<br>respectively. With inverted polarity, when the selected status<br>function state is true or false, the output pin state is Logic 0 or<br>Logic 1, respectively.                                                                                                                                                                                  | 0x0   | R/W | Serial<br>port<br>clock | No             |

|         |       |                | 0 1 2            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |     |                         |                |

|         | [5:4] | M2<br>receiver | 3                | M2 Pin Control Mode (Input). When M2 is configured as a control<br>pin, the user can choose the input polarity (normal (default) or<br>inverted) and logical type (AND (default) or OR).<br>Polarity: normal polarity makes no change to the input pin signal.<br>Inverted polarity inverts the input pin signal.<br>Logical type: the logical type is only meaningful when the Mx pins<br>other than M2 share a common control function (for example, IO<br>update). In this case, the control function responds to all Mx<br>control pins having the same control function as follows. The OR<br>inputs combine in a logical OR sense to yield a single OR result. The<br>AND inputs, along with the OR result, combine in a logical AND<br>sense to yield a single AND result, which applies to the common<br>control function (for example, IO update). | 0x0   | R/W | Serial<br>port<br>clock | No             |

|         |       |                | 0<br>1<br>2<br>3 | AND normal (default).<br>AND inverted.<br>OR normal.<br>OR inverted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |     |                         |                |

| Address | Bits  | Bit Name       | Settings | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Reset | R/W | IO<br>Update            | Auto-<br>clear |

|---------|-------|----------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------------------------|----------------|

|         | [3:2] | M1 driver      |          | M1 Pin Status Mode (Output). When M1 is configured as a status<br>pin, the user can choose the output polarity (normal (default) or<br>inverted) and output driver type (complementary (default) or open<br>drain).<br>Polarity: relates to how the output pin responds to the true or false<br>state of the selected M1 status function (for example, REFA<br>faulted). With normal polarity, when the selected status function                                                                                                                                                                                             | 0x0   | R/W | Serial<br>port<br>clock | No             |

|         |       |                |          | state is true or false, the output pin state is Logic 1 or Logic 0,<br>respectively. With inverted polarity, when the selected status<br>function state is true or false, the output pin state is Logic 0 or<br>Logic 1, respectively.                                                                                                                                                                                                                                                                                                                                                                                       |       |     |                         |                |

|         |       |                | 0        | Driver type: complementary uses a CMOS output circuit. Open<br>drain uses an NMOS or PMOS output circuit (polarity dependent).<br>Normal polarity uses a PMOS device, which actively drives Logic 1,<br>but is high impedance for Logic 0 (requires an external pull-down<br>resistor). Inverted polarity uses an NMOS device, which actively<br>drives Logic 0, but is high impedance for Logic 1 (requires an<br>external pull-up resistor). The open-drain configuration allows a<br>wire-OR'ed connection to other Mx status pins having an open-<br>drain driver with like polarity.<br>Complementary normal (default). |       |     |                         |                |