## Data Converter Function Can Help Solve Cost and Size Design Challenges in 3G and 4G Wireless Infrastructure

As usage and demand for competitive services continue to rise, manufacturers of wireless infrastructure, especially 3G and 4G, must constantly reduce the size and cost of newly installed wireless infrastructure, while holding to high standards of performance, functionality, and quality of service. The data conversion block is a critical function in wireless infrastructure designs, and selecting a converter that is The power reduction in the AD9640, vs. the previous single ADC solutions, provides benefits for base station design. Because many new wireless infrastructure systems are being mounted on outside poles, they cannot utilize active heating and cooling systems as afforded by equipment sheds and buildings. By consuming a relatively low 390 mW/channel, the AD9640 simplifies the mechanical

targeted for this application is key to improving the overall system design and breaking through design barriers such as size and cost.

In the main receiver function, the analog-to-digital converter (ADC) is the key block that digitizes the incoming intermediate frequency (IF) signal (after it has been mixed down from the antenna) and then passes the digital data to the digital downconverter. Most architectures require two receivers, called main and diversity, each requiring a high performance, high speed ADC. Until now, sampling rates beyond 135 MSPS could only be realized by utilizing single-channel 14-bit ADCs. This

and passive thermal design requirements of the pole-mounted transceiver enclosure.

The high performance level achieved by this dual ADC also contributes to significant cost savings in a wireless infrastructure design. Within the radio receiver there is an automatic gain control (AGC) loop that controls the strength of the desired incoming signal. The function of the AGC is to maintain a fixed input signal level to the ADC to ensure that it meets the dynamic range requirements of the system. As a cell phone user moves farther away from the cell

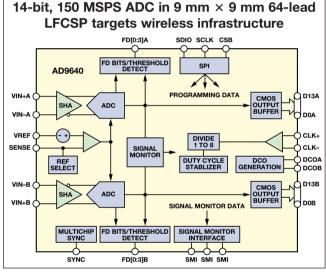

constraint necessitated implementing two separate converter blocks, with their associated requirements in power, PCB area, and cost. The new ADC solution from Analog Devices, the AD9640, dual, 14-bit, 150 MSPS A/D converter, addresses this issue. This dual device enables a 50% reduction in converter board space requirements in the main and diversity architecture. And the AD9640 contains additional attributes that improve wireless infrastructure system design.

A 150 MSPS ADC sampling rate simplifies some of the signal chain complexity and cost associated with a communications design. As sampling rates increase, analog input filtering requirements decrease, and the reduced filtering complexity results in lower cost. Also, because the AD9640 can sample an IF input signal as high as 450 MHz, an analog mix down stage can be eliminated from the receiver input signal chain. This attribute functionality allows savings in board space and cost, and improves performance through the elimination of an analog block and its associated noise contribution.

tower, the AGC loop increases its gain to ensure adequate reception. If the ADC has a higher signal-to-noise ratio (SNR), the AGC loop does not need as much gain because the ADC can resolve smaller signals and can operate with reduced input levels. Likewise, large interfering signals can cause the ADC to generate spurious components or harmonics. ADCs with higher SFDR performance allow the system to tolerate larger interferers without having to adjust the AGC. In both cases the AGC circuit can be simplified or eliminated with a high performance ADC like the AD9640, which delivers SNR of 72.7 dBFS, and an SFDR of 85 dBc, with a 70 MHz IF input.

Analog Devices offers a wide portfolio of ADCs for communications applications. For data sheets and additional information on the AD9640, visit *www.analog.com/AD9640* or call 1-800-AnalogD. ■

Author Profile: **Chris Cloninger** is the business development manager for Analog Devices' High Speed Signal Processing Product Line.