| Radiation Test Report |                                            |  |  |  |  |  |  |  |

|-----------------------|--------------------------------------------|--|--|--|--|--|--|--|

| Product:              | ADA4096-2S                                 |  |  |  |  |  |  |  |

| Effective LET:        | 80.7 MeV-cm <sup>2</sup> /mg               |  |  |  |  |  |  |  |

| Fluence:              | 1E7 lons/cm <sup>2</sup>                   |  |  |  |  |  |  |  |

| Die Type:             | ADA4096-2                                  |  |  |  |  |  |  |  |

| Facilities:           | RADEF, University of<br>Jyvaskyla, Finland |  |  |  |  |  |  |  |

| Tested:               | September 2015                             |  |  |  |  |  |  |  |

The RADTEST® DATA SERVICE is a compilation of radiation test results on Analog Devices' Space grade products. It is designed to assist customers in selecting the right product for applications where radiation is a consideration. Many products manufactured by Analog Devices, Inc. have been shown to be radiation tolerant to most tactical radiation environments. Analog Devices, Inc. does not make any claim to maintain or guarantee these levels of radiation tolerance without lot qualification test.

It is the responsibility of the Procuring Activity to screen products from Analog Devices, Inc. for compliance to Nuclear Hardness Critical Items (HCI) specifications.

### Warning:

Analog Devices, Inc. does not recommend use of this data to qualify other product grades or process levels. Analog Devices, Inc. is not responsible and has no liability for any consequences, and all applicable Warranties are null and void if any Analog Devices product is modified in any way or used outside of normal environmental and operating conditions, including the parameters specified in the corresponding data sheet. Analog Devices, Inc. does not guarantee that wafer manufacturing is the same for all process levels.

# SINGLE EVENT EFFECTS TEST REPORT

Test Type: Heavy ion

Test facility: RADEF, University of Jyvaskyla, Finland

Test Date: September 2015

Part Type: AD4096-2

Part Description: Dual 30 V, Micropower, Overvoltage Protection, Rail-to-Rail

Input/Output Amplifiers

Part Manufacturer: Analog Devices

Analog Devices PO No 45516080 dated 22/06/2015

| Hirex reference : | HRX/SEE/0538  | Issue: 01       | Date: October 28, 2015 |    |  |

|-------------------|---------------|-----------------|------------------------|----|--|

| Written by :      | Mehdi Kaddour | Design Engineer | 4                      |    |  |

| Authorized by:    | F.X. Guerre   | Study Manager   |                        | fm |  |

**Hirex Engineering**

### **SEE Test Report**

Ref.: **HRX/SEE/0538**

Issue: 01

#### **RESULTS SUMMARY**

#### **Facility**

RADEF, University of Jyvaskyla, Finland

#### **Test date**

September 2015

#### **Device description**

Dual Dual 30 V, Micropower, Overvoltage Protection, Rail-to-Rail Input/Output Amplifiers

Part type: AD4096-2

Manufacturer: Analog Devices

Package: MSOP-8

Samples used: 6

Top marking: logo A 2T Bottom marking: #517 7095

Date code: 1517

<u>Die dimensions:</u> 1.230 mm X 0.866 mm

#### **SEL Results**

No SEL neither step current increase has been observed when tested with V+/- set to 5V at any LET value at 125°C with all tested samples.

**Hirex Engineering**

## **SEE Test Report**

Ref.: HRX/SEE/0538

Issue: **01**

#### **DOCUMENTATION CHANGE NOTICE**

| Issue | Date       | Page | Change Item    |  |

|-------|------------|------|----------------|--|

| 01    | 28/10/2015 | All  | Original issue |  |

|       |            |      |                |  |

|       |            |      |                |  |

|       |            |      |                |  |

|       |            |      |                |  |

|       |            |      |                |  |

|       |            |      |                |  |

|       |            |      |                |  |

|       |            |      |                |  |

## Contributors to this work:

Bendy Tanios Hirex Engineering Mehdi Kaddour Hirex Engineering

Issue: **01**

### **SEE TEST REPORT**

## **TABLE OF CONTENTS**

| 1 INTRODUCTION                                          | 5  |

|---------------------------------------------------------|----|

| 2 APPLICABLE AND REFERENCE DOCUMENTS                    | 5  |

| 2.1 APPLICABLE DOCUMENTS  2.2 REFERENCE DOCUMENTS       |    |

| 3 DEVICE INFORMATION                                    | 6  |

| 3.1 DEVICE DESCRIPTION                                  | 6  |

| 4 RADEF FACILITY                                        | 7  |

| 5 TEST SET-UP                                           | 8  |

| 5.1 AD4096-2 TEST PRINCIPLE AND CONDITIONS              | 8  |

| 6 SEE TEST RESULTS                                      | 10 |

| 6.1 SEL RESULTS                                         | 10 |

| 7 GLOSSARY                                              | 11 |

| LIST OF FIGURES                                         |    |

| Figure 1 – AD4096-2 device identification               |    |

| Figure 2 - Heavy ion test set-up                        |    |

| Figure 4 – Photo of test board                          |    |

| LIST OF TABLES                                          |    |

| Table 1 – Ion beam setting                              | 7  |

| Table 2 - Voltage bias conditions applied to the 2 DUTs |    |

| Table 3 - Tester supply channel affectation             |    |

Issue: **01**

#### 1 <u>Introduction</u>

This report presents the results of SEL Heavy Ions test program carried out on Analog Devices AD4096-2. On September 2015, 6 samples were used for heavy ions testing at RADEF, University of Jyvaskyla, Finland .This work was performed for Analog Devices, Greensboro under PO n° 45516080 dated 22/06/2015.

### 2 Applicable and Reference Documents

#### 2.1 Applicable Documents

AD-1. Datasheet: http://www.analog.com/media/en/technical-documentation/data-sheets/ADA4096-2\_4096-4.pdf

#### 2.2 Reference Documents

RD-1. Single Event Effects Test method and Guidelines ESA/SCC basic specification No 25100

HRX/SEE/0538 Ref.:

01 Issue:

#### 3 **DEVICE INFORMATION**

#### 3.1 **Device description**

AD4096-2 is a dual Dual 30 V, Micropower, Overvoltage Protection, Rail-to-Rail Input/Output Amplifiers.

AD4096-2

Part number: ADA4096 - 2ARMZ Manufacturer: **Analog Devices** MSOP-8 Package:

Samples used:

Top marking: logo A 2T **Bottom marking:** #517 7095 Date code: 1517

Die dimensions: 1.230 mm X 0.866 mm

#### 3.2 Sample identification

12 AD4096-2 parts were delivered by Analog Devices, Greensboro. Samples were prepared and opened chemically to be tested to heavy ions. 6 samples were verified fully functional before the test campaign, and 6 were tested under irradiation.

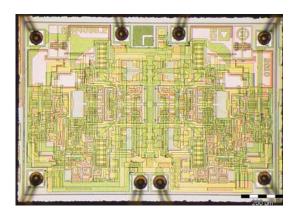

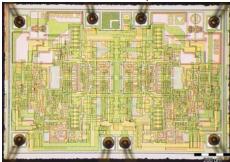

Photo 1 - Device top view

Photo 3 - die, full view

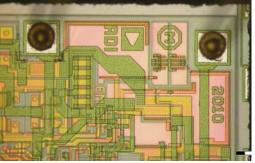

Photo 5 - Die marking #2

Photo 2 - Device delidded

Photo 4 - Die marking #1

Photo 6 - Die marking #3

Figure 1 - AD4096-2 device identification

#### 3.3 Sample preparation and evaluation of dead layer thickness

Samples were opened chemically.

Die micro-section results are given in appendix. Overall dead layer thickness on top of active zone is less or equal to 10 microns of equivalent silicon.

Issue: 01

#### 4 RADEF Facility

Test at the cyclotron accelerator was performed at University of Jyvaskyla (JYFL) (Finland) under HIREX Engineering responsibility.

The facility includes a special beam line dedicated to irradiation studies of semiconductor components and devices. It consists of a vacuum chamber including component movement apparatus and the necessary diagnostic equipment required for the beam quality and intensity analysis.

The cyclotron is a versatile, sector-focused accelerator of beams from hydrogen to xenon equipped with three external ion sources: two electron cyclotron resonance (ECR) ion sources designed for high-charge-state heavy ions, and a multicusp ion source for intense beams of protons. The ECR's are especially valuable in the study of single event effects (SEE) in semiconductor devices. For heavy ions, the maximum energy attainable can be determined using the formula,

130 Q<sup>2</sup>/M,

where Q is the ion charge state and M is the mass in Atomic Mass Units.

#### Test chamber

Irradiation of components is performed in a vacuum chamber with an inside diameter of 75 cm and a height of 81 cm.

The vacuum in the chamber is achieved after 15 minutes of pumping, and the inflation takes only a few minutes. The position of the components installed in the linear movement apparatus inside the chamber can be adjusted in the X, Y and Z directions. The possibility of rotation around the Y-axis is provided by a round table. The free movement area reserved for the components is 25 cm x 25 cm, which allows one to perform several consecutive irradiations for several different components without breaking the vacuum. The assembly is equipped with a standard mounting fixture. The adapters required to accommodate the

special board configurations and the vacuum feed-throughs can also be made in the laboratory's workshops. The chamber has an entrance door, which allows rapid changing of the circuit board or individual components.

A CCD camera with a magnifying telescope is located at the other end of the beam line to determine accurate positioning of the components. The coordinates are stored in the computer's memory allowing fast positioning of various targets during the test.

#### Beam quality control

For measuring beam uniformity at low intensity, a CsI(TI) scintillator with a PIN-type photodiode readout is fixed in the mounting fixture. The uniformity is measured automatically before component irradiation and the results can be plotted immediately for more detailed analysis.

A set of four collimated PIN-CsI(TI) detectors is located in front of the beam entrance. The detectors are operated with step motors and are located at 90 degrees with respect to each other. During the irradiation and uniformity scan they are set to the outer edge of the beam in order to monitor the stability of the homogeneity and flux.

Two beam wobblers and/or a 0.5 microns diffusion Gold foil can be used to achieve good beam homogeneity. The foil is placed 3 m in front of the chamber. The wobbler-coils vibrate the beam horizontally and vertically, the proper sweeping area being attained with the adjustable coil-currents.

#### **Dosimetry**

The flux and intensity dosimeter system contains a Faraday cup, several collimators, a scintillation counter and four PIN-CsI(TI) detectors. Three collimators of different size and shape are placed 25 cm in front of the device under test. They can be used to limit the beam to the active area to be studied.

At low fluxes a plastic scintillator with a photomultiplier tube is used as an absolute particle counter. It is located behind the vacuum chamber and is used before the irradiation to normalize the count rates of the four PIN-CsI(TI) detectors.

| lon                              | LET <sup>SRIM</sup> at surface           | Range | Beam energy |  |  |  |

|----------------------------------|------------------------------------------|-------|-------------|--|--|--|

| 1011                             | [MeV.cm <sup>2</sup> .mg <sup>-1</sup> ] | [µm]  | [MeV]       |  |  |  |

| <sup>20</sup> Ne <sup>6+</sup>   | 3.63                                     | 146   | 186         |  |  |  |

| <sup>40</sup> Ar <sup>12+</sup>  | 10.2                                     | 118   | 372         |  |  |  |

| <sup>56</sup> Fe <sup>15+</sup>  | 18.5                                     | 97    | 523         |  |  |  |

| <sup>82</sup> Kr <sup>22+</sup>  | 32.1                                     | 94    | 768         |  |  |  |

| <sup>131</sup> Xe <sup>35+</sup> | 60.0                                     | 89    | 1217        |  |  |  |

Table 1 – Ion beam setting

SRIM-2003.26

Issue: 01

#### 5 Test Set-up

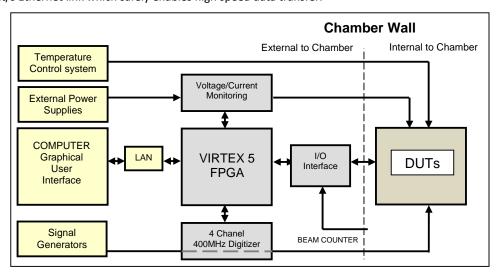

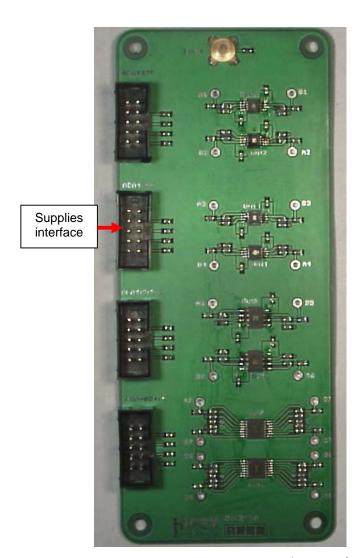

Test system Figure 2 shows the principle of the Heavy Ion test system.

The test system is based on a Virtex5 FPGA (Xilinx). It runs at 50 MHz. The test board has 168 I/Os which can be configured using several I/O standards.

The test board includes the voltage/current monitoring and the latch-up management of the DUT power supplies up to 24 independent channels.

The communication between the test chamber and the controlling computer is effectively done by a 100 Mbit/s Ethernet link which safely enables high speed data transfer.

Figure 2 - Heavy ion test set-up

#### 5.1 AD4096-2 test principle and conditions

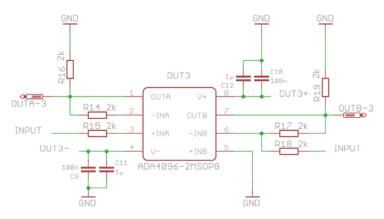

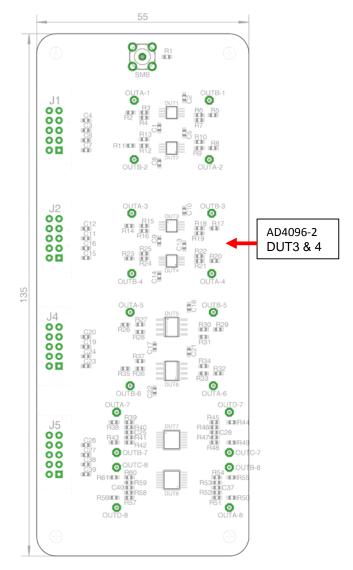

In order to test the AD4096-2, one daughter board was designed. 2 DUTs were mounted on this board (Dut3 and Dut4 positions) and bias conditions are given in Figure 3 and Table 2. Table 3 gives the tester supply channel number used in the tester report.

DUT heating is performed with a thermal resistor in contact with DUTs backside using a thermal conductive paste. The temperature is regulated thanks to a thermocouple sensor put on top of the DUT package.

SEL event is detected when the supply current is over a configurable threshold (in the present case set to 100 mA for V+ and -100mA for V-) and processed (the power supplies are cut off during a configurable wait time, in the present case set to 1s).

The tester monitors independently the 2 DUTs supplies at the same time. If an SEL is detected on 1 supply channel, the tester system records current/voltage on all channels.

| Supply name | voltage                  |  |  |  |  |  |  |

|-------------|--------------------------|--|--|--|--|--|--|

| DUT_V+      | +5V                      |  |  |  |  |  |  |

| DUT_V-      | -5V                      |  |  |  |  |  |  |

| INPUT       | Sine wave ±1V at 100 KHz |  |  |  |  |  |  |

Table 2 - Voltage bias conditions applied to the 2 DUTs

| Supply name | Tester supply channel # |

|-------------|-------------------------|

| DUT3_V+     | 5                       |

| DUT3_V-     | 6                       |

| DUT4_V+     | 7                       |

| DUT4_V-     | 8                       |

| INPUT       | 17                      |

Issue: 01

Table 3 - Tester supply channel affectation

Input: Sine wave  $\pm 1V$  at 100 KHz Supply voltage:  $\pm 5.0V$  Load resistance =  $2~k\Omega$  Channel A gain set to  $\pm 1$

Channel B gain set to -1

Figure 3 - AD4096-2 bias condition

Figure 4 – Photo of test board

Issue: **01**

## 6 **SEE test results**

Runs performed are listed in Table 4.

3 boards have been tested with 2 AD4096-2 samples mounted on each board (Dut3 and Dut4 positions). Upon test completion, all samples were found fully functional

### 6.1 <u>SEL Results</u>

No SEL neither step current increase has been observed when tested with V+/- set to 5V at any LET value at 125°C with all tested samples.

|          |        |                  |                     | G 0G     |                               |              |           |                    |     |                     |      |      |                   |                              |                          |             |

|----------|--------|------------------|---------------------|----------|-------------------------------|--------------|-----------|--------------------|-----|---------------------|------|------|-------------------|------------------------------|--------------------------|-------------|

| Facility | medium | hirex_run_number | Facility_run_number | board_id | dut_part_number<br>under test | power_config | test_mode | temperature<br>° C | lon | LET<br>MeV/(mg/cm2) | roll | tilt | run_duration<br>s | achieved fluence<br>ions/cm2 | eff. LET<br>MeV/(mg/cm2) | dut_comment |

| RADEF    | vacuum | 3                | 3                   | 2        | 3 & 4                         | +/-5V        | SEL       | 105                | Ar  | 10.2                | 0    | 0    | 278               | 1.00E+07                     | 10.2                     | ОК          |

| RADEF    | vacuum | 6                | 6                   | 2        | 3 & 4                         | +/-5V        | SEL       | 125                | Ar  | 10.2                | 0    | 0    | 333               | 1.00E+07                     | 10.2                     | ОК          |

| RADEF    | vacuum | 56               | 56                  | 3        | 3 & 4                         | +/-5V        | SEL       | 125                | Xe  | 60                  | 0    | 0    | 497               | 1.00E+07                     | 60                       | ОК          |

| RADEF    | vacuum | 57               | 57                  | 3        | 3 & 4                         | +/-5V        | SEL       | 125                | Xe  | 60                  | 0    | 31   | 237               | 1.00E+07                     | 70                       | ОК          |

| RADEF    | vacuum | 58               | 58                  | 3        | 3 & 4                         | +/-5V        | SEL       | 125                | Xe  | 60                  | 0    | 42   | 257               | 1.00E+07                     | 80.7                     | ОК          |

| RADEF    | vacuum | 62               | 62                  | 4        | 3 & 4                         | +/-5V        | SEL       | 125                | Xe  | 60                  | 0    | 42   | 269               | 1.00E+07                     | 80.7                     | ОК          |

Table 4 - Run table for the AD4096-2, RADEF September 2015

Issue: 01

#### 7 Glossary

Most of the definitions here below are from JEDEC standard JESD89A

DUT: Device under test.

Fluence (of particle radiation incident on a surface): The total amount of particle radiant energy incident on a surface in a given period of time, divided by the area of the surface. In this document, Fluence is expressed in ions per cm2.

Flux: The time rate of flow of particle radiant energy incident on a surface, divided by the area of that surface.

In this document, Flux is expressed in ions per cm2\*s.

Single-Event Effect (SEE): Any measurable or observable change in state or performance of a microelectronic device, component, subsystem, or system (digital or analog) resulting from a single energetic particle strike. Single-event effects include single-event upset (SEU), multiple-bit upset (MBU), multiple-cell upset (MCU), single-event functional interrupt (SEFI), single-event latch-up (SEL.

Single-Event Transient (SET): A soft error caused by the transient signal induced by a single energetic particle strike.

Single-Event Latch-up (SEL): An abnormal high-current state in a device caused by the passage of a single energetic particle through sensitive regions of the device structure and resulting in the loss of device functionality.

SEL may cause permanent damage to the device. If the device is not permanently damaged, power cycling of the device (off and back on) is necessary to restore normal operation.

An example of SEL in a CMOS device is when the passage of a single particle induces the creation of parasitic bipolar (p-n-p-n) shorting of power to ground.

Single-Event Latch-up (SEL) cross-section: the number of events per unit fluence. For chip SEL cross-section, the dimensions are cm2 per chip.

Error cross-section: the number of errors per unit fluence. For device error cross-section, the dimensions are cm2 per device. For bit error cross-section, the dimensions are cm2 per bit.

Tilt angle: tilt angle, rotation axis of the DUT board is perpendicular to the beam axis; roll angle, board rotation axis is parallel to the beam axis