One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

# ADA4558 Sensor Signal Conditioner for Bridge Sensors

## SCOPE

This reference manual provides a detailed description of the functionality and features of the ADA4558.

Full specifications on the ADA4558 are available in the ADA4558 data sheet. Consult the data sheet in conjunction with this reference manual when working with this device.

# ADA4558 Hardware Reference Manual

# TABLE OF CONTENTS

| Scope 1                                                     |

|-------------------------------------------------------------|

| Revision History 2                                          |

| ADA4558 Overview                                            |

| Bridge Sensor Input 5                                       |

| EMI Filters 5                                               |

| Inverting Switch Operation5                                 |

| PGA                                                         |

| Antialias Low-Pass Filter 6                                 |

| Internal Temperature Sensor7                                |

| Internal Temperature Sensor for Bridge Sensor Calibration 7 |

| Internal Temperature Sensor Output to LIN Signal Frame 7    |

| External Temperature Sensor                                 |

| ADC Operation9                                              |

| User Configurable Filtering11                               |

| OTP Code Storage Memory12                                   |

| EEPROM                                                      |

| EEPROM Bit Descriptions14                                   |

| EEPROM Caching                                              |

# **REVISION HISTORY**

5/2019—Revision 0: Initial Version

| LIN Interface                                                |

|--------------------------------------------------------------|

| LIN Initializations                                          |

| Frame Types22                                                |

| LIN Sleep/Wake-Up Mode28                                     |

| SYSREG Map 28                                                |

| Fault Handling, Diagnostics, and Logging Feature             |

| Fault Recovery                                               |

| Fault Descriptions                                           |

| Calibration Procedure                                        |

| Place the ADA4558 in Configuration Mode                      |

| PGA Gain for the Bridge Sensor Input 39                      |

| Calculating the Common-Mode Voltage Trim                     |

| Calculating the Sensor Offset Voltage Trim at PGA Stage 1 40 |

| Sensor Offset Voltage Trim, PGA Stage 2 41                   |

| Sensor Offset Voltage Trim, PGA Stage 3 41                   |

| Gain Setting for External Temperature Sensor                 |

| Calibration Routine for External Temperature Sensor 42       |

| Bridge Sensor Channel Calibration                            |

# **ADA4558 OVERVIEW**

The ADA4558 is an automotive grade, signal conditioner IC that interfaces to a range of strain gauge sensors, based on a Wheatstone bridge output. The ADA4558 senses the resistive changes in a Wheatstone bridge sensor that are proportional to the force applied to the sensor. A typical application for the ADA4558 is pressure sensing, where the sensor forms a diaphragm type pressure transducer. The measurable signal from the sensor contains errors due to mechanical, thermal, tolerance, and gauge factor errors.

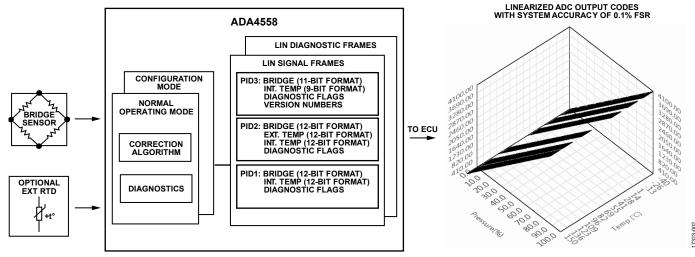

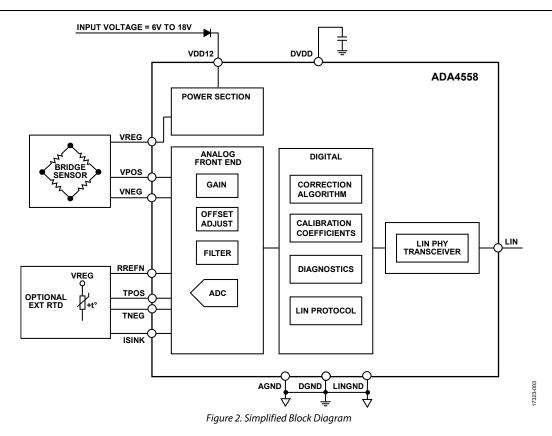

The ADA4558 is a configurable device that nulls out the nonideal behaviors of the sensor. The device provides signal conditioning to compensate for sensor offset errors, voltage span variation, sensitivity linearity, and temperature dependency. To provide temperature compensation, the ADA4558 can be configured to use either an internal temperature sensor or an external resistance temperature detector (RTD). The ADA4558 provides signal conditioning to compensate for first- or secondorder error correction of temperature and sensitivity. Figure 2 shows a simplified block diagram of the ADA4558. The analog front end (AFE) contains circuitry to apply filters, gain, and offset adjust to the input signal. The digital block contains a correction algorithm to apply the linearization correction for temperature and sensitivity. The digital block provides the local interconnect network (LIN) protocol for interface logic for reading the corrected signal measurements.

The corrected measurements are mapped to a digital 12-bit code, where strain gauge minimum to maximum measurements can be mapped to Code 0 to Code 4095. The system accuracy is 0.1% full-scale range (FSR).

Configuration mode allows calibration and initial setup tasks where an end of line calibration can be run. Perform an end of line (EOL) calibration where the strain gauge sensor is connected to the ADA4558. A calibration routine generates coefficients that are stored in electrically erasable programmable read only memory (EEPROM), and used by the correction algorithm.

In normal operating mode, the ADA4558 applies coarse signal conditioning to maximize analog-to-digital converter (ADC) range, and uses a digital correction algorithm to apply a fine signal conditioning and linearization. The device operates as a LIN slave device and communicates the bridge sensor and temperature measurements over the LIN interface to the master engine control unit (ECU).

Figure 1. ADA4558 Operational Overview

# UG-1487

ADA4558 Hardware Reference Manual

# **BRIDGE SENSOR INPUT**

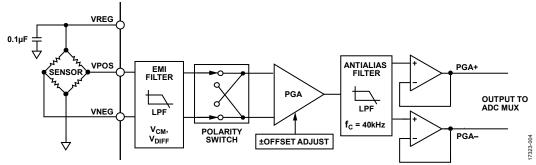

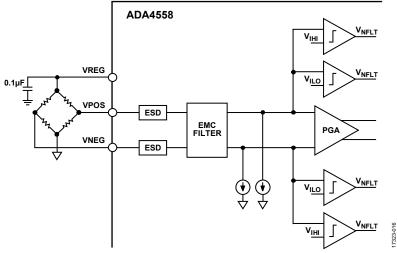

The differential signal from the bridge sensor is measured across the VPOS pin and VNEG pin of the ADA4558 (see Figure 3). The ADA4558 includes a 4 V regulator output at the VREG pin. The VREG pin supplies power to the bridge sensor, the external temperature sensor, and the ADC reference This supply voltage creates a fully ratiometric measurement system.

Figure 2 shows a simplified block diagram of the ADA4558 AFE with the bridge sensor input. The bridge sensor input consists of the following components:

- Electromagnetic interference (EMI) filters

- Optional polarity switching

- Programmable gain amplifier (PGA) gain with offset correction

- Antialiasing filters

- Signal buffers

# **EMI FILTERS**

The ADA4558 features IC level resistor-capacitor (RC) filters on the PGA inputs. The differential filter has a 3 dB cutoff frequency ( $f_{-3}$  dB) of 550 kHz and the common-mode filter has an  $f_{-3}$  dB of 580 kHz. The filters provide 20 dB per decade of roll-off on injected EMI signals.

# **INVERTING SWITCH OPERATION**

An inverting switch connects the PGA inputs, the VPOS pin, and VNEG pin. When enabled in EEPROM, the switch reverses the PGA connection between the VPOS pin and the VNEG pin. This feature provides flexibility in the bonding of the bridge to the printed circuit board (PCB) to simplify connection and improve PCB layout.

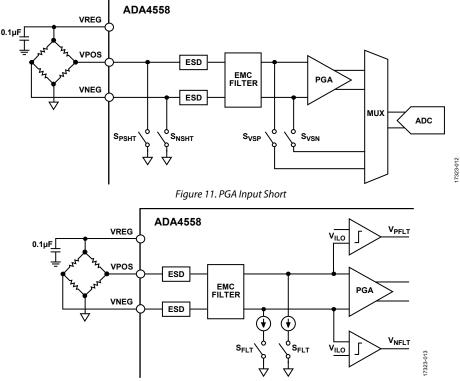

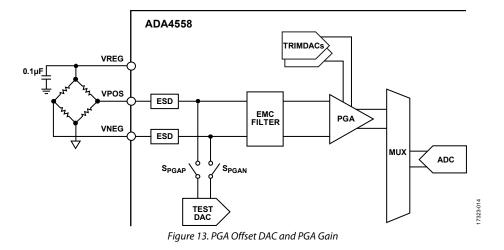

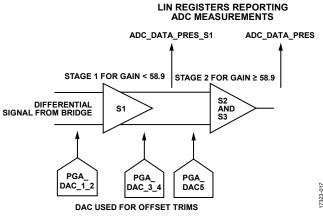

## PGA

A three-stage PGA at the front end provides offset correction and gain of the bridge sensor signal. The range of the coarse PGA gain and offset settings allows accurate operation with a wide range of bridge sensitivities. Configure the PGA for system offset voltage,  $V_{CM_3}$  and PGA gain with the following settings in the EEPROM:

- BRG\_VOS\_TRIM1[6:0]: System offset voltage trim for PGA Stage 1 (S1).

- BRG\_VOS\_TRIM2[6:0]: System offset voltage trim for PGA Stage 2 (S2).

- PGA\_DAC\_5[6:0]: System offset voltage trim for PGA Stage 3 (S3).

- BRG\_VCM\_TRIM[6:0]: Common-mode voltage trim.

- PGA\_GAIN[4:0]: PGA gain setting.

## **Offset Correction**

During EOL calibration, the bridge sensor is set to the zero strain signal level and the system offset voltage is measured. Use PGA DACs to apply biasing to adjust the offset voltage to the desired levels. These PGA DAC codes are saved to the EEPROM. The PGA DAC codes used must be greater than the listed minimum PGA DAC codes shown in Table 2. This is a coarse offset adjust for common mode, and removes positive and negative bridge offsets.

### **Gain Settings**

The PGA has 24 programmable gain settings, and can be set with PGA\_GAIN [4:0] in the EEPROM. See Table 1 for the values used to configure the PGA gain.

The first column of Table 1 shows the settings necessary to program to PGA\_GAIN bits in the EEPROM. The second column in Table 1 shows the selected gain of the PGA. The third column of Table 1 shows the maximum allowed differential input voltage to the VPOS pin and the VNEG pin for each gain setting.

The output of the PGA is the gained signal from the bridge sensor with sensor offset correction and  $V_{\rm CM}$  offset correction. The VDIFF PGA output is applied to the ADC. Select the necessary PGA gain to maximize the dynamic range of the ADC.

The PGA gain settings provide a coarse gain adjust for the ADC input. Fine gain adjustments and linearization are performed by the digital correction algorithm.

### Table 1. PGA Gain Settings and Range

| PGA Gain Settings, | Nominal PGA | Maximum Sensor |

|--------------------|-------------|----------------|

| PGA_GAIN[4:0]      | Gain (V)    | Input Span (V) |

| 00000              | 2.94        | 1.253805       |

| 00001              | 3.8         | 0.970109       |

| 00010              | 5.0         | 0.740447       |

| 00011              | 6.3         | 0.579944       |

| 00100              | 8.1         | 0.455537       |

| 00101              | 11.2        | 0.327793       |

| 00110              | 11.8        | 0.310175       |

| 00111              | 15.1        | 0.240339       |

| 10000              | 20.1        | 0.180348       |

| 10001              | 25.0        | 0.144312       |

| 10010              | 32.5        | 0.110424       |

| 10011              | 44.9        | 0.079112       |

| 10100              | 58.9        | 0.059942       |

| 10101              | 75.4        | 0.046314       |

| 10110              | 100.3       | 0.034592       |

| 10111              | 125.2       | 0.027282       |

| 11000              | 162.52      | 0.020524       |

| 11001              | 224.72      | 0.014165       |

| 11010              | 274         | 0.011194       |

| 11011              | 349.1       | 0.008343       |

| 11100              | 473.5       | 0.005731       |

| 11101              | 573.0       | 0.004252       |

| 11110              | 722.3       | 0.002910       |

| 11111              | 971.10      | 0.001582       |

Figure 3. AFE for Bridge Sensor Input

The PGA output on the ADA4558 uses chopper stabilization to improve offset performance. To ensure that the PGA output does not saturate at the rails, select the PGA gain such that the output (including the gained up, residual, unchopped offset) always remains within the power supply rails. The residual, unchopped offset is approximately 1 mV.

# **ANTIALIAS LOW-PASS FILTER**

The output of the PGA is fed through an antialias, low-pass filter with an  $f_{-3}$  dB of 40 kHz, which limits the bandwidth of the sampled analog signal at the ADC.

This output is buffered and provided to the ADC input through PGA+ and PGA-. The PGA- input to the ADC is fixed at 6.25% regulated 4.0 V output at pin  $11(V_{REG})$ . Note that the ADC converts the difference between the PGA+ and PGA- when estimating the ADC output for a given PGA input voltage.

### Table 2. PGA DAC Minimum Usable Code

| PGA DAC | Minimal DAC Code |

|---------|------------------|

| PGADAC1 | 15               |

| PGADAC2 | 15               |

| PGADAC3 | 12               |

| PGADAC4 | 12               |

| PGADAC5 | 2                |

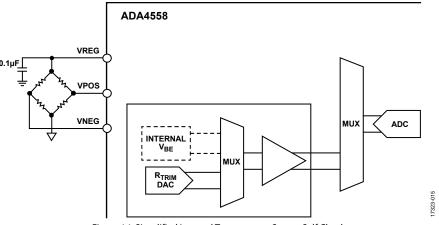

# INTERNAL TEMPERATURE SENSOR

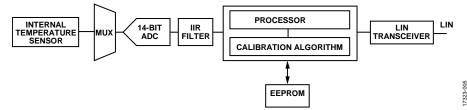

Figure 4. Internal Temperature Sensor

ADC Low Code = 1720

ADC High Code = 8840

# INTERNAL TEMPERATURE SENSOR FOR BRIDGE SENSOR CALIBRATION

The ADA4558 has an on-board, silicon diode-based temperature sensor that reads back the die temperature. The internal temperature sensor block is read by the ADC at a 50 kHz sample rate, and then filtered through a 125 Hz bandwidth. Further filtering is possible, as described in the User Configurable Filtering section. This temperature channel, raw ADC data is saved to the SYSREG Address 0x91 (ADC DATA TEMP).

The ADA4558 uses the die temperature reading to approximate the bridge sensor temperature in applications where the sensor and IC are in close proximity. Configure the ADA4558 to use the ADC\_DATA\_TEMP value for the bridge sensor correction of temperature dependent effects by writing 0 to the TEMP\_SEL bit in the EEPROM Address 13 (0x0D).

# **INTERNAL TEMPERATURE SENSOR OUTPUT TO** LIN SIGNAL FRAME

A 9-bit or 12-bit representation of the die temperature reading is available over the LIN signal frames where the ADC code represents a maximum temperature range of -40°C to +150°C. To calibrate the internal temperature reported via LIN, use the INT\_ TCOEFF0 and INT\_TCOEFF1 values stored in the EEPROM. The following equation is the transfer function for the internal temperature output to LIN signal frames. Note that this calibration is not required for nonlinear correction of the bridge sensor channel input.

Internal Temperature = (INT\_TCOEFF0 + INT\_TCOEFF1 × ADC\_DATA\_TEMP × 4095 (1)

where:

$INT_TCOEFF0 = Q0.12.$  $INT_TCOEFF1 = Q3.9.$ ADC\_DATA\_TEMP is normalized in the 0 to 1 range. Both INT\_TCOEFF0 and INT\_TCOEFF1 are twos complement. The Qx.y format represents integer (x bits) + fraction (y bits) in twos complement format.

For example, the 14-bit ADC\_DAT\_TEMP register varies in ADC codes from 1720 to 8840 over the -40°C to +150°C range. Use the following equations to calculate the internal temperature coefficients for LIN signal frame:

| $INT\_TCOEFF1$ Floating Point = $2^{14} \div (ADC High Code - ADC Low Code)$                                                                                                                         | (2) |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| $INT\_TCOEFF0$ Floating Point = $-(ADC Low Code \div 2^{14}) \times INT\_TCOEFF1$ Floating Point                                                                                                     | (3) |

| $INT\_TCOEFF1 = $ floor (( $INT\_TCOEFF1$ $Floating$ $Point \times 511$ ) + 0.5)                                                                                                                     | (4) |

| $INT\_TCOEFF0 = $ floor (( $INT\_TCOEFF0$ $Floating$ $Point \times$ 4095) + 0.5) (                                                                                                                   | (5) |

| where (for this example):<br>$INT_TCOEFF1$ Floating Point = 2.30112359<br>$INT_TCOEFF0$ Floating Point = -0.24157303<br>$INT_TCOEFF1$ = 1176 decimal (0x498)<br>$INT_TCOEFF0$ = -989 decimal (0xC23) |     |

The EVAL-ADA4558EBZ software provides a tool for applying further examples of calculating the INT\_TCOEFF0 and INT\_TCOEFF1 values.

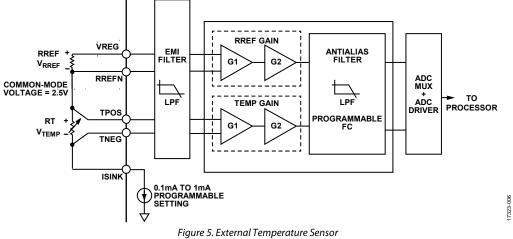

# EXTERNAL TEMPERATURE SENSOR

The ADA4558 has an external temperature sensor input to allow the temperature compensation of remote sensors. Write 1 to the TEMP\_SEL bit in EEPROM Address 13 (0x0D) to configure the ADA4558 to use the external temperature sensor value to temperature compensate for the bridge sensor.

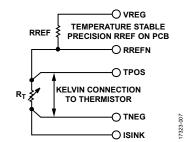

Remote RTDs are measured across the TPOS pin and the TNEG pin, as shown in Figure 5. A local reference resistor is measured in series to provide a reference temperature. The voltage across the RREF resistor ( $V_{RREF}$ ) and the voltage across the RT resistor ( $V_{TEMP}$ ) are amplified, filtered, and applied to the ADC of the IC via the on-chip multiplexer (MUX).

The ADA4558 supports the use of the platinum 100 (100  $\Omega$  at 0°C, PT100) RTD or platinum 1000 (1000  $\Omega$  at 0°C, PT1000) RTD. The external temperature sensor block is read by the ADC at a 50 kHz sample rate and then filtered through a 125 Hz bandwidth. Further filtering is described in the User Configurable Filtering section. This external temperature channel saves raw ADC data to the SYSREG Address 0x92 (ADC\_DATA\_EXTTS).

An on-chip sink current ( $I_{SINK}$ ) generates the voltages across the RTD and reference resistor. The  $I_{SINK}$  is programmed to ensure a wide signal range for the RTD over the expected temperature range. Let  $I_{SINK} = 1$  mA for PT100, and let  $I_{SINK} = 0.2$  mA for PT1000. See Table 3 for the full list of programmable sink currents available.

The  $V_{RREF}$  voltage is used in on-chip calculations to reduce the dependence on the internal bias current drift over temperature. It is critical for system accuracy that the RREF reference resistor is a precision resistor with stable temperature characteristics. Choose a location for the RREF reference resistor on the PCB that avoids heating of the RREF reference resistor caused by power dissipation in the application.

The RTD is remotely located to accurately sense the target temperature. Connect the TPOS pin and the TNEG pin to the RTD using the Kelvin method (matched local connections) to ensure maximum accuracy.

Figure 6. External Temperature Sensor Connection Guideline

As shown in Figure 5, the RREF reference resistor and RTD inputs have a programmable gain setting where the total gain is G1 × G2 for each channel. See Table 3 for the full list of programmable gain settings. Select the gain setting of G1 to maximize the signal without saturating the ADC. Select the gain setting of G2 to further maximize the signal without saturation. The recommended ADC input range is 0.1 V to  $V_{REG}$  (4 V).

Calibrate and scale the external temperature sensor input to allow the calibration routine to produce five coefficients that must be saved to the EEPROM. See the Calibration Procedure section for details of the calibration routine. The calibrated external temperature data is reported back to the application in an LIN signal frame.

| Parameter        | Description                           | Programmable Values                   |

|------------------|---------------------------------------|---------------------------------------|

| EXTTS_ISNK       | Programmable Isink                    | 3-bit binary value (3'b) 0xx = 0 mA   |

|                  |                                       | 3'b 100 = 0.1 mA                      |

|                  |                                       | 3'b 101 = 0.2 mA                      |

|                  |                                       | 3'b 110 = 0.5 mA                      |

|                  |                                       | 3'b 111 = 1 mA                        |

| EXTTS_REF_GAIN1  | Reference resistor, first stage gain  | 3'b 000 = 1 V/V                       |

|                  |                                       | 3'b 001 = 1.5 V/V                     |

|                  |                                       | 3'b 010 = 2 V/V                       |

|                  |                                       | 3'b 011 = 3 V/V                       |

|                  |                                       | 3'b 100 = 4 V/V                       |

|                  |                                       | 3'b 101 = 6 V/V                       |

|                  |                                       | 3'b 110 = 8 V/V                       |

|                  |                                       | 3'b 111 = 12 V/V                      |

| EXTTS_REF_GAIN2  | Reference resistor, second stage gain | 2-bit binary value (2'b) $00 = 1 V/V$ |

|                  |                                       | 2'b 01 = 1.5 V/V                      |

|                  |                                       | 2'b 10 = 2 V/V                        |

|                  |                                       | 2'b 11 = 3 V/V                        |

| EXTTS_TEMP_GAIN1 | RTD, first stage gain                 | 3'b 000 = 1 V/V                       |

|                  |                                       | 3'b 001 = 1.5 V/V                     |

|                  |                                       | 3'b 010 = 2 V/V                       |

|                  |                                       | 3'b 011 = 3 V/V                       |

|                  |                                       | 3'b 100 = 4 V/V                       |

|                  |                                       | 3'b 101 = 6 V/V                       |

|                  |                                       | 3'b 110 = 8 V/V                       |

|                  |                                       | 3'b 111 = 12 V/V                      |

| EXTTS_TEMP_GAIN2 | RTD, second stage gain                | 2'b 00 = 1 V/V                        |

|                  |                                       | 2'b 01 = 1.5 V/V                      |

|                  |                                       | 2'b 10 = 2 V/V                        |

|                  |                                       | 2'b 11 = 3 V/V                        |

### Table 3. External Temperature Front End Settings

# ADC OPERATION

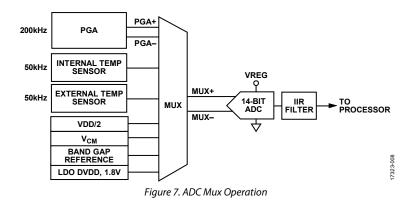

The ADA4558 features a 14-bit successive approximation register (SAR) ADC. The ADC converts the output of the PGA, the internal and external temperature sensor,  $V_{DD} \div 2$ , bridge input  $V_{CM}$ , on-chip coarse band gap voltage, internal 1.8 V analog and digital supply (DVDD), and other miscellaneous signals. The bridge sensor channel is sampled at 200 kHz, the temperature sensor is sampled at 50 kHz, and all remaining ADC time slots are allocated for self checks, fault detection, and other functions.

The ADC output for the bridge sensor is filtered through a 500 Hz cutoff digital infinite impulse response (IIR) filter in the datapath. Further filtering is described in the User Configurable Filtering section.

The differential measurement for the bridge sensor PGA Stage 1 is stored in the SYSREG Address 0x94 (ADC\_DATA\_PRES\_S1). PGA Stage 3 outputs a single-ended measurement for the bridge sensor, which is saved to the SYSREG Address 0x90 (ADC\_ DATA\_PRES). These bridge sensor registers are not subject to the digital correction algorithm. The digital correction algorithm is applied by the processor when a LIN request is received. The corrected bridge sensor measurement is sent to the system master over the LIN compliant interface

The ADC output for various channels is accessible via the LIN interface by using the user defined diagnostic frames. The ADC operates in both single-ended mode and differential mode. All channels on the ADA4558 are single-ended, apart from ADC\_DATA\_PRES\_S1, which is differential.

In single-ended mode, the 14-bit output varies between 0x0000 and 0x3FFF as the analog input moves from 0 V to  $V_{\text{REG}}$ .

In differential mode, zero differential voltage at the input corresponds to 0x2000. Table 4 shows the range of ADC\_DATA\_PRES\_S1 ADC codes.

#### Table 4. ADC\_DATA\_PRES\_S1 Code Range

| ADC_DATA_PRES_S1 Code | VPOS             | VNEG             |

|-----------------------|------------------|------------------|

| 0x0000                | 0 V              | V <sub>REG</sub> |

| 0x2000                | Vсм              | Vсм              |

| 0x3FFF                | V <sub>REG</sub> | 0 V              |

# **USER CONFIGURABLE FILTERING**

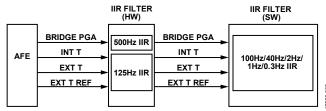

Figure 8. Hardware Filters and Configurable Software Filters for the AFE Signals

The ADA4558 has a user configurable IIR filter for each of the following ADC channels:

- PGA for the bridge sensor input

- Internal temperature (INT T)

- External temperature (EXT T)

- External temperature reference resistor (EXT T REF)

Each channel has a hardware (HW) IIR filter and a software (SW) IIR filter. In the event of a reset, the device defaults to the hardware filter where bridge sensor input has a 500 Hz, low-pass filter, while the temperature channel inputs have a 125 Hz low-pass filter. Select software IIR filters with lower cutoff frequencies using the temperature low-pass filter (LPF) and bridge low-pass filter (LPF) registers at EEPROM Address 12. The device switches to other selected filters after a settling time.

The ADA4558 implements a Chebyshev Type II fourth-order IIR filter for 100 Hz and 40 Hz pass band, and implements a first-order IIR filter for the 2 Hz, 1 Hz or 0.3 Hz pass band. The sample frequency is 4 KHz.

Write to the bridge LPF at EEPROM Address 12 (0x0C) to configure the IIR filter cutoff frequency to 500 Hz, 100 Hz, 40 Hz, 2 Hz, 1 Hz, or 0.3 Hz.

Write to the temperature LPF at EEPROM Address 12 (0x0C) to configure the IIR filter cutoff frequency for the temperature channels. Available cutoff frequencies are 125 Hz, 100 Hz, 40 Hz, 2 Hz, 1 Hz, or 0.3 Hz.

See Table 24 and Table 25 for IIR filter setting values.

# **OTP CODE STORAGE MEMORY**

The ADA4558 has one time programmable (OTP) memory to hold the program code and the Analog Devices, Inc., data stored at final test. To improve reliability, the data in the OTP memory is encoded using Hamming code. The error correction code (ECC) performs the correction of single-bit errors and detection of 2-bit errors using seven ECC bits for every 32 bits of data. This ECC ensures reliability of the memory and that any potential field failures are detectable. The OTP memory is preprogrammed. The data stored in the OTP include trims and configuration bits together with traceability data, such as wafer lot number and wafer X/Y coordinates, to provide full traceability of the silicon. The software revision identification is also encoded when the software is programmed into OTP memory.

All traceability data can be read back using the LIN commands described in the LIN Diagnostic Frames section.

# EEPROM

The ADA4558 includes EEPROM memory to store factory trim coefficients, user calibration data, manufacturing data, and end customer serialization data. The ADA4558 EEPROM is based on a charge storage technology, and uses a differential bit cell for improved retention.

To improve reliability, the data in the EEPROM memory is encoded using Hamming code. The ECC performs the correction of single-bit errors and the detection of 2-bit errors using seven ECC bits for every 32 bits of data. This ECC ensures reliability of the memory and that any potential field failures are detectable.

After the EEPROM is programmed, read back the EEPROM status register at SYSREG Address Map 0xBB to verify that the correct data has been programmed to the EEPROM. See the SYSREG Map section for more information.

Table 5 lists the ADA4558 EEPROM map. See Table 6 to Table 44 for EEPROM bit descriptions.

## Table 5. EEPROM Map

|          | [                                       |             |     |       | 1        |      |         |          |        |          | В           | t       |         |             |            |       |              |         |              |               |

|----------|-----------------------------------------|-------------|-----|-------|----------|------|---------|----------|--------|----------|-------------|---------|---------|-------------|------------|-------|--------------|---------|--------------|---------------|

| Addr     | 31                                      | 30          | 29  | 28    | 27 26    | 25   | 24      | 23 22    | 21 20  | 19 18    | -           | 15 14   | 13 12   | 2 11 10     | 98         | 7     | 6            | 5 4     | 3 2          | 1 0           |

| 31       |                                         |             |     |       |          |      |         |          | 1 1    |          | Rese        | ved     |         | 1 1         | 11         |       |              |         |              | <u> </u>      |

| 30       | Reserved FAULT_STATE[29:0]              |             |     |       |          |      |         |          |        |          |             |         |         |             |            |       |              |         |              |               |

| 29       |                                         |             |     |       |          |      |         |          |        |          |             | .T_ID1  | I       | FAULT_NU    | M1         |       | FAULT_ID     | 0       | FAULT        | _NUM0         |

| 28       |                                         | Reserved FA |     |       |          |      |         |          |        |          | FAUL        | T_ID3   | I       | FAULT_NU    | M3         |       | FAULT_ID     | 2       | FAULT        | _NUM2         |

| 27       | Function ID                             |             |     |       |          |      |         |          |        |          |             | Var     | iant ID |             |            | INT   | _TCOEFF      | 1[11:4] |              |               |

| 26       |                                         | Serial      |     |       |          |      |         |          |        |          |             | 0[31:0] |         |             |            |       |              |         |              |               |

| 25       | Reserved LINPID8[7:0]                   |             |     |       |          |      |         |          |        |          |             |         |         |             | Supplie    | er ID |              |         |              |               |

| 24       |                                         |             | LIN | IPID3 | 5[7:0]   |      |         |          |        | PID2[7:0 | ]           |         | LINP    | ID1[7:0]    |            |       |              | Reserve |              |               |

| 23       |                                         |             |     |       |          |      |         |          | Reser  | ved      |             |         |         |             |            |       | INT          | _TCOEFF | 0[11:4]      |               |

| 22       |                                         |             |     |       |          |      |         |          |        |          | Rese        |         |         |             |            |       |              |         |              |               |

| 21       |                                         |             |     |       |          |      |         |          |        |          | Rese        |         |         |             |            |       |              |         |              |               |

| 20       |                                         |             |     |       |          |      |         |          |        |          | Rese        |         |         |             |            |       |              |         |              |               |

| 19<br>18 |                                         |             |     |       |          |      |         |          | Reser  | (a.d.    | Rese        | ved     |         |             |            | 1     | BS SV        | M.      | DC           | HW            |

| 17       |                                         |             |     |       |          |      |         |          | neser  | veu      | Poro        | avod    |         |             |            |       | D3_3V        | v       | D3           |               |

| 16       | Reserved<br>Reserved                    |             |     |       |          |      |         |          |        |          |             |         |         |             |            |       |              |         |              |               |

| 15       | FAULT_LOG_EN                            |             |     |       |          |      |         |          |        |          |             |         |         |             |            |       |              |         |              |               |

| 14       | FAULT_EN                                |             |     |       |          |      |         |          |        |          |             |         |         |             |            |       |              |         |              |               |

| 13       |                                         |             |     | NAD   | )        |      |         |          |        | INAD     |             |         | EMP CC  | DEFF_K [10: | 3]         | IDLE  | Reserved     | TEM- TE | MP           | LIN           |

|          |                                         |             |     |       | -        |      |         |          |        |          |             | -       |         |             | -,         | SLP   |              |         | DEFF_K [2:0] |               |

| 12       | TE                                      | MP_LP       | F   | Bri   | dge LPF  | R    | Reserve | d        |        | NORN     | AL_FACTOR   |         |         | EXTTS_      | EXT        |       | EXTTS        |         | (TTS_REF_    | EXTTS_        |

|          |                                         |             |     |       |          |      |         |          |        |          |             |         |         | ISNK        | TEM<br>GAI |       | TEMP<br>GAIN |         | GAIN1        | REF_<br>GAIN2 |

| 11       | PGA                                     | PGA_        |     | PGA   | GAIN[4:0 | )]   | Rese-   | INT T    | COEFF1 |          | FAULT       |         |         |             |            |       | FF2[15:0]    |         |              | 67 1112       |

|          | ADD_                                    | REVE-       |     |       |          |      | rved    | _        | 3:0]   |          | LERANCE_    |         |         |             |            |       |              |         |              |               |

|          | PULL-                                   |             |     |       |          |      |         |          |        |          | NUM         |         |         |             |            |       |              |         |              |               |

|          | 0P_<br>150                              | UP_ IN      |     |       |          |      |         |          |        |          |             |         |         |             |            |       |              |         |              |               |

| 10       |                                         |             |     |       | т        | COR  | r coef  | F1[15:0  | 0      |          |             |         |         |             | TCOR       | R COE | FF0[15:0]    |         |              |               |

| 9        |                                         | Reserv      | /ed |       |          |      | VCM_T   |          | _      | BRO      | G_VOS_TRIM1 |         |         | BRG_VOS     | _TRIM2     | _     |              | PGA_    | DAC_5        |               |

| 8        | CC                                      | DRR_        | CO  | RR_   | CORR_    | C    | ORR_    | CORR_    | CORR_  | CORR_    | Reserved    | INT_TC  | OEFF0   |             |            | ADC   | _RREF_IN\    | /_CONST |              |               |

|          |                                         | EFF14       |     | FF13  |          |      |         |          |        |          |             | [3      | :0]     |             |            |       |              |         |              |               |

|          | [1:0] [1:0] [1:0] 0 [1:0] F8[1:0] [1:0] |             |     |       |          |      |         |          |        |          |             |         |         |             |            |       |              |         |              |               |

| 7        |                                         |             | 1   |       | C        | ORR  | COEFF   | 14[17:2  | .]     | 1        | 1           | CORR    | CORR    | CORR        | CORR       | CORR  | COEFF3       | CORR    | CORR         | CORR          |

|          |                                         |             |     |       | -        |      |         |          | -      |          |             | COEFF7  | COEFF   | 6 COEFF5    | COEFF4     |       | [1:0]        | COEFF   | 2 COEFF1     | COEFF         |

|          |                                         |             |     |       |          |      |         |          | [1:0]  | [1:0]    | [1:0]       | [1:0]   |         |             | [1:0]      | [1:0] | [1:0]        |         |              |               |

| 6        | CORR_COEFF13[17:2]                      |             |     |       |          |      |         |          |        |          |             |         | _       | F12[17:2]   |            |       |              |         |              |               |

| 5        | CORR_COEFF11[17:2]                      |             |     |       |          |      |         |          |        |          |             |         |         |             | F10[17:2]  |       |              |         |              |               |

| 4        |                                         |             |     |       |          |      |         | F9[17:2] |        |          |             |         |         |             |            | _     | F8[17:2]     |         |              |               |

| 3<br>2   |                                         |             |     |       |          |      |         | F7[17:2] |        |          |             |         |         |             |            |       | F6[17:2]     |         |              |               |

| 2        |                                         |             |     |       |          |      | _       | F5[17:2] |        |          |             |         |         |             |            | _     | F4[17:2]     |         |              |               |

|          |                                         |             |     |       |          |      |         | F3[17:2] |        |          |             |         |         |             |            |       | F2[17:2]     |         |              |               |

| 0        |                                         |             |     |       | (        | LOKK |         | F1[17:2] |        |          |             |         |         |             | COR        | LOF   | F0[17:2]     |         |              |               |

# **EEPROM BIT DESCRIPTIONS**

## Table 6. EEPROM Address 0

| Bit No. | Bit Name          | Description                                        |  |  |  |  |

|---------|-------------------|----------------------------------------------------|--|--|--|--|

| [15:0]  | CORR_COEFF0[17:2] | Bridge Sensor Correction Coefficient 0, Bits[17:2] |  |  |  |  |

| [31:16] | CORR_COEFF1[17:2] | Bridge Sensor Correction Coefficient 1, Bits[17:2] |  |  |  |  |

#### Table 7. EEPROM Address 1

| Bit No. | Bit Name          | Description                                        |

|---------|-------------------|----------------------------------------------------|

| [15:0]  | CORR_COEFF2[17:2] | Bridge Sensor Correction Coefficient 2, Bits[17:2] |

| [31:16] | CORR_COEFF3[17:2] | Bridge Sensor Correction Coefficient 3, Bits[17:2] |

### Table 8. EEPROM Address 2

| Bit No. | Bit Name Description |                                                    |  |  |  |

|---------|----------------------|----------------------------------------------------|--|--|--|

| [15:0]  | CORR_COEFF4[17:2]    | Bridge Sensor Correction Coefficient 4, Bits[17:2] |  |  |  |

| [31:16] | CORR_COEFF5[17:2]    | Bridge Sensor Correction Coefficient 5, Bits[17:2] |  |  |  |

### Table 9. EEPROM Address 3

| Bit No. | Bit Name          | Description                                        |

|---------|-------------------|----------------------------------------------------|

| [15:0]  | CORR_COEFF6[17:2] | Bridge Sensor Correction Coefficient 6, Bits[17:2] |

| [31:16] | CORR_COEFF7[17:2] | Bridge Sensor Correction Coefficient 7, Bits[17:2] |

#### Table 10. EEPROM Address 4

| Bit No. | Bit Name          | Description                                        |

|---------|-------------------|----------------------------------------------------|

| [15:0]  | CORR_COEFF8[17:2] | Bridge Sensor Correction Coefficient 8, Bits[17:2] |

| [31:16] | CORR_COEFF9[17:2] | Bridge Sensor Correction Coefficient 9, Bits[17:2] |

### Table 11. EEPROM Address 5

| Bit No. | Bit Name           | Description                                         |

|---------|--------------------|-----------------------------------------------------|

| [15:0]  | CORR_COEFF10[17:2] | Bridge Sensor Correction Coefficient 10, Bits[17:2] |

| [31:16] | CORR_COEFF11[17:2] | Bridge Sensor Correction Coefficient 11, Bits[17:2] |

## Table 12. EEPROM Address 6

| Bit No. | Bit Name           | Description                                         |

|---------|--------------------|-----------------------------------------------------|

| [15:0]  | CORR_COEFF12[17:2] | Bridge Sensor Correction Coefficient 12, Bits[17:2] |

| [31:16] | CORR_COEFF13[17:2] | Bridge Sensor Correction Coefficient 13, Bits[17:2] |

#### Table 13. EEPROM Address 7

| Bit No. | Bit Name           | Description                                         |

|---------|--------------------|-----------------------------------------------------|

| [1:0]   | CORR_COEFF0[1:0]   | Bridge Sensor Correction Coefficient 0, Bits[1:0]   |

| [3:2]   | CORR_COEFF1[1:0]   | Bridge Sensor Correction Coefficient 1, Bits[1:0]   |

| [5:4]   | CORR_COEFF2[1:0]   | Bridge Sensor Correction Coefficient 2, Bits[1:0]   |

| [7:6]   | CORR_COEFF3[1:0]   | Bridge Sensor Correction Coefficient 3, Bits[1:0]   |

| [9:8]   | CORR_COEFF4[1:0]   | Bridge Sensor Correction Coefficient 4, Bits[1:0]   |

| [11:10] | CORR_COEFF5[1:0]   | Bridge Sensor Correction Coefficient 5, Bits[1:0]   |

| [13:12] | CORR_COEFF6[1:0]   | Bridge Sensor Correction Coefficient 6, Bits[1:0]   |

| [15:14] | CORR_COEFF7[1:0]   | Bridge Sensor Correction Coefficient 7, Bits[1:0]   |

| [31:16] | CORR_COEFF14[17:2] | Bridge Sensor Correction Coefficient 14, Bits[17:2] |

# Table 14. EEPROM Address 8

| Bit No. | Bit Name           | Description                                                                                       |

|---------|--------------------|---------------------------------------------------------------------------------------------------|

| [11:0]  | ADC_RREF_INV_CONST | Refer to the external temperature sensor calibration routine in the Calibration Procedure section |

| [15:12] | INT_TCOEFF0[3:0]   | Internal Temperature Sensor Coefficient 0, Bits[3:0]                                              |

| [17:16] | Reserved           | Reserved                                                                                          |

| [19:18] | CORR_COEFF8[1:0]   | Bridge Sensor Correction Coefficient 8, Bits[1:0]                                                 |

| [21:20] | CORR_COEFF9[1:0]   | Bridge Sensor Correction Coefficient 9, Bits[1:0]                                                 |

| [23:22] | CORR_COEFF10[1:0]  | Bridge Sensor Correction Coefficient 10, Bits[1:0]                                                |

| [25:24] | CORR_COEFF11[1:0]  | Bridge Sensor Correction Coefficient 11, Bits[1:0]                                                |

| [27:26] | CORR_COEFF12[1:0]  | Bridge Sensor Correction Coefficient 12, Bits[1:0]                                                |

| [29:28] | CORR_COEFF13[1:0]  | Bridge Sensor Correction Coefficient 13, Bits[1:0]                                                |

| [31:30] | CORR_COEFF14[1:0]  | Bridge Sensor Correction Coefficient 14, Bits[1:0]                                                |

# Table 15. EEPROM Address 9

| Bit No. | Bit Name      | Description                                                          |

|---------|---------------|----------------------------------------------------------------------|

| [6:0]   | PGA_DAC_5     | Third stage bridge offset correction DAC                             |

| [13:7]  | BRG_VOS_TRIM2 | Final PGA Offset 2                                                   |

| [20:14] | BRG_VOS_TRIM1 | Final PGA Offset 1                                                   |

| [27:21] | BRG_VCM_TRIM  | Final common-mode trim value (see the Calibration Procedure section) |

| [31:28] | Reserved      | Reserved                                                             |

# Table 16. EEPROM Address 10

| Bit No. | Bit Name           | Description                                          |  |

|---------|--------------------|------------------------------------------------------|--|

| [15:0]  | TCORR_COEFF0[15:0] | External Temperature Sensor Correction Coefficient 0 |  |

| [31:16] | TCORR_COEFF1[15:0] | External Temperature Sensor Correction Coefficient 1 |  |

# Table 17. EEPROM Address 11

| Bit No. | Bit Name            | Description                                                                                                              |

|---------|---------------------|--------------------------------------------------------------------------------------------------------------------------|

| [15:0]  | TCORR_COEFF2[15:0]  | External Temperature Sensor Correction Coefficient 2                                                                     |

| [19:16] | FAULT_TOLERANCE_NUM | Sets the number of consecutive faults, N, that must occur before the fault is flagged to the system, or logged to EEPROM |

| [23:20] | INT_TCOEFF1[3:0]    | Internal Temperature Sensor Coefficient 1, Bits[13:0]                                                                    |

| 24      | Reserved            | Reserved                                                                                                                 |

| [29:25] | PGA_GAIN[4:0]       | Selects the PGA gain (see Table 1 for PGA gain settings)                                                                 |

| 30      | PGA_REVERSE_IN      | Enable to reverses the PGA input                                                                                         |

|         |                     | 0 = PGA input normal                                                                                                     |

| _       |                     | 1 = PGA input reversed                                                                                                   |

| 31      | PGA_ADD_PULUP_150   | Additional PGA pull-down current to detect open bridge                                                                   |

|         |                     | 0 = 300 nA                                                                                                               |

|         |                     | 1 = 450 nA                                                                                                               |

## Table 18. EEPROM Address 12

| Bit No. | Bit Name         | Description                                                                      |

|---------|------------------|----------------------------------------------------------------------------------|

| [1:0]   | EXTTS_REF_GAIN2  | External temperature sensor reference resistor, second stage gain (see Table 19) |

| [4:2]   | EXTTS_REF_GAIN1  | External temperature sensor reference resistor, first stage gain (see Table 20)  |

| [6:5]   | EXTTS_TEMP_GAIN2 | External temperature sensor RTD, second stage gain (see Table 21)                |

| [9:7]   | EXTTS_TEMP_GAIN1 | External temperature sensor RTD, first stage gain (see Table 22)                 |

| [12:10] | EXTTS_ISNK       | External temperature sensor programmable I <sub>SINK</sub> (see Table 23)        |

| [22:13] | NORMAL_FACTOR    | See the Calibration Routine for External Temperature Sensor section              |

| [25:23] | Reserved         | Reserved                                                                         |

| [28:26] | Bridge LPF       | Bridge sensor low-pass filter configuration (see Table 24)                       |

| [31:29] | TEMP_LPF         | Temperature low-pass filter configuration (see Table 25)                         |

UG-1487

# UG-1487

# ADA4558 Hardware Reference Manual

| Table 19. External Tem | perature Sensor Reference | e Resistor Second Sta | ge Gain Settings |

|------------------------|---------------------------|-----------------------|------------------|

|                        |                           |                       |                  |

| EXTTS_REF_GAIN2 | Second Stage Gain |

|-----------------|-------------------|

| 00              | 1                 |

| 01              | 1.5               |

| 10              | 2.0               |

| 11              | 3.0               |

### Table 20. External Temperature Sensor Reference Resistor First Stage Gain Settings

| EXTTS_REF_GAIN1 | First Stage Gain |

|-----------------|------------------|

| 000             | 1                |

| 001             | 1.5              |

| 010             | 2.0              |

| 011             | 3.0              |

| 100             | 4.0              |

| 101             | 6.0              |

| 110             | 8.0              |

| 111             | 12.0             |

#### Table 21. External Temperature Sensor RTD Second Stage Gain Settings

| EXTTS_TEMP_GAIN2 | Second Stage Gain |

|------------------|-------------------|

| 00               | 1                 |

| 01               | 1.5               |

| 10               | 2.0               |

| 11               | 3.0               |

# Table 22. External Temperature Sensor RTD First Stage Gain Settings

| EXTTS_TEMP_GAIN1 | First Stage Gain |

|------------------|------------------|

| 000              | 1                |

| 001              | 1.5              |

| 010              | 2.0              |

| 011              | 3.0              |

| 100              | 4.0              |

| 101              | 6.0              |

| 110              | 8.0              |

| 111              | 12.0             |

## Table 23. External Temperature Sensor Programmable Sink Current Settings

| EXTTS_ISNK | Sink Current (mA) |

|------------|-------------------|

| 0xx        | 0                 |

| 100        | 0.1               |

| 101        | 0.2               |

| 110        | 0.5               |

| 111        | 1.0               |

#### Table 24. Bridge Sensor Low-Pass Filter Settings

| Bridge LPF | Filter Bandwidth (Hz) |

|------------|-----------------------|

| 000        | 500                   |

| 001        | 100                   |

| 010        | 40                    |

| 011        | 2                     |

| 100        | 1                     |

| 101        | 0.3                   |

| 110        | 500                   |

| 111        | 500                   |

| TEMP_LPF | Filter Bandwidth (Hz) |

|----------|-----------------------|

| 000      | 125                   |

| 001      | 100                   |

| 010      | 40                    |

| 011      | 2                     |

| 100      | 1                     |

| 101      | 0.3                   |

| 110      | 125                   |

| 111      | 125                   |

### Table 25. Temperature Low-Pass Filter Settings

| Bit<br>No. | Bit Name                            | Description                                                                                                   |  |

|------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------|--|

| [1:0]      | LINCONFIG Select LIN configuration. |                                                                                                               |  |

|            |                                     | 00 = LIN 2.1 (default).                                                                                       |  |

|            |                                     | 01 = LIN 2.0.                                                                                                 |  |

|            |                                     | 10 = LIN 1.3.                                                                                                 |  |

|            |                                     | 11 = reserved.                                                                                                |  |

| [4:2]      | TEMP_COEFF_K[2:0]                   | External temperature compensation constant, K.                                                                |  |

| 5          | TEMP_SEL                            | FEMP_SEL         Select internal or external temperature sensor for calibration of the bridge sensor channel. |  |

|            |                                     | 0 = internal temperature sensor for calibration of the bridge sensor channel.                                 |  |

|            |                                     | 1 = external temperature sensor for calibration of the bridge sensor channel.                                 |  |

| 6          | Reserved                            | Not Available                                                                                                 |  |

| 7          | IDLE_SLP                            | Enable or disable auto sleep mode.                                                                            |  |

|            |                                     | 0 = enable auto sleep mode.                                                                                   |  |

|            |                                     | 1 = disable auto sleep mode.                                                                                  |  |

| [15:8]     | TEMP_COEFF_K[10:3]                  | External temperature compensation constant, K.                                                                |  |

| 23:16]     | INAD                                | Initial node address (INAD) for slave node.                                                                   |  |

| 31:24]     | NAD                                 | Node address (NAD) for slave node.                                                                            |  |

## Table 27. EEPROM Address 14

| Bit No. | Name     | Description                                                                        |  |

|---------|----------|------------------------------------------------------------------------------------|--|

| [31:0]  | FAULT EN | Enable faults. Selects which faults are enabled based on the fault ID code.        |  |

|         |          | Bit $n = 0$ : fault detection is disabled, where n is the fault ID (see Table 82). |  |

|         |          | Bit $n = 1$ : fault detection enabled, where n is the fault ID (see Table 82).     |  |

#### Table 28. EEPROM Address 15

| Bit No. | Bit Name     | Description                                                                                                                                       |

|---------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:0]  | FAULT_LOG_EN | Enable fault logging. Select which faults are logged to the EEPROM based on the fault identification code. See the Calibration Procedure section. |

|         |              | Bit $n = 0$ : fault logging disabled, where n is the fault identification.                                                                        |

|         |              | Bit $n = 1$ : fault logging enabled, where n is the fault identification.                                                                         |

### Table 29. EEPROM Address 16

| Bit No. | Name     | Description |

|---------|----------|-------------|

| [31:0]  | Reserved | Reserved    |

# Table 30. EEPROM Address 17

| Bit No. | Bit Name | Description |

|---------|----------|-------------|

| [31:0]  | Reserved | Reserved    |

### Table 31. EEPROM Address 18

| Bit No. | Bit Name | Description                                                                                 |

|---------|----------|---------------------------------------------------------------------------------------------|

| [3:0]   | BS_HW    | User defined version number for bridge sensor hardware, value reported in LIN signal frame. |

| [7:4]   | BS_SW    | User defined version number for bridge sensor software, value reported in LIN signal frame. |

| [31:8]  | Reserved | Reserved                                                                                    |

#### Table 32. EEPROM Address 19

| Bit No. | Bit Name | Description |

|---------|----------|-------------|

| [31:0]  | Reserved | Reserved    |

#### Table 33. EEPROM Address 20

| [31:0] Reserved Reserved | Bit No. | Bit Name | Description |

|--------------------------|---------|----------|-------------|

|                          | [31:0]  | Reserved | Reserved    |

#### Table 34. EEPROM Address 21

| Bit No. | Bit Name | Description |

|---------|----------|-------------|

| [31:0]  | Reserved | Reserved    |

| [31:8]  | Reserved | Reserved    |

### Table 35. EEPROM Address 22

| Bit No. | Bit Name | Description |

|---------|----------|-------------|

| [31:0]  | Reserved | Reserved    |

#### Table 36. EEPROM Address 23

| Bit No. | Bit Name          | Description                               |

|---------|-------------------|-------------------------------------------|

| [7:0]   | INT_TCOEFF0[11:4] | Internal Temperature Sensor Coefficient 0 |

| [31:8]  | Reserved          | Reserved                                  |

#### Table 37. EEPROM Address 24

| Bit No. | Bit Name     | Description                                                    |

|---------|--------------|----------------------------------------------------------------|

| [7:0]   | Reserved]    | Reserved.                                                      |

| [15:8]  | LINPID1[7:0] | LIN Protected Identifier 1. If unused, set these bits to 0x40. |

| [23:16] | LINPID2[7:0] | LIN Protected Identifier 2. If unused, set these bits to 0x40. |

| [31:24] | LINPID3[7:0] | LIN Protected Identifier 3. If unused, set these bits to 0x40. |

### Table 38. EEPROM Address 25

| Bit No. | Bit Name     | Description            |

|---------|--------------|------------------------|

| [15:0]  | Supplier ID  | LIN supplier ID        |

| [16:23] | LINPID8[7:0] | Protected Identifier 8 |

| [24:31] | Reserved     | Reserved               |

#### Table 39. EEPROM Address 26

| Bit No. | Bit Name  | Description                           |

|---------|-----------|---------------------------------------|

| [31:0]  | Serial ID | Customer specific identification data |

## Table 40. EEPROM Address 27

| Bit No. | Bit Name          | Description                                                           |  |

|---------|-------------------|-----------------------------------------------------------------------|--|

| [7:0]   | INT_TCOEFF1[11:4] | Internal Temperature Sensor Coefficient 0                             |  |

| [15:8]  | Variant ID        | LIN variant ID defined in LIN Version 2.0 to the current LIN version  |  |

| [31:16] | Function ID       | LIN function ID defined in LIN Version 2.0 to the current LIN version |  |

# Table 41. EEPROM Address 28

| Bit No. | Bit Name   | Description                                                                                 |  |

|---------|------------|---------------------------------------------------------------------------------------------|--|

| [3:0]   | FAULT_NUM2 | Number of occurrences of the third fault (among the enabled faults) detected by the device  |  |

| [8:4]   | FAULT_ID2  | ID of the third fault (among the enabled faults) detected by the device                     |  |

| [12:9]  | FAULT_NUM3 | Number of occurrences of the fourth fault (among the enabled faults) detected by the device |  |

| [17:13] | FAULT_ID3  | ID of the fourth fault (among the enabled faults) detected by the device                    |  |

| [31:18] | Reserved   | Reserved                                                                                    |  |

# Table 42. EEPROM Address 29

| Bit No. | Bit Name   | Description                                                                                 |

|---------|------------|---------------------------------------------------------------------------------------------|

| [3:0]   | FAULT_NUM0 | Number of occurrences of the first fault (among the enabled faults) detected by the device  |

| [8:4]   | FAULT_ID0  | ID of the first fault (among the enabled faults) detected by the device                     |

| [12:9]  | FAULT_NUM1 | Number of occurrences of the second fault (among the enabled faults) detected by the device |

| [17:13] | FAULT_ID1  | ID of the second fault (among the enabled faults) detected by the device                    |

| [31:18] | Reserved   | Reserved                                                                                    |

# Table 43. EEPROM Address 30

| Bit No. | Bit Name          | Description                               |

|---------|-------------------|-------------------------------------------|

| [29:0]  | FAULT_STATE[29:0] | Indicates the state of the enabled faults |

| [31:30] | Reserved          | Reserved                                  |

# Table 44. EEPROM Address 31

| Bit No. | Bit Name | Description |

|---------|----------|-------------|

| [31:0]  | Reserved | Reserved    |

# **EEPROM CACHING**

EEPROM values are cached either during startup or periodically. If the value is not periodically cached, the change in value using the write EEPROM LIN user defined diagnostic frame does not affect the system behavior. These values update into the system only during power-up (power-on reset).

# Table 45. EEPROM Map with Behavior During EEPROM Caching

| EEPROM Variable Name                                        | Caching Behavior               |

|-------------------------------------------------------------|--------------------------------|

| TEMP_SEL                                                    | Cached during normal operation |

| BRG_VCM_TRIM                                                | Cached during normal operation |

| BRG_VOS_TRIM1                                               | Cached during normal operation |

| BRG_VOS_TRIM2                                               | Cached during normal operation |

| PGA_DAC_5                                                   | Cached during normal operation |

| TCORR_COEFF0 to TCORR_COEFF2                                | Cached during normal operation |

| CORR_COEFF0 to CORR_COEFF14                                 | Cached during normal operation |

| PGA_GAIN                                                    | Cached during normal operation |

| LINCONFIG                                                   | Cached at power-up only        |

| NAD                                                         | Cached at power-up only        |

| INAD                                                        | Cached at power-up only        |

| LINPID1 to LINPID3, and LINPID8 (see Table 37 and Table 38) | Cached at power-up only        |

| Supplier ID                                                 | Cached at power-up only        |

| Serial ID                                                   | Cached at power-up only        |

| Function ID                                                 | Cached at power-up only        |

| Variant ID                                                  | Cached at power-up only        |

| IDLE_SLP                                                    | Cached at power-up only        |

| FAULT_STATE                                                 | Cached at power-up only        |

| FAULT_ID0 to FAULT_ID3                                      | Cached at power-up only        |

| FAULT_NUM0 to FAULT_NUM3                                    | Cached at power-up only        |

| TEMP_COEFF_K                                                | Cached during normal operation |

# LIN INTERFACE

Figure 10. Byte Field Structure

The ADA4558 incorporates a 12 V LIN physical transceiver and LIN protocol stack. The ADA4558 supports LIN 1.3, LIN 2.0, and LIN 2.1 compatibility modes. Select the correct LIN compatibility mode using the LINCONFIG bits at EEPROM Address 13. See Table 26 for setting values.

The device operates as an LIN slave device where it replies to a header frame from the LIN master. The ADA4558 response frame supports single, unconditional frames that allow readings of the measurements, diagnostics, and programming of the EEPROM.

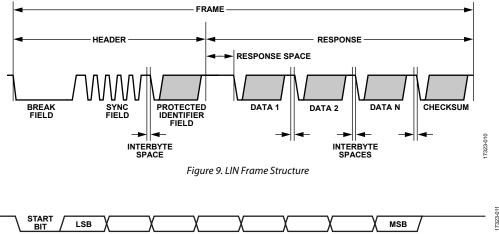

Figure 9 shows the LIN frame structure consisting of a header (from the LIN master) and response (from the ADA4558).

The header frame generated by the master node is constructed of the following:

- Break Field: wakes the ADA4558 from sleep mode and indicate the start of a new frame.

- Sync Field: a byte field with the data value of 0x55. The sync field is used to define the baud rate where the ADA4558 monitors the bit transition timing.

- Interbyte Space: the time between the end of the stop bit of the preceding field and the start bit of the following byte.

- Protected Identifier (PID) Field: requests from the LIN master. The PID carries the frame ID and the parity bits. The PID is split into values with an ID of 0 to 59 (0x0B) that are signal carrying frames, and values with an ID of 60 (0x3C) or 61 (0x3D) that carry diagnostic and configuration data.

The response frame from the ADA4558 is defined by the header PID field value. The data and checksum fields are transmitted as serial bytes, as shown in Figure 10, where each field transmission contains a dominant start bit, 8 data bits, and a recessive stop bit. The response frame shown in Figure 9 is constructed of the following:

- Response Space: the bus idle time between the header field and the response field.

- Byte Fields: the corresponding data related to the PID field. The LSB is the first bit sent and the MSB is the last bit sent (little endian), as shown in Figure 10.

- Checksum: calculate the checksum by adding each byte value, as well as any carry over to the 8-bit result. The result is then inverted. Supported checksums include classic checksum, where all data bytes are used for calculation, and enhanced checksum, where all data bytes and PID are used for calculation. The master node manages the use of either classic or enhanced checksum.

## Table 46. Checksum Description

| Checksum Model | LIN Compatibility Mode                     |

|----------------|--------------------------------------------|

| Classic        | LIN 1.3, and Frame Identifier 60 (0x3C) to |

|                | Frame Identifier 61 (0x3D)                 |

| Enhanced       | LIN 2.0, LIN 2.1, and LIN 2.2              |

# LIN INITIALIZATIONS

The following EEPROM data is used to initialize the LIN:

- PID values (EEPROM Address 24 and 25)

- Idle sleep mode (EEPROM Address 13)

- Node address for diagnostic (NAD) and initial NAD (INAD) (EEPROM Address 13)

- LIN compatibility mode (EEPROM Address 13)

- Product identification, supplier ID, variant ID and function ID (EEPROM Address 25 and Address 27)

# **FRAME TYPES**

The ADA4558 supports LIN signal frames and LIN diagnostic frames.

LIN signal frames always carry signals (data). An LIN master initiates a signal frame by sending a PID.

LIN diagnostic frames always carry diagnostic data, and can be used to configure the ADA4558 or read memories.

## LIN Signal Frame

The ADA4558 supports the signal frames shown in Table 51. Table 47 shows the definitions of the signal frame fields. The signal frames transmit calibrated bridge sensor measurements, internal temperature, external temperature data, and fault handling data. Each signal frame has a unique PID field that must be configured in the EEPROM at Address 24 and Address 25. Unused PIDs should be assigned a value of 0x40.

#### Table 47. Signal Frame Descriptions

| Signal Name        | Description                                                                                                                                   |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| BRIDGE_SENSOR_11   | The 11 MSBs of the 12-bit calibrated bridge output                                                                                            |

| BRIDGE_SENSOR_12   | 12-bit calibrated bridge output                                                                                                               |

| TEMPERATURE_9      | The 9 MSBs of the 12-bit internal<br>temperature sensor output                                                                                |

| TEMPERATURE_12     | 12 bits of internal temperature sensor output                                                                                                 |

| EXT_TEMPERATURE_12 | External temperature sensor output                                                                                                            |

| BS_SENSORERROR     | Available only in LIN-U3, for more information, see Table 83                                                                                  |

| BS_GLOBALFAULT     | Available in LIN-U1 to LIN-U2, for<br>more information, see Table 83                                                                          |

| BS_CHECKSUMERROR   | Sets when the checksum of the<br>frame is incorrect, caused by a<br>corrupted frame or using the wrong<br>checksum model in the frame         |

| BS_RESPONSEERROR   | Sets when an error in the frame response occurs                                                                                               |

| BS_BITERROR        | Sets when the bit error is reported                                                                                                           |

| ΤΝΟΤΟ              | Fault flag bit for incomplete IIR filter<br>settling during power-up (see the<br>Fault Handling, Diagnostics, and<br>Logging Feature section) |

| HW                 | Indicates the 4-bit value in the<br>EEPROM Address 18 named BS_HW                                                                             |

| SW                 | Indicates the 4-bit value in the<br>EEPROM Address 18 named BS_SW                                                                             |

| SLFCHK_INIT        | Allows the subordinate node to perform a power-up check during normal operation when set to 1                                                 |

| Unused             | All unused PIDs are set to 0x40                                                                                                               |

# Table 48. READ\_P12\_T12\_STATUS (LIN-U1) Frame

| Byte Field | Bits    | Description            |

|------------|---------|------------------------|

| PID        | No bits | LINPID1                |

| DATA0      | [7:0]   | BRIDGE_SENSOR_12[7:0]  |

| DATA1      | [3:0]   | BRIDGE_SENSOR_12[11:8] |

|            | [7:4]   | Unused                 |

| DATA2      | [7:0]   | TEMPERATURE_12[7:0]    |

| DATA3      | [3:0]   | TEMPERATURE_12[11:8]   |

|            | 4       | BS_GLOBALFAULT         |

|            | 5       | BS_CHECKSUMERROR       |

|            | 6       | BS_RESPONSEERROR       |

|            | 7       | TNCTOC                 |

# Table 49. READ\_P12\_ET12\_T12\_STATUS (LIN-U2) Frame

| Byte Field | Bits    | Description              |

|------------|---------|--------------------------|

| PID        | No bits | LINPID2                  |

| DATA0      | [7:0]   | BRIDGE_SENSOR_12[7:0]    |

| DATA1      | [3:0]   | BRIDGE_SENSOR_12[11:8]   |

|            | [7:4]   | EXT_TEMPERATURE_12[3:0]  |

| DATA2      | [7:0]   | EXT_TEMPERATURE_12[11:4] |

| DATA3      | [7:0]   | TEMPERATURE_12[7:0]      |

| DATA4      | [3:0]   | TEMPERATURE_12[11:8]     |

|            | 4       | BS_GLOBALFAULT           |

|            | 5       | BS_CHECKSUMERROR         |

|            | 6       | BS_RESPONSEERROR         |

|            | 7       | TNCTOC                   |

## Table 50. READ\_P11\_T9\_STATUS\_HW\_SW (LIN-U3) Frame

| Byte Field | Bits    | Description            |  |  |

|------------|---------|------------------------|--|--|

| PID        | No bits | LINPID3                |  |  |

| DATA0      | [7:0]   | BRIDGE_SENSOR_11[7:0]  |  |  |

| DATA1      | [2:0]   | BRIDGE_SENSOR_11[10:8] |  |  |

|            | [7:3]   | TEMPERATURE_9[4:0]     |  |  |

| DATA2      | [3:0]   | TEMPERATURE_9[8:5]     |  |  |

|            | 4       | BS_SENSORERROR         |  |  |

|            | 5       | BS_RESPONSEERROR       |  |  |

|            | 6       | BS_CHECKSUMERROR       |  |  |

|            | 7       | BS_BITERROR            |  |  |

| DATA3      | [3:0]   | HW[3:0]                |  |  |

|            | [7:4]   | SW[3:0]                |  |  |

|            |         |                        |  |  |

# Table 51. SELFCHECK (LIN-U8) Frame

| Byte Field     | Bits    | Description |  |  |  |  |

|----------------|---------|-------------|--|--|--|--|

| PID            | No bits | LINPID8     |  |  |  |  |

| DATA0          | 0       | SLFCHK_INIT |  |  |  |  |

|                | [7:1]   | Unused      |  |  |  |  |

| DATA1 to DATA4 | No bits | Unused      |  |  |  |  |

|                |         |             |  |  |  |  |

## LIN Diagnostic Frames

The LIN diagnostic frame is used to configure the ADA4558 and to read status of the device. The LIN master issues the diagnostic command request. Table 52 shows this LIN frame format. Table 53 shows the ADA4558 response frame format. The frames are a fixed length of eight data bytes and are sent after the LIN header frame. Diagnostic frames always use the classic checksum. The classic checksum is transited at the end of the diagnostic frame. The PID value in the LIN header frame indicates which type of diagnostic frame is in use. A PID value of 0x3C indicates a master request frame. A PID value of 0x7D indicates the ADA4558 response frame. Table 54 shows a description of each byte field in the diagnostic frame. Table 55 shows the LIN diagnostic frames supported by the ADA4558.

#### Table 52. Diagnostic Frame Master Request PDU (Packet Data Unit) Response Field

| ſ | NAD PCI SID DATA1 DATA2 DATA3 DATA4 DATA5                              |  |  |  |  |  |  |  |  |  |

|---|------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 7 | Table 53. Diagnostic Frame Slave Response PDU Response Field           |  |  |  |  |  |  |  |  |  |

| r | NAD     PCI     RSID     DATA1     DATA2     DATA3     DATA4     DATA5 |  |  |  |  |  |  |  |  |  |

Table 54. Diagnostic Frame Response Field

| PDU Byte       | Description                                                                                | Description                                                         |                                                                                                                  |  |  |  |  |  |

|----------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAD            | Node add                                                                                   | Node address of a logical slave node.                               |                                                                                                                  |  |  |  |  |  |

| PCI            | Protocol c                                                                                 | ontrol information                                                  | n (PCI), flow control information.                                                                               |  |  |  |  |  |