# Low Power Analog to Digital Converter

**ADC1121**

FEATURES

12 Bit Resolution and Accuracy

CMOS Compatible

Very Low Power Consumption

Exceptional Power Supply Rejection

Can Operate From Single Battery

No Missing Codes, 0 to +70°C

GENERAL DESCRIPTION

The CMOS compatible ADC1121 requires less than 6 microjoules of energy to perform a complete, 12 bit analog-to-digital conversion. In addition, it has ±0.01% relative accuracy, a 70µs maximum conversion time, a maximum power consumption of 100mW for continuous conversions, and no missing codes from 0 to +70°C. Power may be supplied by a single +12V to +15V source, but the logic portions of the converter may also be powered by a separate +5V to +15V supply to permit logic level matching. If batteries are used as a power source, the resulting voltage droop will have little effect on the ADC1121 accuracy due to its excellent power supply rejection.

The ADC1121 accepts analog inputs in the range of 0 to +5V, 0 to +10V, ±5V, or ±10V and produces both parallel and serial digital outputs. Parallel outputs are binary, offset binary, or two's complement coded; serial outputs are binary or offset binary coded.

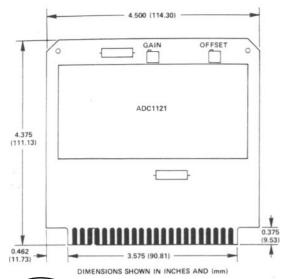

The special combination of high performance and low power exhibited by this 2" x 4" x 0.4" (51 x 102 x 10mm) module makes it ideal for use in applications such as remote and portable instrumentation, and large data handling networks.

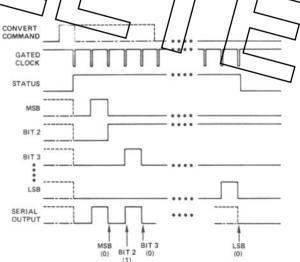

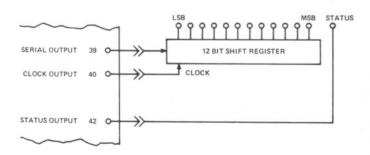

#### TIMING

When the convert command is set to logic "1", the internal clock starts to run. The first '1' to '0' clock transition sets the STATUS output to logic '1' and sets the MSB through LSB and SERIAL output lines to logic '0'. The CONVERT COMMAND input may be returned to logic '0' 100ns after this clock transition but may also remain at logic '1' until 500ns before the sixth clock transition. The MSB decision process starts on the second negative-going clock edge and concludes one clock period later. The bit decisions continue at the rate of one per clock cycle until the LSB decision has finally been made. After

the LSB decision, the clock returns to logic '1' and the STATUS output returns to logic '0'.

The serial data output is of the non-return-to-zero (NRZ) type. The data is available, MSB first, at the third and subsequent positive going lock transitions.

Figure 1. Timing Diagram

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Route 1 Industrial Park; P.O. Box 280; Norwood, Mass. 02062 Tel: 617/329-4700 TWX: 710/394-6577

West Coast 213/595-1783

Mid-West 312/894-3300 Texas 214/231-5094

# SPECIFICATIONS (typical @ +25°C unless otherwise noted)

| RESOLUTION                                                                                             | 12 Bits                                                                                                                                                      | OUTLINE DIMENSIONS AND                                                                                  |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| ACCURACY<br>Error Relative to Full Scale<br>Differential Nonlinearity Error<br>Missing Codes           | ±1/2LSB max<br>±1/2LSB max<br>No Missing Codes from<br>0 to +70°C                                                                                            | PIN DESIGNATIONS Dimensions shown in inches and (mm).                                                   |

| TEMPERATURE COEFFICIENT Gain Unipolar Zero Bipolar Offset Differential Nonlinearity                    | ±20ppm/°C of Reading, max <sup>1</sup><br>±8ppm/°C of Range, max <sup>2</sup><br>±20ppm/°C of Range, max <sup>2</sup><br>±5ppm/°C of Range, max <sup>2</sup> | 0.41 MAX (10.4)  0.2 MIN (5.1)                                                                          |

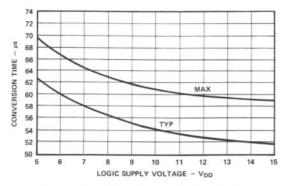

| CONVERSION TIME <sup>3</sup> +5V Logic Supply +10V Logic Supply +15V Logic Supply                      | 63µs (70µs max)<br>54µs (61µs max)<br>52µs (59µs max)                                                                                                        | ♦ 36 ———————————————————————————————————                                                                |

| INPUT VOLTAGE RANGES                                                                                   | 0 to +5V, 0 to +10V,<br>±5V, ±10V                                                                                                                            |                                                                                                         |

| INPUT IMPEDANCE  0 to +V Range 0 to +10V Range ±5V Range ±1DV Range                                    | $400$ k $\Omega$ min $144$ k $\Omega$ min $144$ k $\Omega$ min $120$ k $\Omega$ min                                                                          | 4.02 MAX<br>19 54 (102.1)                                                                               |

| DIGITAL OUTPUTS Logic Levels Parakel Output Codes Unipolar Bipolar                                     | CMOS Compatible (see pg. 4)  Positive True Binary Positive True Offset Binary of Two's domplement                                                            | 18 55 6                                                                                                 |

| Serial Output Codes Unipolar Bipolar                                                                   | Positive True Binary, NRZ Format, MSB First Positive True Offset Binary,                                                                                     |                                                                                                         |

| Status Output                                                                                          | NRZ Format, MSB First<br>Logic '1' During Conversion                                                                                                         | BOTTOM VIEW GRID 9.1" (25)                                                                              |

| CONVERT COMMAND INPUT<br>Logic Levels<br>Pulse Width<br>Rise and Fall Times                            | CMOS Compatible (see pg. 4)<br>6µs min, 15µs max;<br>1µs max                                                                                                 | NOTE!  Terminal pins installed only in shaded hole locations.  All pins are gold plated half-hard brass |

| POWER SUPPLY REQUIREMENTS <sup>4</sup> Analog Supply (V <sub>S</sub> ) Logic Supply (V <sub>DD</sub> ) | +12V to +15V<br>+5V to +15V                                                                                                                                  | (MIL-G-45204), 0.019" ±0.001" (0.48 ±0.03mm) dia. For plug-in mounting card order Board                 |

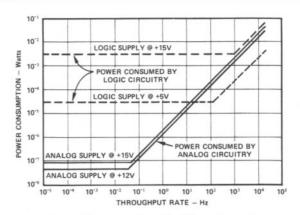

| POWER CONSUMPTION                                                                                      | See Graphs on pg. 3                                                                                                                                          | No. AC1521, \$33.00 (1-9)                                                                               |

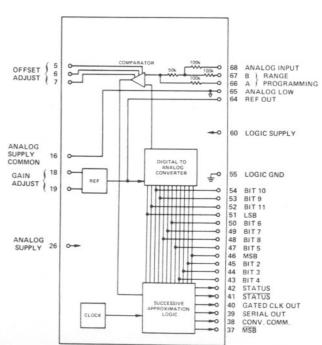

| POWER SUPPLY SENSITIVITY <sup>5</sup> Gain Unipolar Zero Bipolar Offset                                | ±%LSB<br>±%LSB<br>±%LSB                                                                                                                                      | BLOCK DIAGRAM                                                                                           |

| TEMPERATURE RANGE Operating Storage                                                                    | 0 to +70°C<br>-55 to +125°C                                                                                                                                  |                                                                                                         |

| ADJUSTMENT RANGES Gain Offset                                                                          | ±0.2% of Range <sup>2</sup><br>±0.2% of Range <sup>2</sup>                                                                                                   | OFFSET 6 COMPARATOR SON TOOK 68 ANALOG 67 B RAN ALOG 67 A PROV                                          |

| PRICE (1-9)                                                                                            | \$229                                                                                                                                                        | 64 REFOUT                                                                                               |

|                                                                                                        |                                                                                                                                                              |                                                                                                         |

<sup>1</sup> Reading for bipolar operation is defined as: Actual Reading – (-Full Scale) <sup>2</sup> Range for unipolar operation is defined as: + Full Scale

Range for bipolar operation is defined as: 2 (+ Full Scale)

Range for bipolar operation is defined as: 2 (+ Full Scale)

<sup>3</sup> Conversion time is measured from the rising edge of the convert command pulse to the falling edge of the STATUS output. A graph showing conversion time as a function of logic supply voltage is shown on page 3.

<sup>4</sup> Power supply current for both the analog and logic supplies is very transient in nature; peak current for both is less than 100mA.

<sup>5</sup> Maximum change as analog supply voltage varies from +12V to +15V.

Specifications subject to change without notice.

SE

Th to-

bii po

Fi<sub>§</sub>

is

tic pu set

SE

STA

Th m:

th

pu

ing

15

SI

# **Applying the ADC1121**

Conversion Time Vs. Logic Supply Voltage

Power Consumption Vs. Throughput Rate and Supply Voltages

Logic Circuits Power Consumption

LOGIC SUPPLY VOLTAGE - VDD

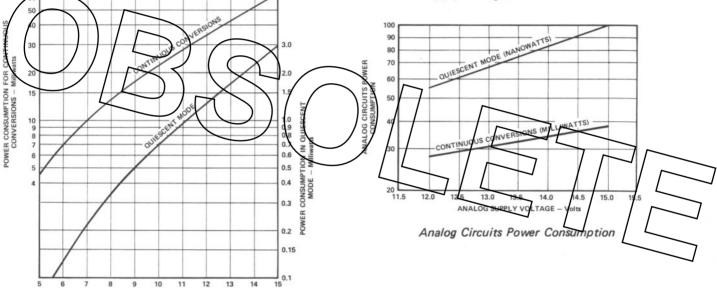

#### ANALOG INPUT CHARACTERISTICS

The input circuit of the ADC1121 is shown below in block diagram form.

Figure 2. Analog Input Configuration

Analog signals in the range of 0 to +5V, 0 to +10V,  $\pm$ 5V, or  $\pm$ 10V are applied between pins 68 and 65. The range programming circuitry serves to offset and divide these signals as neces-

sary to provide the comparator with a 0 to +5V input which is then compared to the 0 to +5V D/A converter output. Table I, below, shows the range programming connections required for the various input ranges and also shows the resulting input impedances.

| INPUT     | CONNE      | INPUT      |           |

|-----------|------------|------------|-----------|

| RANGE     | PIN 66 TO: | PIN 67 TO: | IMPEDANCE |

| 0 to +5V  | 68         | 68         | 500kΩ min |

| 0 to +10V | 65         | 68         | 180kΩ min |

| ±5V       | 64         | 68         | 180kΩ min |

| ±10V      | 64         | 65         | 150kΩ min |

Table I. Range Programming

### PARALLEL DATA OUTPUTS

The ADC1121 produces natural binary coded outputs when configured as a unipolar device; as a bipolar device it can produce either offset binary or two's complement output codes.

The most significant bit is represented by pin 46 (the MSB output) for binary and offset binary codes and by pin 37 (the MSB output) for the two's complement code. Tables II and III, below, illustrate the relationship between the analog input and digital output for all three codes.

| ANALOG INPUT      |                    | DIGITAL OUTPUT |  |

|-------------------|--------------------|----------------|--|

| 0 TO +5V<br>RANGE | 0 TO +10V<br>RANGE | BINARY CODE    |  |

| +4.9988V          | +9.9976V           | 111111111111   |  |

| +2.5000V          | +5.0000V           | 100000000000   |  |

| +0.6250V          | +1.2500V           | 001000000000   |  |

| +0.0012V          | +0.0024V           | 000000000001   |  |

| +0.0000V          | +0.0000V           | 000000000000   |  |

Table II. Nominal Unipolar Input-Output Relationships

| ANALO                            | G INPUT                           | DIGIT                                                     | AL OUTPUT                               |       |

|----------------------------------|-----------------------------------|-----------------------------------------------------------|-----------------------------------------|-------|

| ±5V<br>RANGE                     | ±10V<br>RANGE                     | OFFSET BINARY                                             | TWO'S COMPLEMENT CODE                   |       |

| +4.9976V<br>+2.5000V             | +9.9951V<br>+5.0000V              | 111111111111                                              | 0111111111111                           | -<br> |

| +0.0024V<br>+0.0000V<br>-5.0000V | +0.0049V<br>+0.0000V<br>-10.0000V | 100000000000<br>10000000 <del>000</del> 00<br>00000000000 | 000000000000000000000000000000000000000 |       |

|                                  |                                   |                                                           |                                         | -     |

Table III. Nominal Bipolar Input-Output Relationships

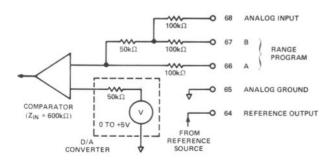

#### **SERIAL DATA OUTPUTS**

The serial data output, available at pin 39, is of the non-returnto-zero format. The data, which is transmitted MSB first, is binary coded for unipolar units and offset binary coded for bipolar units.

Figure 3, below, indicates one method for transmitting data serially using only three wires (plus a digital ground). The data is clocked into a receiving shift register by the positive-going transitions of the gated clock output. Since these clock transitions occur typically 250 to 550ns after each bit of serial output data becomes valid, ample time is allowed for shift register set-up.

Figure 3. Serial Data Transmission

The STATUS output goes from logic '1' to logic '0' approximately 100 to 450ns after the last '0' to '1' clock transition. If the shift register's propagation delay exceeds this CLOCK output to STATUS output delay, the parallel output data appearing at its terminals will not be stable when end-of-conversion is signalled. The introduction of a suitable delay into the STATUS output line will readily circumvent this problem.

#### LOGIC LEVELS

The logic levels of the ADC1121's CMOS digital outputs are as shown below:

$$V_{DD} \ge Logic "1" \ge V_{DD} - 0.1V$$

; where  $V_{DD}$  is the logic supply voltage.

$0.1V \ge Logic "0" \ge 0.0V$

The logic power supply voltage (which is independent of the analog supply voltage) can be varied from +5V to +15V. This allows the user to match the converter's logic levels to the logic levels of other CMOS devices in his system.

Although TTL logic levels can be achieved by setting the logic supply voltage to +5V, the MSB through LSB output gates do not have sufficient current sink capability to drive standard TTL logic. They can, however, readily drive low power TTL such as the series 74L devices. The remaining digital outputs (STATUS, STATUS, SERIAL OUT, CLOCK OUT, and MSB) have a 4mA current sink capability and, thus, can be used directly with standard TTL logic.

CONVERT COMMAND, the only digital input, will respond to logic levels of:

$$V_{DD} \ge Logic "1" \ge 0.7 V_{DD}$$

0.3  $V_{DD} \ge Logic "0" \ge 0.0V$

Nowever for minimum logic power supply consumption, Logic '1' should be kept as close to V<sub>DD</sub> as possible and Logic b' as close to 0.0V as possible.

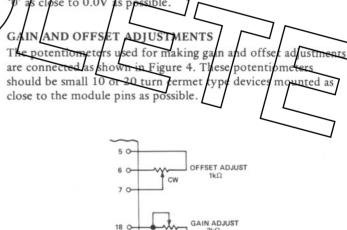

Figure 4. Adjustment Potentiometer Connections

Proper gain and offset calibration requires great care and the use of sensitive and accurate reference instruments. The voltage standard used as a signal source must be very stable. It should be capable of being set to within  $\pm 1/10$ LSB of the desired value at both ends of its range.

The gain and offset calibrations will be independent of each other if the offset adjustment is made first. These adjustments are not made with zero and full scale input signals and it may be helpful to understand why. An A/D converter will produce a given digital word output for a small range of input signals, the nominal width of the range being 1LSB. If the input test signal is set to a value which should cause the converter to be on the verge of switching between two adjacent digital outputs, the unit can be calibrated so that it does, in fact, switch at just that point. With a high speed convert command rate and a visu-

al display, these adjustments can be performed in a very accurate and sensitive way. Analog Devices' Conversion Handbook gives more detailed information on testing and calibrating A/D converters.

#### OFFSET CALIBRATION

For 0 to +5V units set the input voltage precisely to +0.0006V; for 0 to +10V units set it to +0.0012V. Adjust the offset potentiometer until the converter is just on the verge of switching from 0000000000000 to 000000000001.

## GAIN CALIBRATION

Set the input voltage precisely th +4.9982 y for 0 to +5 y units, to +9.9963 y for 0 to +10 y units, to +4.9963 y for ±5 y units, or to +9.927 y for ±10 y unit. Note that these values are 1½LSB's less than nominal full scale. Adjust the gain potention meter until binary and offset binary coded units are just on the verge of switching from 111111111111 to 1111111111 and two's complement coded units are just on the verge of switching from 011111111111 to 01111111111.

#### POWER SUPPLY AND GROUNDING CONNECTIONS

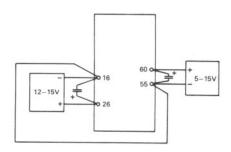

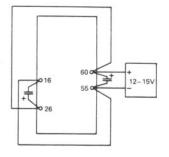

The ADC1121 has independent analog and logic supply inputs which may be powered from a single source or from separate sources. Figures 5 and 6, below, show the proper connections for both cases. The analog supply ground, pin 16, and the digital supply ground, pin 55, are not connected internally but should be jumpered together close to the module pins. Although the analog supply ground and analog signal ground, pin 65, are joined inside the module, pin 65 should never be used as a power supply return. Due to the transient nature of the supply currents encountered in a device of this type, it is recommended that  $15\mu\text{F}$ , 35V tantalum bypass capacitors be added across the analog and digital supplies at a location close to the module pins.

Figure 5. Two Source Connection

Figure 6. Single Source Connection

Since battery-powered equipment is one of the prime areas of application for the ADC1121, excellent power supply rejection has been provided. The ADC1121 will have less than a ±¼LSB gain shift and less than a ±¼LSB offset shift as the analog supply voltage changes from +15V to +12V during the course of a battery discharge cycle.

#### REPETITIVE CONVERSIONS

When making repetitive conversions, a new convert command pulse may be initiated any time after the '1' to '0' transition of the STATUS output. If the STATUS output is connected to the CONVERT COMMAND input, a new conversion will automatically begin as soon as the conversion in progress has been completed. The STATUS line will remain in the logic '1' state for approximately this between conversions in this mode of operation.

#### HANDLING CONSIDERATIONS

Care must be taken in the handling of the ADC1121 to prevent electrostatic damage to its CMOS logic. The unit should be transported on conductive foam or other suitable material and should be handled only by properly grounded personnel. Ground connections must be made before power is applied. Electrostatic damage, should it occur, would be manifested by excessive logic current drain and/or complete failure of one or more logic IC's.

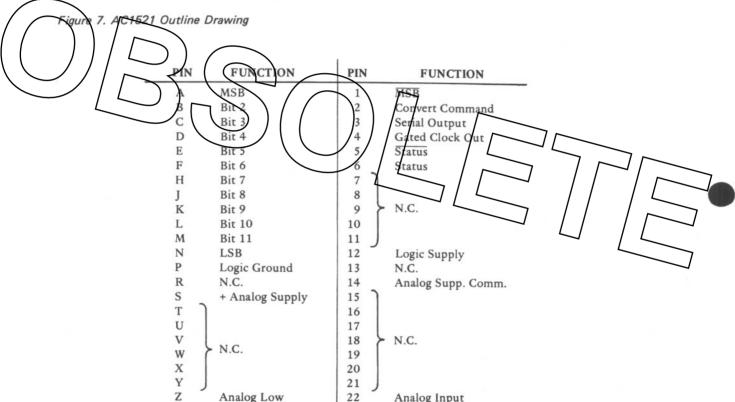

#### THE AC1521 MOUNTING CARD

The AC1521 mounting card is available to assist in the application of the ADC1121. This 4.5" x 4.4" (114 x 111mm) printed circuit card, shown in Figure 7, has sockets which allow an ADC1121 to be plugged directly onto it. It includes the necessary gain and offset adjustment potentiometers and bypass capacitors; it mates with a Cinch 251-22-30-160 (or equivalent) dual 22 pin edge connector which is supplied with every card.

The input voltage range is programmed by means of jumpers which the user installs as shown in Figure 8. The pin connections are as shown in Table IV.

| INPUT<br>VOLTAGE<br>RANGE | JUMPER<br>CONNECTIONS |

|---------------------------|-----------------------|

| 0 to +5V                  | E-D, B-A              |

| 0 to +10V                 | E-F, B-A              |

| :5V                       | E-G, B-A              |

| ±10V                      | E-G, B-C              |

Figure 8. AC1521 Range Programming

Table IV. AC1521 Pin Designations

22

Analog Input

Analog Low