| Radiation Test Report |                            |  |  |  |

|-----------------------|----------------------------|--|--|--|

| Product:              | ADCLK925S                  |  |  |  |

| Effective LET:        | 85 MeV-cm <sup>2</sup> /mg |  |  |  |

| Fluence:              | 1E7 lons/cm <sup>2</sup>   |  |  |  |

| Die Type:             | AD8210                     |  |  |  |

| Facilities:           | TAMU                       |  |  |  |

| Tested:               | June 2014                  |  |  |  |

The RADTEST® DATA SERVICE is a compilation of radiation test results on Analog Devices' Space grade products. It is designed to assist customers in selecting the right product for applications where radiation is a consideration. Many products manufactured by Analog Devices, Inc. have been shown to be radiation tolerant to most tactical radiation environments. Analog Devices, Inc. does not make any claim to maintain or guarantee these levels of radiation tolerance without lot qualification test.

It is the responsibility of the Procuring Activity to screen products from Analog Devices, Inc. for compliance to Nuclear Hardness Critical Items (HCI) specifications.

#### Warning:

Analog Devices, Inc. does not recommend use of this data to qualify other product grades or process levels. Analog Devices, Inc. is not responsible and has no liability for any consequences, and all applicable Warranties are null and void if any Analog Devices product is modified in any way or used outside of normal environmental and operating conditions, including the parameters specified in the corresponding data sheet. Analog Devices, Inc. does not guarantee that wafer manufacturing is the same for all process levels.

# SINGLE EVENT EFFECTS TEST REPORT

Test Type: Heavy ion

Test facility: TAMU, College Station - TX- USA

Test Date: June 2014

Part Type: ADCLK925

Part Description: Ultrafast SiGe ECL Clock/Data Buffers

Part Manufacturer: Analog Devices

Analog Devices PO No 45457246 dated 03/04/2014

| Hirex reference : | HRX/SEE/0499   | Issue: 01       | Date : | July 23, 2013 |

|-------------------|----------------|-----------------|--------|---------------|

| Written by :      | Cédric VIGREUX | Design Engineer |        |               |

| Authorized by:    | F.X. Guerre    | Study Manager   |        | fm            |

Hirex Engineering SEE Test Report Ref.: HRX/SEE/0499

Issue: 01

#### **RESULTS SUMMARY**

# **Facility**

TAMU, College Station, Texas, USA

## **Test date**

June 2014

# **Device description**

<u>Part type:</u> ADCLK925 <u>Manufacturer:</u> Analog Devices

Samples used 4

Package: FP-16

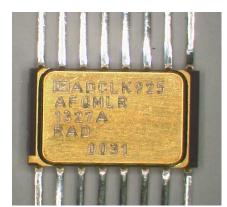

Top marking: logo ADCLK925 AFQMLR 1327A RAD

serial

Bottom marking: E240257 PHILIPPINES

Date code: 1327A

<u>Die dimensions:</u> 1.1 mm X. 1.3 mm

# **SEL Results**

No SEL neither step current increase has been observed when tested with V+ set to +4V on the 4 samples with LET of 85 MeV/(mg/cm²) and at a temperature of 125°C.

Hirex Engineering SEE Test Report Ref. : HRX/SEE/0499

Issue : 01

# **DOCUMENTATION CHANGE NOTICE**

| Issue | Date       | Page | Change Item    |  |

|-------|------------|------|----------------|--|

| 01    | 23/07/2014 | All  | Original issue |  |

|       |            |      |                |  |

|       |            |      |                |  |

|       |            |      |                |  |

|       |            |      |                |  |

|       |            |      |                |  |

|       |            |      |                |  |

|       |            |      |                |  |

|       |            |      |                |  |

Contributors to this work:

Cédric VIGREUX Hirex Engineering

Ref. : **HRX/SEE/0499**

Issue: **01**

# **SEE TEST REPORT**

# **TABLE OF CONTENTS**

| 1 INTRODUCTION                                                                                           | 5     |

|----------------------------------------------------------------------------------------------------------|-------|

| 2 APPLICABLE AND REFERENCE DOCUMENTS                                                                     | 5     |

|                                                                                                          |       |

| 3 DEVICE INFORMATION                                                                                     | 6     |

| 3.2 SAMPLE IDENTIFICATION                                                                                |       |

| 4 TAMU FACILITY                                                                                          | 7     |

| 5 TEST SET-UP                                                                                            | 9     |

| 5.1 ADCLK925 TEST PRINCIPLE AND CONDITIONS                                                               | 9     |

| 6 SEE TEST RESULTS                                                                                       | 11    |

| 6.1 SEL RESULTS                                                                                          | 11    |

| 7 GLOSSARY                                                                                               | 12    |

| 8 APPENDIX : μSECTION ANALYSIS                                                                           | 13    |

| STACK CONSTRUCTION ANALYSIS                                                                              | 13    |

| LIST OF FIG                                                                                              | BURES |

| Figure 1 – ADCLK925 device identificationFigure 2 - ion beam setting                                     |       |

| Figure 3 - Heavy ion test set-up<br>Figure 4 – ADCLK925 Bias condition<br>Figure 5 – Photo of test board | 10    |

| LIST OF TA                                                                                               | ABLES |

| Table 1 - Voltage bias conditions applied to the 2 DUTs                                                  |       |

| Table 2 - Tester supply channel affectation<br>Table 3 –Run table for the ADCLK925, TAMU June 2014 .     |       |

| Table 4: Material identification and thickness measuremen                                                |       |

Hirex Engineering SEE Test Report Ref. : HRX/SEE/0499

Issue : 01

# 1 <u>Introduction</u>

This report presents the results of SEL Heavy Ions test program carried out on ADCLK925. During June 20144, 4 samples were used for heavy ions testing at TAMU, College Station, Texas, USA. This work was performed for Analog Devices under PO n° 45457246 dated 03/04/2014.

# 2 Applicable and Reference Documents

## 2.1 Applicable Documents

AD-1. Datasheet <a href="http://www.analog.com/static/imported-files/data-sheets/ADCLK905-907-925.pdf">http://www.analog.com/static/imported-files/data-sheets/ADCLK905-907-925.pdf</a>

# 2.2 Reference Documents

RD-1. Single Event Effects Test method and Guidelines ESA/SCC basic specification No 25100

# 3 **DEVICE INFORMATION**

#### 3.1 Device description

The ADCLK925 is an Ultrafast SiGe ECL Clock/Data Buffers.

<u>Part type:</u> ADCLK925 <u>Manufacturer:</u> Analog Devices

Package: FP-16

Top marking: logo ADCLK925 AFQMLR

1327A RAD serial

Bottom marking: E240257 PHILIPPINES

Date code: 1327A

Die dimensions: 1.1 mm X. 1.3 mm

## 3.2 Sample identification

10 ADCLK925 parts were delivered by Analog Devices. All samples were prepared and delidded to be tested to heavy ions. 4 samples were verified fully functional before the test campaign, and 4 were tested under irradiation.

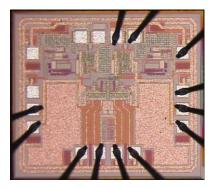

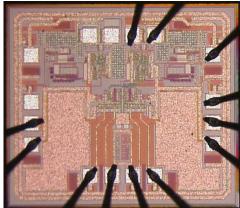

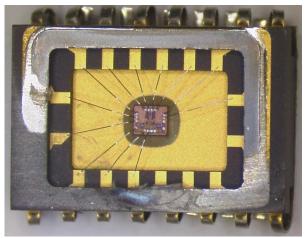

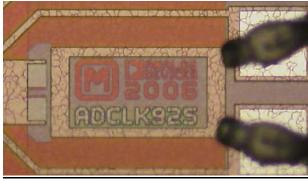

Photo 1 – Device top view

Photo 3 - die, full view

Photo 2 - Device delidded

Photo 4 - Die marking

Figure 1 - ADCLK925 device identification

#### 3.3 Sample preparation and evaluation of dead layer thickness

Samples were prepared by mechanical delidding.

Die micro-section results are given in appendix. Overall dead layer thickness on top of active zone is less than 10 microns of equivalent silicon. Active zone thickness is less than 5 microns.

#### 4 TAMU Facility

Test at the cyclotron accelerator was performed at Texas A & M in College Station - TX- USA.

This facility includes a special beam line dedicated to irradiation studies of semiconductor components and devices. Testing may be conducted in either 30" diameter vacuum chamber or with in-air positioning system. Both provide precise positioning in x, y, and z as well as rotations up to 60 degrees. Positioning and dosimetry are carried out by custom-made SEUSS software.

#### **In Air Station**

The in-air station is located at the end of dedicated beam-line. The station consists of a rotating platform and a removable target mounting fixture. The target positioning assembly allows the motion of the target in four directions: X, Y, Z and Theta. X and Y are the horizontal and the vertical axis in the target plane, respectively. The Z-axis is in the direction of the beam-line, with theta being the clockwise and counter-clockwise rotation about the y-axis. Target position verification is provided by the means of a CCD camera aligned with the beam path and a narrow laser beam that crosses the beam path at the center of the target chamber. The size of the exposed area is controlled by the aperture defined by a pair of remotely adjustable horizontal and vertical slits.

#### **Vacuum Station**

Vacuum station has an inside diameter of 30inch and a height 30inch. Pumping time to an operating pressure in the low 10 -4 Torr range is approximately ten minutes and the chamber vents to gaseous nitrogen in two and half minutes. Target positioning system allows X, Y, Z and Theta moving. Like for in air station, the position is checked with the means of a CCD camera.

#### Ion Beam

Various ion beams are available for the Radiation Effects Facility. These beams provide for a wide scope of LET with high energies for deep part penetration. Time for beam species changes will vary, but with species that have the same energy per nucleon change times is about one half hour.

Beams can be delivered with a high degree of uniformity over a 1.8" x 1.8" cross sectional area for measurements inside the vacuum chamber and 1" diameter circular cross sectional area for the in-air station. Uniformity is achieved by means of magnetic defocusing.

A degrader foil system makes it possible to set the desired beam LET value at a particular depth inside the target without changing the beam or rotating the target. The beam energy is reduced by means of a degrader system with foils having a suitable thickness and orientation with respect to the incident beam. Each foil can be inserted, withdrawn, and rotated remotely through use of computer controls.

The intensity of any beam is easily regulated over a broad range spanning several orders of magnitude in a matter of seconds. This can be done by the operator on duty at the users request.

The target exposure system is fully automated. Exposure can be set for a certain time, total accumulated fluence, or can be manually stopped at any time.

### **Beam Quality control**

The beam uniformity and flux are determined using an array of five detectors. Each detector is made up with a plastic scintillator coupled to photo-multiplier tubes. Four of the detectors are fixed in position and set up to measure beam particle counting rates continuously at four characteristic points 1.64 inches (4.71 mm) away from the beam axis. The fifth scintillator can be optionally put in to measure the beam particle counting rate right at the beam axis. The sensitive area of each detector is defined by a 0.1 cm^2 aperture, while the intrinsic efficiency is 100% for all practical purposes. The beam uniformity parameter (ranging from 0 to 100%), the axial gain (%), and the beam flux (in particles/cm^2/s) are determined by the control software based on the detector counting rates. The results are displayed and updated once every second.

#### Dosimetry

The current TAMU Cyclotron dosimetry system and procedures were used.

Hirex Engineering SEE Test Report Ref. : HRX/SEE/0499

Issue : 01

# **Beam configuration used**

15MeV/a cocktail have been for this test.

| Ion | Selected beam | Al degrader<br>thickness (mil) | Number of layers<br>(layer file name) | Beam energy<br>(MeV) | Nominal LET<br>(MeVcm2/mg) | Nominal range (um) |

|-----|---------------|--------------------------------|---------------------------------------|----------------------|----------------------------|--------------------|

| Xe  | 15.0 MeV/u Xe | 2,096                          | 3 (30 mm air)                         | 737                  | 60                         | 59.6               |

| Au  | 15 MeV/u Xe   | 0                              | 3 (30 mm air)                         | 2247                 | 85.4                       | 118.1              |

Figure 2 - ion beam setting

# 5 Test Set-up

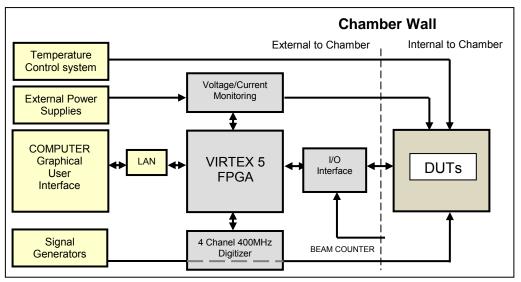

Test system Figure 3 shows the principle of the Heavy Ion test system.

The test system is based on a Virtex5 FPGA (Xilinx). It runs at 50 MHz. The test board has 168 I/Os which can be configured using several I/O standards.

The test board includes the voltage/current monitoring and the latch-up management of the DUT power supplies up to 24 independent channels.

The communication between the test chamber and the controlling computer is effectively done by a 100 Mbit/s Ethernet link which safely enables high speed data transfer.

Figure 3 - Heavy ion test set-up

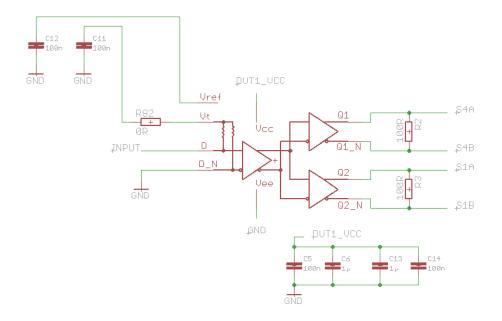

#### 5.1 ADCLK925 test principle and conditions

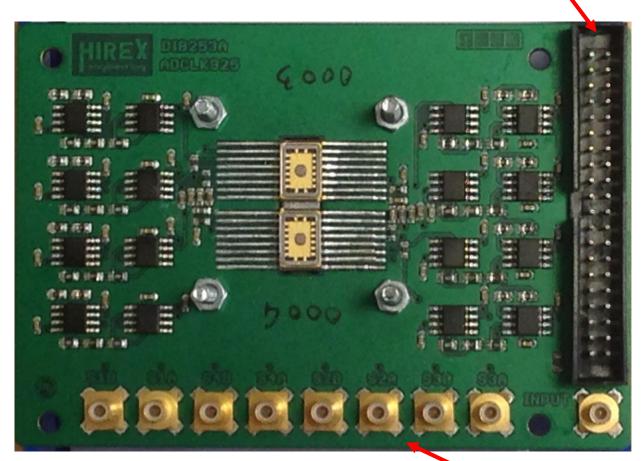

In order to test the ADCLK925 2 daughter boards were designed. 2 DUTs were mounted on each board and bias conditions are given in Figure 4 and Table 1. Table 2 gives the tester supply channel number used in the tester report.

DUT heating is performed with a thermal resistor and aluminum plate in contact with DUT backsides. The temperature is regulated thank to a thermocouple sensor put on top of the device.

SEL event is detected when the supply current is over a configurable threshold (in the present case set to 100 mA) and processed (the power supplies are cut off during a configurable wait time, in the present case set to 1s).

The tester monitors independently the 2 DUTs supplies at the same time. If an SEL is detected on 1 supply channel, the tester system records current/voltage on all channels.

| Supply name | voltage |

|-------------|---------|

| DUT_V+      | +4V     |

| INPUT       | 1V      |

Table 1 - Voltage bias conditions applied to the 2 DUTs

| Supply name | Tester supply channel # |

|-------------|-------------------------|

| DUT1_V+     | 1                       |

| DUT2_V+     | 4                       |

| INPUT       | 13                      |

Table 2 - Tester supply channel affectation

Ref. : **HRX/SEE/0499**

Issue: 01

Figure 4 - ADCLK925 Bias condition

Supplies interface

Figure 5 – Photo of test board

DUT1 to 2 outputs

# 6 **SEE test results**

Runs performed are listed in Table 3.

Upon test completion, all 4 samples were found fully functional

# 6.1 SEL Results

No SEL neither step current increase has been observed when tested with V+/- set to +4V at any LET value with all tested samples.

| Run# | DUT#   | Power supply | Temperature<br>°C | lon | LET<br>MeV/(mg/cm²) | Fluence<br>lons/cm² | <b>Duration</b><br>S | SEL |

|------|--------|--------------|-------------------|-----|---------------------|---------------------|----------------------|-----|

| 2    | 1 to 2 | 4            | 85                | Xe  | 60                  | 1,00E+07            | 443                  | 0   |

| 3    | 1 to 2 | 4            | 125               | Xe  | 60                  | 1,00E+07            | 445                  | 0   |

| 5    | 3 to 4 | 4            | 125               | Xe  | 60                  | 1,00E+07            | 384                  | 0   |

| 7    | 3 to 4 | 4            | 85                | Au  | 85.4                | 1,00E+07            | 251                  | 0   |

| 8    | 3 to 4 | 4            | 125               | Au  | 85.4                | 1,00E+07            | 278                  | 0   |

| 9    | 1 to 2 | 4            | 85                | Au  | 85.4                | 1,00E+07            | 324                  | 0   |

| 10   | 1 to 2 | 4            | 125               | Au  | 85.4                | 1,00E+07            | 370                  | 0   |

Table 3 -Run table for the ADCLK925, TAMU June 2014

# 7 Glossary

Most of the definitions here below are from JEDEC standard JESD89A

**DUT**: Device under test.

**Fluence** (of particle radiation incident on a surface): The total amount of particle radiant energy incident on a surface in a given period of time, divided by the area of the surface. In this document, Fluence is expressed in ions per cm2.

**Flux**: The time rate of flow of particle radiant energy incident on a surface, divided by the area of that surface.

In this document, Flux is expressed in ions per cm2\*s.

**Single-Event Effect** (SEE): Any measurable or observable change in state or performance of a microelectronic device, component, subsystem, or system (digital or analog) resulting from a single energetic particle strike.

Single-event effects include single-event upset (SEU), multiple-bit upset (MBU), multiple-cell upset (MCU), single-event functional interrupt (SEFI), single-event latch-up (SEL.

**Single-Event Transient** (SET): A soft error caused by the transient signal induced by a single energetic particle strike.

**Single-Event Latch-up** (SEL): An abnormal high-current state in a device caused by the passage of a single energetic particle through sensitive regions of the device structure and resulting in the loss of device functionality.

SEL may cause permanent damage to the device. If the device is not permanently damaged, power cycling of the device (off and back on) is necessary to restore normal operation.

An example of SEL in a CMOS device is when the passage of a single particle induces the creation of parasitic bipolar (p-n-p-n) shorting of power to ground.

Single-Event Latch-up (SEL) cross-section: the number of events per unit fluence. For chip SEL cross-section, the dimensions are cm2 per chip.

**Error cross-section**: the number of errors per unit fluence. For device error cross-section, the dimensions are cm2 per device. For bit error cross-section, the dimensions are cm2 per bit.

**Tilt angle**: tilt angle, rotation axis of the DUT board is perpendicular to the beam axis; roll angle, board rotation axis is parallel to the beam axis