# ADP5056-EVALZ User Guide

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

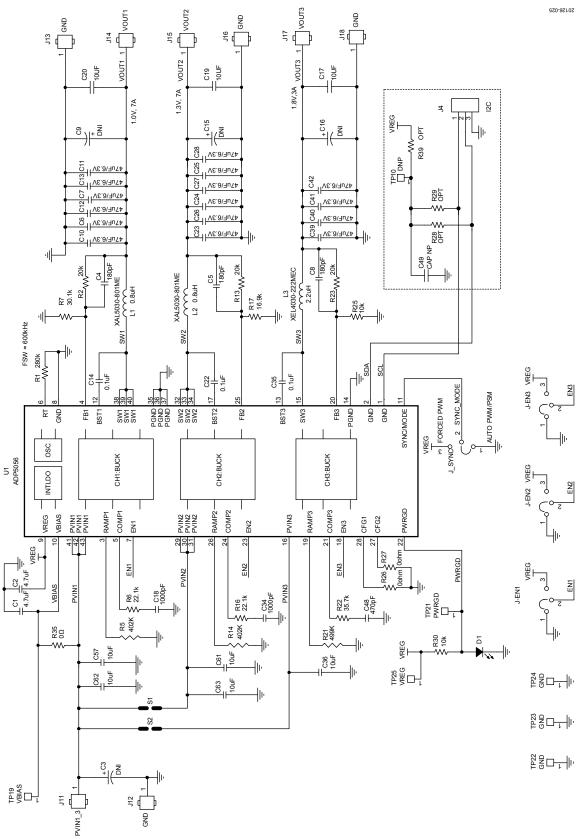

# Evaluating the ADP5056 Triple Buck Regulator Integrated Power Solution

### **FEATURES**

Wide input voltage range: 2.75 V to 18 V

Bias input voltage range: 4.5 V to 18 V

Full-featured evaluation board for the ADP5056

Channel 1 and Channel 2: 7 A synchronous buck regulator, or 14 A output in parallel operation

Channel 3: 3 A synchronous buck regulator

Selective PSM or FPWM operation

Programmable switching frequency from 2.5 MHz to 250 kHz

Frequency synchronization input or output

### **GENERAL DESCRIPTION**

This user guide describes the evaluation of the ADP5056 and includes detailed schematics and printed circuit board (PCB) layouts.

The ADP5056-EVALZ features the ADP5056, which combines three high performance buck regulators in a 43-terminal land grid array (LGA) to meet the demanding performance and board space requirements. The ADP5056-EVALZ connects to input voltages up to 18 V directly, without any preregulators.

Full details on the device are provided in the ADP5056 data sheet, available from Analog Devices, Inc. Consult this data sheet in conjunction with this user guide when evaluating the ADP5056.

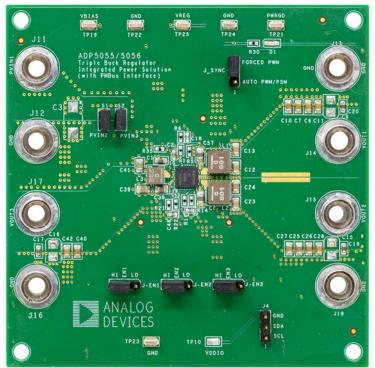

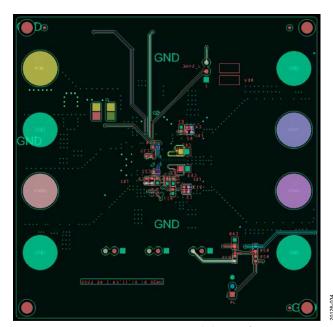

### **ADP5056-EVALZ PHOTOGRAPH**

Figure 1.

## UG-1517

# **ADP5056-EVALZ** User Guide

### **TABLE OF CONTENTS**

| Features                    | J |

|-----------------------------|---|

| General Description         | 1 |

| ADP5056-EVALZ Photograph    | 1 |

| Revision History            | 2 |

| Evaluation Board Hardware   | 3 |

| Enable Jumpers              | 3 |

| Power Input Jumpers         |   |

| J-SYNC Jumper (SYNC/MODE)   | 3 |

| Input Power Source          | 3 |

| Output Load                 |   |

| Input and Output Voltmeters |   |

| Quick Startup                                          | .4 |

|--------------------------------------------------------|----|

| Measuring Evaluation Board Performance                 | .5 |

| Measuring Output Voltage Ripple of the Buck Regulator  | .5 |

| Measuring the Switching Waveform of the Buck Regulator | .5 |

| Evaluating the Synchronization Input or Output         | .5 |

| Evaluating Efficiency                                  | .5 |

| Modifying the Board                                    | .5 |

| Evaluation Board Schematics and Artwork                | .7 |

| Ordering Information                                   | 0  |

| Dill of Matarials                                      | Λ  |

### **REVISION HISTORY**

5/2020—Revision 0: Initial Version

### **EVALUATION BOARD HARDWARE**

The ADP5056-EVALZ is fully assembled and tested. Before applying power to the evaluation board, follow the procedures in this section.

#### **ENABLE JUMPERS**

Each channel has an enable pin that must be pulled high to enable that channel (see Table 1). Pull the enable pin low or leave it floating to disable the channel.

The enable control for each regulator has a 0.615 V precision enable threshold, which allows the ADP5056 to be sequenced between channels or other input/output supplies.

Table 1. Enable Pin Channels

| Channel   | Pin Name | Enable Jumpers |  |

|-----------|----------|----------------|--|

| Channel 1 | EN1      | J-EN1          |  |

| Channel 2 | EN2      | J-EN2          |  |

| Channel 3 | EN3      | J-EN3          |  |

### **POWER INPUT JUMPERS**

Each channel has its own power input jumper, which supports separate input voltages or cascaded options for all channels.

The input voltage range for the three buck regulators is 4.5 V to 18 V. If separate power supplies are used for PVIN1 and VBIAS with R35 removed (on the ADP5056-EVALZ, PVIN1 and VBIAS are connected together through the R35, 0  $\Omega$  resistor by default), the input voltage range for the three buck regulators is 2.75 V to 18 V. Shunt S1 and S2 to allow easy setup by using the same input voltages for the three buck regulators. See Table 2 for the power input details.

**Table 2. Power Input Pin Channels**

| Channel   | Pin Name | Input Jumper | Input Range (V) |

|-----------|----------|--------------|-----------------|

| Channel 1 | PVIN1    | J11          | 4.5 to 18       |

| Channel 2 | PVIN2    | S1           | 4.5 to 18       |

| Channel 3 | PVIN3    | S2           | 4.5 to 18       |

### J-SYNC JUMPER (SYNC/MODE)

The J-SYNC jumper, as shown in Figure 1, is used to connect the SYNC/MODE pin of the device to either low (GND) or high (VREG).

- Shunt the center contact of J-SYNC (SYNC\_MODE) to the top pin header, which pulls the SYNC/MODE pin high to VREG (4.8 V) to allow the three buck regulators into forced pulse width modulation (FPWM) operation.

- 2. Shunt the center contact of J-SYNC to the bottom pin header, which pulls the SYNC/MODE pin low to force the three buck regulators to operate in automatic pulse width modulation/power saving mode (PWM/PSM) operation.

### **INPUT POWER SOURCE**

Use the following steps to connect the evaluation board to the input power source:

- Ensure that the evaluation board is disabled by connecting the enable jumpers (J-EN1 to J-EN3) to the low position before connecting the power source to the ADP5056-EVALZ.

- 2. If the input power source includes a current meter, use the meter to monitor the input current.

- 3. Connect the positive terminal of the power source to the PVIN1 terminal (J11) on the evaluation board, and connect the negative terminal of the power source to the GND terminal (J12) of the evaluation board.

- 4. If the power source does not include a current meter, connect a current meter in series with the input source voltage.

- 5. Connect the positive terminal of the power source to the positive lead of the current meter, the negative terminal of the power source to the GND terminal (J12) on the evaluation board, and the negative lead of the current meter to the PVIN1 terminal (J11) on the board.

### **OUTPUT LOAD**

Use the following steps to connect the evaluation board to the output load:

- 1. Ensure that the evaluation board is turned off before connecting the load.

- 2. Connect an electronic load or resistor to set the load current. If the load includes an ammeter, or if the current is not measured, connect the load directly to the evaluation board, with the positive load connected to one of the channels. For example, connect the positive load terminal to the Channel 1 buck regulator output, J14 (VOUT1), and connect the negative load terminal to J13 (GND).

- 3. If an ammeter is used, connect it in series with the load.

- 4. Connect the positive ammeter terminal to the Channel 1 buck regulator output, J14 (VOUT1), connect the negative ammeter terminal to the positive load terminal, and connect the negative load terminal to J13 (GND).

### INPUT AND OUTPUT VOLTMETERS

Use the following steps to measure the input and output voltages with voltmeters:

- Ensure that the voltmeters are connected to the appropriate evaluation board terminals and not to the load or power sources themselves. If the voltmeters are not connected directly to the evaluation board, the measured voltages are inaccurate due to the voltage drop across the leads and/or connections between the evaluation board, the power source, and/or the load.

- Connect the voltmeter positive terminal measuring the input voltage to J11 (PVIN1), and connect the voltmeter negative terminal measuring the input voltage to J12 (GND).

3. Connect the voltmeter positive terminal measuring the output voltage of the Channel 1 buck regulator to J14 (VOUT1), and connect the voltmeter negative terminal measuring the output voltage to J13 (GND).

### **QUICK STARTUP**

Verify the following before powering up the evaluation board:

- The power source voltage for the three buck regulators (PVIN1, PVIN2, and PVIN3) is 4.5 V to 18 V. Shunt the S1 and S2 jumpers to use the same input voltage for all three buck regulators

- Use the J-EN1, J-EN2, and J-EN3 jumpers to enable or disable the desirable channel

When the power source and load are connected to the evaluation board, the evaluation board can be powered for operation. If the load is not enabled, enable the load. Check that the load is drawing the proper current and that the output voltage maintains voltage regulation.

After power-up, the following output voltages ( $V_{\mbox{\scriptsize OUTx}}$  ) can be measured:

- $V_{OUT1} = 1.0 \text{ V}$ , supply up to 7 A continuous load current

- $V_{OUT2} = 1.3 \text{ V}$ , supply up to 7 A continuous load current

- V<sub>OUT3</sub> = 1.8 V, supply up to 3 A continuous load current

### MEASURING EVALUATION BOARD PERFORMANCE

# MEASURING OUTPUT VOLTAGE RIPPLE OF THE BUCK REGULATOR

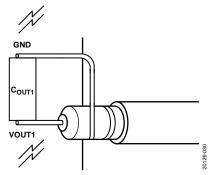

To observe the output voltage ripple of Channel 1, place an oscilloscope probe across the output capacitor ( $C_{OUT1}$ ) with the probe ground lead at the negative capacitor terminal and the probe tip at the positive capacitor terminal.

Set the oscilloscope to ac coupling and 1  $\mu$ s/division time base, with the bandwidth set to 20 MHz to avoid noise that interferes with the measurements. It is recommended to shorten the ground loop of the oscilloscope probe to minimize coupling.

An accurate output voltage ripple measurement can be performed across C11 or C20 using the proper measurement technique as shown in Figure 2.

Figure 2. Measure Output Voltage Ripple

# MEASURING THE SWITCHING WAVEFORM OF THE BUCK REGULATOR

To observe the switching waveform using an oscilloscope, place the oscilloscope probe tip at the exposed copper trace at the SWx terminal of the inductor with the probe ground at GND. Set the oscilloscope to dc coupling, 5 V/division, and 1  $\mu$ s/division time base.

When the SYNC/MODE pin is set to high, the buck regulators operate in FPWM mode. When the SYNC/MODE pin is set to low, the buck regulators operate in PSM, improving the light load efficiency.

# **EVALUATING THE SYNCHRONIZATION INPUT OR OUTPUT**

The SYNC/MODE pin can be configured as the clock output by the CFG1 pin. A clock pulse with a 50% duty cycle is generated at the SYNC/MODE pin with the frequency equal to the internal frequency set by the RT pin.

When the SYNC/MODE pin is configured as the input, the ADP5056 can be synchronized to an external clock applied to the SYNC/MODE pin. The internal switching frequency set by the RT pin must be programed to a value close to the external clock value.

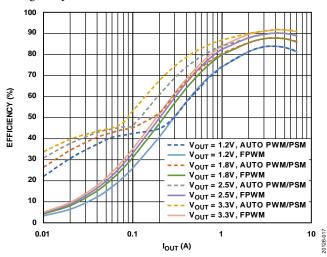

### **EVALUATING EFFICIENCY**

Measure the efficiency,  $\eta$ , by comparing the input power with the output power.

$$\eta = \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times I_{IN}}$$

where

$V_{OUT}$  is the output voltage.

$I_{OUT}$  is the output current.

$V_{IN}$  is the input voltage.

$I_{IN}$  is the input current.

Measure the input and output voltages as close as possible to the input and output capacitors to reduce the effect of the trace voltage drops.

Figure 3. Typical Channel 1/Channel 2 Efficiency,  $V_{IN} = 12 V$ , Switching Frequency ( $f_{SW}$ ) = 600 kHz, FPWM and PSM Mode

### **MODIFYING THE BOARD**

### **Setting the Output Voltages**

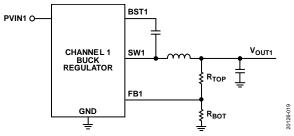

The output voltage three buck regulators are set through external resistor dividers, as shown in Figure 4, for Channel 1. The equation for setting the output voltage is

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R_{TOP}}{R_{BOT}}\right)$$

where:

$V_{REF}$  is the reference voltage,  $V_{REF} = 0.6$  V.

$R_{TOP}$  is the top resistor in the feedback voltage divider.

$R_{BOT}$  is the bottom resistor in the feedback voltage divider.

Figure 4. Channel 1 Output Voltage Setting

When the output voltage of the buck regulator is changed, the values of the inductors, the output capacitors, and the compensation networks may require recalculation and changes for stable operation. Refer to the ADP5056 data sheet for details on external components selection.

The ADP5056-EVALZ is supplied with resistor dividers for setting target output voltages. Table 3 shows the external resistor divider components for each channel.

Table 3. External Resistor Dividers in Each Channel

| Resistor Divider | Channel 1 | Channel 2 | Channel 3 |

|------------------|-----------|-----------|-----------|

| R <sub>TOP</sub> | R2        | R13       | R23       |

| R <sub>BOT</sub> | R7        | R17       | R25       |

### **Changing the Switching Frequency**

The switching frequency of ADP5056-EVALZ is programmed to be 600 kHz by default. To change the switching frequency (within the range of 2.5 MHz to 250 kHz), replace the R3 resistor connected to the RT pin with a different value. Refer to the ADP5056 data sheet for the relationship between switching frequency and the RT resistor. When the switching frequency is changed, the values of the inductors, output capacitors, and the compensation networks may need to be recalculated and changed for stable operation. Refer to the ADP5056 data sheet for more details on external components selection.

### Setting Channel 1 and Channel 2 to Interleaved Parallel Operation

Channel 1 and Channel 2 are configured as individual outputs on the ADP5056-EVALZ by default. To configure Channel 1 and Channel 2 to operate in interleaved parallel single output mode, follow these steps:

- Short J14 and J15

- Ensure that Jumper S1 is shunted

- Change R26 to 23.7 k $\Omega$  on the CFG1 pin

- Remove R16 and C34 on the COMP2 pin

- Remove R13, and replace R17 with 0  $\Omega$  on the FB2 pin

- Shunt the J-EN2 jumper to low

- Use the Channel 1 feedback resistor dividers, R2 and R7, to set the output voltage

- Use J-EN1 (EN1 pin) to enable or disable the regulator

During parallel operation, the input voltage and current-limit threshold for both channels are the same, and FPWM mode operation on both Channel 1 and Channel 2 is recommended. Refer to the ADP5056 data sheet for more details on inphase parallel operation and interleaved parallel operation.

### Phase Shift (0°, 120°, 240°) in the Three Buck Regulators

In the ADP5056-EVALZ, the phase shift is 120° between Channel 1, Channel 2, and Channel 3. This value provides the benefits of out of phase operation by reducing the input ripple current and lowering the ground noise.

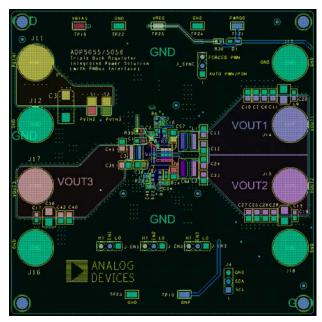

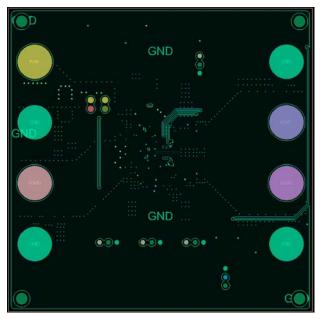

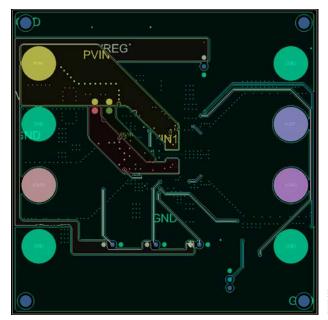

### **EVALUATION BOARD SCHEMATICS AND ARTWORK**

Figure 5. Evaluation Board Schematic of the ADP5056

Figure 6. Top Layer, Recommended Layout for ADP5056

Figure 7. Second Layer, Recommended Layout for ADP5056

Figure 8. Third Layer, Recommended Layout for ADP5056

Figure 9. Bottom Layer, Recommended Layout for ADP5056

## UG-1517

### **ORDERING INFORMATION**

### **BILL OF MATERIALS**

Table 4.

| Qty. | Reference Designator                       | Description                                       | Manufacturer         | Part Number                          |

|------|--------------------------------------------|---------------------------------------------------|----------------------|--------------------------------------|

| 1    | C1                                         | Ceramic capacitor, 4.7 μF, X6S, 25 V, 10%, 0603   | Murata               | GRM188C81E475KE11                    |

| 1    | C2                                         | Ceramic capacitor, 4.7 μF, X6S, 6.3 V, 20%, 0402  | Murata               | GRM155C80J475MEAA                    |

| 3    | C4, C5, C8                                 | Ceramic capacitors, 180 pF, C0G, 50 V, 1%, 0402   | Murata               | GCM1555C1H181FA16D                   |

| 16   | C6, C7, C10 to C13, C23 to C28, C39 to C42 | Ceramic capacitors, 47 μF, 6.3 V, 20%, 0805       | Murata/Taiyo Yuden   | GRM21BR60J476ME11,<br>MK212BJ476MG-T |

| 3    | C14, C22, C35                              | Ceramic capacitors, 0.1 μF, X7R, 16 V, 10%, 0402  | KEMET                | C0402C104K4RACTU                     |

| 2    | C18, C34                                   | Ceramic capacitors, 1 nF, 50 V, 5%, 0402          | Murata               | GRM1555C1H102JA01                    |

| 5    | C36, C57, C61 to C63                       | Ceramic capacitors, 10 μF, X7S, 25 V, 10%, 0805   | Murata               | GRM21BC71E106KE11                    |

| 3    | C17, C19, C20                              | Ceramic capacitors, 10 µF, X5R, 10 V, 10%, 0603   | Murata               | GRM188R61A106KAAL                    |

| 5    | C3, C9, C15, C16, C49                      | Capacitors                                        |                      | Do not install (DNI)                 |

| 1    | C48                                        | Ceramic capacitor, 470 pF, C0G, 50 V, 5%, 0402    | Murata               | GRT1555C1H471JA02                    |

| 1    | D1                                         | Clear green LED, 0603, surface-mount device (SMD) | LITE-ON              | LTST-C191KGKT                        |

| 4    | J-EN1, J-EN2, J-EN3, J_SYNC                | 2.54 mm, 3-pin headers                            | Wurth                | 61300311121                          |

| 2    | S1, S2                                     | 2.54 mm, 2-pin headers                            | Wurth                | 61300311121                          |

| 8    | J11 to J18                                 | Noninsulated jacks, .218 inches                   | Keystone Electronics | 575-4                                |

| 2    | L1, L2                                     | Inductors, 0.8 μH                                 | Coilcraft            | XAL5030-801ME                        |

| 1    | L3                                         | Inductor, 2.2 μH                                  | Coilcraft            | XEL4030-222ME                        |

| 1    | R1                                         | Resistor, SMD, 280 kΩ, 1%, 1/16 W, 0402           | Vishay Dale          | CRCW0402280KFKED                     |

| 3    | R2, R13, R23                               | Resistors, SMD, 20 kΩ, 1%, 1/16 W, 0402           | Vishay Dale          | CRCW040220K0FKED                     |

| 2    | R5, R14                                    | Resistors, SMD, 402 kΩ, 1%, 1/16 W, 0402          | Vishay Dale          | CRCW0402402KFKED                     |

| 2    | R6, R16                                    | Resistors, SMD, 22.1 kΩ, 1%, 1/16 W, 0402         | Vishay Dale          | CRCW040222K1FKED                     |

| 1    | R7                                         | Resistor, SMD, 30.1 kΩ, 1%, 1/16 W, 0402          | Vishay Dale          | CRCW040230K1FKED                     |

| 1    | R17                                        | Resistor, SMD, 16.9 kΩ, 1%, 1/16 W, 0402          | Vishay Dale          | CRCW040216K9FKED                     |

| 1    | R21                                        | Resistor, SMD, 499 kΩ, 1%, 1/16 W, 0402           | Vishay Dale          | CRCW0402499KFKED                     |

| 1    | R22                                        | Resistor, SMD, 35.7 kΩ, 1%, 1/16 W, 0402          | Vishay Dale          | CRCW040235K7FKED                     |

| 2    | R25, R30                                   | Resistors, SMD,10 kΩ, 1%, 1/16 W, 0402            | Vishay Dale          | CRCW040210K0FKED                     |

| 3    | R26, R27, R35                              | Resistors, SMD, 0 Ω, jumper, 1/10 W, 0603         | Vishay Dale          | CRCW04020000Z0ED                     |

| 3    | R28, R29, R39                              | Resistors, 0402                                   |                      | DNI                                  |

| 6    | TP19, TP21 to TP25                         | Test points, miniature                            | Keystone Electronics | 5019                                 |

| 1    | TP10                                       | Test point                                        |                      | DNI                                  |

| 1    | U1                                         | Triple buck regulator                             | Analog Devices       | ADP5056                              |

### **NOTES**

$l^2 C\ refers\ to\ a\ communications\ protocol\ originally\ developed\ by\ Philips\ Semiconductors\ (now\ NXP\ Semiconductors).$

#### ESD Caution

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### **Legal Terms and Conditions**

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. "(ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer, all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the ROHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "AS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

©2020 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. UG20126-5/20(0)

www.analog.com