# Low Feedthrough Multiplying D/A Converter

DAGIZE

# PRELIMINARY TECHNICAL DATA

## **FEATURES**

12 Bit Resolution and Accuracy

Two Quadrant or Four Quadrant Operation

Four Quadrant Feedthrough < ½LSB to 40kHz

3µs Settling Time

3ppm/°C Gain TC

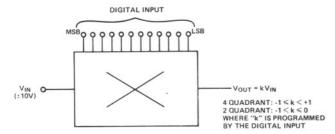

The DAC1125 is a 12-bit multiplying digital-to-analog converter. As shown in Figure 1, it functions essentially as a multiplier whose output voltage represents the product of a bipolar analog input voltage and a digitally programmed bipolar constant. This constant can be varied in 4,096 steps from -1 to 0 (Two Quadrant operation), or from -1 to +1 (Four Quadrant operation).

Figure 1. DAC1125 Functional Diagram

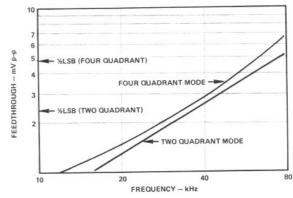

One of the primary features of the DAC1125 is its exceptionally low Four Quadrant Zero feedthrough. Analog input signals with frequencies of up to 40kHz produce a feedthrough which is guaranteed to be less than  $\pm \%$ LSB. The DAC1125 also features  $\pm \%$ LSB accuracy,  $3\mu$ s settling time to  $\pm 0.01\%$  of reading, and a  $\pm 10$ ppm/°C maximum gain temperature coefficient. The digital inputs are fully TTL/DTL compatible.

#### LOW FEEDTHROUGH

The ideal multiplying D/A converter would be one which had a feedthrough of zero. For such a device, the output voltage would be zero when "k" was programmed to be zero, regardless of the amplitude or frequency of the analog input signal. However, due to capacitive coupling, switch leakage, and other

effects, practical multiplying D/A's do have a measurable feedthrough which increases with frequency. In 12 bit devices available prior to the DAC1 25, Four Quadrant Zero feedthrough would generally exceed 2LSB for full scale input signals of 500Hz and above. The utility of these products was, therefore, greatly restricted

The DAC1125 combines innovative design with advanced CMOS technology to achieve a new standard of converter performance. Figure 2 shows the typical zero feedthrough as a function of input signal frequency for the Two Quadrant and Four Quadrant modes of operation. Note that the Four Quadrant Zero feedthrough is under ½LSB even at 40kHz.

Figure 2. Typical Zero-Code Feedthrough vs. Input Frequency (For a 20V p-p Sinewave Input)

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Route 1 Industrial Park; P.O. Box 280; Norwood, Mass. 02062 Tel: 617/329-4700 TWX: 710/394-6577

West Coast 213/595-1783

nast Wild-west 1783 312/894-3300

Mid-West Texas 2/894-3300 214/231-5094

# **SPECIFICATIONS** (Typical at +25°C and ±15VDC supplies unless otherwise noted)

| RESOLUTION                                  | 12 Bits                         | OUTLINE DIMENSIONS                                     |

|---------------------------------------------|---------------------------------|--------------------------------------------------------|

| ACCURACY                                    |                                 | Dimensions shown in inches and (mm).                   |

| Relative to Input <sup>1</sup>              |                                 | 2.01 MAX<br>(51.1)                                     |

| Two Quadrant                                | ±0.4LSB max                     | 0.41 MAX                                               |

| Four Quadrant                               | ±0.5LSB max                     | (10.4)                                                 |

| Monotonicity                                | Guaranteed                      | 0.2 MIN<br>(5.1)                                       |

|                                             | 0 to +70°C (Two Quadrant)       |                                                        |

|                                             | 0 to +50°C (Four Quadrant)      | 28 K •                                                 |

| ANALOG INPUT                                |                                 | 28 1                                                   |

| Voltage Range                               |                                 | 22 7 2.01 MAX                                          |

| Nominal                                     | ±10V                            |                                                        |

| Absolute Maximum                            | ±15V                            | 21 8 0                                                 |

| Input Impedance                             | 5kΩ (±1%) Shunted by ≈10pF      | 21 80                                                  |

| DIGITAL INPUT                               |                                 | 15 14                                                  |

| Logic Levels                                |                                 | GRID 0.1" (2.5)                                        |

| 0V ≤ Logic "0" ≤ 0.7V                       | -180µA max                      | BOTTOM VIEW                                            |

| 2y ≤ Logic '1" ≤ 5.5V                       | +10µA max                       | NOTE:                                                  |

| Coding                                      |                                 | Terminal pins installed only in shaded                 |

| Two Quadrant                                | Complementary Binary            | hole locations                                         |

| Four Quadrant                               | Positive True Offset Binary, or | Module weight: 1.6 ounces (45 grams)                   |

| $\setminus \bigcup / / \bigwedge <$         | Two's Complement                | All pins are gold plated half-hard brass,              |

| OUTPUT                                      |                                 | (MIL-G-45204), 0.019" ±0.001" (0.483<br>±0.025mm) dia. |

|                                             | ‡11V max                        | For plug-in mounting card order Board                  |

| Voltage                                     | Liv max                         | No. AC4102 @ \$15.                                     |

| Current                                     | Din Amar                        |                                                        |

| Impedance                                   | 200 F                           | DAC1125 BLOCK DIAGRAM                                  |

| Capacitive Load                             | 300pF max                       | PACES BLOCK BAIGKAIN                                   |

| DYNAMIC CHARACTERISTICS                     |                                 |                                                        |

| Feedthrough (4 Quad. Zero)                  | ±0.5LSB max, 0 to 40kHz         | 10kΩ                                                   |

| Settling Time <sup>2</sup> (to 0.01% of FS) | 3μs (10μs max)                  | ANALOG IN 28 -15V -15V -15V -15V -15V -15V -15V -15V   |

| Frequency Response <sup>3</sup>             | -3dB @ 450kHz                   | INPUT 27<br>OUTPUT 26                                  |

| Full Power Bandwidth                        | 500kHz (300kHz min)             | LSB 25 0 10kΩ                                          |

| Slew Rate                                   | 20V/μs                          | BIT 11 24 0<br>BIT 10 23 01                            |

| Output Noise <sup>4</sup>                   |                                 | 20 OUTPUT 22                                           |

| Two Quadrant                                | 5mV p-p                         | BIT 9 21 0 CONTROLLED                                  |

| Four Quadrant                               | 8mV p-p                         | BIT 9 21 CONTROLLED SPOT CMOS SWITCHES                 |

| Phase Shift <sup>5</sup>                    | -0.5° @ 5kHz                    | -V <sub>IN</sub> 19 0 1 1 1                            |

| TEMPERATURE COEFFICIENTS                    |                                 | RESISTOR                                               |

| Gain                                        | 3ppm/°C (10ppm/°C max)          | BIT 7 16 0 NETWORK                                     |

| Zero                                        | Sppin/ C (Toppin/ C max)        | 10kΩ                                                   |

| 2010                                        | 20μV/°C max                     | 10κΩ                                                   |

| Two Quadrant                                |                                 | 4=                                                     |

| Four Quadrant                               | $50\mu V/^{\circ}C$ max         |                                                        |

| Differential Nonlinearity                   | 3ppm/°C                         |                                                        |

| POWER REQUIREMENT <sup>6</sup>              |                                 |                                                        |

| Positive Supply                             | 13V to 17V @ 17mA               |                                                        |

| Negative Supply                             | -12V to -18V @ -10mA            |                                                        |

| POWER SUPPLY REJECTION                      | >80dB                           |                                                        |

| TEMPERATURE RANGE                           |                                 |                                                        |

| Operating                                   | $0^{\circ}$ to $+70^{\circ}$ C  |                                                        |

| Operating                                   | -55°C to +125°C                 |                                                        |

9 BIT 2 10 MSB IN 11 BIT 3 12 MSB OUT 13 BIT 4 14 BIT 5

PRICE (1-9)

\$295

Specifications subject to change without notice.

<sup>&</sup>lt;sup>1</sup> For a ±10V sinewave, 0 to 10kHz.

<sup>2</sup> For a 20V output step of either polarity resulting from an analog or digital input change.

<sup>&</sup>lt;sup>3</sup> For a ±10V sinewave input and output.

<sup>&</sup>lt;sup>4</sup> White noise at output as measured over a 20MHz bandwidth.

<sup>5</sup> Input to output phase shift for a ±10V sinewave output.

<sup>6</sup> If input and output voltage ranges are restricted to ±5V, the positive supply may be reduced to 8.5V and the negative supply reduced to -7V.

#### PRINCIPLE OF OPERATION

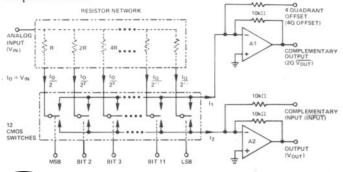

The DAC1125 consists of two identical current summing D/A's in one package. Figure 3 shows its circuitry in greatly simplified form.

Figure 3. Simplified DAC1125 Circuit

An analog voltage which can vary from -10V to +10V is applied to the analog input. The resistor network develops a series of 12 binarily weighted currents which are proportional to the input voltage. These 12 currents are directed to either of two op amp summing junctions by a series of 12 digitally controlled SPDT CMOS switches. When a logic '1' is applied to the switch control line, the corresponding bit current goes to the summing junction of A1 and when logic '0' is applied it goes to A2. The maximum current going to A1 will occur when a digital input of 1111111111111 is applied. Any other digital input will divert current to A2. Thus, for a fixed V<sub>IN</sub>, the sum of I<sub>1</sub> and I<sub>2</sub> is a constant.

# TWO QUADRANT OPERATION

In the Two Quadrant mode of operation, the COMPLEMEN-TARY INPUT and FOUR QUADRANT OFFSET inputs are grounded. The OUTPUT voltage is related to the INPUT voltage and the digitally programmed constant, k, by:

$$V_{OUT} = k V_{IN}; -0.99976 \le k \le 0$$

Table I shows the relationship between the complementary binary coded digital input and the nominal value of k for this mode of operation. Note that a 1LSB step is represented by a fractional change of 0.00024.

| DIGITAL INPUT | k        |

|---------------|----------|

| 111111111111  | 0.00000  |

| 111111111110  | -0.00024 |

| 101111111111  | -0.25000 |

| 100000000000  | -0.49976 |

| 011111111111  | -0.50000 |

| 001111111111  | -0.75000 |

| 000000000000  | -0.99976 |

Table I. Values of k for the Two Quadrant Mode (Complementary Binary Code)

The COMPLEMENTARY OUTPUT voltage is related to the IN-PUT and OUTPUT voltages by the following two expressions:

$$V_{OUT} + 2Q\overline{V_{OUT}} = -0.99976 V_{IN}$$

$2Q\overline{V_{OUT}} = -(k + 0.99976) V_{IN}$

The values of k as seen at the COMPLEMENTARY OUTPUT are not factory adjusted and may vary by ±1 percent from the ideal values.

# FOUR QUADRANT OPERATION

To achieve Four Quadrant operation, the COMPLEMENTARY OUTPUT is connected to the COMPLEMENTARY INPUT. This subtracts the output of A1 from A2. To implement offset binary code, in which a digital input of 100000000000 gives an output of 0.0V, a small amount of current must be subtracted from I1. This current, proportional to V<sub>IN</sub>, has to shift the OUTPUT voltage by ½LSB. This is done by using a third inverting op amp (not shown in Figure 3) to develop a voltage equal to -V<sub>IN</sub>. A jumper connected between the output of this op amp and the 4Q OFFSET terminal provides the necessary ½LSB offset current. The OUTPUT voltage is thus related to the INPUT voltage and the digitally programmed constant, k, by:

$$V_{OUT} = k V_{IN}; -1 \le k \le 0.99951$$

Table II shows the relationship between offset binary coded digital inputs and the nominal value of k. Note that a 1LSB step is represented by a fractional change of 0.00049.

|            | DIGITAL INPUT            | k                    |           |

|------------|--------------------------|----------------------|-----------|

|            | 111111111111             | +0.99951             |           |

| ~          | 110000000000             | +0.50000             |           |

| 17         | 100000000001             | +0.00049             |           |

|            | 100000000000             | 0.00000              |           |

| 1 1        | 01111111111              | -0.00049             |           |

| 1 1        | 010000000000             | -0.50000             |           |

| / /        | 000000000000             | -1,00000             |           |

| Table II.  | Values of k for the Four | r Quadrant Mode (Off | $\supset$ |

| set Binary | 1_ 1                     |                      | 7         |

|            |                          |                      | 7         |

|            |                          |                      |           |

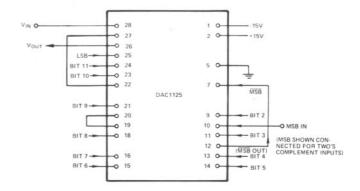

A TTL inverter (input at pin 10, but out at pin 11) is available for the purpose of inverting the MSB to obtain Two's Complement input coding in the Four Quadrant mode. Table III shows the relation between the nominal value of k and the digital input for this mode.

| DIGITAL INPUT | k        |  |

|---------------|----------|--|

| 011111111111  | +0.99951 |  |

| 010000000000  | +0.50000 |  |

| 000000000001  | +0.00049 |  |

| 000000000000  | 0.00000  |  |

| 111111111111  | -0.00049 |  |

| 110000000000  | -0.50000 |  |

| 100000000000  | -1.00000 |  |

Table III. Values of k for the Four Quadrant Mode (Two's Complement Code)

## INPUT-OUTPUT RELATIONSHIPS

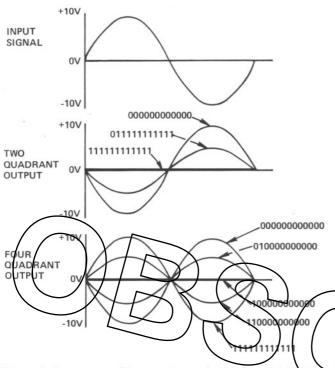

The input-output relationships are further illustrated below in Figure 4 which shows several two quadrant and four quadrant outputs for a 10V sinewave input and various digital codes.

Figure 4. Response to Sinewave Input for Various Digital Input

#### MODULE CONNECTIONS

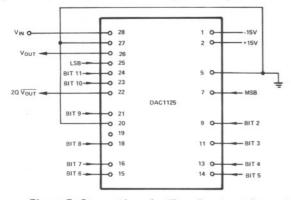

The DAC1125 is connected as shown in Figure 5 for twoquadrant, and Figure 6 for four-quadrant operation.

Figure 5. Connections for Two Quadrant Operation

Figure 6. Connections for Four Quadrant Operation

All connections between module pins, especially where pins 20 and 27 are involved, should be made with short leads. The use of shielded cable is recommended for analog signal inputs and outputs if the lead length is greater than approximately one foot (300mm). The DAC1125 has internal  $0.2\mu F$  capacitors which bypass the  $\pm 15 V$  supplies and, therefore, external bypass capacitors will only be required in exceptionally noisy environments.

#### HANDLING CONSIDERATIONS

Care must be taken in the handling of the DAC1125 to prevent electrostatic damage to its internal CMOS switches. The unit should be transported on conductive foam or other suitable material and should only be handled by properly grounded personnel. The ground pin must be connected before power is applied. Electrostatic damage, should it occur, van result in excessive power supply current, degraded performance, or total failure.

# THE AC4102 MOUNTING CARD

The AC4102 mounting card is available to assist in evaluation of the DAC1125. This 3" x 3" (76 x 76mm) printed circuit card has sockets which allow a DAC1125 to be plugged directly onto it. Each of the 28 active pin sockets is connected to a turret terminal so that connections can be easily made to the module without soldering directly to its pins.