RADECS 2017

# Radiation Evaluation of Analog Devices' RT6804-1 Radiation Tolerant Multicell Battery Monitor

Shirley C. Hart\*, Member, IEEE, Philip G. Pandol\*, Nathan R. Wendel, Member, IEEE, Ryan Peralta

Abstract—Radiation Tolerant Multicell Battery Monitor RT6804-1 from Analog Devices Inc. has been evaluated for total dose radiation performance and Single event effect characterization. Results and discussions are presented in this work.

### I. INTRODUCTION

The demand for highly advanced integrated circuits capable of surviving hash space application has been growing rapidly. These phenomena are driven by the desire to improve space systems performance and functionality with advanced technologies which currently do not exist in the space part market. To respond to the demand, Linear Technology now a part of Analog Devices, has developed the radiation tolerant line of product, RT line. The subject of this study, RT6804-1, is an enhanced product devised from the mature LTC6804-1 technology. It is one of the first products produced using the RT product definition. To ensure both the functionality and survivability of this device under space radiation environments, a series of total cumulated ionizing dose (TID) testing and heavy ion single event effect (SEE) testing has been conducted. This paper summarized the results from TID testing, both high dose rate and low dose rate, and SEE testing.

### II. DEVICE INFORMATION

The device under test (DUT) is the Analog Devices Inc.'s RT6804-1 radiation tolerant multicell battery stack

Manuscript received June 4<sup>th</sup>, 2017. This work was supported in part by Analog Devices Inc and SSL/MDA.

\*These authors contributed equally to this work

Shirley C. Hart formerly with Analog Devices Inc. now with Jet Propulsion Laboratory (4800 Oak Grove Dr, Pasadena, CA 91109 Email: Shirley.hart@jpl.nasa.gov)

Philip G. Pandol is with SSL/MDA (3825 Fabian Way, Palo Alto, CA 94303 Tel: 650-852-4527 Email: Philip.Pandol@sslmda.com)

Nathan R. Wendel is with Analog Devices Inc. (1630 McCarthy Blvd, Milpitas, CA 95035 Tel: 408-42-1900 Email: Nathan.Wendel@analog.com)

monitor. It is capable of accurately monitoring up to 12 cells per IC and stacking multiple IC's for much higher cell count. Cell voltage can range from 0 to 5V. In this work, DUTs were under standard bias for TID testing; meanwhile DUTs were tested in multiple configurations to simulate a wide range of application conditions.

### III. EXPERIMENTS

# A. Total Ionizing Dose: High Dose Rate

High dose rate irradiation was performed at the Defense Military Electronic Activity (DMEA), Sacramento, CA using the Shepard 484 Irradiator. Dose rate was set at just above 50rad/s which met MIL-STD-883 Method 1019 condition A. After parts were irradiated, to the accumulative total dose of 10krad(Si) and 15krad(Si), they were transported to Analog Devices Inc. test lab for electrical testing.

a) Bias conditions and Test Configurations

Test boards were built for TID testing, each can

accommodate at least 14 parts. A voltage ladder was

simulating the 12 battery cells each at 3.3V. Serial clock

input was 1kHz. High voltage power supply (V+) was

set to 39.6V, and low voltage supply (Vreg) was set to

5V. A total of 60 parts across five evaluation lots were

tested. 50 of these parts were biased to the above

condition, with the remaining 10 parts being as controls.

# b) Test Results and Discussion

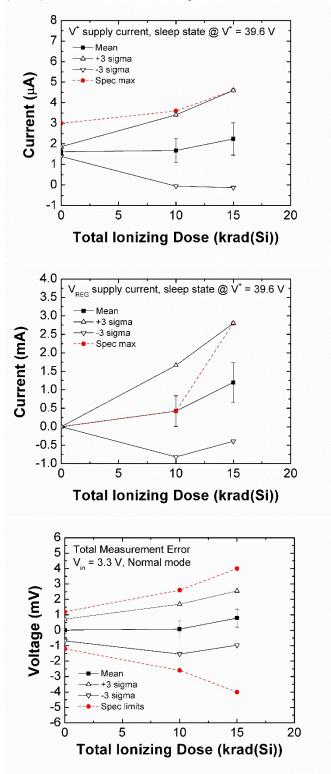

All preliminary datasheet parameters were tested and passed the specified limits.  $\pm 3\sigma$  statistic is shown for comparison purpose only. Due to the brevity of the summary, only high voltage supply current (V+), Low

Ryan Peralta is with Analog Devices Inc. (1630 McCarthy Blvd, Milpitas, CA 95035 Tel: 408-42-1900 Email: Ryan.Peralta@analog.com)

**RADECS 2017** 2

voltage supply current (Vreg) and Total measure error (TME) at normal mode were reported.

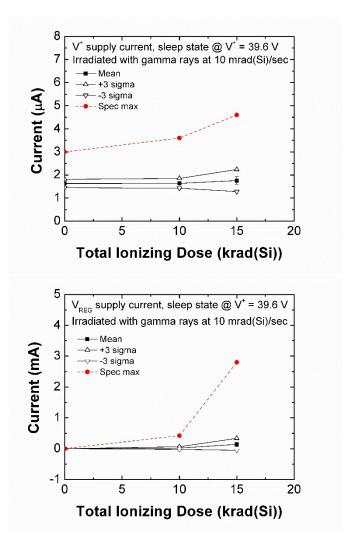

B. Total Ionizing Dose: Low Dose Rate

Low does rate irradiation was performed at the Cobham RAD Inc, Colorado Spring, CO. Dose rate was set at 10mrad/s, meeting MIL-STD-883 Method 1019 condition D. Parts were delivered over night from test facility to Analog Devices Inc. test lab in dry ice packed

shipping container, parts were tested within 48 hours after irradiation.

# a) Bias conditions and Test Configurations The DUTs were irradiated with the same test boards and same electrical bias conditions as the HDR testing. A total of 28 parts across four evaluation lots were tested. 24 of these parts were biased to the above condition, with the remaining 4 parts being as controls.

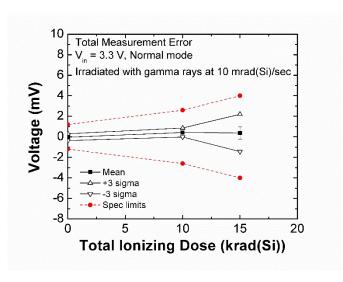

### b) Test Results and Discussion

Preliminary datasheet parameters were tested and passed the proposed limits. The degradation of most parameters was generally smaller than of the HDR exposure. This behavior could be due to the prolonged exposure time of the low dose rate experiment where the rate was 5000x lower than the HDR. This could lead to the DUTs annealing during exposure. Future work is planned to study this in detail which could be expanded upon in the future publication.

RADECS 2017 3

# C. Single Event Effect

Single Event Effect testing was performed using heavy ion at Berkeley Laboratory Cyclotron facility. Exposures were conducted using ion ranged from LET 14MeV/mg-cm2 to 58MeV/mg-cm2. Particle fluence were set around 1x10<sup>6</sup> to 5x10<sup>6</sup>, with flux adjusted to prevent multiple events aliasing.

### *a)* Bias conditions and test configurations

DUTs were biased at different battery stack voltages, cell voltages, and sources. These include 4.2V cell simulators via power supplies and 3.3V LiFePO4 battery cells. All were arranged in a daisy-chain configuration measuring 24 cells in the battery stack. The top and bottom RT6804-1 were exposed to the beam separately. The BMS chips were battery stack powered on the high and low voltage interfaces in order to approximate mission conditions. Interfaces were monitored for disruption of functionality and latchup. In order to determine rates of disruption several methods of resetting latchup were implemented.

# b) Test Setup and Procedure

21 RT6804-1 BMS chips were tested for SEE at LBNL. Custom test boards were designed to provide different methods of resetting SEL and monitoring the DUTs. Baseline measurements were made for cell voltages, thermistor inputs, and operational currents. Analog measurements were made using a Tektronix DPO3014 Digital Oscilloscope and a Dewetron DEWE-3211 digital chart recorder. A microcontroller was used to directly communicate with the SPI interface of the RT6804-1. A test loop consisting of Cell Voltage measurements, thermistor measurements, and self-test diagnostics was repeated every second for the duration of beam application.

The overall procedure of the test is as follow:

- 1.) Power DUT

- 2.) Start test script and verify measurements are within nominal limits

- 3.) Apply all beam attenuators

- 4.) Power up beam

- 5.) Slowly remove attenuators to increase flux until approximately 1e3 MeV/mg/cm<sup>2</sup>/s.

- 6.) Observe current draw for increase. If no or minimal activity then slightly increase flux to no higher than 5e3MeV/mg/cm<sup>2</sup>/s

- 7.) Log any SEU, SEFI, and SEL

# c) Test Results and Discussion

During testing 3 disruptions in operation were observed.

### 1.) SEU

Anomalous readings were occasionally observed in a cell voltage measurement, or thermistor measurement, or one of the diagnostic parameters. These were non-persistent between readings (with an interval of 1 second)

# 2.) SEFI

Persistent disruption would present in the General Purpose Input/Output pins (GPIOs) which were being used to measure thermistors.

# 3.) SEL

A single event latchup would present on the low voltage input to the RT6804-1 (Pin 37 Vreg).

Mission requirements allow for non-persistent anomalous readings caused by SEU. Error Correction Code is incorporated in software. Greater characterization of SEU is left to a more extensive paper and further testing.

SEFI were present in the thermistor measurements. This would present a complete drop out of measurement on the affected pin resulting in measurement of a few mV where 1.5V was expected.

A reset circuit was implemented to allow the test board to scan for SEFI so as to positively detect and reset the SEFI.

The RT6804-1 has 5 GPIO pins. It was noted that GPIO1 and GPIO2 do not suffer from SEFI. The distribution of SEFI amongst GPIO3-GPIO5 is fairly uniform.

RADECS 2017 4

|       | GPIO1 | GPIO2 | GPIO3 | GPIO4 | GPIO5 |

|-------|-------|-------|-------|-------|-------|

| Ar    | 0     | 0     | 4     | 3     | 2     |

| Cu    | 0     | 0     | 3     | 1     | 27    |

| Kr    | 0     | 0     | 5     | 3     | 0     |

| Ag    | 0     | 0     | 70    | 12    | 16    |

| Xe    | 0     | 0     | 94    | 121   | 125   |

| Au    | 0     | 0     | 2     | 13    | 0     |

| Total | 0     | 0     | 178   | 153   | 170   |

The reset logic was inconsistent for much of the test until a permanent solution was determined. Thus, much of the data is inconsistent. Future work will focus on more accurately characterizing the incidence rate of SEFI.

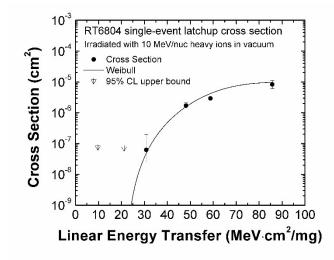

SEL was observed on the low voltage (Vreg) pin of the RT6804-1. When not current limited this could draw up to 1A of current. Some SEL were observed consuming as little as 38mA. SEL was not observed on any other pin of the RT6804-1.

When the RT6804-1 enters SEL the IC becomes non-responsive and must be reset. Further, if powered off of a battery stack the IC would represent a significant parasitic drain on the battery.

A reset circuit was implemented which would detect SEL and reset the condition.

Fig. A cross section vs LET with Weibull curve fitted.

Weibull fit for orbital error-rate:  $\sigma = \sigma_0 [1 - e^{-((L-L_0)/w)^s}]$  Weibull Fit Parameters:

| Wellouif I it I didifferens. |    |     |            |  |  |  |

|------------------------------|----|-----|------------|--|--|--|

| $L_0$                        | W  | S   | $\sigma_0$ |  |  |  |

| 21                           | 45 | 3.5 | 1E-0e      |  |  |  |

Note: Fit parameters are for reference only.

# IV. DISCUSSION AND FUTURE WORK

RT6804-1 is rated to 10krad(Si) TID level, with possible 15krad(Si) limits being discussed, both high dose

rate and low dose rate testing yield satisfactory result complying with the proposed specification limits. However, fabrication lot to lot variation regarding performance has been observed during testing. This indicates that Radiation Lot Acceptance test is crucial for all flight lots. User should consult Analog Devices for additional information. The RT6804-1 is shown to be robust in the presence of high energy heavy ions. The combination of visual inspection and die probing analysis of the DUTs post-SEE testing indicated no damage from SEL or SEFI. The RT6804-1 proved to be able to be consistently recovered from a state of SEL and continue to perform to all limits specified in the datasheet.

Future tests will focus on HDR and LDR testing and comparison, characterizing the SEU rate, as well as determine the susceptibility to SEFI at different LET levels. Additionally, more LET should be tested as well to more accurately determine the LET threshold.

# **ACKNOWLEDGMENT**

The authors would like to thank Josh Jones, David Hutchinson, Raj Ramchandani, TJ Fure and Bob Scott from Analog Devices for their assistance with the DUT technology analyses. Additional thanks to James Loman, Frankie Wong, Katherine McDaniel, Catherine Keys, Fredy Uruchima, Anthony Applewhite, MaryCarmen Gonzalez-Dorbecker from SSL/MDA for their assistance with the SEE testing and data analysis.

# **REFERENCES**

[1] Test Method Standard, Microcircuits, MIL-STD-883, Dept. Defense, Supply Center, Columbus, OH, Jun. 18, 2004. http://www.dscc.dla.mil/Downloads/Mil-spec/Docs/MIL-STD-883/std883.pdf

[2] Dept. Defense, Defense Supply Center, Columbus, OH, "MIL-PRF-38535 Integrated Circuits (Microcircuits) Manufacturing, General Specification," Mar. 16, 2007. http://www.dscc.dla.mil/Downloads/MilSpec/Docs/MIL-PRF-38535/prf38535.pdf

http://cds.linear.com/docs/en/datasheet/680412fc.pdf

[3] K. Kruckmeyer, J. S. Prater, B. Brown, T. Trinh, "Analysis of low dose rate effects on parasitic bipolar structures in CMOS processes for mixed-signal integrated circuits", *IEEE Trans. Nucl.Sci.*,

pp. 1023-1031, June 2011.

vol. 58, no. 3,