# 2-12. Wideband AC V Functional Description (Option -03)

The Wideband AC Voltage module (Option -03) consists of the Wideband Oscillator assembly (A6) and the Wideband Output assembly (A5). There are two wideband frequency ranges:

- o 10 Hz to 1.1 MHz

- o 1.2 MHz to 30 MHz

During operation between 10 Hz and 1.1 MHz, output from the Oscillator Output assembly is routed to the Wideband Output assembly where it is amplified and attenuated to achieve the specified amplitude range. The output is connected to the 5700A front panel WIDEBAND connector. Operation between 1.2 MHz and 30 MHz works the same way, except the input to the Wideband Output assembly is the ac signal from the Wideband Oscillator assembly.

### 2-13. DC Current Functional Description

DC current is generated in five ranges:

- o 20 uA 220 uA

- o 220 uA 2.2 mA

- o 2.2 mA 22 mA

- o 22 mA 220 mA

- o 2.2A

All current ranges except 2.2A are generated by the current portion of the Current/Hi-Res assembly. These currents are created by connecting the output of the DAC assembly, set to the 22V range, to the input of the Current assembly. The Current assembly uses this dc voltage to create the output current. The current output can be connected to the AUX CURRENT OUTPUT binding post by relays on the Current assembly, to the OUTPUT HI binding post by relays on the Current, Switch Matrix, and Analog Motherboard assemblies, or to the 5725A via the B-CUR line by relays on the Analog Motherboard assembly and Rear Panel assembly.

The 2.2A range is an extension of the 22 mA range. The 22 mA range output from the Current assembly is amplified by a gain of 100 by the High Voltage/High Current assembly operating in conjunction with the Power Amp assembly and the High Voltage Control assembly. The 2.2A current range is routed back to the Current assembly where it is connected to either the AUX CURRENT OUTPUT binding post, the OUTPUT HI binding post, or the 5725A in the same manner as the lower current ranges.

## 2-14. AC Current Functional Description

AC current is created in the same manner as dc current, except the input to the Current assembly is the ac voltage from the Oscillator Output assembly set to the 22V range. The switching between ac and dc is carried out on the Switch Matrix, Oscillator Control, Oscillator Output, and DAC assemblies.

#### 2-15. Ohms Functional Description

Two assemblies function as one to supply the fixed values of resistance:

- o Ohms Main assembly (A10)

- o Ohms Cal assembly (A9)

All of the resistance values except the 1 ohm, 1.9 ohm, and short are physically located on the Ohms Main assembly. The 1 ohm, 1.9 ohm, and short are physically located on the Ohms Cal assembly. The desired resistance is selected by relays on these Ohms assemblies and is connected to the 5700A binding posts by relays on the Analog Motherboard. The Ohms Cal assembly also contains the appropriate circuitry to enable the 5700A to perform resistance calibration. Once calibrated, the 5700A output display shows the true value of the resistance selected, not the nominal (e.g., 10.00031 kilohm, not 10 kilohm).

Four ohms measurement modes are available:

- o For the two-wire configuration, measurement with or without lead-drop compensation sensed at the binding posts of the UUT (using the SENSE binding posts and another set of leads), or at the ends of its test leads is available for 19 kilohms and below.

- o Four-wire configuration is available for all but the 100 megohm value.

#### 2-16. SYSTEM INTERCONNECT DETAILED CIRCUIT DESCRIPTION

The Motherboard assembly contains the Digital Motherboard assembly (A4), and the Analog Motherboard assembly (A3). These two Motherboards are mechanically fastened together with screws. They are electrically connected by connectors P81 and P82 on the Digital Motherboard and connectors J81 and J82 on the Analog Motherboard. AC voltage taps from the Transformer assembly (A22) are connected to the Analog Motherboard through these connectors. Refer to Figure 2-4 for an overview of system interconnections. Figure 2-4 continues on the reverse side, showing system grounds.

#### 2-17. Digital Motherboard Assembly (A4)

The Digital Motherboard contains the line-select switches, line fuse, power switch, a fiber-optic transmitter (J73), and a fiber-optic receiver (J74). It also contains connectors for the Transformer assembly (A22), Digital Power Supply assembly (A19), CPU assembly (A20), Front Panel assembly (A2), Rear Panel assembly (A21), and the two 24V dc fans mounted in the chassis.

The fiber-optic receiver and transmitter provide the serial communication link between the CPU on the unguarded Digital Motherboard and the Regulator/Guard Crossing on the guarded Analog Motherboard.

## 2-18. Transformer Assembly (A22)

The Transformer assembly receives ac line inputs routed through the A4 Digital Motherboard. This assembly supplies outputs throughout the 5700A, all of which are routed through the A4 Digital Motherboard.

The Transformer assembly, the filter portion of the Filter/PA Supply assembly (A18), and the regulator portion of the Regulator/Guard Crossing assembly (A17) create the system power supply for all analog assemblies. The Transformer assembly also supplies ac voltages to the Digital Power Supply assembly which generates five regulated dc voltages for use by the CPU, Front Panel assembly, Rear Panel assembly, and the cooling fans.

# 2-19. Analog Motherboard Assembly (A3)

The Analog Motherboard contains the connectors for all assemblies in the guarded section of the calibrator. The Analog Motherboard also contains 13 relays, a fiber-optic transmitter, a fiber-optic receiver, a cable for binding post connections, and two cables for the interface to the Rear Panel assembly.

Table 2-1 lists Analog Motherboard connectors.

Table 2-1. Analog Motherboard Connectors

| MOTHERBOARD                                                                                                                                                                       | CONNECTED TO                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| CONNECTOR                                                                                                                                                                         | ASSEMBLY                                  |

| J101 J111 J201 and J202 J211 and J212 J301 and J302 J311 and J312 J401 and J402 J501 and J502 J511 and J512 J601 and J602 J611 and J612 J701 and J702 J801 and J802 J901 and J902 | Ohms Cal assembly (A9) DAC assembly (A11) |

The fiber-optic transmitter (J72) and the fiber-optic receiver (J71) provide the serial communication link between the Regulator/Guard Crossing assembly and the CPU assembly on the unguarded Digital Motherboard.

#### SYSTEM INTERCONNECT DETAILED CIRCUIT DESCRIPTION

Control lines for relays K1-K10 and K13 on the Analog Motherboard assembly are generated on the Switch Matrix (A8) assembly. Control line RLY11\*, which controls relay K11, is generated on the Current/Hi-Res assembly (A7). Control line RLY12\*, which controls relay K12, is generated on the the Rear Panel assembly (A21).

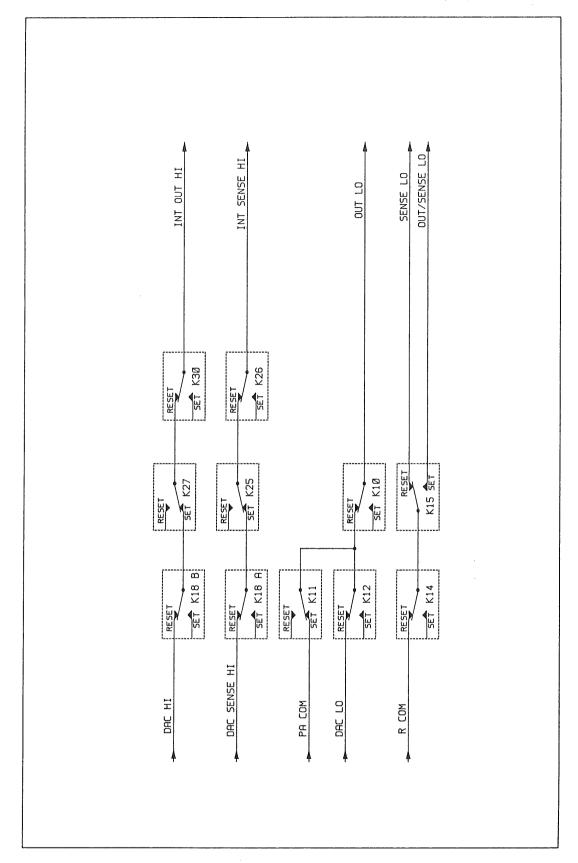

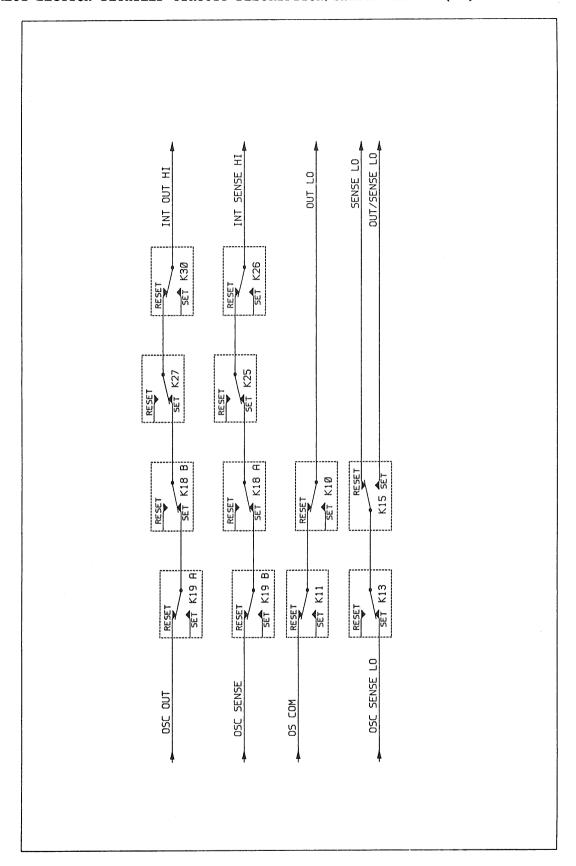

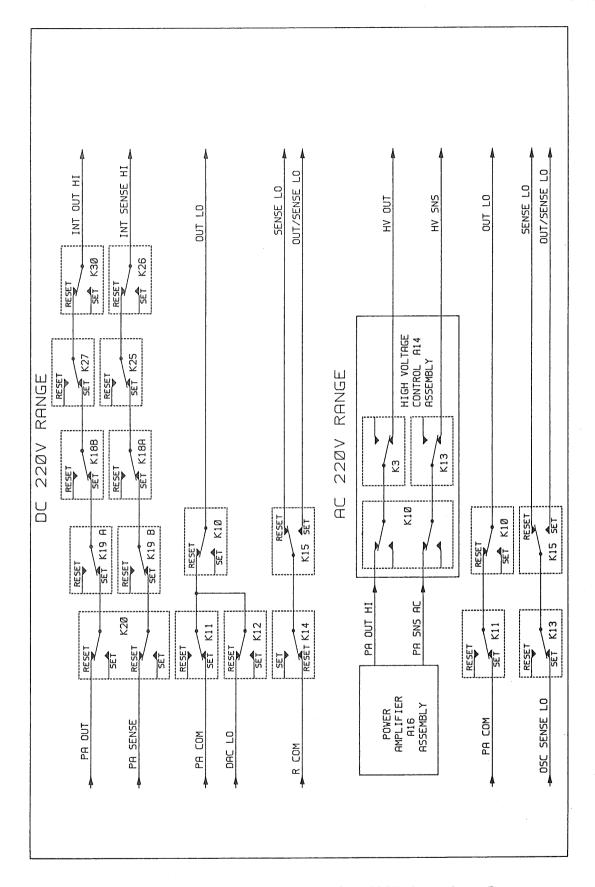

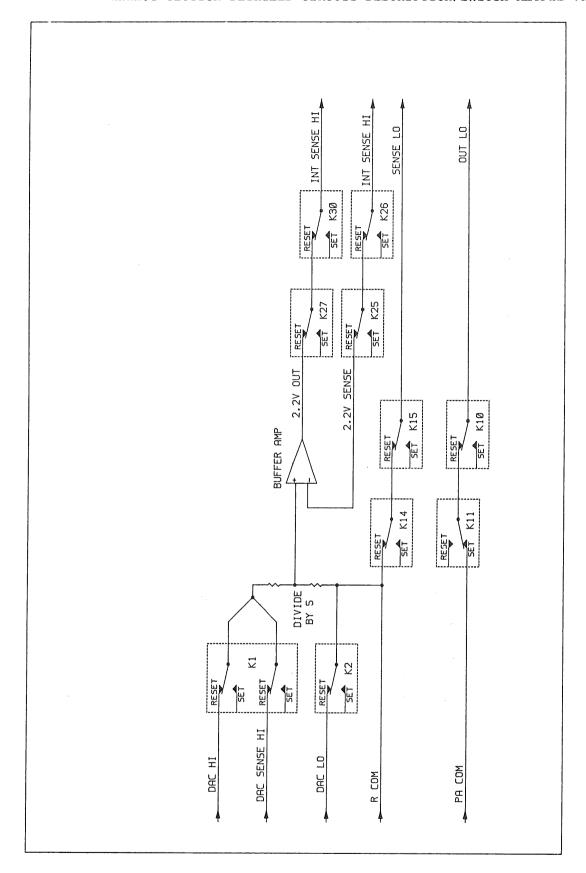

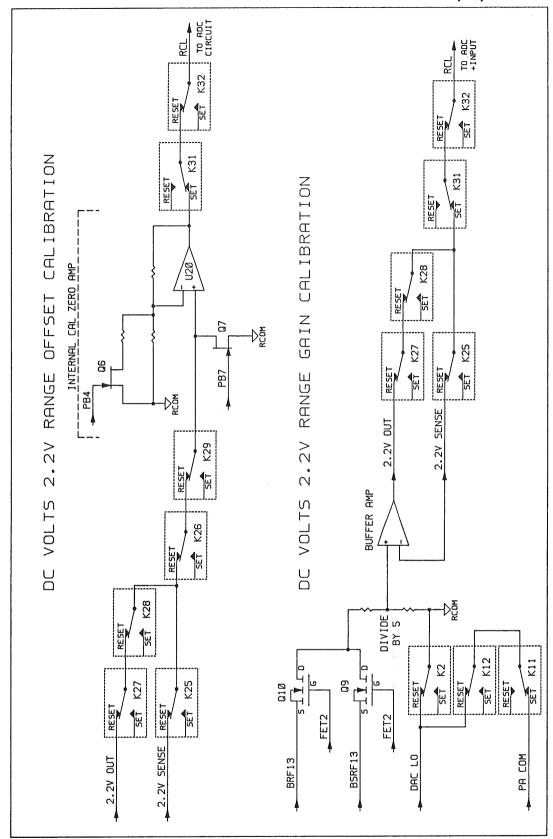

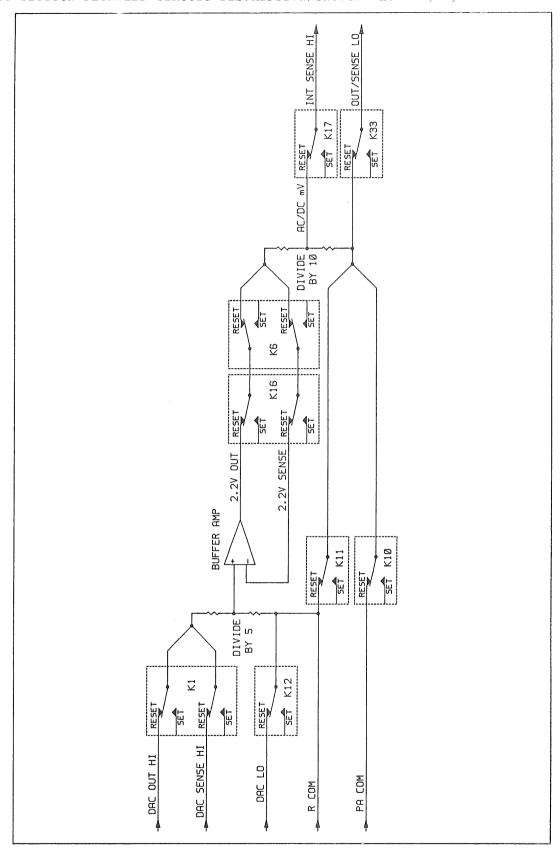

Line INT OUT HI is the calibrator output for ac voltage operation in the 22V range and below, dc voltage operation in the 220V range and below, all resistance functions, and all ac/dc current ranges. Relays on the Current assembly route the current output to the AUX CURRENT OUTPUT binding post via the I OUT line if so selected by the operator. INT SENSE HI is the sense high path during these modes of operation. INT OUT HI is connected to the OUTPUT HI binding post through relay K1. INT SENSE HI is connected to the SENSE HI or OUTPUT HI binding post through relays K2 and K3.

Line HV OUT is the calibrator output for dc voltage operation in the 1100V range, and ac voltage operation in the 220V and 1100V ranges. Line HV SENSE is the sense high path during these modes of operation. HV OUT is connected to the OUT HI binding post through relays K9 and K1. HV SENSE is connected to the SENSE HI or OUTPUT HI binding post through relays K10, K2, and K3.

The 5725A Amplifier output is B OUT HI and the sense high path is B SNS HI. When the 5725A is active, B OUT HI is connected to the OUT HI binding post through relays K4 and K1. When the 5725A Amplifier is inactive, B OUT HI is connected to GUARD CHASSIS by relay K12. Line B SNS HI is tied to B OUT HI through diode clamps CR1 and CR2 and is connected to the SENSE HI or OUTPUT HI binding post through relays K5, K2, and K3.

The cable from the Motherboard to the binding posts consists of six insulated wires and six shields, each with its own drain wire. The OUT HI line, SENSE HI line, OUT/SENSE HI line and AUX CURRENT line each connect to an insulated wire and each has a shield around the wire. These shields are connected to OUT LO, SENSE LO, OUT/SENSE LO, and I/V GUARD, respectively. The I/V GUARD line is connected to I GUARD during operation in the current mode or V GUARD during operation in the voltage mode. This selection is done by relay K11.

When the 5700A is in standby, all binding posts are open-circuited except the GROUND binding post. In addition, GUARD CHASSIS is connected to S COM by K6. When in the operate condition, this connection is broken (K6 energized) and GUARD CHASSIS is connected to V GUARD via K7, which goes to the GUARD binding post, and to OUT LO via K8. GUARD CHASSIS is also connected to OSC LO GD by K13 except during ac or dc millivolt operation, when instead OSC LO GD is connected to S COM.

### 2-20. Front/Rear Binding Posts

An internal cable can be configured to enable either the front panel or rear panel binding posts. When compared to front panel binding posts, the rear panel provides the same OUTPUT HI, OUTPUT LO, SENSE HI, SENSE LO, AND V GUARD functions. Also, the rear panel provides an I GUARD (current guard) connection for use when the 5700A is supplying low-level ac current through a long cable. Use of the I GUARD connection removes errors introduced by leakage through such cables. The rear panel binding posts do not provide an AUX CURRENT OUTPUT connection. The procedure to disable the front panel binding posts and enable the rear panel binding posts is to be done at Service Centers, although it is described in this manual in Section 4.

### 2-21. Rear Panel

The Rear Panel assembly provides physical and electrical connections for the auxiliary amplifiers, along with RS-232-C and IEEE-488 interface connections. Relays on the Rear Panel assembly are used as the interfaces for the 5205A, 5215A, 5220A, or 5725A amplifiers, or for switching the PHASE LOCK IN and VARIABLE PHASE OUT signals.

Three Auxiliary Amplifiers can be physically connected to the Rear Panel assembly of the 5700A: the 5725A at J7, the 5220A at J4, and either 5205A or 5215A at J3. Only one amplifier can be in use at one time.

- o The Rear Panel assembly provides relay switching for 5725A signals. Voltage outputs from the 5725A are routed to the binding posts on the 5700A. Current outputs are sourced at the 5725A OUTPUT binding posts. An alternate configuration is also available, allowing for routing of 5700A current outputs to the 5725A OUTPUT binding posts.

- o When the 5220A (current output) is selected via the front panel, the output of the 5700A is routed to connector J4 on the rear panel, which is the interface to the 5220A.

- o When the 5205A (ac and dc volts) or 5215A (ac volts only) function is selected via the calibrator keyboard, the output of the calibrator is routed to connector J3 (pins 1, 9, 2, and 10) on the Rear Panel assembly.

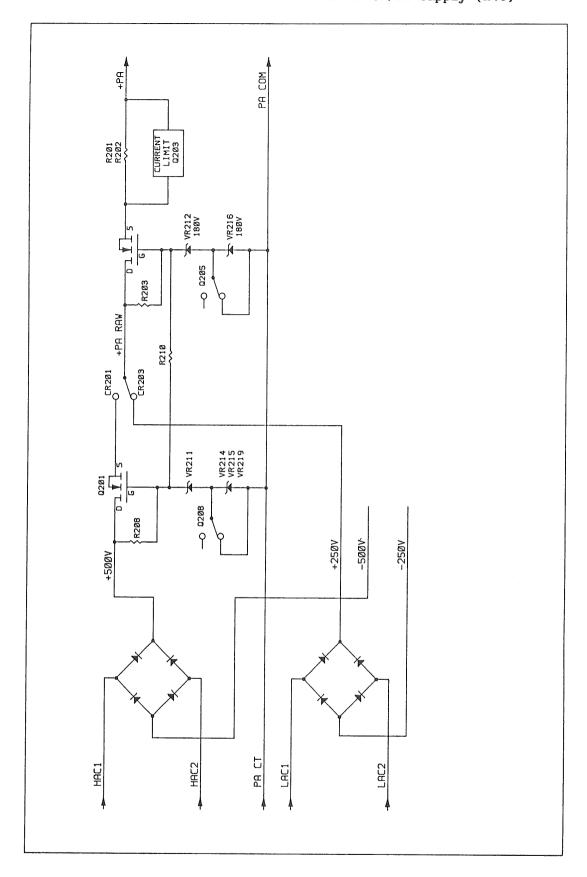

## 2-22. Power Supply

The Filter/PA Supply assembly (A18) incorporates two sections. The first section contains filters and regulators for some of the in-guard low-voltage supplies, and the second contains the power supply for the Power Amplifier output. Theory for each section is discussed separately.

### 2-23. DIGITAL SECTION DETAILED CIRCUIT DESCRIPTION

Detailed descriptions of each assembly in the digital section are provided here. Simplified schematics and block diagrams are provided to supplement the text.

## 2-24. Digital Power Supply (A19)

The Digital Power Supply assembly receives ac voltages from the transformer and provides five regulated dc voltages for use by the CPU, Front Panel assembly, Rear Panel assembly, and the cooling fans. All power supply voltages are referenced to COMMON, which is the transformer center tap for the  $\pm$  12V supplies. Test points at the top of the assembly can be used to check unregulated input voltages, and regulated dc output voltages.

Table 2-2 lists the supplies generated by the Digital Power Supply.

|    |                                                 |               | NOMINAL<br>OUTPUT | DLERANCE       | CURI |                 | RATED<br>  OUTPUT                         |  |

|----|-------------------------------------------------|---------------|-------------------|----------------|------|-----------------|-------------------------------------------|--|

| ÷. | 75V OUT  <br>35V OUT  <br>12 VOLTS <br>12 VOLTS | •             | 73V<br>35V<br>12V | 8%<br>7%<br>5% | 1 1. | mA<br>mA<br>.5A | 100 mA<br>  40 mA<br>  700 mA<br>  450 mA |  |

| +  | 5V  <br>OMMON                                   | TP12 <br>TP13 | . — •             | 5%             | •    | .4A             | 2.0A                                      |  |

Table 2-2. Supplies Generated by the Digital Power Supply

#### 2-25. +5V POWER SUPPLY

The unregulated +5V supply uses CR25-CR28 in a full-wave rectifier configuration with filter capacitors C12, C13, and C14. Capacitors C20 and C21 filter out high-frequency noise. Inductor L8 is a common-mode choke and C11 is a bypass capacitor. The regulator is fused by 3.15A slow-blow fuse F5.

The regulated +5V is generated by three-terminal low-dropout +5V regulator U3 with heat sink. The regulator's output voltage is increased about 0.2V by CR35, a germanium diode connected between the regulator's ground pin and COMMON. Capacitor C14 is for bypass. Capacitor C23 filters out high-frequency noise. Diode CR29 protects the regulator against input shorts, and diode CR30 protects the regulator from reverse voltage. Inductor L7 and C16 further filter the output to P41.

### 2-26. + 12V POWER SUPPLIES

A full-wave rectifier made of diodes CR17-CR20 and filter capacitors C6 and C7 generate the unregulated +12V and -12V supplies. AC inputs are fused by F3 and F4, both 2A slow blow.

The regulated +12V supply is generated by a three-terminal +12V regulator U1 with heat sink. Capacitors C5 and C9 are for bypass. Diode CR21 protects the regulator from input shorts, and diode CR23 protects the regulator from reverse voltage. Capacitor C22 filters out high frequency noise.

Three-terminal -12V regulator U2 with heat sink generates the regulated -12V supply. Capacitors C8, C10, and C19 are for bypass. Diode CR22 protects the regulator from input shorts, and diode CR24 protects the regulator from reverse voltage.

Inductors L3-L6 filter the regulated outputs. R7 further isolates the  $\pm 12V$  FAN lines from the  $\pm 12V$  power lines. The  $\pm 12V$  FAN and  $\pm 12V$  FAN lines power the two  $\pm 12V$  fans inside the calibrator.

### 2-27. +35V POWER SUPPLY

The +35V power supply powers the grid drivers and anode drivers on the front panel output display circuitry.

A full-wave rectifier made of diodes CR9-CR12 and filter capacitor C3 generate the unregulated +35V supply. Its input is fused by F2, a 0.125A slow-blow. Capacitor C18 is for bypass. Capacitor C25 filters out high frequency noise.

Zener diodes VR14, VR15 and transistor Q5 generate the +35V regulated output. Zener diodes VR14 and VR15 (both 18V) make up the control element which sets the output voltage. Transistor Q5 is used as an emitter follower. CR13 is the constant current source supplying current to the zener diodes and the base of Q5. Components R5 and Q6 make up the current-limiting circuit. During an over-current condition, the voltage drop across R5 turns Q6 on, thus drawing current away from the base of Q5 and limiting current flow to the output. Diode CR16 protects this circuit from reverse voltage and C4 is a bypass capacitor. Inductor L2 filters the regulated output. Resistor R13 is a bleed-off resistor for C3.

## 2-28. +75V POWER SUPPLY

The +75V power supply powers the grid drivers and anode drivers on the front panel control display circuitry.

A full-wave rectifier made of diodes CR1-CR4 and filter capacitor C1 generate the unregulated +75V supply. Its input is fused by F1, a 0.315A slow-blow. Capacitor C17 is for bypass. Capacitor C24 filters out high frequency noise.

The +75V regulated output is generated by 36V zener diode VR6, 39V zener diode VR7, and transistors Q1 and Q3. Zener diodes VR6 and VR7 set the output voltage. Transistors Q1 and Q3, in a Darlington configuration for current gain, are used as an emitter follower. Transistor Q4, zener diode VR5, and resistors R2 and R3 make up the constant current source supplying current to the zener diodes and the base of Q3. Current limiting is performed by R1 and Q2 in the same manner as in the +35V supply. Diode CR8 protects the circuit from reverse voltage and C2 is a bypass capacitor. Inductor L1 filters the regulated output. Resistor R6 is a bleed-off resistor for C1.

#### 2-29. +35V AND +75V SHUT-DOWN CIRCUIT

The +35V and +75V high voltage supplies are shut down when a fault occurs in the control display refresh circuitry. This shut-down circuit prevents the Control Display and Output Display from burning out, and also verifies that the master clock is generating control signals for both displays.

During normal operation, 75VSD is low, turning Q10 off. Line RESETL pulls the base of Q9 high through R9, turning Q9 on. This action in turn pulls the junctions of CR31-CR32 and CR33-CR34 low, turning Q7 and Q8 off. The +75V and +35V constant-current sources can then supply the appropriate zener diodes and drive the bases of the respective emitter followers.

When a display refresh fault occurs, the 75VSD line on P41 pin 5C, coming from the Front Panel assembly, goes high. this signal, pulled up by R4, drives the base of Q10 through base resistor R11. Transistor Q10 then saturates, pulling the base of Q9 near ground, turning Q9 off. On power-up or during a CPU reset, the RESETL signal is low, pulling the base of Q9 near ground through R9, also turning Q9 off. Resistor R12 is a turn-off resistor for Q9. Diodes CR31 and CR33 are in a wired-OR configuration. When Q9 is saturated (on), CR31 and CR33 pull their respective junctions to CR32 and CR34 near ground, turning Q7 and Q8 off. When Q9 is off, the junctions are pulled high through R8 and R10, saturating Q7 and Q8 (on). When on, Q7 removes the base drive from Q3, shutting down the +75V supply. Similarly, Q8 removes the base drive from Q5, shutting down the +35V supply.

Diodes CR32 and CR34 simply insure that Q7 and Q8 are off when Q9 is on. Resistor R8 guarantees that Q7 will hold the +75V supply off until it drops below 15.6V, and R10 holds the +35V supply off to 7.8V.

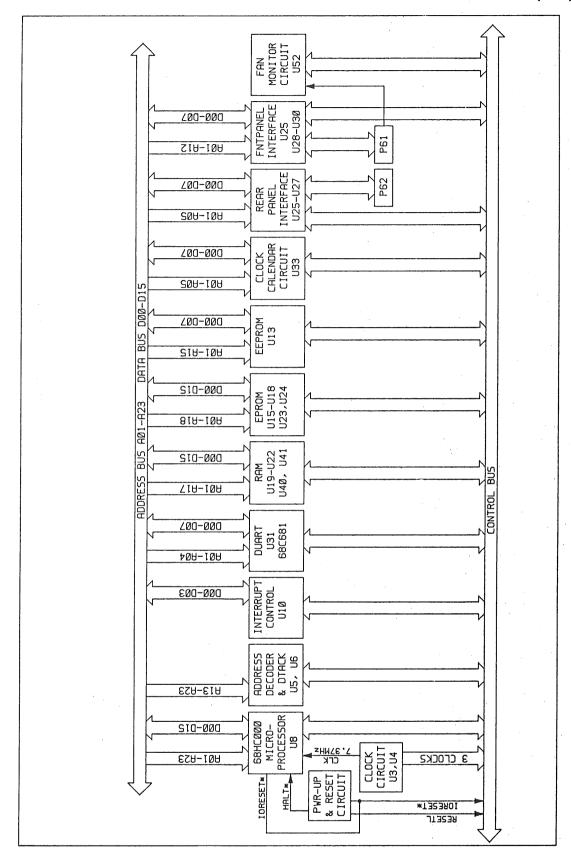

### 2-30. CPU (Central Processing Unit, A20)

The CPU (Central Processing Unit) for the 5700A is a single-board computer based on a 68HC000 microprocessor. The CPU assembly communicates with the Guarded Digital section, the Front Panel assembly, and the Rear Panel assembly. The board can be divided into three primary areas:

- o The microprocessor and its support circuitry

- o Memory

- o Peripheral chips and I/O interfaces

Microprocessor support circuitry consists of a power-up and reset circuit, clock generation, a watchdog timer, address decoders and dtack generator, bus error timeout, and interrupt controller.

Figure 2-5 is a block diagram of the CPU assembly. Table 2-3 is a glossary of the acronyms used in the text and schematic for the CPU assembly.

Figure 2-5. CPU Assembly Block Diagram

Table 2-3. CPU Acronym Glossary

|                | , and the same of |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A01-A23        | Address lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADCLKCS*       | Clock/calendar (U33) chip select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AS*            | Address strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BERR*          | Bus error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BGACK*         | Bus grant acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BR*            | Bus request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| BRPDRTINT*     | Rear panel DUART interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BRPDTK*        | Rear panel data transfer acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BRPIEEEINT*    | Rear panel IEEE-488 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CLKCALINT*     | Clock/calendar interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| D00-D15        | Data lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DOGCLR         | Dog clear (clears watchdog timer)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DOGINTH        | Dog interrupt (interrupt from watchdog timer)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DRTDTK*        | DUART data transfer acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DTACK*         | Data transfer acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| E              | Enable for 6800 family devices (737.28 kHz clock)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| EXDUARTINT*    | External DUART Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| FAN1           | Signal monitoring fan 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FAN2           | Signal monitoring fan 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FANINT*        | Fan monitor interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FC0            | Function code output 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FC1            | Function code output 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FC2            | Function code output 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FPDTK*         | Front panel data transfer acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FRNTPNLCS*     | Front panel chip select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FRNTPNLEN*     | Front panel enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GCDRTCS*       | Guard crossing DUART chip select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |