For example, if the duty cycle of the first channel is 10% and the second channel 50%, the overall average voltage would be:

$(0.1 \times 13V) + (0.5 \times 0.78 \text{ mV}) = 1.300390V.$

The duty cycle resolution is 0.0024%, which gives a first channel resolution of 0.309 mV and second channel resolution of 18.5 nV.

The duty cycle control circuitry creates the two digital square waves for the first and second channels. These two waveforms are first run through optocouplers for isolation and then into analog switching and level shifting circuits. These circuits derive the proper signals to switch the input of the filter at the levels explained above.

2-102. DAC ASSEMBLY DIGITAL CONTROL

The digital control circuit is located on page 6 of the DAC schematics. The 82C55 Programmable Peripheral Interface IC (U31) is the heart of this circuit.

This IC, which is under software control via the guarded digital bus, has three ports that provide 24 static lines. Port A (PAO-PA7) is configured as a read-only port register. It passes the add readings from the ADC IC (U25) to the guarded digital bus.

PBO-PB4 of port B control relays K1-K4 and K6-K8 via relay drivers U33 and U34. PBO is also control line DAC OUT SEL used to turn on FET Q25, via FET Q26, and connect RCOM to SCOM during calibrator operation in the ac function.

PC7 of port C, buffered by U8A, provides the enable for these relay drivers. Relay driver U33 controls latching relays K7 and K8. Outputs from U33 are also used by Relay driver U34 to control latching relays K1-K6. PB5-PB7 are decoded by U32 to create six control lines. These control lines are used to select one input to the adc amplifier -input. K5SEL is an input to the relay drivers to control latching relay K5. The remaining five control lines are used by comparators in U35 and U36. These comparators provide the proper level shifting to create control lines BSRF6 SEL, BSRF13 SEL, REF6 SEL, REF13 SEL, and ADC COM SEL. These control lines are used to control FETs on the DAC Buffered Reference SIP assembly (A11A2).

PCO of port C is buffered by U8 (B and C) and routed through opto-isolator U37 to create RANGE SELECT, which sets the DAC to the 11V or 22V range. PC1 is used in the duty cycle control circuit to shut off the 8 MHz clock via buffer U8F and the first channel via OR gate U9D. This is done during calibrator operation in the resistance function. PC2 controls a FET in U23 for use in self-diagnostics. PC3 and PC4 are level-shifted by comparators in U36 before they are used to control FETs in U23. PC5 of port C is connected to a comparator in U36. This comparator provides the proper level shifting to create control line ADCAMP OUT SEL to control a FET in U23. PC6 is control line ADC TRIGGER which triggers the adc (analog-to-digital converter) IC U25. AO, A1, and CS\*, from the guarded digital bus, are used by OR gates in U9 (B and C) to create control line ADC READ for use by the adc IC U25.

### ANALOG SECTION DETAILED CIRCUIT DESCRIPTION/DAC (A11)

2-103. DAC ASSEMBLY REFERENCE CIRCUITRY

The reference circuitry is on the reference hybrid, located on the HR5 assembly. The HR5 assembly contains a ceramic substrate reference hybrid bonded to a resistor network.

All components on this assembly are surface mount devices, except U6 and U7. The resistors are screened with a thick film paste. Associated resistors, capacitors, and zener diodes are mounted on the main board to supply this hybrid with the appropriate power and ground returns.

As previously explained, the amplitudes of the pulse width modulated signals for the first and second channel are assumed to be fixed. Any change in amplitude shows up as an error on the output of the DAC. Since the reference is used to determine the amplitude, it must be very stable and generate little noise.

The 13V reference contains two cascaded 6.5V temperature compensated transistor/zener diode pairs called ref amps (U6 and U7). The excellent temperature characteristics of the ref amps are obtained by biasing the collector current on their transistors with a value such that the TC (temperature coefficient) of its base-emitter junction cancels the TC of the zener diode. Since the base-emitter junction and the zener diode are in series, the result is a near zero TC.

Correct bias currents are achieved with a thin-film resistor network in a surface-mount package mounted on the hybrid.

The reference circuit is designed such that the effects of the thin-film resistors and op amp errors are second order. Thus, accuracy is determined almost entirely by the ref amps.

To further reduce the effects of ambient temperature variations, the hybrid is heated to a constant 62 oC by the heater control circuitry on page 1 of the DAC schematic.

Temperature is sensed near the ref amps by a thermistor (RT1). If the substrate temperature changes, the thermistor resistance changes. This creates a correction voltage to the base of Q2 (on the main board). This, in turn, causes the power into the heater resistor, which is screened on the back of the substrate, to increase or decrease as necessary to maintain a stable temperature.

Thermal runaway is prevented by a protection circuit. Once the substrate temperature reaches approximately  $67^{\circ}\text{C}$ , the change in resistance of RT2 causes Q9 to turn on. As transistor Q9 turns on, it steals base current from Q1 on the main board, which brings it out of saturation. This breaks the current path through the heater resistor. This condition exists only if there is a failure.

The exact value of the reference is determined during calibration. Because of the stability of the reference, it can be used for future internal calibration procedures to remove short term errors in the calibrator.

The 13V output, REF13 HI, is from pin 9 and REF13 SENSE is on pin 12. Also, a 6.5V reference line, REF6, is brought out on pin 14 of the reference for use during calibration.

In order to make these reference voltages available to other assemblies, the 6.5V and 13V references are buffered on the DAC Buffered Reference SIP assembly (A11A2). This assembly also contains the circuitry to switch the references and buffered references into the input of the adc during calibrator calibration. Refer to the section on the DAC Buffered Reference SIP for more information.

## 2-104. DUTY-CYCLE CONTROL CIRCUIT

Duty-cycle control circuitry is pictured on page 3 of the schematics. DAC output voltages are represented in software by what are called first and second channel counts. Each count is a 16-bit number which is sent to the DAC assembly via the guarded digital bus.

For example, a first channel count of 20,000 (in decimal) represents a DAC output voltage of approximately 6.5V (half the reference voltage).

The first function of the duty-cycle control circuitry is to convert each count into a stable, TTL level, square wave, with a duty cycle proportional to the numeric value of the count. This is accomplished with the 82C54 programmable interval timer (U6).

A low-level 8 MHz clock is generated on the Regulator/Guard Crossing assembly (A17) and routed to the DAC assembly via the motherboard. This low-level clock, CLK and CLK\*, is amplified to a TTL level by comparator U7 to generate the 8 MHz clock which is used by U6 and the adc IC U25.

The 82C54 programmable interval timer receives its input counts from the guarded digital bus and creates the second channel signal on OUT2 (pin 20) and the first channel signal on OUT1 (pin 16).

The second channel signal is buffered by U8 (D and E) and runs through opto-isolator U12 to become CH2 FLOATING. This signal alternately turns FETs Q30 and Q32 on and off to turn the 3V source (called 3V) into a floating 3V pulse width modulated waveform called CH2 FILTER INPUT.

The 3V source is created from the 13V reference. The 13V reference is buffered by op amp U1B, configured as a voltage follower. The output from U1B is divided down to 3V by a 100 kilohm and 30 kilohm resistor in the HR5 assembly, creating 3V.

This 3V is again buffered by op amp U11, configured as a voltage follower, to create the 3V, which is switched by FETs Q30 and Q32. CH2 FILTER INPUT uses three resistors on the HR5 assembly to resistively divide its 3V amplitude by an additional factor of approximately 3800.

The first channel signal is buffered by U8 (G and H) and run through opto-isolator U13, to become CH1 FLOATING. Since the first channel is much more critical than the second, CH1 FLOATING is clocked into a flip flop (U14) to insure an accurate waveform.

To clock in this waveform, the low-level 8 MHz clock (CLK and CLK\*) from the Regulator/Guard Crossing assembly (A17) is isolated by transformer T1 and amplified to a TTL level by comparator U10. This generates the clock inputs for U14. The output Q1 (pin 5) from U14 creates CH1 SERIES A, which switches Q7. The output Q1\* (pin 6) is inverted by Q35, creating CH1 SHUNT, which switches Q6. The output Q1\*, which is a TTL level, is also amplified by components Q33, Q34, VR11, VR12, and R44-R46, so it switches from 0 to 18V, creating CH1 SERIES B, which switches Q4 and Q5.

The watchdog timer sets the first channel filter input to OV if a failure occurs on the 8 MHz clock. This circuit uses a monostable multivibrator (one shot) U15, C63, and R48. The 8 MHz clock is divided to 4 MHz by U14. This 4 MHz clock is connected to U15 and discharges C63 to ground. If the 4 MHz clock stops, C63 charges up, causing the Q1 output of U15 to go low. This logic low on Q1 is connected to the preset pin of U14 (PRI), which causes its Q1 output high and its Q1\* output low. This condition turns on the shunt switch and turns off the series switch, which forces the filter input to be REFCOM.

## 2-105. DAC FILTER CIRCUIT

The dac filter circuit is located on the DAC Filter SIP (A11A1) assembly. The dominant pole of the filter is near 10 Hz. This gives 120 dB of rejection at 190 Hz.

The +30FR1 supply and 15V zener diode, VR1, create the 15V supply (15V) for the op amps in the filter circuit. 15V is also connected to the main DAC board, where it is used with R111 as a pull up for the RANGE SELECT control line.

# 2-106. DAC OUTPUT STAGE

The output stage of the DAC assembly consists of the DC Amplifier Hybrid assembly (HR6) and the output buffer circuitry. Like the Reference Hybrid, the DC Amplifier Hybrid is constructed of surface-mount components (except precision op amp U2), on a ceramic substrate hybrid, bonded to a resistor network.

It is temperature-controlled by a heater control circuit in the same manner as explained on the Reference Hybrid. Transistor Q3 provides proper power to the heater resistor.

The DC Amplifier Hybrid consists of a precision op amp U2, with a bootstrapped power supply (Q1, Q2, R1-R4, VR1-VR2). The op amp has low noise and low offset. It is bootstrapped to improve the common-mode rejection in its noninverting configuration.

The DC Amplifier assembly interfaces with the output buffer (U5) to create the output stage. Control line RANGE SELECT configures this output stage for unity gain for the 11V range or a gain of 2 for the 22V range. In the 11V range, Q15 is turned off, which gives U5 unity gain, and Q20 is on, which gives the DC Amplifier unity gain.

In the 22V range, Q20 is off and Q21 is on, which switches in the 40 kilohm feedback resistors located on the HR6 assembly. Precise ratio matching of these resistors provides high accuracy in the 22V range.

FET Q15 is on in the 22V range so that the output of the dc amplifier is half the output of the DAC. This is necessary so that the output of the dc amplifier is approximately the same as its inputs, which allows the bootstrap circuit to work.

The output buffer (U5) provides drive for the DAC output. It is used in a feedback loop with the DC Amplifier Hybrid so that the dc accuracy is dependent upon the dc amplifier, and the output drive capability is dependent on the output buffer.

The output buffer is current-limited to a short circuit current of about 60 mA. The short-circuit protection circuitry works as follows:

The supply current is sensed by R23. When the output current of U5 reaches approximately 50 mA, the voltage across R23 is large enough to turn on Q10. As Q10 turns on, the voltage across R20 increases, and pulls down the supply voltage at pin 4 of U5. In order to prevent the supply of U5 from dropping below the input, Q8 saturates turning on Q11 which shorts the input to FR1 COM. When the short is removed, R22 and C41 cause Q11 to turn off slowly, which prevents a large overshoot at the DAC output.

# 2-107. SENSE CURRENT CANCELLATION CIRCUIT

This circuit uses op amp U1A and four resistors on the HR6 assembly. This circuit supplies the sense current of equal, but opposite, polarity to the feedback resistors in the 22V range. This eliminates current in the sense lead during external sensing.

# 2-108. LINEARITY CONTROL CIRCUIT

The linearity control circuitry contains the series linearity control circuit and the shunt linearity control circuit, as outlined on the schematic. These linearity control circuits eliminate filter current in the series switch (Q5) and the shunt switch (Q6). This is necessary because Q5 and Q6 have finite resistance (3 to 5 ohms) and a small mismatch in the resistances can cause a linearity error.

The series linearity control circuit uses op amp U38, resistor network Z2, and a single 19.996 kilohm resistor on the HR5 assembly. This circuit eliminates filter current in the series switch Q5.

When the series switch (FET Q5) is on, it connects the 13V reference to the first channel input of the filter, and FET Q4 is also turned on. This causes U38 to supply the current to the filter through the 19.996 kilohm resistor in HR5 and Q4, which makes the resistance from TP2 to TP5 look like near 0 ohms.

The shunt linearity control circuit uses op amp U2B, FET Q22, three  $80\,$  kilohm resistors on the HR6 assembly, and one resistor in the HR5 assembly.

# ANALOG SECTION DETAILED CIRCUIT DESCRIPTION/DAC (A11)

Op amp U2B is configured as an amplifier with an inverting gain of 1 in the 11V range, and an inverting gain of 0.5 in the 22V range. This gain is determined by FET Q22 and the three 80 kilohm resistors in the HR6 assembly.

When the shunt switch (FET Q6) is on, connecting the input of the filter to REFCOM, the current from the filter flows through the two 40 kilohm resistor (pin 7 to pin 8) on the HR6 assembly to the output of U2B. This cancels out the current that would flow through Q6 which makes it look like 0 ohms.

### 2-109. NEGATIVE OFFSET CIRCUIT

This circuit creates a constant offset voltage of approximately -127 mV at the filter input. Thus, for a DAC output voltage of 0V, the first channel count must be approximately 400 to offset this negative voltage. This guarantees a minimum duty cycle pulse width of approximately 50 us.

This minimum duty cycle is necessary to overcome the offset of the output stage and to allow the reference voltage to settle out after being switched into the filter input. Op amp U2A and two 20 kilohm resistors in HR6 form an amplifier with an inverting gain of 1. This amplifier input is the 13V reference which produces -13V at its output. This -13V is divided by resistors in the HR5 assembly to create the -127 mV on the filter input.

## 2-110. DAC OUTPUT SWITCHING

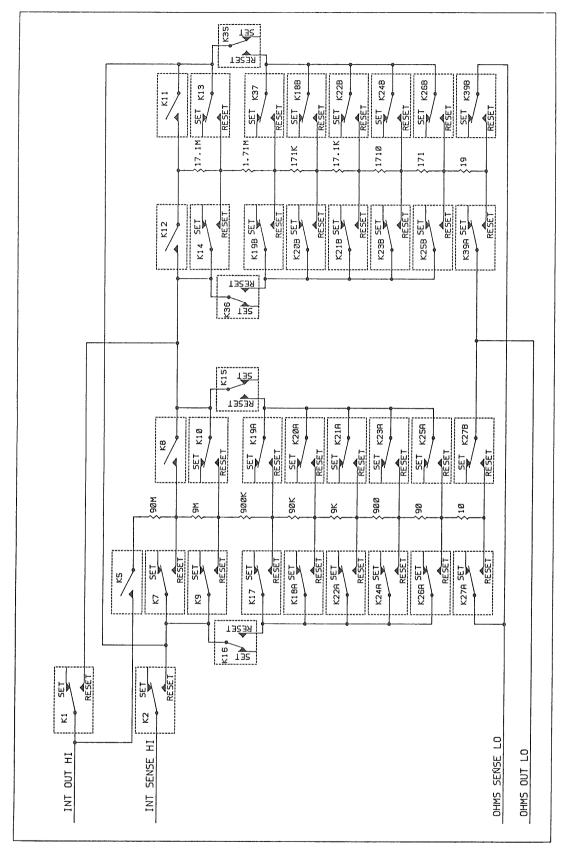

The floating outputs of the DAC are switched with latching-type relays K1, K2, K3, K4, and K8.

Relays K1 and K2 determine the polarity of the DAC. In the reset position, the DAC output is positive. In the set position, output is negative. Relay K1 also generates DAC LO DIAG and DAC HI DIAG which are used by the adc circuit during DAC diagnostics.

Relays K3 and K4 switch the DAC to various assemblies. In the reset position, the DAC is available to all assemblies except the oscillator. Relays K3 and K4 are set during operation in the ac function so the DAC output is connected to the DAC/OSC lines which run only to the Oscillator assembly. Also during operation in the ac function, control line DAC OUT SEL turns on FET Q25, via FET Q26, to connect SCOM to RCOM.

Relay K8, when in the set position, allows the DAC to be sensed right on the output of the DAC assembly.

## 2-111. DAC BUFFERED REFERENCE SIP

The DAC Buffered Reference SIP assembly (A11A2) has two main functions. First, it buffers the the 6.5V and 13V references so they can be used by other assemblies.

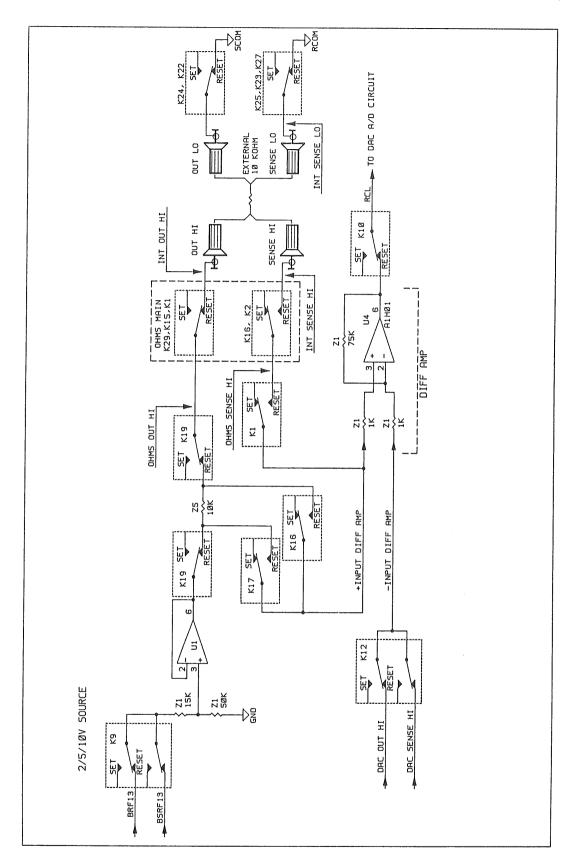

The 6.5V reference, REF6, is buffered by op amps U1A and U2A which creates BRF6 and its sense line BSRF6. The 13V reference, REF13 FILT, is buffered by op amps U1B and U2B which creates BRF13 and its sense line BSRF13. These are routed to other assemblies in the calibrator for use during calibrator calibration.

Second, it allows the the reference voltages, or the buffered reference voltages, to be switched to the REFCAL line, which is connected to the inverting input of the adc amplifier by K5 during calibration of the DAC assembly.

Control line REF6 SEL and FETs Q1 and Q2 connect the 6.5V reference REF6 to REFCAL.

Control line BSRF6 SEL and FETs Q5-Q7 tie BRF6 and BSRF6 together and connects them to REFCAL.

Control line REF13 SEL and FETs Q8 and Q9 connect the 13V reference REF13 to REFCAL.

Control line BSRF13 SEL and FETs Q12-Q14 tie BRF13 and BSRF13 together and connects them to REFCAL.

ADC COM can also be connected to REFCAL by FET Q15 and control line ADC COM SEL.

#### 2-112. SELF-CALIBRATION HARDWARE

The main components of the calibration hardware are the adc amplifier and the adc (analog to digital converter). This adc circuitry converts dc analog voltages into 22-bit binary numbers which the software interprets.

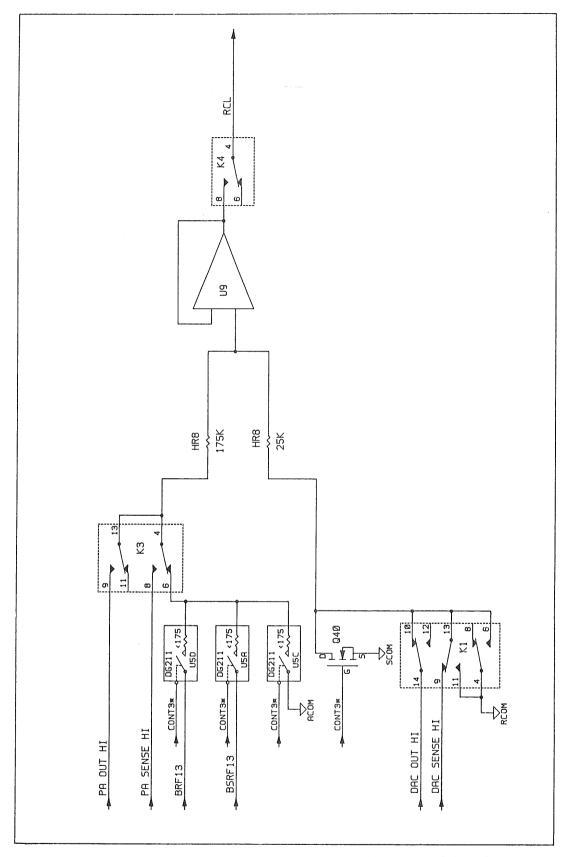

# 2-113. ADC AMPLIFIER

ADC amplifier circuitry is located on page 4 of the DAC schematic. The adc amplifier is used like a null detector. It has two inputs (inverting and noninverting) and a single output with ADC AMP OUT and ADC AMP SENSE connected together.

The noninverting input (+INPUT) is switched between ADC COM, RCL, or DAC SENSE CAL by relays K6 and K7. DAC SENSE CAL is the output of the DAC and RCL is the calibration line which other assemblies use during their calibration.

The inverting input (-INPUT) is switched between DAC SENSE CAL and REFCAL by relay K5. ADC amplifier inputs are high impedance. The output voltage is the voltage difference between the inputs multiplied by the overall adc amplifier gain of 11.

To determine adc amplifier output, the following formula is used: (Noninverting input - inverting input) X 11 = adc amplifier output.

For example if the noninverting input is a 5.0V and the inverting input is at 5.1V, the output would be -1.1V. (The calculation for this example is (5.0V - 5.1V) X 11 = -1.1V.) Op amp U20A configured as an amplifier with an inverting gain of 1 is used to cancel the current in ADC COM generated from op amp U19A.

Zener diodes VR19 and VR20 keep the output of the adc amplifier from exceeding  $\pm 4.0$ V. Similarly, this protection is provided for the adc amplifier inputs by VR17, VR18, VR21 and VR22.

The advantage of having a gain of 11 is that the noise of the adc is divided by this gain. For example, if the noise of the adc is 4 uV rms, the effective noise of the adc becomes 4 uV/11 = 0.36 uV rms, referred to as the adc amplifier inputs.

### 2-114. ADC INPUT SELECTION

The input to the adc chip, U25, is selected by a quad FET analog switch array, U23. A large filter (R74 and C84) and a buffer (U24) are put on the adc input line to filter out 60 Hz and 190 Hz before it is connected to the adc chip input (pin 22).

During calibrator diagnostics, control line PC2 selects the SDL (system diagnostic line) line, which is used by other analog assemblies to monitor their diagnostic voltages.

During diagnostics of the DAC assembly control, line PC3 selects DAC HI DIAG which is divided by R79 and R84. Control line PC4 selects DCAMP HEATER and REF HEATER which are summed and divided by R80, R81, and R83.

Since DCAMP HEATER and REF HEATER are referenced to FR1 COM, DAC LO DIAG is buffered by U22 to provide the proper current return.

During calibrator calibration, control line ADC OUT SEL selects the output of the adc amplifier.

# 2-115. ADC CIRCUIT

The adc (analog-to-digital converter) is shown on page 5 of the DAC schematic.

Most of the adc is contained on one chip (U25) which uses the Fluke-patented recirculating remainder technique.

The adc has rms noise of approximately 20 uV between readings. This is reduced by a factor of 5 by averaging the readings. The adc measures input voltages between -1.8V and +1.8V.

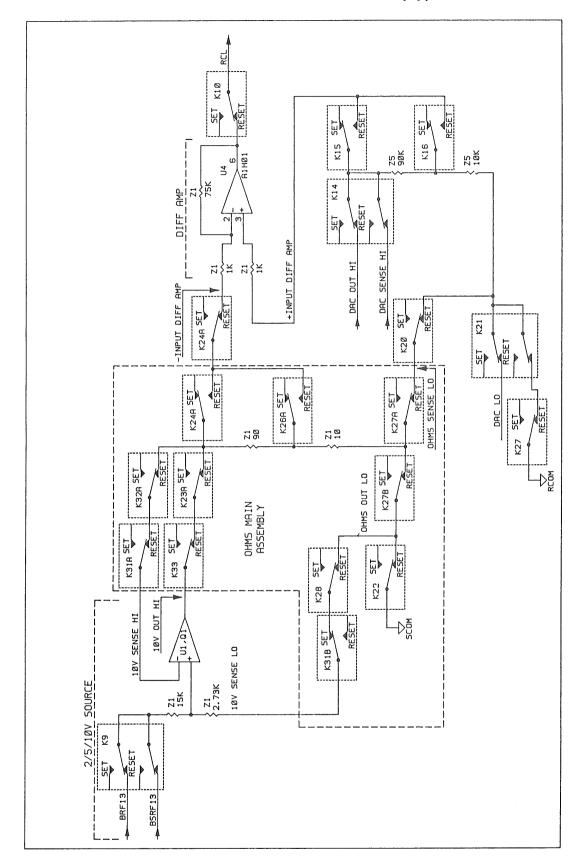

Hardware for the adc has four major sections external to adc IC U25. These sections are:

- o ADC reference voltage

- o ADC dac

- o ADC comparator/amplifier

- o Timing/data control circuitry.

The adc reference voltage circuit is made up of zener diodes VR29, VR30, and resistors R91-R93, which generate a 6.4V reference. This -6.4V is inverted by U27B to create the +6.4V reference and is also buffered by U27A and connected to U25. A reference common point for the adc reference is made by buffering ADC COM with op amps U20B and U26A, resulting in an isolated ADC COM. Buffering allows the common point to be referenced to ADC COM, yet current from R85, C89, C90, R93, VR29, and VR30 to return to SCOM through the output of the buffer instead of through ADC COM.

The adc dac contains the dac amplifier, U28B, and a binary ladder network consisting of resistors in Z10. Digitally controlled analog bit switches are contained in U25. The bit switches determine the output voltage of U28B by control of the binary ladder network. The output voltage of U28B can be varied from -1.95V to 1.95V.

The adc comparator/amplifier contains op amp U29, two remainder storage capacitors (C89 and C90), an autozero storage capacitor (C95), and several digitally-controlled analog switches in U25.

The supplies for U29 are bootstrapped off its input voltage. This circuitry includes U28A, VR31-VR34, R95-R100, Q56, Q57, and C97.

The timing/data control circuit is the digital portion of U25. This internal circuitry controls the adc by manipulating the switches in the adc comparator/amplifier and the bit switches in the adc dac.

An adc conversion cycle is triggered by the falling edge of control line ADC TRIGGER from the digital control circuit. Once triggered, the adc, under control by U25, generates five 6-bit nibbles without any further interaction.

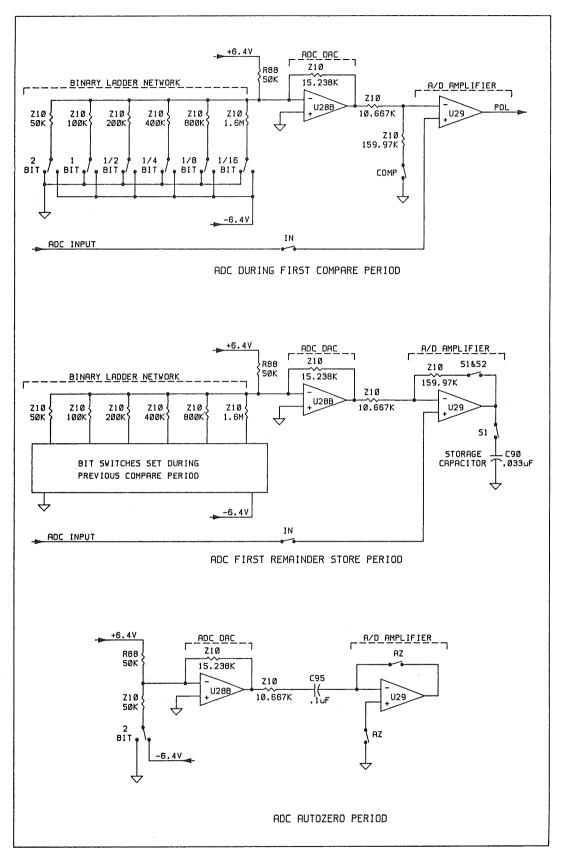

Once the adc is triggered, it goes through five measurement cycles. Each cycle is made up of three functions, an autozero function, a compare function and a remainder store function. Figure 2-17 illustrates these three functions.

Before the adc is triggered, it stays in the autozero function. In this function, the adc dac is set to OV with some offset error. Through U25, pin 3 of U29 is connected to ADC COM and pins 2 and 6 are connected together. In this function, the offset of the adc dac is stored on C95.

Figure 2-17. ADC Circuit Measurement Functions

In the compare function, U29 compares the adc dac with the adc input (during the first pass) or the stored remainder (C89 or C90) during the remaining four passes. The voltage to be measured is switched into pin 3. The adc dac is connected to pin 2 and adjusted according to the polarity output of U29 resolving the voltage on pin 3. During this function the six bits of one nibble are determined.

During the remainder store function, U29 amplifies and stores the difference between the ADC INPUT and the adc dac output on one of the remainder storage capacitors, C89 or C90. In this function, U29 is configured by the adc as a difference amplifier with a gain of 16. The output of U29 is now the difference between the input voltage and the DAC voltage, multiplied by 16. This voltage is stored on C89 or C90.

On the next cycle, this remainder voltage is switched into U29 as the input voltage during the compare function.

Once this is repeated five times, U25 sends out an interrupt signal (ADC INT) to tell the processor that it is waiting to read. To read the five passes of the adc, the processor reads port A of the 82C55 five times.

For the most critical applications, the adc measures the output of the adc amplifier. Since the output of the adc amplifier is adjusted until it reaches a checkpoint voltage, the adc needs only to be repeatable at this voltage and low in noise. This reduces the constraints on adc linearity and long term stability which allows a much simpler adc reference to be used.

2-116. HOW THE DAC IS USED IN SELF-CALIBRATION

For internal and external calibration, the adc amplifier output is switched to ADC INPUT.

The adc amplifier acts as a null meter. It measures the voltage difference between its inverting and noninverting inputs and amplifies it by a gain of 11.

The adc amplifier can measure common-mode voltages up to 14V. Input switching circuitry allows the DAC SENSE, buffered and unbuffered reference, RCL, and ADC COM to be switched into the adc amplifier inputs.

To make a typical cal measurement, software sets the DAC to the approximate expected common-mode voltage. The DAC is then switched into both adc amplifier inputs and an adc reading is taken. This is the checkpoint measurement. It represents the adc amplifier common-mode and offset error, and the errors in the adc and adc amplifier input switching. The unknown voltage is switched into one input of the adc amplifier and the DAC is adjusted by software until the adc reading matches the checkpoint reading. At this point the unknown voltage is equal to the DAC voltage and is represented by the current DAC counts.

# ANALOG SECTION DETAILED CIRCUIT DESCRIPTION/DAC (A11)

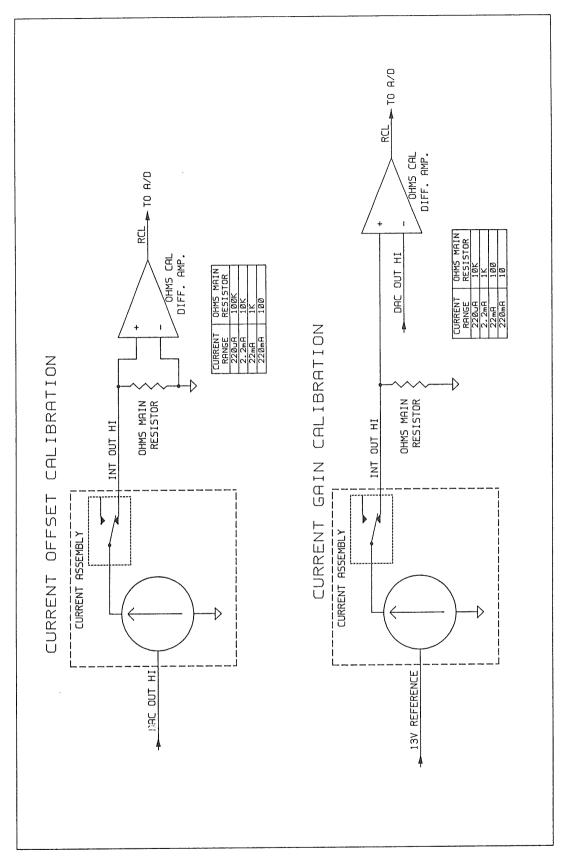

### 2-117. DAC ASSEMBLY CALIBRATION

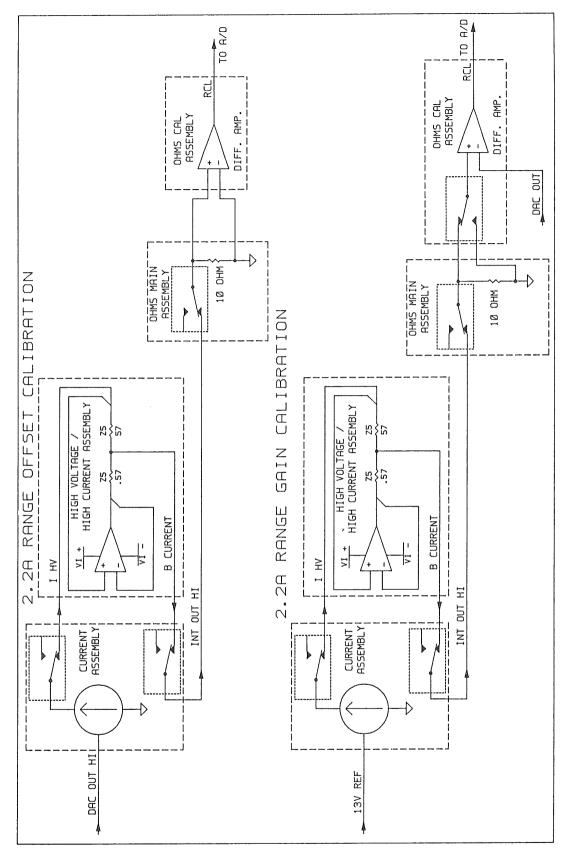

The DAC assembly is completely characterized using a single external 10V source. Calibration occurs in the following steps:

Ratio calibration of the first and second channels is performed first. The first channel count is set for a DAC output of near OV. The second channel count is set to its minimum value of approximately 10,000. The DAC output is connected to the input of the zero amplifier on the Switch Matrix assembly (A8) and its output connected to the +input of the adc amplifier via the RCL line and the -input is connected to ADC COM.

The adc measures this value and stores it as a checkpoint reading. The first channel is decremented by one count and the second channel is increased until the adc reads the same as the previous checkpoint. The number of counts the second channel is increased represents the channel ratio constant.

The  $\pm 11\text{V}$  and  $\pm 22\text{V}$  range zeros are calibrated next. This is done by the same technique as the ratio cal except the checkpoint reading is obtained by connecting the input of the zero amplifier on the Switch Matrix assembly to RCOM. The DAC output (DAC SENSE CAL) is then connected to the zero amplifier input and adjusted until the adc reads the same as the previous checkpoint. This determines the exact first and second channel counts for a OV output.

Next, the +11V and +22V range gain constants are calibrated by nulling the DAC to the external 10V source, connected to the front panel binding posts of the calibrator. This 10V source is connected to the RCL line by relays on the Switch Matrix assembly (A8).

The RCL line is connected to the +INPUT of the adc amplifier. The DAC output is connected to the -INPUT of the adc amplifier and is adjusted until the adc reads a null. This determines the first and second channel counts required for an exact 10 V output from the DAC. Software determines floating point gain constants from these counts.

The exact value of all the reference voltages (6.5V and 13V) are determined next. The reference voltage to be determined is connected to the -INPUT of the adc amplifier. The DAC output is connected to the +INPUT and adjusted until the adc reads a null. The reference voltage is the value to which the DAC is set. This procedure is done for the 6.5V buffered and unbuffered, and 13V buffered and unbuffered references.

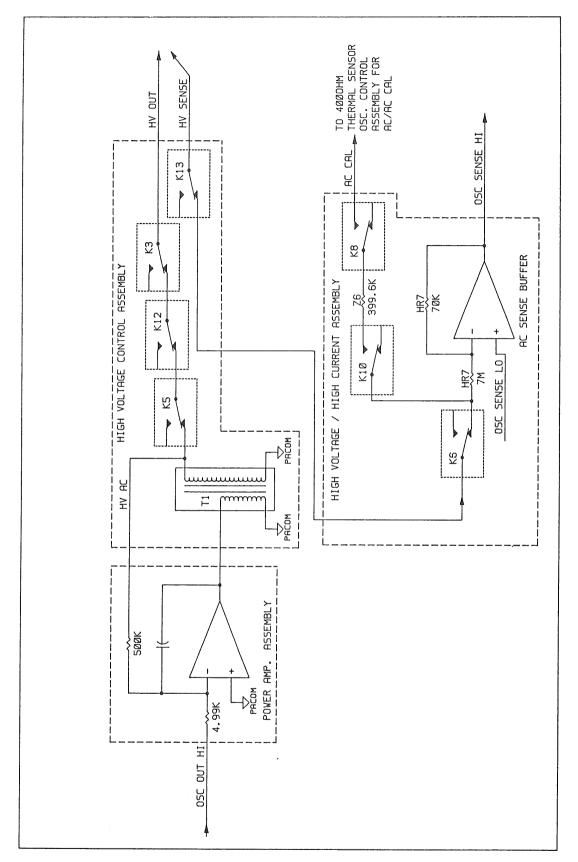

## 2-118. Oscillator Section Overview

The ac module consists of two plug-in assemblies, the Oscillator Output assembly (A13) and the Oscillator Control assembly (A12). These assemblies generate a precision amplitude-stabilized ac sine wave from 0.22V to 22V with a frequency range of 10 Hz to 1.2 MHz. This signal is either routed to the OUTPUT binding posts if the desired output is within this range, or used internally by the Power Amplifier, High Voltage, Wideband, Current, Switch Matrix, or an Auxiliary Amplifier (Model 5725A, 5205A, 5215A, or 5220A) for voltages and/or functions outside this range.

Output sensing of the amplitude helps obtain an accurate output signal regardless of output amplitude and load variations. Sensing is available for all voltage ranges above 200 mV at the calibrator SENSE binding posts. In the current function, and for voltages less than 200 mV, sensing is performed internally and output accuracy is guaranteed only for specified operating conditions.

The Oscillator Output assembly (A13) creates an ac voltage. The Oscillator Control assembly (A12) controls the amplitude of this ac signal by comparing the SENSE HI signal from the Oscillator Output with an accurate dc voltage from the DAC assembly (A11). The Oscillator Control assembly adjusts the amplitude of the Oscillator Output via the OSC CONT line. The frequency accuracy is controlled by the phase-locked loop circuit on the Oscillator Output assembly, which phase locks to the signal created by the Current/Hi-Res assembly (A7), or to an external signal connected to the 5700A rear panel through the PHASE LOCK IN jack.

The following discussions separately cover these two assemblies.

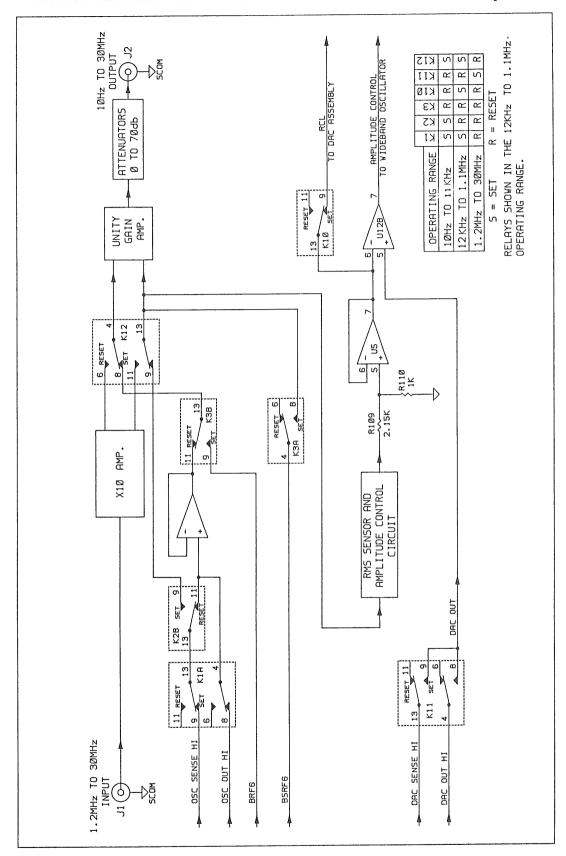

# 2-119. Oscillator Control Assembly (A12)

The Oscillator Control assembly (A12) contains all the precision ac amplitude control circuitry except the output AGC amplifier, which is located on the Oscillator Output assembly (A13). The primary function of the Oscillator Control assembly is to monitor the output of the 5700A in the ac voltage function, and to adjust the output until the rms voltage across the SENSE point is equal to the voltage requested by the operator. This assembly provides amplitude control for both the ac current function and the Wideband AC Module (Option -03) during low-frequency operation.

The oscillator control circuitry contains an averaging converter, an error intergrator, a three-pole filter, an ac/dc thermal transfer circuit, an ac/ac thermal transfer circuit, a 15-bit dac, and a digital control circuit.

All power supplies used by this assembly are generated by the Guard Crossing/Regulator assembly (A17) except the +5 OSC supply, which is generated by a three-terminal +5V regulator (U25) from the +15 OSC supply. The  $\pm 15$  OSC supplies are buffered by L3, L4, C34 and C35 to create the  $\pm 15$ A supplies, and L1, L2, C86 and C87 to create the  $\pm 15$ B supplies. A +2.5V reference voltage is created from the +5LH supply by resistors R52 and R53. A -200 mV reference voltage is created from the -15V OSC supply by resistors R57 and R58 for use exclusively by the protection circuitry for the thermal sensors U14 and U16.

# 2-120. OSCILLATOR CONTROL DIGITAL CONTROL

The digital control circuit contains an 82C55 Programmable Peripheral Interface (U20) and latching relay drivers (U23, U24). The 82C55 is controlled via the guarded digital bus, and has three ports that generate 24 outputs. Port A (PA0-PA7) is a common input bus (DATA) for the relay drivers (U23, U24) and the 14-bit DAC (U10). Relay driver U23, which controls latching relays K1 through K4, K6, and K8, is strobed by PC5 and enabled by PC7 of port C. Relay driver U24, which controls latching relays K5, K7, and K9, is strobed by PC6 and enabled by PC7 of port C. The SW control bus contains control lines SW1-SW4 from PB4-PB7 of port B which control a CMOS analog switch IC U19. PC1-PC4 of port C create control lines GCAL, AC\*/DC, DAC\* and BIT14\* respectively. The Oscillator Output assembly (A13) generates two more control lines: LFCOMP\* and HFCOMP\*. These control lines are routed to this assembly via the Motherboard and enter on pins 18A/C and 19A/C of connector P502.

A self-diagnostic circuit contains a multiplexer (U18) and resistor networks Z5 and Z6. It monitors  $\pm 15$ V, VREF, and the outputs of the error integrator and 14-bit DAC. These inputs are divided by the resistor networks, while U18 applies one to the SDL line. The SDL line is routed to the DAC assembly (A11) to be measured by the adc circuit.

# 2-121. OSCILLATOR INPUT SWITCHING

Relay K1 selects an input to the Oscillator Control assembly. During ac voltage operation, relay K1 is reset. This connects the input (SENSE HI) to the averaging converter and the ac sense buffer to OSC SENSE HI. The reference voltage, VREF, is connected to both DAC/OSC OUT HI and DAC/OSC SENSE HI, which is the dc voltage from the DAC assembly (A11). During internal calibration K1 is set, so VREF is the 6.5V reference voltage (BRF6 and BSRF6) from the DAC assembly. The input to the averaging converter and ac sense buffer is DAC/OSC OUT HI and DAC/OSC SENSE HI from the DAC assembly.

# 2-122. SENSE CURRENT CANCELLATION

The SENSE HI current cancellation circuit, containing op amp U1, Q1, Q2, K8, K2B and associated components, supplies the current into SENSE HI (Z2 pin 1) so that no current is pulled from the OSC SENSE HI line. During operation in the 2.2V and 22V, range K8 is set so the input is OSC OUT. In the 22OV range K8 is reset so OSC SENSE HI is connected to the input. Relay K2B is reset in the 2.2V range and set in the 22V range. Transistors Q1 and Q2 form a bootstrapped supply for U1.

The SENSE LO current cancellation circuit, built around op amp U2, forces the return current back to SCOM instead of OSC SENSE LO. Relay K2A is reset in the 2.2V range and set in the 22V range.

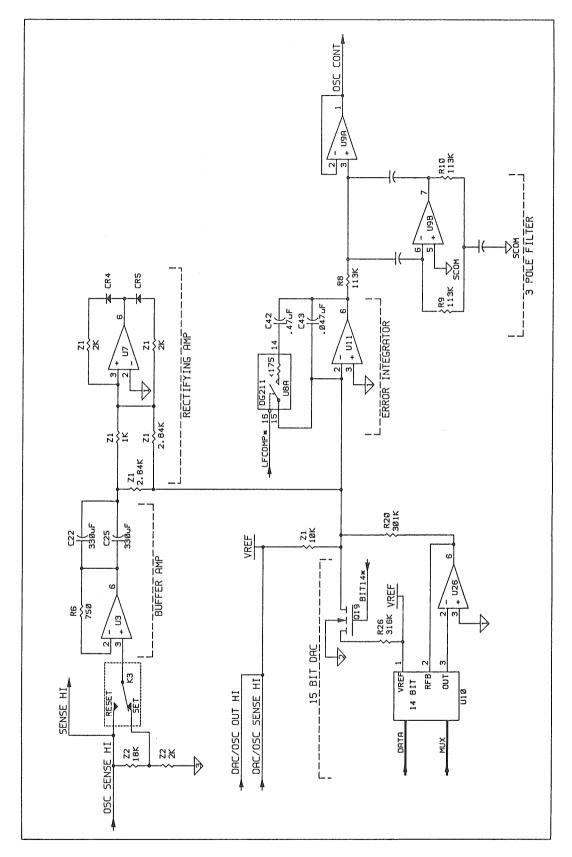

To better understand the detailed circuit descriptions for the averaging converter, error intergrator, and three-pole filter, refer to Figure 2-18.

### 2-123. AVERAGING CONVERTER

The averaging converter contains the buffer amplifier and rectifying amplifier circuits as outlined on page 1 of the schematic.

The buffer amplifier is a non-inverting unity gain amplifier (U3). Input to the buffer amplifier is either a 0 or 20 dB attenuator contained in Z2 as selected by K3. In the 2.2V range, SENSE HI is connected directly to the buffer amplifier with K3 in the reset position. In the 22V range, K3 is in the set position, so the buffer amplifier input (SENSE HI) is attenuated 20 dB by the 18 kilohm and 2 kilohm resistors in Z2. The buffer amplifier output voltage is always between 0.22 and 2.2V, and is capacitively coupled to the rectifying amplifier by C22 and C25.

The rectifying amplifier is comprised of U5, U7, Q3 and Q4, and has an inverting gain of 2. When the input voltage (from the buffer amp) is positive, feedback is negative through CR5 and a 2 kilohm resistor in Z1 (pins 6 and 5). When the input voltage is negative, the feedback path is through CR4 and a different 2 kilohm resistor in Z1 (pins 3 and 5). This amplifier produces a full-wave rectified negative output current proportional to input voltage. Output current is summed at the input of the error intergrator with the positive adjustable reference current (VREF, which is the output of the DAC assembly).

### 2-124. ERROR INTEGRATOR

The error integrator circuit contains op amp U11, CMOS analog switch U8A, and capacitors C42 and C43. When operating at frequencies above 119 Hz, op amp U11 and C43 form an integrator. When operating at frequencies below 119 Hz, control line LFCOMP\* goes low to close U8A, adding C42 to C43. This reduces the integrator crossover point by a factor of ten. If the magnitude of the averaging converter dc output current is different than the reference current, the output of the error integrator begins to change. Error integrator output goes through a three-pole filter and is buffered by U9A to generate OSC CONT. OSC CONT is routed to the Oscillator Output assembly to adjust the Oscillator amplitude. The output of the error integrator is also monitored by the diagnostic circuit via ERROR INT. OUT.

### 2-125. THREE-POLE FILTER

The three-pole filter contains op amp U9B, CMOS analog switches U8B-U8D, and C26-C31. This circuit filters out ac from the output of the error integrator. Control line LFCOMP\* goes low when operating at 119 Hz or less to reduce the crossover point.

Figure 2-18. Oscillator Control Analog Control Loop

## 2-126. ANALOG AMPLITUDE CONTROL LOOP

This loop is comprised of the averaging converter, error integrator, three-pole filter, and the agc amplifier on the Oscillator Output assembly (A13). It stabilizes the 5700A output voltage in the presence of load changes. This loop by itself is very stable but does not have the conversion accuracy or gain flatness necessary to meet the precise amplitude specifications of the 5700A. Thus this circuit is used only to provide quick load regulation recovery and short term output stability.

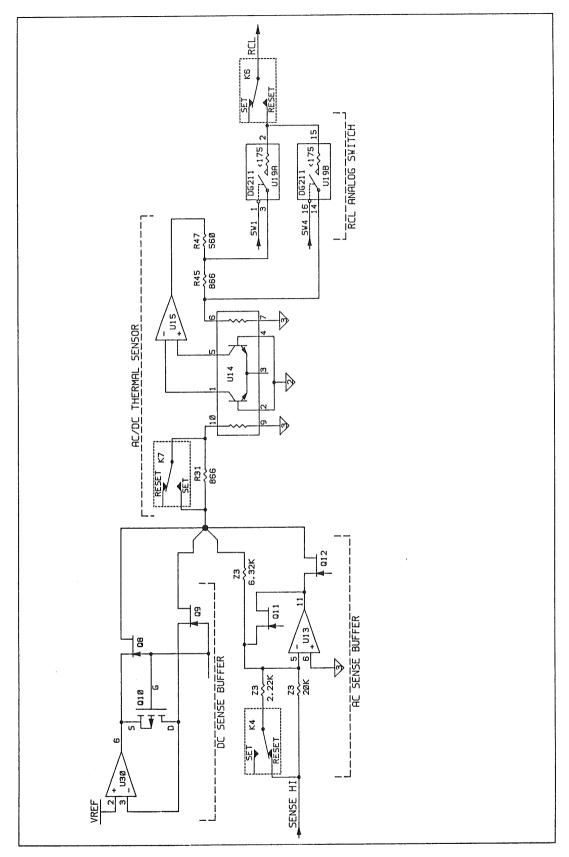

### 2-127. AC/DC THERMAL TRANSFER CIRCUIT

Refer to Figure 2-19 for the following discussion. The ac/dc thermal transfer circuit achieves basic mid-band amplitude accuracy. This is done by first applying the reference voltage (VREF) to the thermal rms sensor (U14) and measuring the output. Next, the ac voltage is applied to the thermal rms sensor and the dc output is compared to the previous reading. The sensor detects the difference between the ac and dc input voltages to within a few ppm.

If there is an ac/dc difference, the dc reference current applied to the error integrator of the analog control loop is adjusted via the 15-bit dac until the ac/dc difference is zero. The ac/dc thermal transfer circuit that performs this function is further described in detail. It contains the the dc sense buffer, ac sense buffer, ac/dc thermal sensor, and the square-root amplifier and 15-bit dac as outlined on the schematic.

As previously mentioned, the input to the thermal rms sensor is either the dc reference voltage (VREF) buffered by the dc sense buffer or the ac voltage (SENSE HI) buffered by the ac sense buffer.

The dc sense buffer circuit uses op amp U30 as a buffer amplifier. Enhanced-mode FET Q10 provides feedback for U30 while FETs Q8 and Q9 are off. During a dc transfer, control line AC\*/DC and comparator U21C turn on the FETs, applying the output of the dc sense buffer to the input of thermal rms sensor U14.

The ac sense buffer circuit contains op amps U12A, U12B, U13; FETs Q6, Q7, Q11, Q12; relay K4, and associated components. Relay K4 selects the input resistance to amplifier U13, which has a nominal inverting gain of 0.316 in the 22V range and 3.16 in the 2.2V range.

During operation in the 22V range, relay K4 is set, feeding the input, SENSE HI, through the 20 kilohm resistor in Z3. When operating in the 2.2V range, the 2.22 kilohm and 20.0 kilohm resistors in Z3 are put in parallel by K4 in the reset position, reducing the input resistance to 2 kilohm.

During an ac transfer, control line AC\*/DC and comparator U21D turn on FET Q12 so the output of amplifier U13 is applied to the input of thermal rms sensor U14. At this time, FET Q11 is turned off and the feedback path for U13 is through the 6.32 kilohm resistor in Z3.

Figure 2-19. AC/DC Thermal Transfer Circuit

During a dc transfer, Q12 is off and comparator U21B turns on FET Q11, providing the feedback path for U13. Op amps U12A and U12B provide low offset and increase the gain. Control line HFCOMP and comparator U22C turn on FETs Q6 and Q7 during operation in the 1 MHz range.

The output of either the dc sense buffer or the ac sense buffer becomes the input of thermal rms sensor U14. During operation from 0.22V to 0.7V in the 2.2V range, or 2.2V to 7V in the 22V range, relay K7 is set, directly connecting the input signal to the sensor. The input to the thermal sensor is through R31 by K7 in the reset position during operation from 0.7V to 2.2V in the 2.2V range, or 7V to 22V in the 22V range.

Comparator U21A provides protection for thermal rms sensor U14. If the junction temperature of the sensor goes above 200 oC, the voltage at pin 3 increases, driving the output of U21A negative. This turns off the FETs controlling the output of the dc sense buffer and ac sense buffer, removing the input to the thermal sensor.

The ac/dc thermal sensor and square-root amplifier, as outlined on the schematic, contain the thermal sensor U14, op amp U15 and transistor array U17. The dc voltage from the thermal sensor is connected to U15B configured as an integrator. Comparator U22B is used to control FETs Q18 and Q20. These FETs are turned on, adding C84 and C62 to the integrator, by control lines LFCOMP\* and AC\*/DC both at logic low. The output of integrator U15B is used by the square-root amplifier contained in U15A, U15C and U17. This circuit keeps the settling time of the sensor constant when its input is varied between full and 1/3 scale. The output of the sensor is connected to the RCL line by relay K6 and CMOS analog switch U19A and U19B. During operation from 0.22V to 0.7V in the 2.2V range, or 2.2V to 7V in the 22V range, sensor output is connected to the RCL line through buffer U31, U19B, and K6 in the set position. During operation from 0.7V to 2.2V in the 2.2V range, or 7V to 22V in the 22V range, sensor output is connected to the RCL line through U19A and K6. Control lines SW1 and SW4 control U19A and U19B respectively. The RCL line is routed to the DAC assembly (A11) where its amplitude is measured by the adc circuit.

To do an ac/dc transfer, the dc sense buffer is connected to the thermal sensor and the sensor output is connected to the +input of the DAC's adc circuit. The -input of the adc circuit is connected to the DAC output (VREF), and the difference between the two is measured and stored in memory. Next, the output of the ac sense buffer is connected to the sensor and the sensor output is connected to the +input of the DAC's adc circuit. The difference is measured and compared to the previous reading. The difference between these two readings is the difference in rms value of the ac and dc input voltages. If there is an ac/dc difference, the dc reference current applied to the error integrator of the analog control loop is adjusted via the 15-bit dac until the ac/dc difference is zero.

The 15-bit dac contains an AD7534 dac IC (U10), FET Q19 and op amp U26. The first 14 bits (bits 0-13) are generated by the dac IC U10, and bit 14 is generated by Q19, R26, and control line BIT14. Control busses DATA and MUX from the digital control circuit select the data and address for U10. The output is inverted by U26 to create 14 BIT DAC OUT, which is applied to the summing node of the error integrator by R20. This output is also monitored by the diagnostic circuit.

### 2-128. OSCILLATOR CALIBRATION

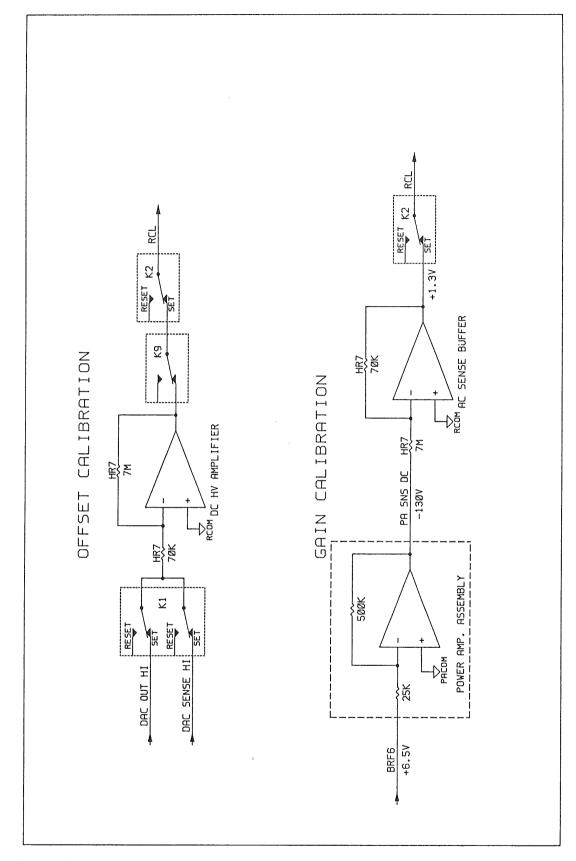

Calibration consists of determining the offset and gain errors of the ac/dc switching circuitry. Errors are measured at dc using the calibrator DAC and the 6.5V reference as the primary sources of accuracy. This characterization is valid for frequencies up to 1 kHz. Above 1 kHz, ac/ac characterization is used to insure the output accuracy.

The DAC assembly (A11) is set to OV with its output connected to the ac sense buffer (via SENSE HI) by relay K1 in the set position. The output of the ac sense buffer is connected to the RCL line by K6 in the set position and by control line GCAL and comparator U22A turning on Q13. The OV input is stored as Vin1. The output measured by the adc circuit on the DAC assembly is stored as Vout1.

Relay K1 ties 6.5V reference BRF6 and BSRF6 to VREF, where it is measured at the output of the thermal sensor in the same manner as a dc transfer. This measured output is stored in memory.

The DAC output is set to 20V or 2V and is measured at the output of the thermal sensor in the same manner as an ac transfer. The DAC is then adjusted until this measured output is the same as stored in the previous step. The DAC setting is stored as Vin2 and the 6.5V reference is Vout2. The gain can now be calculated with the formula: (Vout2 - Vout1)/(Vin2 - Vin1).

# 2-129. AC/DC FREQUENCY RESPONSE CHARACTERIZATION

Characterization is accomplished by first performing an ac/dc transfer with the Oscillator Output set to a low frequency. The ac/ac thermal sensor circuit, containing the thermal sensor U16 and op amp U15D, characterizes the frequency response of the main ac/dc thermal sensor. This sensor has no active circuitry at its input, and all switching is done by relays to insure a flat frequency response.

In the 20V range, the Oscillator Output is switched through R34 to the ac/ac thermal sensor via SENSE HI, K5, and K9 in the set position. In the 2.2V range, R34 is bypassed by K9 in the reset position. The output of this sensor is routed to the RCL line via U19C and K6. A reading is taken and stored in memory as ACref.

The output frequency of the Oscillator Output is changed to the first cal point and the 15-bit dac is adjusted until the reading from this ac/ac thermal sensor is the same as ACref.

The RCL line is then switched back to the ac/dc thermal sensor. A reading is taken stored in memory as ACdif. The gain constant is calculated using the formula (ACdif + Vdac)/Vdac, where Vdac is the DAC assembly (A11) voltage.

This ac/ac transfer function is also performed for the 220V range and the 1100V range. These ranges are generated by the Power Amplifier assembly (A16) and the High Voltage/High Current assemblies (A14 and A15). High voltage ac signals are attenuated and connected to AC CAL, where they are connected to the sensor though relay K5 in the reset position. In the 220V range, the output of the sensor is divided by Z4 and connected to the RCL line by U19D and K6.

Protection for this thermal sensor is provided by comparator U22D, FET Q14, zener diodes VR5, VR6, resistor network Z10, and diodes CR12 and CR13. During normal operation, U22D keeps Q14 off. If the junction temperature of the sensor goes above 200 oC, the voltage at pin 3 increases, driving the output of U22D positive. This turns on Q14, shunting the input of the sensor to common through CR12 and CR13.

# 2-130. Oscillator Output Assembly (A13)

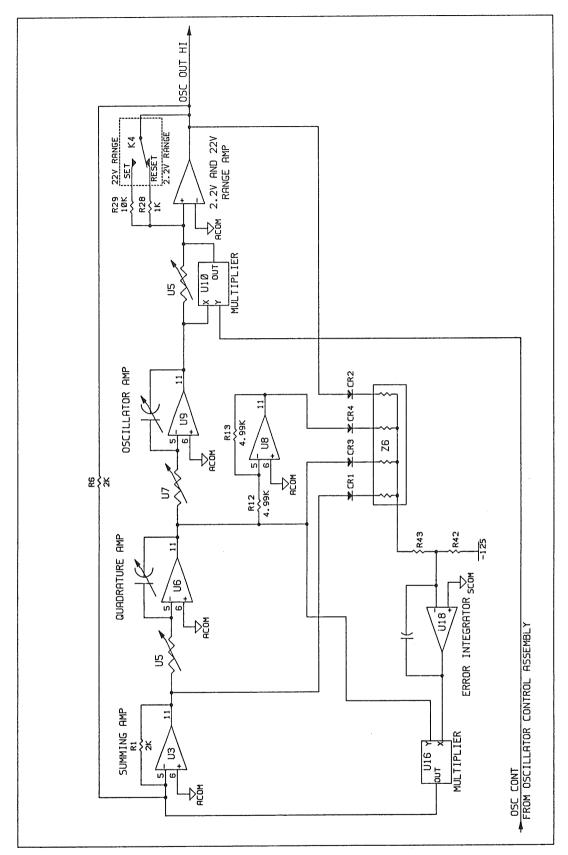

The Oscillator Output assembly is controlled by the Oscillator Control assembly. Refer to Figure 2-20 and the schematic diagram for the following discussion.

The Oscillator Output assembly generates an ac sine wave from 0.22V to 22V with a frequency range of 10 Hz to 1.1999 MHz. There are five frequency ranges (100 Hz, 1 kHz, 10 kHz, 100 kHz and 1 MHz) and two voltage ranges (2.2V and 22V). The output signal is either routed to the OUTPUT binding posts, or it is used internally by the Power Amplifier, High Voltage, Wideband AC Module (Option -03), Current, or Switch Matrix assemblies, or it is routed to an Auxiliary Amplifier for generation of voltages and/or functions outside this range. Output sensing is available for all voltage ranges above 220 mV at the SENSE binding posts.

The Oscillator Output assembly contains a fixed-amplitude quadrature RC oscillator, a 0.22-22V digital/linear gain-controlled amplifier, a fixed-amplitude variable phase-shifting network, phase-locked loop control circuitry for phase locking to an external signal or the PLOCK signal from the Current/Hi-Res assembly (A7), and digital control circuitry.

All power supplies used by this assembly except the -12S supply are generated by the Guard Crossing/Regulator assembly (A17). The -12S supply is generated on this assembly by a three-terminal -12V regulator (U2) using the -17S supply as its input.

Figure 2-20. Quadrature RC Oscillator Circuit

## 2-131. OSCILLATOR OUTPUT DIGITAL CONTROL

The digital control circuit consists of an 82C55 Programmable Peripheral Interface (U26), a 5801 Latching Relay Driver (U24), and three HC374 Octal D-Type Flip Flops (U12, U32, U33). The Programmable Peripheral Interface (U26) is under software control via the guarded digital bus and has three ports which generate 24 outputs. Port A (PAO-PA7) is a common input bus for U24, U12, U32, U33, and U28. Latching relay driver U24 controls the four latching relays K1-K4. Relays K1-K3 select the frequency range and K4 selects the voltage range. This IC is strobed by PC3 of port C and enabled by PC6 of port C. To insure that the relays are latched properly the driver must be enabled for 10 ms.

Latch U32 is clocked by PCO and generates the data bus FREQ DATA for controlling 8-bit resolution hybrid resistive dacs U5 and U7. Latch U12 is clocked by PC1 and generates the data bus AMPL DATA for controlling U11, which is identical to U5 and U7. Latch U33 is clocked by PC2 and generates control bus PHASE, which controls multiplexer U27 in the phase shifter circuit and control bus MUX, which controls the SDL multiplexer U25 in the diagnostic circuit. This diagnostic circuit monitors the  $\pm 44$ S supplies,  $\pm 15$ S supplies, INTEGRATOR OUT, LOOP FILTER OUT, and AMP1 which is from U30, the A13A1 assembly. These voltages are divided by Z2 and Z3 and connected to the SDL line by multiplexer U25, where they are measured by the adc circuit on the DAC assembly (A11).

PBO-PB2 of port B generates control bus PLOCK RNG which is used in the phase-locked loop circuit. PB4 is control line 0/180 to control FET Q7 via comparator U31B in the phase-locked loop circuit. PB6 is control line LFCOMP\* to control FET Q6 via comparator U20A in the integrator circuit. PB7 is control line HFCOMP\*, which is routed to the Oscillator Control assembly (A12). PC4 and PC5 are control lines DAC STRB and DAC SEL respectively, which control the dual 8-bit dac U28 in the phase shifter circuit. PC7 is control line INH to enable the multiplexer U25 in the diagnostic circuit.

## 2-132. QUADRATURE RC OSCILLATOR

The quadrature oscillator is a double integrator type. It contains two op amp RC integrators and a unity-gain inverting summing amplifier. The integrators are identical and use relay-switched feedback capacitors to select five frequency ranges. An 8-bit resolution resistive dac selects frequency within a range.

The summing amplifier uses op amp U3 to provide a  $180^{\circ}$  phase shift in the oscillator loop at unity gain. Its exact phase shift and gain are adjusted by the amplitude control and phase-locked loop circuits to satisfy the conditions required for amplitude stable oscillation: exactly  $360^{\circ}$  loop-phase and unity gain. This amplitude control circuit uses an integrator and multiplier as outlined on page 1 of the schematic. These two circuits are described in detail later.

The two op amp RC integrators are the quadrature amplifier and the oscillator amplifier. Their purpose is to provide  $-90^{\circ}$  each to the loop phase with an amplitude slope of -20dB/decade. The quadrature amplifier contains op amp U6, 8-bit resolution resistive dac U5, and relays K1B, K2B, and K3B. The relays select feedback capacitors C25, C24, C22, and C21 for frequency ranges 100 Hz, 1 kHz, 10 kHz and 100 kHz respectively. For the 1 MHz range, all the above capacitors are removed from the loop, and the only feedback path is C19. The input resistor is the 8-bit resolution resistive dac U5 which is under the control of the FREQ DATA bus from the digital control circuit. Its equivalent resistance is R = (256/X)\*2 kilohm, where X is the digital code on the FREQ DATA bus. The oscillator amplifier contains op amp U9 and performs the same function as the quadrature amplifier. Its input resistance is controlled by resistive dac U7. Relays K1A, K2A, and K3A select the feedback capacitance. Since their phase shift is constant with frequency and the sum of the phase shifts around the loop is zero for all frequencies, we have satisfied one half of the requirement for oscillation. In summing the gain in dB around the loop it is apparent that unity gain occurs at only one frequency. This happens when the closed loop gains of the integrators are unity. This corresponds to  $F = 1/(2 \times PI \times R \times C)$ , which is the frequency of oscillation.

# 2-133. OSCILLATOR AMPLITUDE CONTROL

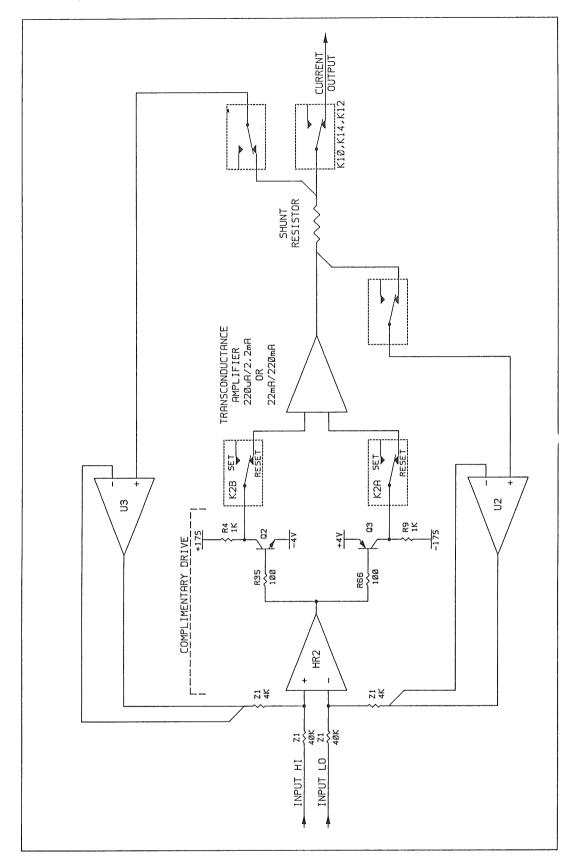

Since small excess phase shifts exist in all three amplifiers and the gain of the summing amplifier cannot be made exactly one, it is impossible to generate an amplitude-stable sinusoidal waveform from just these elements. A control circuit consisting of an error integrator and a linear four-quadrant multiplier is used to sense the output amplitude and stabilize it by adjusting the loop phase shift slightly.

To do this, a fourth oscillator signal is generated using U8 to invert the output of the quadrature amplifier. The Oscillator now has four equal-amplitude signals all spaced  $90^{\circ}$  apart. These signals are rectified and summed by CR1-CR4 and Z6 in such a way that a dc representation of the output amplitude is created. This dc signal is summed with a -12V reference voltage by the error integrator circuit which contains op amp U18. If there is a magnitude difference between the rectified dc and the reference, the output of the error integrator changes. This in turn controls the amplitude of the oscillation. This is done via multiplier U16, a linear-variable resistance with a value inversely proportional to the error integrator output voltage.

If the control input (x input) to the multiplier is zero, the equivalent resistance from the signal input (y input) is infinite. If the control input is negative, the equivalent resistance is negative. The Y signal input of the multiplier is the quadrature amplifier output. Any nonzero control voltage changes the phase shift of the loop by injecting a small amount of out-of-phase current into the summing amplifier. This negative feedback is used to stabilize the amplitude of the oscillating signal by allowing one output amplitude only to satisfy the required conditions of oscillation. During operation in the 100 Hz range, control line LFCOMP\* and comparator U20A turn off FET Q6.

## 2-134. PHASE-LOCKED LOOP

The Oscillator Output assembly is phase locked to an external frequency to increase frequency accuracy. This external frequency comes from the High-Resolution Oscillator on the Current/Hi-Res assembly (A7) or from an external source connected to the rear-panel PHASE LOCK IN jack.

The frequency capture range is approximately  $\pm 5\%$  of the nominal output frequency range. This is done by comparing the oscillator output frequency SUMMING AMP OUT or INT OSC OUT against the external frequency source P LOCK HI with a phase detector. The P LOCK HI signal is referenced to P LOCK LO. The phase-locked loop circuit locks SUMMING AMP OUT to the external frequency when the calibrator is in the 22V range or less. The phase-locked loop circuit locks INT OSC OUT, which is  $180^{\rm O}$  out of phase from SUMMING AMP OUT, during calibrator operation at higher voltages. This occurs because the output from the Power Amplifier and High Voltage assemblies (which are used to generate the higher voltage ranges) are  $180^{\rm O}$  out of phase from the Oscillator output. When the 5700A is in the higher voltage ranges, control line 0/180 and op amp U31B turn on Q7, which selects INT OSC OUT to the Zero Crossing Detector.

Since the phase detector circuit requires digital inputs, both signals are converted to square waves using U23A/B as dual zero crossing detectors. Square waves from the zero crossing detector circuitry are fed to the phase detector circuit containing U22A/B and U21. The phase detector circuit looks for the falling edge of both signals. The first signal that makes a positive to negative transition causes the phase detector to turn on either the positive (CR5, CR6) or the negative (CR7, CR8) charge pump, depending on which signal is first. The Charge Pump is turned off when the other signal makes its transition. Thus the signal with the highest frequency has its respective charge pump pulsed on and off while the other charge pump remains off.

The accumulated charge is integrated by the loop filter circuit, which contains op amp U31A, multiplexer U17, Z1, and C75-C84. Multiplexer U17 is controlled by the PLOCK RNG control bus from the digital control circuit. This multiplexer changes the cross-over point of the loop filter by selecting C83 and C84 for feedback in the 100 Hz range. Capacitors C81 and C82 are used for the 1 kHz range, C79 and C80 for the 10 kHz range, C77 and C78 for the 100 kHz range, and C75 and C76 for the 1 MHz range.

The output of the loop filter controls two multipliers (U15 and U19) similarly to the amplitude control section. The only difference is that the signal input is derived from the in-phase signal. In the case of U15, the input signal is QUADRATURE AMP OUT, which changes the unity-gain frequency of the oscillator amplifier. In the case of U19, the input signal is SUMMING AMP OUT, which changes the unity-gain frequency of the quadrature amplifier. The new frequency of oscillation is the new unity gain frequency of the integrators. Under phase-locked conditions, neither charge pump is allowed to turn on because neither signal reaches the phase detector first.

### 2-135. 2.2V AND 22V RANGE OUTPUT AMPLIFIER

The 2.2V and 22V range output amplifier is an inverting wide-band low-distortion amplifier that provides output signal OSC OUT HI at the OUTPUT binding posts in the 2.2V and 22V ranges. OSC OUT HI is used by the Power Amplifier and High Voltage assemblies to generate the higher voltage ranges.

This amplifier uses a surface-mount gain block (U30) called the Oscillator Wideband SMD PCA (A13A1) and a complementary Darlington emitter follower bootstrapped output stage. Relay K4 selects feedback resistor R28 for the 2.2V range and R29 for the 22V range. It also changes the open-loop frequency response for each voltage range. Its gain within a range is controlled by the gain control multiplier circuit and the dac gain control circuit.

The dac gain control circuit contains the same 8-bit resolution resistive dac (U11) as in the oscillator with the exception that it is controlled by the AMPL DATA control bus from the digital control circuit. This resistive DAC provides the coarse gain control. The gain control multiplier circuit contains a multiplier U10, which provides a small linear control range of several dac counts. The control input to the multiplier, OSC CONT, comes from the Oscillator Control assembly (A12). This allows the output amplitude to be adjusted as required by the Oscillator Control Assembly. The theory of operation for the rest of the output stage is described following the A13A1 theory.

### 2-136. Oscillator Wideband SMD Assembly (A13A1)

The A13A1 is a surface-mount assembly on the Oscillator Output assembly (A13) that provides the 22V output signals of the 5700A. It is essentially an operational amplifier built using discrete components to provide the necessary speed, power output and breakdown voltage required for such a high output signal.

The input stage is a differential pair (Q2 and Q3) that is buffered by a source follower Q1. The transconductance is determined by R3, R4 and R26. The inherent input offset voltage of this stage is corrected by U1 and U2 and related components. The output of Q3 is level-shifted by VR5-VR7 before being applied to the mid stage. Transistor Q4 serves as a high-impedance current sink used to bias the input stage to approximately 10 mA. Potentiometer R30 adjusts the dc zero at the output of U2.

The mid stage is a common-emitter, Miller-compensated gain stage (Q5) that drives a common-base level shifter (Q13) on the Oscillator Output assembly. This stage is current limit protected by R12 and Q4. The dominant pole is set with the Miller capacitor C5 and the input stage transconductance. The mid stage is biased to 10 mA by Q6 and related components.

The output stage of the amplifier is a bootstrapped complementary Darlington pair. The only parts of the output stage on this A13A1 assembly are the input transistors Q7 and Q8. The output bias current is set by R17 and CR4-CR5 to be approximately 40 mA. This keeps the output stage class A for all normal output conditions.

## 2-137. OUTPUT STAGE

The output stage circuit is a complementary Darlington emitter follower bootstrapped buffer amplifier. The input transistors are Q7 and Q8 on the A13A1 assembly. These transistors drive the output transistors Q8 and Q14 respectively. Transistors Q10 and Q11 in the positive side and Q16 and Q17 in the negative side are parallel transistors bootstrapped by VR3 and VR4. Current sources CR13, CR14, CR17, CR18, CR15, CR16, CR11, and CR20 provide the bias current for their respective bootstrapped transistors. Current limiting for the positive side is provided by Q9 and R91. During an overcurrent condition, the voltage drop across R91 turns on Q9, which draws current away from the base of Q11. Current limiting is done in the same manner for the negative side with Q15 and R99.

Switch S1 can be switched to pull the input of the A13A1 output stage low for troubleshooting the output stage. Refer to the Oscillator Output troubleshooting section for more information.

## 2-138. PHASE SHIFTER

The phase shifter circuit provides a fixed amplitude variable phase auxiliary signal at the rear panel of the calibrator. This signal is the same frequency as the output, but can be phase shifted over a  $360^{\circ}$  range. The four phases (each  $90^{\circ}$  apart) for the oscillator circuit are divided by Z4 and Z5. These signals are connected to the dual four-channel multiplexer (U27), which is under the control of the PHASE control bus from the digital control circuit. This multiplexer selects any two adjacent oscillator phases (e.g.  $0^{\circ}$  and  $90^{\circ}$ ) that are connected to the input of a dual monolithic DAC U28. These signals are then scaled by the dac (U28), also under the control of the digital control circuit. The two outputs of this dac are summed by op amp U29. Using this method, the output of U29 is a phase shifted signal between 0 and  $360^{\circ}$ , where the scaling of the signals controls the phase shift within a  $90^{\circ}$  range.

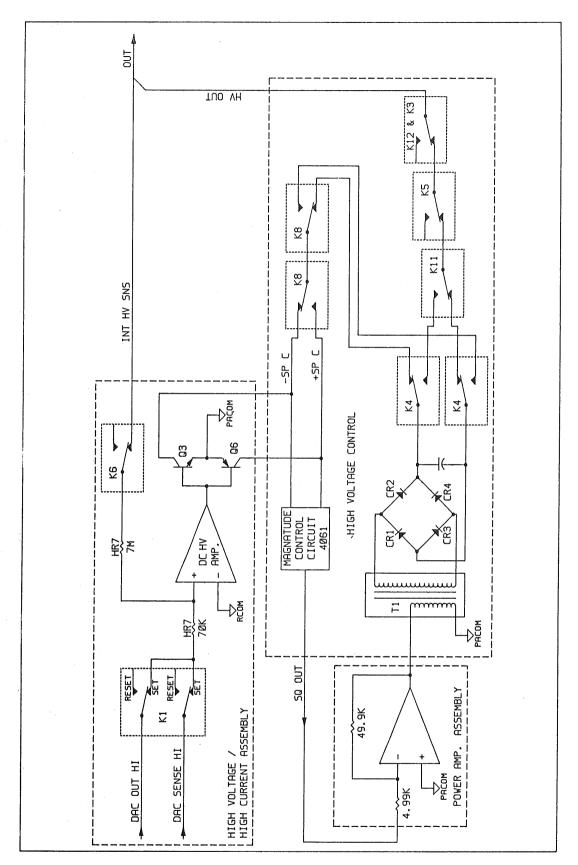

# 2-139. Power Amplifier Assembly (A16)

The Power Amplifier assembly outputs dc voltages from  $\pm 22V$  to  $\pm 219.99999V$  and ac voltages from 22V to 219.99999V rms. The frequency limit for 220V ac output is 100 kHz. Output voltage limits are derated at frequencies above 100 kHz. At 1 MHz, the maximum output voltage is 22V rms. The Power Amplifier drives the High Voltage assemblies (A14, A15) in all high voltage and high current functions.

This assembly also contains calibration circuitry that enables the internal calibration system to determine exact Power Amplifier ac and dc gain, offsets and frequency response.

The main sections of this assembly are the input stage, mid stage, output stage, sense-current cancellation circuit, the dc and ac gain calibration circuits, and the Power Amplifier Digital Control SIP assembly (A16A1), which is mounted on the Power Amplifier assembly.

2-140. POWER AMPLIFIER DIGITAL CONTROL SIP ASSEMBLY (A16A1)

Digital control for the Power Amplifier assembly is contained on the SIP assembly (A16A1) mounted at the bottom of the Power Amplifier. This assembly configures the Power Amplifier assembly for its various modes of operation. (Also see "+PA Supplies Digital Control" in the Power Amplifier Supply theory of operation.)

The heart of the Digital Control assembly is an 82C55 Programmable Peripheral Interface IC (U11) operating under software control via the guarded digital bus. This IC has three ports that generate 24 outputs. These outputs control two 5801 relay driver ICs (U10, U12), two LM339 Comparators (U13, U15) and an analog multiplexer (U14) used for diagnostics.

Relay driver U10 generates eight control lines (LCO\*-LC7\*) that control four latching relays (K1-K4). Relay driver U12 generates eight control lines (CO\*-C7\*) for non-latching relays K10-K17. CO\* also controls FETs Q57 and Q58. Port A (PAO-PA7) from U11 provides an input bus common to relay drivers U10 and U12. Each driver has separate strobe and enable lines from port C of U11. Driver U10 is strobed by PC7 and enabled by PC5. Driver U12 is strobed by PC4 and enabled by PC6. When a STROBE line is selected, data on the bus (PAO-PA7) is strobed into the respective driver chip. When an ENABLE is selected, this strobed data appears at the output, thereby energizing the appropriate relays. Latching relays only need to be energized for 10 ms; non-latching relays need to be energized continuously.

As an example, the following steps are taken to set up latching relays controlled by relay driver U10.

- 1. Write the proper data for these relays to port A of the 82C55 (U11).

- 2. Write hex A to PC4-PC7 to strobe the data into U10.

- 3. Write hex 0 to PC4-PC7, wait 10 ms and write hex 2 to PC4-PC7. This takes U10's output out of tri-state and energizes the proper relay coils for 10 ms. Since PC4 and PC6 are always low, U12 is undisturbed.

Two LM339 quad comparators (U13 and U15) get their data from port B of U11 (PBO-PB7) and generate control lines SWO-SW7. SWO-SW2 are inputs to decoder U9, which generates eight additional control lines (CONTO\*-CONT7\*) for controlling FETs and solid state switches. Control line SW3 controls FETs Q50 and Q51. Control lines SW4-SW7 are routed through the Motherboard to the Filter/Power Amplifier Supply assembly (A18) to control the +PA and -PA supplies.

The diagnostic circuit enables the 5700A to monitor eight diagnostic (MUX) signals on the Power Amplifier assembly. A 4051 analog multiplexer (U14) is controlled by PCO-PC3 from U11. This multiplexer selects of the eight MUX signals to the SDL line, where it is measured by the adc circuit on the DAC assembly (A11). Resistor network Z2 and various resistors and zener diodes on the Power Amplifier assembly divide these MUX signals down to a proper level for measurement by the adc circuit. The eight monitored points are:

- o MUXO Output of U7; indicates the status of the amplifier loop

- o MUX1 +PA Supply

- o MUX2 -PA Supply

- o MUX3 Power Amplifier output

- o MUX4 Indicates the temperature of the Power Amplifier assembly

- o MUX5 Power Amplifier dc input

- o MUX7 Diagnoses the state of the hybrid heater-control circuit

### 2-141. PA COMMON CIRCUITRY

Common circuitry consists of the +PA and -PA supplies, input stage, mid stage, and the output stage. These four circuits are described under the next four headings.

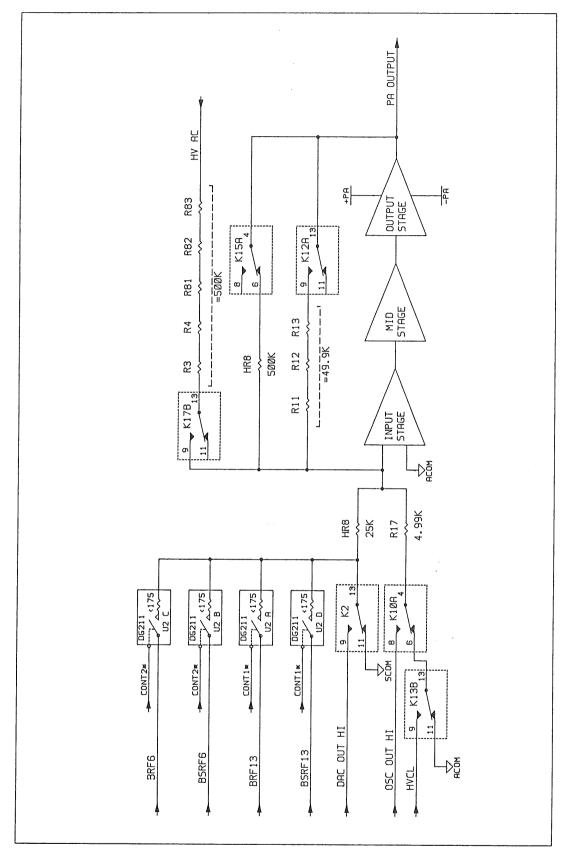

Power Amplifier input node, gain, and feedback are different for dc and ac operation. Power Amplifier gain is -20 in the dc function, determined by the ratio of resistor network bonded to the HR8 assembly (500 kilohm/25 kilohm). Gain in the ac function is -10, which is determined by the ratio resistors [(R11 + R12 + R13)/R17]. This is described in more detail under "DC Voltage Function" and "AC Voltage Function".

# 2-142. +PA AND -PA SUPPLIES

The  $\pm PA$  supplies are high voltage supplies generated by the Filter/PA Supply assembly (A18). These supplies can be controlled by the Digital Control SIP assembly (A16A1) and are switched between the two modes shown in Table 2-13.

- o +185V

- o +365V

Theory of operation for the Filter/PA Supply assembly (A18) describes how these voltages are generated and selected.

| Table 2-13. | +PA a | nd -PA | Supply | Settings | at | Different | Outputs 0 |

|-------------|-------|--------|--------|----------|----|-----------|-----------|

|-------------|-------|--------|--------|----------|----|-----------|-----------|

| CALIBRATOR OUTPUT              | +PA   | -PA   |

|--------------------------------|-------|-------|

| Less than 22V ac or dc         | +185V | -185V |

| 22 to 110V dc                  | +185V | -185V |

| 110 to 220V dc                 | +365V | -185V |

| -220 to -110V dc               | +185V | -365V |

| 22 to 101V ac (freq < 120 kHz) | +185V | -185V |

| 22 to 85V ac (freq > 120 kHz)  | +185V | -185V |

| 0ther voltages                 | +365V | -365V |

| 220 to 550V de or ae           | +185V | -185V |

| 550 to 1100V de or ae          | +365V | -365V |

| 220 mA to 2.2A                 | +365V | -365V |

### 2-143. PA INPUT STAGE

The input stage consists of a heater-controlled hybrid HR8, op amp U7, transistor Q6, and JFET Q2. The HR8 assembly consists of an op amp mounted on a heated-substrate hybrid, with a resistor network bonded to it. Hybrid HR8 provides the input stage with excellent dc characteristics of low offset, noise and drift. The hybrid heater-control circuit (on page 3 of the schematic) adjusts the base voltage of Q38 to deliver the correct current to the heater resistor. This maintains the hybrid assembly at a constant temperature in spite of environmental temperature variations. Transistor Q35 protects the hybrid in case Q38 fails. Input of the hybrid op amp is protected by CR13 and CR14. Output of the hybrid op amp is connected to the input of a faster op amp (U7), which provides additional dc gain and a higher slew rate. JFET Q2 and transistor Q6 combined with these two op amps complete the input stage. Q2 is a very low-bias-current, high-frequency JFET.

In mid to high-frequency operation, Q2 is effectively the only path for the input stage signal. HR8 and the U7 op amps are bypassed at these frequencies by R89, C42, R24, and C12. As a result, the base of Q6 is at ac ground. In dc to mid-frequency operation, the gate of Q2 is at ground potential. At any frequency, the potential difference between the gate of Q2 and the base of Q6 results in a current through Q6 as determined by the network consisting of R22, R145, and L11 and by the transconductance of Q2 and Q6. The input stage is called a transconductance stage because an input voltage results in a current output at the collector of Q6.

This current output is coupled to the mid stage (Q12, Q14, and Q16) by Q8, Q9, Q13 and C15, where it results in a voltage across the base-emitter of Q16 (the input of the mid stage). Current source Q9 determines bias current in Q2 and Q6. Variations of Q6 output current become voltage variations at the base of Q16. This transfer is through Q8 and Q13 at dc and low frequencies, and through C15 at high frequencies.

The input stage operates with low voltage supplies  $(\pm 17\text{V})$  whereas Q16 of the mid stage is connected to the -PA supply, which can be as high as -365V. This potential difference is dropped across level shifter Q13.

### 2-144. PA MID STAGE

The mid stage (Q12, Q14, and Q16), biased by the 8 mA current source (CR53, Q31, Q32 and R87 on page 2 of the schematic), is a voltage amplifier providing additional gain. The base of transistor Q16 is the input to the mid stage. MOSFETs Q12 and Q14 are biased by R41 and R53 respectively. Components CR21, CR23, and VR22 protect Q12 from excessive source-to-gate voltage, and R112 prevents Q12 from oscillating. Components CR25, CR29, VR28, and R113 perform the same function for Q14. A signal at the base of Q16 appears amplified at the drain of Q12. Total impedance from the drain of Q12 to ground, divided by R58, determines gain at dc and low frequencies. At high frequencies, the effective drain to ground impedance is R53. Relay K12A parallels C18 and C57 during dc operation for a lower bandwidth. Capacitors C18 and C57 provide the Miller capacitance for the amplifier.

Transconductance gain of the input stage and the Miller capacitance determine Power Amplifier frequency response at high frequencies. All the voltage gain of the Power Amplifier comes from the input and mid stages.

### 2-145. PA OUTPUT STAGE

The Output Stage is an emitter follower that provides current gain but no voltage gain. It is needed because the mid stage cannot drive the rated load by itself.

Voltage across R74 and R35 determines the bias current through the output stage. This voltage equals the voltage across Q7, minus the value (4 x Vbe) (for each transistor Q4, Q5, Q10, and Q11). Transistor Q7 is configured as a Vbe multiplier, the voltage across which (and thus the output stage bias current) is the value (1 + (R23+R26)/R32). The output bias current is 50 mA.

NMOSFETs Q1, Q3, and transistor Q5 source current, while PMOSFETs Q15, Q17, and transistor Q10 sink current from the load. This output stage can drive up to 50 mA of load current as determined by the current limit circuit on  $\pm$ PA supplies on the Filter/PA Supply assembly (A18).

Zener diodes VR15 and VR18 bootstrap NMOSFETs Q3 and Q15 respectively, and provide the power supplies SC+ and SC- to op amp U1 in the sense current cancellation circuit. Two stacked NMOSFETs (Q1, Q3) on the top end (+PA side), and two stacked PMOSFETs (Q15, Q17) on the bottom end (-PA side) withstand the high voltage drops between ±PA supplies and output. NMOSFETs Q1 and Q3 are biased by R15 and R19 respectively. PMOSFETs Q15 and Q17 are biased by R52 and R57 respectively. Components CR5, CR7 and VR6 protect Q1 from excessive source-to-gate voltage and R108 prevents Q1 from oscillating. Protection is also provided for remaining MOSFETs in the output stage. Output of this stage, called PA OUT HI, is the output of the Power Amplifier assembly. Components R120 and L10 isolate capacitive loads.

## 2-146. PA SENSE CURRENT CANCELLATION CIRCUITRY

During dc operation of the Power Amplifier, sense current in the 500 kilohm feedback resistor (on the resistor network in the HR8 assembly) can cause an output error because of the finite resistance path of the connection to the load. Op amp U1 eliminates this error by feeding an equal and opposite current in this path. The magnitude of this current is determined by PA OUT HI, which is connected to the non-inverting input of U1. This circuit generates a current through R8, which is equal to current flowing through the 500 kilohm feedback resistor. Sense-current cancellation is active only in dc 220V range.

# 2-147. PA IN STANDBY

The Power Amplifier schematic shows all relays and DG211 FET switches in the standby condition. The Power Amplifier 25 kilohm input resistor and R17 are tied to OS COM through Q39 and R118. Power Amplifier output is close to zero and the whole loop is stabilized.

To better understand Power Amplifier configuration in the ac/dc 220V range, refer to Figure 2-21.

## 2-148. PA OPERATION: 220V DC RANGE

During dc operation, Power Amplifier gain is -20, as determined by the 500 kilohm/25 kilohm resistor network on the HR8 assembly. Control line SW3, inverted by U8, turns on Q51. This references the +input of the precision op amp in the input stage to R COM. The DAC assembly is set to the negative 11V range and its outputs, DAC OUT HI and DAC SENSE HI, are connected to pin 2 of the resistor network on the HR8 assembly by relay K2. The sense current cancellation circuit is active during dc operation. Its output, SIG1, is connected to the resistor network feedback resistor pin 1 by relay K15A. The amplifier has a much lower bandwidth in this mode because of the much higher Miller capacitance in C57. Lower bandwidth results in lower amplifier noise.

The output signal, PA OUT HI, is routed to the High Voltage Control assembly (A14), where it goes through relay K10 and becomes PA OUT DC. PA OUT DC is routed to the Switch Matrix for connection to the OUTPUT HI binding post. The sense signal, PA SENSE DC from the Sense Current Cancellation circuit, is routed to the Switch Matrix assembly (A8) for connection to the OUT/SENSE HI or SENSE HI binding posts, thus making the binding post the sense point in internal sense and allowing for external sense through the SENSE HI binding post.

# 2-149. PA OPERATION: 220V AC RANGE

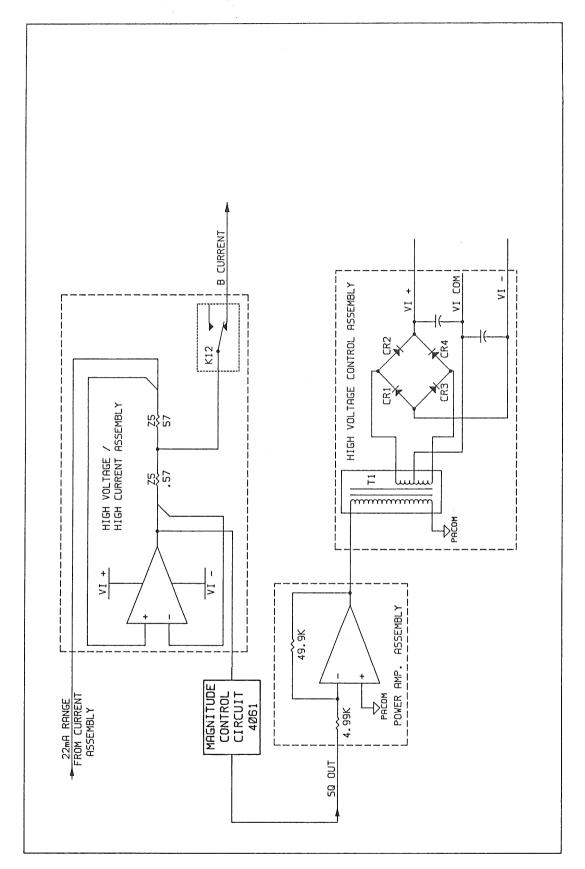

During ac operation, Power Amplifier gain is -10 as determined by the 4.99 kilohm input resistor R17, and 49.9 kilohm feedback resistors (R11 + R12 + R13). Control line SW3 turns Q50 on, which references the +input of the precision op amp in the input stage to OS COM. The Oscillator assembly (A13) is set to the 22V range and its output OSC OUT HI is connected to the input resistor R17 by relay K10A. The Power Amplifier output is connected to the feedback resistors R11-R13 by relay K12B.

Figure 2-21. Power Amplifier Simplified Schematic

The Power Amplifier output is attenuated by a precise 1/100 by 220V range ac attenuator. The attenuated signal is connected to OSC SENSE HI, where it is sent to the Oscillator Control assembly (A12). The Oscillator Control assembly regulates the Oscillator Output so that an exact calibrated ac signal appears at OSC SENSE HI. Since the 220V range ac attenuator is completely characterized (as explained below), the exact desired signal appears at PA SENSE AC and hence at the appropriate sense point at the output.

The 220V range ac attenuator circuit contains op amp U4, a 400 kilohm/4 kilohm resistor network Z1, and transistor Q54. PA SENSE AC, which is connected to PA OUT HI at the load, is connected to the 400K input resistor (pin 1) of Z1 by relay K16. The 400 kilohm/4 kilohm node (pin 3) of Z1 is connected to the inverting input of U4.

During ac operation, control line CO\* is inverted by U8, which turns on Q58 to connect the non-inverting input to OSC RCOM. Transistor Q54 supplies current gain for the output of U4 to drive the capacitance of the OSC SENSE HI line. This voltage is connected to the 4 kilohm feedback resistor (pin 4) of Z1. The output is connected to OSC SENSE HI by relays K10B and K11. The dc feedback 500 kilohm/25 kilohm resistor network and the sense-current cancellation circuitry are disconnected by energizing K15.

The sense signal, PA SENSE AC, and the output signal, PA OUT HI, are routed to the High Voltage Control assembly (A14), where relays K10, K13, and K3 connect them to HV SNS and HV OUT. HV SNS and HV OUT are connected to the binding posts by the Motherboard relays in the same manner as in the 1100V high voltage mode. Refer to the High Voltage assembly theory of operation for more information.

2-150. HIGH VOLTAGE ASSEMBLY SUPPORT MODE

2-151. High Voltage AC 1100V Range