## **Getting Started Guide**

### HP 1650B/HP 1651 B Logic Analyzers

**OTS LIBRARY**

@Copyright Hewlett-Packard Company 1989

Janual Part Number 5952-4240

Printed in the USA. July 1989

01650-90914

#### **Contents**

#### Introduction About this book . . . Chapter 1: Introducing the HP1650B/HP1651B What Are the HP 1650B and HP 1651B? ..... 1-1 operating Environment ...... 1-6 Ventilation ..... Installing the Operating System Disc ...... 1-8 Line Switch ..... 1-9 Intensity Control Power-up Self-Test ...... 1-10 Chapter 2: **Getting to Know the Front Panel** Front Panel Organization ..... Cursor Kevpad ..... Roll ..... 2-4 Menu .... 2-5 Display ..... Disk Drive ..... .2-7

| Chapter 3: | How Do I Use the Front Panel?  IntroductionI |  |  |  |

|------------|----------------------------------------------|--|--|--|

| Chapter 4: | Learning the Basic Menu8  Introduction       |  |  |  |

| Chapter 5: | Using the Timing Analyzer  Introduction      |  |  |  |

|            | Display Resolution 5-12 Making the Measurement 5-13 Finding the Answer 5-14 summary 5-15 |  |  |  |

|------------|------------------------------------------------------------------------------------------|--|--|--|

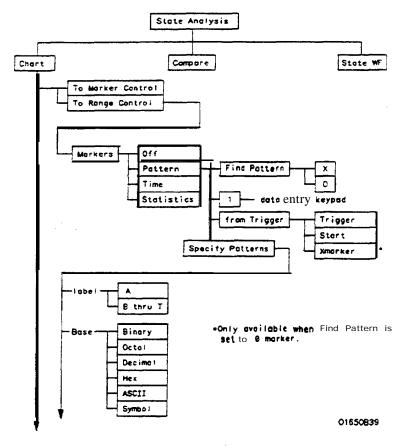

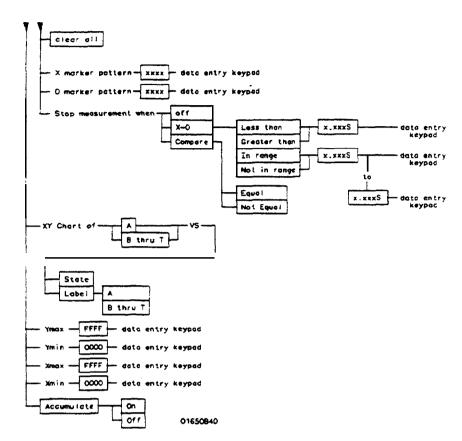

| Chapter 6: | Using the State <b>Analyzer</b>                                                          |  |  |  |

|            | Introduction 6-1                                                                         |  |  |  |

|            | ProblemSolvingwiththeStateAnalyzer                                                       |  |  |  |

|            | What Am I Going to Measure? 6-2                                                          |  |  |  |

|            | How Do I Configure the Logic Analyzer? 6-4                                               |  |  |  |

|            | Connecting the Probes 6-6                                                                |  |  |  |

|            | Activity <b>Indicators</b> 6-6                                                           |  |  |  |

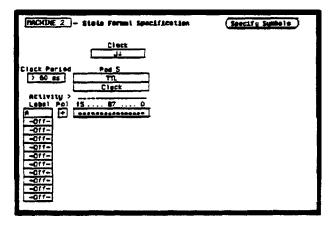

|            | Configuring the State Analyzer 6-7                                                       |  |  |  |

|            | Specifying the J Clock                                                                   |  |  |  |

|            | Specifying a Trigger Condition 6-10                                                      |  |  |  |

|            | Acquiring the Data 6-12                                                                  |  |  |  |

|            | The State Listing 6-13                                                                   |  |  |  |

|            | Finding the Answer 6-14                                                                  |  |  |  |

|            | Summary                                                                                  |  |  |  |

| Chapter 7: | Using the Timing/State Analyzer  Introduction                                            |  |  |  |

|            | What Additional Measurements Must I Make?7-7                                             |  |  |  |

|            | How Do I <b>Re-configure</b> the <b>Logic</b> Analyzer?                                  |  |  |  |

|            | Connecting the Timing Analyzer Probes                                                    |  |  |  |

|            | Configuring the Timing Analyzer                                                          |  |  |  |

|            | Setting the Timing Analyzer Trigger                                                      |  |  |  |

|            | Time Correlating the Data                                                                |  |  |  |

|            | Re-acquiring <b>the</b> Data                                                             |  |  |  |

|            | Mixed Mode Display                                                                       |  |  |  |

|            | Interpreting the Display                                                                 |  |  |  |

|            | Overlapping Timing Waveforms                                                             |  |  |  |

|             | Finding the Answer Summary                          |             |  |

|-------------|-----------------------------------------------------|-------------|--|

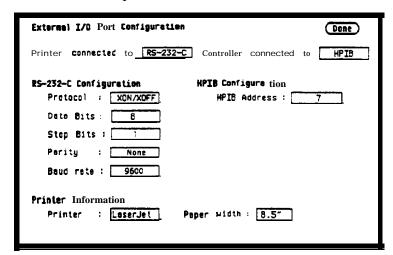

| Chapter 8:  | Making Hardcopy Prints                              |             |  |

| •           | Introduction                                        | 8-1         |  |

|             | Hooking Up Your Printer                             |             |  |

|             | Setting RS-232C for HP Printers                     |             |  |

|             | Setting RS-232C for Your Non-HP Printer             |             |  |

|             | Setting HP-IB for HP Printers starling the Printout |             |  |

|             | Print screen                                        |             |  |

|             | Print All                                           |             |  |

|             | What Happens during a Printout?                     | s-6         |  |

|             | Summary                                             | 8-7         |  |

| Chapter 9:  | What's Next?                                        |             |  |

| Appendix A: | Logic Analyzer Turn-on Check List                   | <del></del> |  |

|             | <u></u>                                             |             |  |

| Appendix B: | Leading Dama Files from the Diek                    |             |  |

| Appendix b: | Loading Demo Files from the Disk                    |             |  |

#### Introduction

## About this book. . .

Welcome to the new generation of **HP** logic **analyzers**. The HP **1650B/51B** logic **analyzers** have been **designed** to be the easiest to use logic **analyzers** ever. In addition to beil easy to use, these logic **analyzers** make a **significant** contribution to digital measurement **technology**.

That's why we'd like you to invest your time going through this *Getting Started manual* Whether you're a novice logic analyzer user or just new to these particular models, this book will give you a working **knowledge** of the HP **1650B/51B** so that you can start using it to solve your measurement problems. It **covers:**

- front panel organization;

- how to operate the front panel;

- learning the basic menus;

- · how to set up the analyzer;

- how to make basic measurements.

To make the book easier to use, we have put the names of **keys** (FORMAT, SELECT etc.) in bold type. And we have highlighted actions (rotate the knob, press the **DISPLAY**) in color.

If you are au experienced HP logic **analyzer** user but new to this family of logic **analyzers**, you may feel like going directly to the reference manual. We'd like you to reconsider and read chapters 1 through 4 first. These chapters will **only** take a few **minutes** and you will **find** the user interface of the **HP 1650B/51B** very friendly **and** easy to learn.

Don't **worry...we** didn't **try** to cover every feature and function of the **HP 1650B/51B** logic analyzer **in** this manual That's the job of your **HP 1650B/51B Front-Panel** manual

If you're new to logic analysis...or just need a refresher, we think you'll find *Feeling Comfortable With Logic Analyzers* valuable reading. It will help you sort out any confusion you may have about their application and show you how to get the most out of your new logic analyzer.

#### Introducing the HP1650B/HP 1651B

What Are the HP 1650B and HP 1651B?

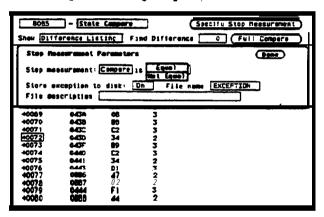

The HP 1650B/51B logic analyzers are new general-purpose logic analyzers with improved features to accommodate next-generation design tasks. They are basically the same as their predecessors the HP 1650A and HP 1651A, but now have State Compare, State Waveform, and State Chart modes. They both have HP-IB capabilities in addition to RS-232C. Both the 80-channel HP 1650B and the 32-channel HP 1651B logic analyzers are capable of 100 MHz timing analysis. The HP 1651B is capable of 25 MHz state analysis while the HP 1650B is capable of 35 MHz state analysis on all channels. The HP 1651B, while only having 32 channels, has basically the same features as the HP 1650B. That's why you have the same manual set regardless of whether you have an HP 1650B or HP 1651B.

The key features of the HP 1650B and HP 1651B are:

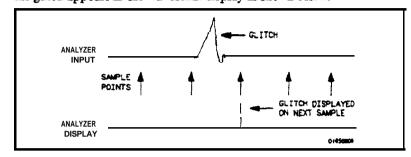

- Transitional or glitch timing modes

- Simultaneous state/state or state/timing modes

- 1k-deep memory on all channels

- Glitch detection on all channels

- Maker measurements

- · Pattern, edge, and glitch triggering

- Overlappii of timingwaveforms

- Eight sequence levels

- Eight pattern recognizers

- One range recognizer

- Small lightweight probing

- · Time and number of states tagging

- Pre-store

- State Compare

- State Waveform

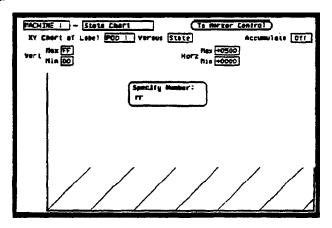

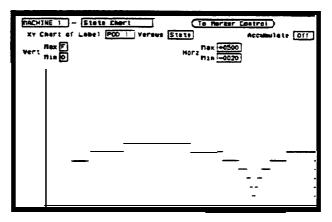

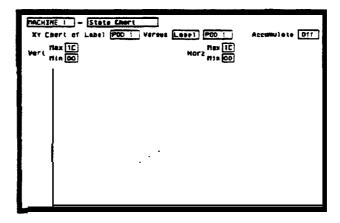

- State Chart

Not all of these features will be covered in this Getting Started manual. However, you can find the details of these and all the features of the HP 1650B/1651B in the HP 1650B/HP 1651B Reference manual.

HP 1650B/HP 1651B Getting Started Guide What Is the HP 1650B/HP 1651B?

## Getting Ready to Operate

If you have just unpacked your new HP 1650B/51B logic analyzer, please take a few minutes to completely read this chapter. It tells you how to prepare your Logic analyzer for applying power and turning it on. If you are learning how to use the logic analyzer and it is already turned on, start with with chapter 2 "Getting to Know the Front Panel".

## Initial Inspection

Inspect the **shipping container** for damage. If the shipping container or packaging materials are damaged, you should keep them until the contents of the shipment have been checked for completeness and the instrument has been checked mechanically and electrically.

If the contents of the shipping container have been damaged or the instrument does not operate properly, refer to the service manual.

#### **Accessories**

In addition to checking the instrument for damage, you should also check to see that the accessories supplied with it are complete. Accessories can sometimes be lost in transit when the shipping container is damaged.

The Front-Panel Reference manual lists all the accessories for the HP 1650B/51B logic analyzers. If any of these items are missing contact your nearest Hewim-Packard office.

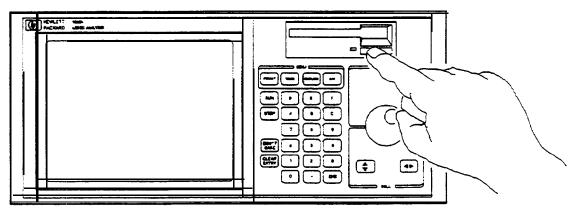

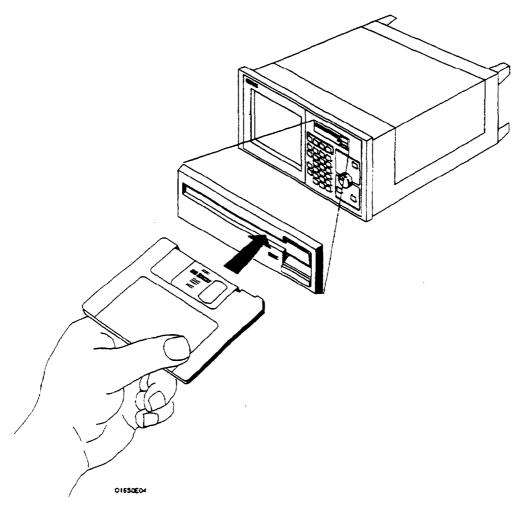

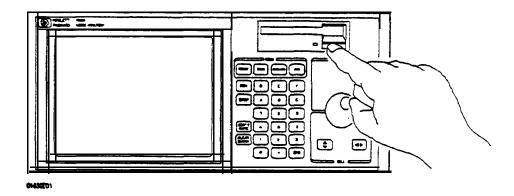

#### Removing Yellow Shipping Disc

Your logic analyzer is shipped with a protective yellow shipping disk in the disk drive. Before you can insert the operating system disk you must remove the yellow shipping disk. Press the disk eject button as shown in the figure. The yellow shipping disk will pop out part way so you can pull it out of the disk drive.

01850E01

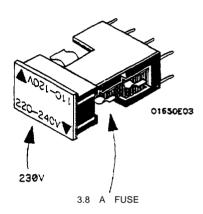

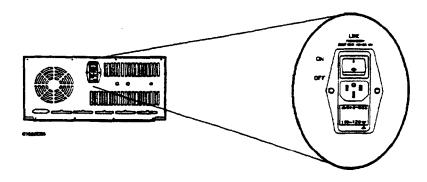

## Selecting the line Voltage

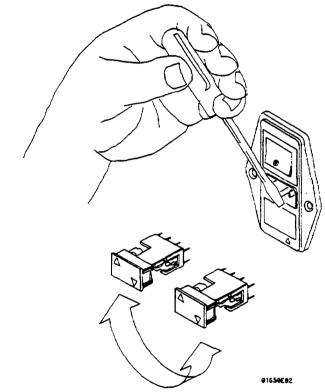

The line voltage selector has been factory set to the line voltage used in your **country**. It is a good idea to check the setting of the line voltage selector so you can become **familiar** with what it looks like. If the setting needs to be changed, follow the procedure in the next paragraph.

#### CAUTION

You can damage the logic **analyzer** if the module is not set to the **correct position**.

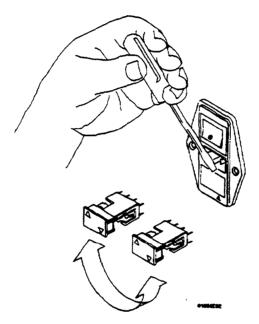

You change the line voltage setting by pulling the fuse module out and reinserting it with the **proper** arrows aligned To remove the fuse **module**, **carefully** pry at the top center of the module (as shown) until you can grasp it and pull it out by hand.

What Is the HP 1650B/HP 1651B? 1-4

HP 1650B/HP 1651B Getting Started Guide

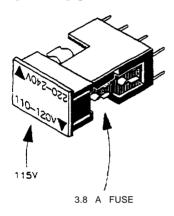

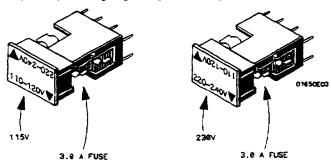

#### Checking for the Correct Fuse

If you need to check for the correct fuses, remove the fuse module and look at the amperage and voltage of each fuse. The following figure will help you locate the 115 V and 230 V fuses. To remove the fuse module, carefully pry at the top center of the module until you can grasp it and pull it out by hand. (Refer to "Selecting the Line Voltage" on the previous page.)

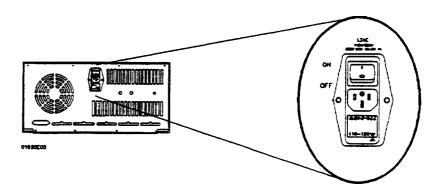

#### **Getting Power** to the Instrument

The HP 1650B/51B comes with a 3-wire power cable. When you connect the cable to an appropriate AC power receptacle, a ground is provided for the **instrument** cabinet. The type of power cable you **receive** with the instrument depends on your **country**.

WARNING 🥻

To avoid possible shock hazard, you must connect the instrument to a properly grounded 3-wire receptacle.

#### **Operating Environment**

You may operate your logic analyzer in a normal lab or office **environment** without any additional considerations. But don't block its **ventilation.** If you intend to use it in another type of **environment**, you must not exceed certain limits. You can find these limits in the HP 1650B/HP 1651B Front-Panel Reference manual.

#### Ventilation

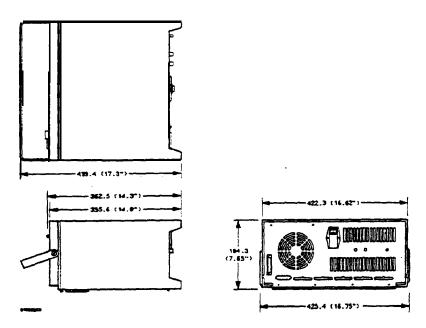

You must provide an unrestricted airflow for the fan and ventilation openings in the rear of the logic analyzer. However, you may stack the logic analyzer under, over, or in-between other instruments as long as **the** surfaces of the other instruments aren't needed for their ventilation.

#### Loading the **Operating System**

Before you can operate the logic analyzer, it must transfer its operating system from a disk to its memory. This is called "loading the operating system" or "booting.

The logic analyzer operating system is a set of instructions that control the operation of the instrument. The operating system resides on a 3.5-inch flexible disk. You received two identical operating system disks. You should mark one of them Master and store it in a safe place. Mark the other one Work and use only the work copy. This will provide you with a back-up in case your work copy becomes corrupt.

CAUTION 👺

To prevent damage to your operating system disk, DO NOT remove the disk from the disk drive while it is running. Only remove it after the indicator light has gone out

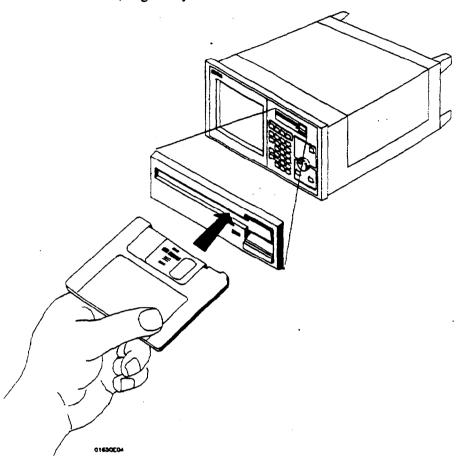

## Installing the Operating System Disc

To load the logic analyzer's operating system, you must install the disk as shown below before you turn on the power. When the disk snaps into place, the disk eject button will pop out. Now you can turn on the logic analyzer.

The logic analyzer runs a series of self-tests and loads the operating system before it is ready to be operated.

What Is the HP 1650B/HP 1651B? 1-8

HP **1650B/HP** 16618 Getting Started Guide

#### Line Switch

The line switch is on the rear panel. You turn on the logic analyzer by pressing the 1 on the rocker switch. Make sure the operating system disk is in the disk drive before you turn it on. If you forget the disk, don't worry, you won't harm anything. You will merely have to repeat the turn-on procedure with the disk in the drive.

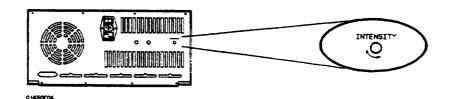

#### **Intensity** Control

Once **you have** turned on the instrument, you **may want** to set **the** display intensity to a different level that's more comfortable for you. You do **this** by turning the **INTENSITY control** on the rear **panel**.

#### Power-up Self-Test

When you turn on the logic analyzer, it performs a series of self-tests. When it has successfully completed these tests, it loads the operating system into memory from the disk

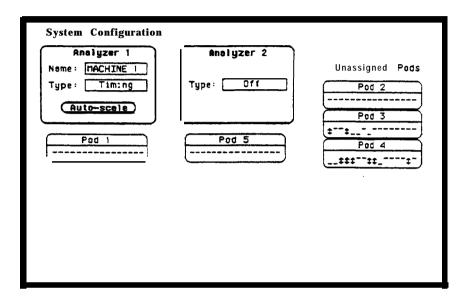

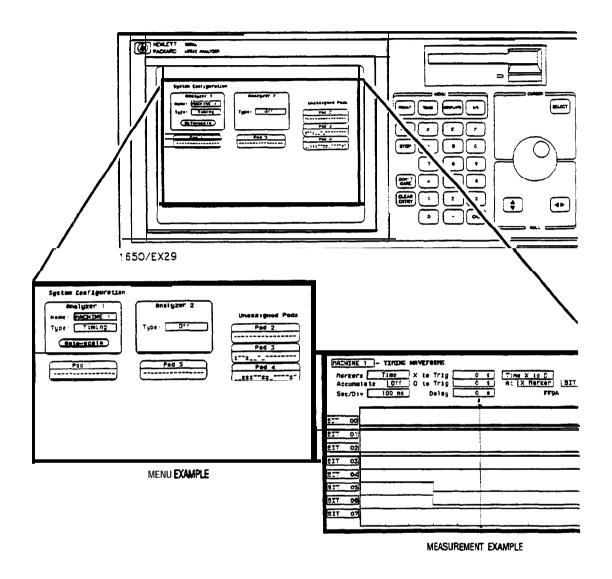

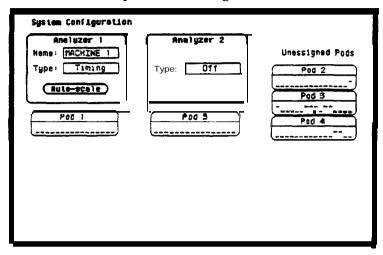

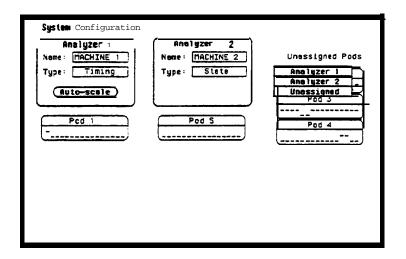

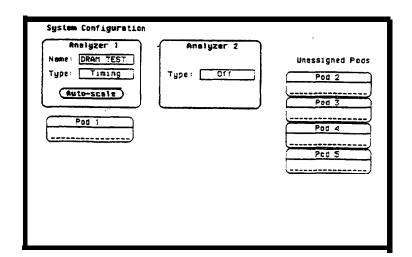

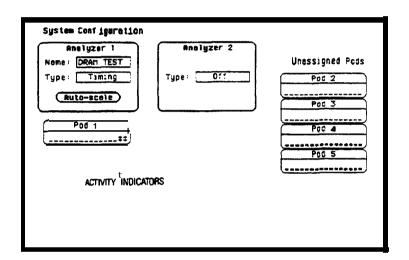

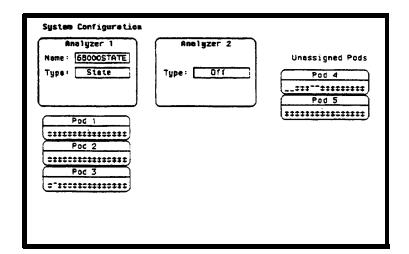

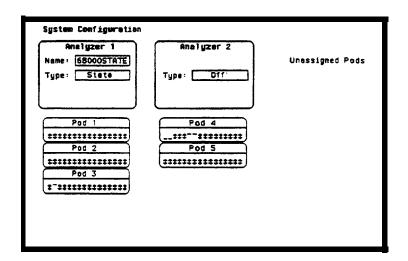

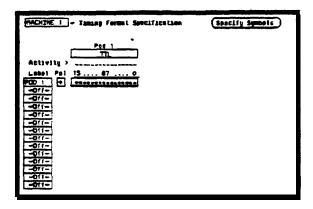

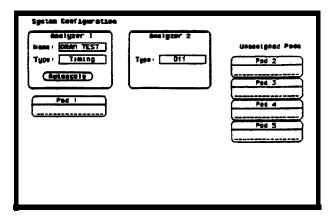

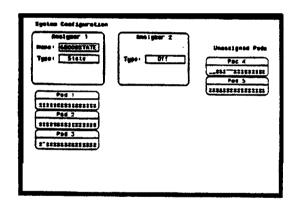

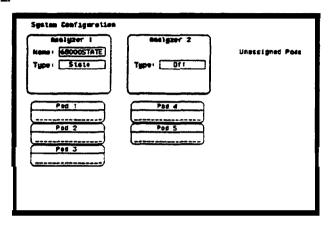

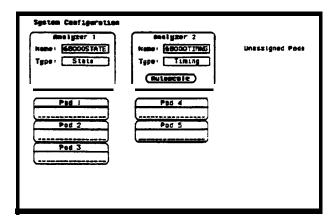

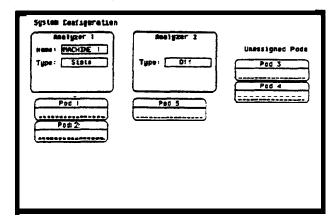

When the logic analyzer has completely loaded the operating system it displays the System Configuration menu as shown below.

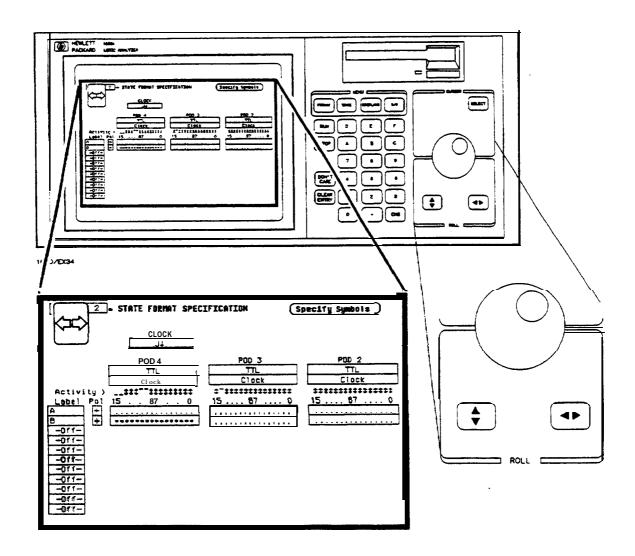

This is the HP 1650B System Format Specification menu. If you have an HP 1651B, the only difference is pod 1 will be assigned to analyzer 1 and pod 2 will be assigned to analyzer 2. There won't be any pods in the UNASSIGNED area of the display.

#### Summary

Now that you have unpacked, inspected, and begun operating the logic analyzer, the next step will depend on your needs. If you are a first-time logic analyzer user who wanted to get the instrument running before reading Feeling Comfortable with Logic Analyzers you should read it now. If you are familiar with logic analysis, read either the rest of this Getting Started Guide or the HP 1650B/HP 1651B Front-Panel Reference Manual.

In a task format this Getting Started Guide teaches you the basics of how to operate the front panel and configure it for basic measurements.

The HP 1650B/HP 1651B Front-Panel Reference manual describes all the front-panel and programming functions of the logic analyzers. The HP 1650B/HP 1651B Programming Reference manual describes the programming commands and conventions for the logic analyzers. Once you feel comfortable with the basic operation of the front panel, use this book.

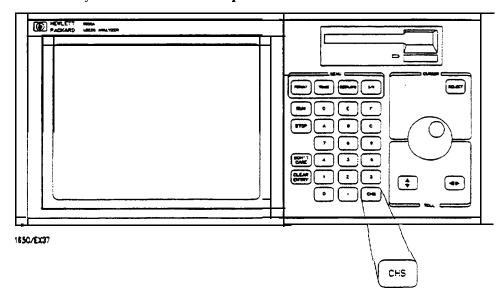

#### **Getting to Know the Front Panel**

#### Introduction

The HP 1650B/51B logic analyzers have been designed to be very easy to use. The controls are located logically by function so you can learn how to use them quickly and easily.

This chapter breaks down the front panel into these functional areas and gives you an overview of each area.

## Front Panel Organization

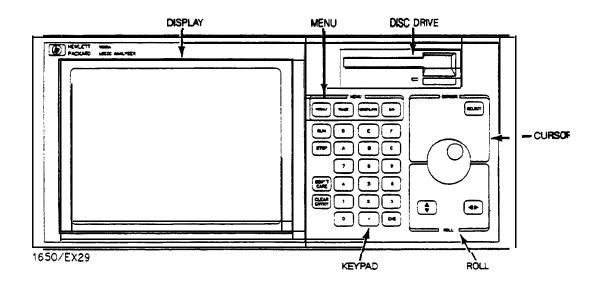

The functional areas of the front panel are: display, MENU, keypad, CURSOR, ROLL and disk drive.

#### Cursor

The CURSOR is a movable indicator on the display that allows you to access desired fields in **each menn**. It changes the field where it resides from the normal white **background** to the dark **background** (inverse video). The KNOB moves the cursor to the field (function) you wish to use. You **activate** the field (function) by pressing the SELECT key.

MENU EXAMPLE

Getting to Know the Front Panel 2-2

HP 1650B/HP 1651B Getting Started Guide

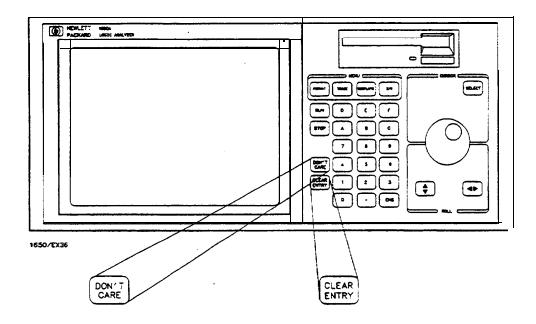

Keypad The keypad allows you to start and stop data acquisition as well as enter alphanumeric data Also in the keypad area are the DON'T CARE and CLEAR ENTRY keys.

When pact of the data display is off screen, the ROLL keys define which way the KNOB will move the displayed data. You will use these keys and the KNOB to roll displayed data up/down or left/right to view data that is off screen.

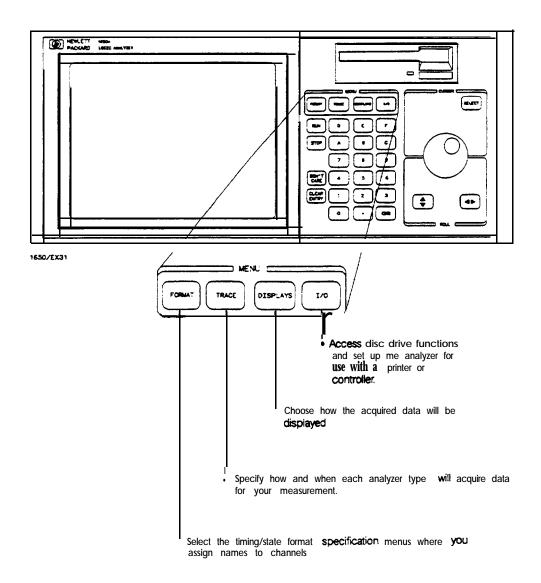

### Menu The MENU area contains keys that give you access to the four major menus of the logic analyzer. You use this area to:

HP 1650B/HP 1651B Getting Started Guide Getting to Know the Front Panel

Display The display shows you the menus for configuring the logic analyzer and the results of your measurements.

Getting to Know the Front Panel 2-6

HP 1650B/HP 1651B Getting Started Guide

#### **Disk Drive**

The logic analyzer uses the disk drive every time you turn on the logic analyzer to load its operating system. The disk drive uses 3.5-inch flexible disks. You can also use the disk drive to store instrument configurations, acquired data, and inverse assemblers for later use. Complete details on the disk drive and its functions can be found in the Ii?' 1650B/HP 1651B Front-Panel Reference manual.

#### **Summary**

Now that you are acquainted with the front panel organization, you will be able to decide where you want to go **next**. If you are just **starting** to learn logic analysis, you should read this entire manual. If you are **experienced in** logic **analysis**, you should **continue** to read **chapters** 3 and 4 to become more **familiar with** the operation of **the front panel** before you **turn** to the reference **manual**. **These** chapters will show you how easy the HP **1650B/51B** logic **analyzers** are **to** operate.

#### How Do I Use the Front Panel?

#### Introduction

In this chapter you will learn how easy the HP 1650B/51B logic analyzer front panel controls are to use. You will also learn the front panel by following self-paced exercises.

This chapter starts you off in the System Configuration menu, the same place the logic analyzer starts after you turn it on. You will learn how easy it is to get in and out of this menu. You will also learn what the shapes of the menu fields mean

Don't be concerned about not seeing measurement examples in this chapter. You will see them in chapters 5 through 8.

#### Menu Field Convent ions

Before starting to work with the menus, you need to know the two menu field conventions. This allows you to quickly recognize what type of action will occur when you select a field.

There are two shapes that you should become familiar with: rectangles with square comers and rectangles with rounded corners.

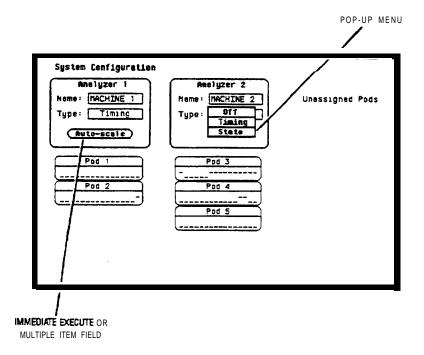

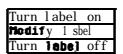

When you select a field with square comers, it pops up and lists two or more items. You must select a single item.

Fields with rounded comers will either execute the function immediately or pop up with a list of multiple items that you must specify.

#### **Your First Step**

When you turn on the logic analyzer and the operating system has finished loading, you will see the System Configuration menu. Notice the cursor is in one of the fields in this menu. Operating the HP 1650B/51B front panel is like leaning to drive a car.

To "drive" around the menu, turn the KNOB and watch the cursor move from field to field. Most of the logic analyzer operation is accomplished by placing the cursor on the field you want to interact with and pressing the **SELECT** key. Depending on the field type (immediate execute or pop-up) pressing SELECT will either execute a function or open a pop-up menu.

This is the ZIP 1650B System Format Specification menu If you have an HP 1651B, the only difference is pod 1 will be assigned to analyzer 1 and pod 2 will be assigned to analyzer 2. There won't be any pods in the UNASSIGNED area of the display.

#### Returning to the System Configuration Menu

When you leave the System Configuration menu, you can return to it at anytime by following these steps

- 1. Press either the FORMAT, TRACE, or DISPLAY key. You now see a new menu. All three of these menus have a field in the upper left comer. This field will display either MACHINE 1 or MACHINE 2 depending on how the logic analyzer was configured.

- 2. Place the cursor on this field and press SELECT. You will see the following pop-up menu.

- 3. Place the cursor on System and press **SELECT.** You will be returned to the System **Configuration** menu

# Exploring the System Configuration Menu

Now is a good time to explore the System Configuration mean by driving the cursor around and pressing SELECT. Don't worry, you can't hurt anything because no matter what field you select you will have an easy way out.

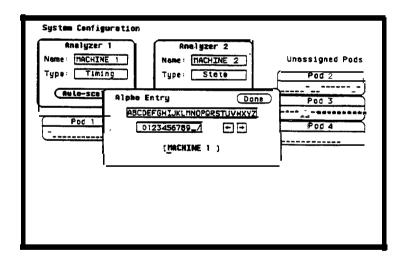

For example, select the Name: MACHINE 1 field, and you will see a pop-up that you can use to name analyzer number 1. In this pop-up menu you will see a field named Done that lets you get out of this menu and back to the System Configuration menu where you started.

If you select Auto-scale, the logic analyzer will display a pop-up with the choices of Cancel and Continue. The Cancel allows you to change your mind before the auto-scale is executed. This is handy because auto-scale will change your previous configurations.

If you select **Continue**, the logic analyzer will display the **TIMING** WAVEFORMS menu However, if there is no signal activity at the probes, the Waveforms menu will not display data and the label to the left of the waveform area will be **-off-**.

To get back to the System Configuration menu after executing Auto-scale:

- L Place the cursor on the field in the upper left corner and press SELECT.

- 2 Place the cursor on System in the pop-up and press SELECT. You will now be back in the System Configuration menu.

## Closing Pop-up Menus

In previous exercises, you closed the Alpha Entry pop-up by using the Done field. But, what if there is no Done in the other fields? Fields that don't have choices like Done, Cancel, or Exit will close automatically when you make your selection. For example, you have used this type of pop-up to get back to the System Configuration menu.

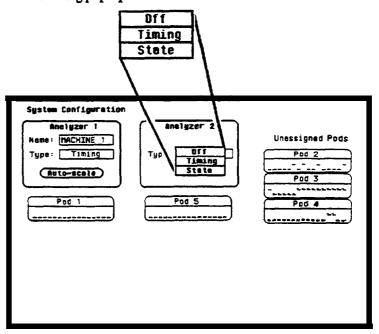

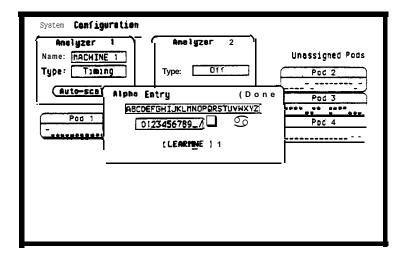

To see another example of a pop-up that automatically doses, follow these steps:

L Rotate the KNOB until the cursor is on the Off field in the ANALYZER 2 field, then press SELECT. You will now see the following pop-up:

2. Place the cursor on State and press Select.

The pop-up menu will automatically dose, analyzer 2 is now on and the type will be State.

#### **Summary**

In this chapter you learned what menu the logic analyzer displays once you have turned it on and where you will usually start configuring the logic analyzer once you are ready to make measurements.

The next chapter will teach you the most common types of pop-up menus, which will help you progress towards making measurements as explained in chapters 5 &rough 7.

#### Learning the Basic Menus

#### Introduction

in this chapter you will learn the most common pop-up menu types by doing some basic exercises. The pop-up menu types you will learn in this chapter are:

- Selector

- Alpha Entry

- Numeric Entry

- Assignment/Specification

#### Selector Pop-up Menu

In the selector type of pop-up **menu** you do what the name implies, make a **selection** from **two** or more **options**. The best way to **introduce** you to a **selector** type of menu is to **have** you work **with** one right away.

## Switching Between Analyzers

You will use a selector type of **pop-up** menu to switch between analyzers or get back to the System **Configuration** menu- You can switch analyzers in the FORMAT, TRACE and DISPLAY menus, without having to go back to the System Configuration menu. This is done easily by following these steps:

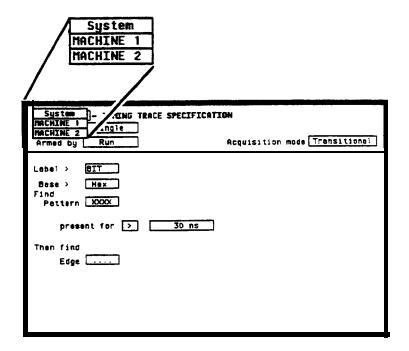

1. Press the TRACE key. You will now be **in** either the TIMING **TRACE** or **STATE** TRACE **SPECIFICATION** menu depending on **what** you did last in the System **Configuration** menu.

2. Place the cursor in the field in the upper left comer of the menu and press SELECT. A pop-up menu will appear displaying System and the current analyzer names (default names are MACHINE 1 and MACHINE 2). The cursor will be on the current analyzer.

3. Move the cursor to the other machine (analyzer) and press **SELECT.** The pop-up will close and you will see the corresponding menu of the other analyzer on the display.

Assigning Pods Another selector menu type you will use is assigning pods to the analyzers. To assign pods:

- L Get back to the System Configuration menu (refer to "Returning to the System Configuration Menu" in chapter 3 if you need a reminder).

- 2 Place the cursor on one of the pod fields on the right side of the display and press **SELECT.** You will see the following menu:

3. Place the cursor on Analyzer 2 and press **SELECT.** The pop-up closes and your desired pod is now assigned to analyzer 2

#### Alpha Entry Pop-up Menu

You can give specific names to several things. These names can represent your measurement specifically.

The two major examples of items that can be named are:

- Bothana@crs

- 858111●

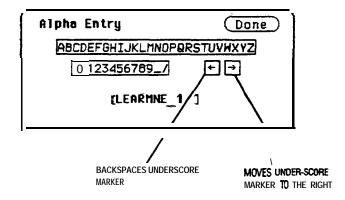

To learn how this type of pop-up works, you'll name analyzer 1 LEARN. However, LEARN will be misspelled when you finish entering it. Don't worry, this is intentional. You will then be shown how to correct it.

- L Get back to the System Configuration menu refer to "Returning to the System Configuration Menu" in chapter 3 if you need a reminder).

- 2. Rotate the KNOB until the cursor is over MACHINE 1 and press SELECT.

You will now see a pop-up window in the System Configuration menu **25** shown in the example.

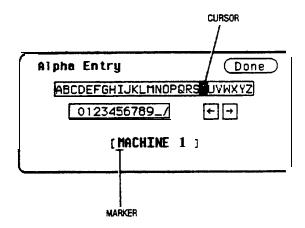

3. Rotate the KNOB and you will see how the cursor moves within the pop-up.

4. Now that you are ready to name analyzer 1, move the cursor so that it is on the L and press SELECT.

In the bottom of the pop-up, you will see an L in the far left comer of the bottom box Also notice the under-score marker in the bottom box is now under the A of MACHINE. The under-score marker tells you in what space in the box your next selection will be placed.

5. Rotate the KNOB again until you have placed the cursor over the E, then press SELECT.

You can also make direct keypad entries. Your selection will be placed where the under-score marker is in the box.

6. Repeat step 5 three more times selecting A, R, and M respectively.

You should now see LEARMNE 1 in the bottom box. Since this is not the name you wanted, change the name.

### Changing Alpha **Entries**

**To** make changes or **corrections** in the Alpha Entry field, place the under-score marker **under** the character you want to change.

To move the under-score marker to the left, place the cursor over the left arrow and press SELECT once for each backspace.

To move the under-score marker to the right, you either place the cursor on a desired character and press SELECT, or place it on the right arrow and press SELECT:

You **can** also use the ROLL **Keys** and the KNOB to move the underscore marker. To use **this alternate method**:

- 1. Press the left/right ROLL key.

- 2. Rotate the KNOB to place the under-score marker **under** the desired character.

- 3. Press the left/right ROLL keyagain to turn off the ROLL function

HP 1650B/HP 1651B Getting Started Guide Learning the Basic Menus

4-7

If you want to crase the entire entry and place the under-score marker at the beginning of the name box, press the CLEAR ENTRY key on the front panel.

If you want to replace a **character** with a space, place the underscore marker under that character and press the **DON'T** CARE key on the front panel.

Now that you have entered and edited a name, you will know how to use the Alpha Entry pop-up menu in other logic analyzer menus where it appears.

### Numeric Entry Menus

There are many pop-up menus in which you enter numeric data. The two major types are:

- \$♦OMOHN M■♦OO •H♦# AHEMA ◆■H♦• (i.e. ❖□•♦•®

- Numeric entry with variable tits (i.e. ms,  $\mu$  s, etc.)

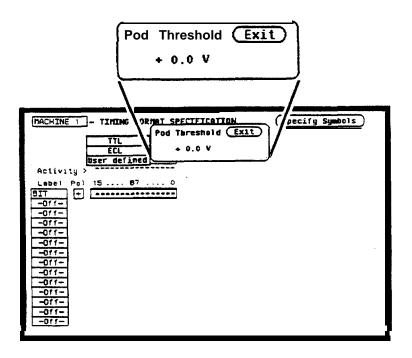

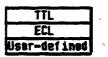

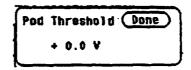

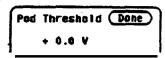

There are several numeric **entry** menus **in** which you only enter the value, and the **units** are fixed. One such type of numeric entry pop-up is the POD **Threshold pop-up menu**.

Besides being able **to** set the pod **thresholds** to either of the **preset** thresholds **(TTL** or ECL), you **can set** the thresholds to a specific **voltage** from -9.9 V to +9.9 V.

To set pod **thresholds** to a specific voltage, follow these steps:

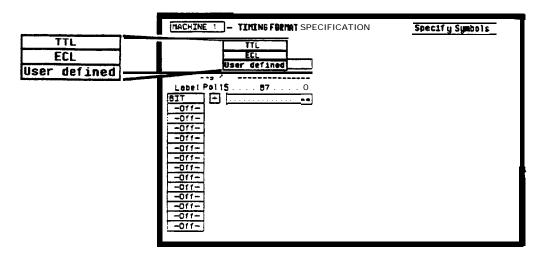

- 1. Select either the **TIMING** or STATE FORMAT SPECIFICATION **menu** by **pressing the FORMAT** key. It doesn't matter whether you are **in** the **TIMING** or STATE FORMAT **SPECIFICATION** menu.

- 2 Rotate the KNOB to place the cursor **in** the TTL field of any pod displayed and press SELECT. You**will** now see a **pop-up** with the choices, **TTL,ECL**, and User defined.

HP 1650B/HP 1651 B Getting Started Guide

Learning the Basic Menus

3. Place the cursor on User**Defined** and press SELECT. Another pop-up menu will appear as shown.

You can enter your desired threshold with either of two methods when the pod threshold **pop-up** is **open**. The first method is to rotate the KNOB until your desired threshold is displayed-Rotating the KNOB increments or decrements the value in small **increments**.

The **second** method is to use the keypad, which allows you to change large values quickly. With the keypad follow these simple steps to enter  $-5.0 \, V$  for the pod threshold:

4. Enter 5.0 from the keypad. You will see the 0.0 V replaced with 5.0.

**Learning** the **Basic Menus 4-10**

HP 1650B/HP 1651B Getting Started Guide 5. Press the **CHS** (change sign) key on the front **panel**. You will now see -5.0 in the **pop-up**.

Also notice the cursor is **in** the upper right **corner** of the pop-up over the operative Exit. When you press **SELECT,** the pop-up will close and your new threshold will be **placed** in the Pod field.

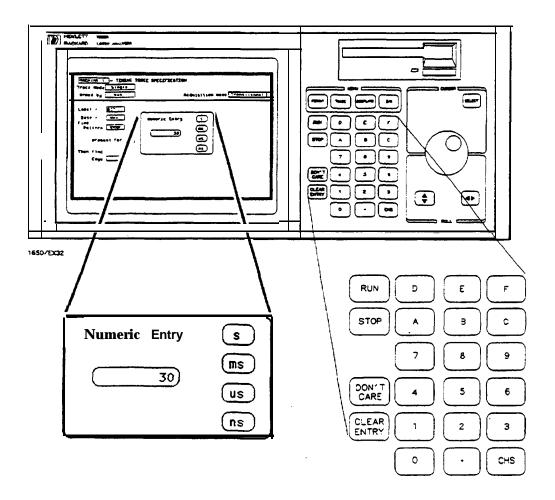

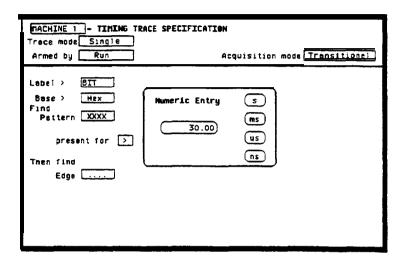

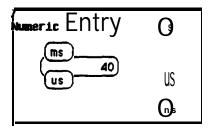

Another type of numeric **entry** you **will** use **requires** you to **specify** the units as well as the numeric value. The following steps show you how

1. Select the TIMING **TRACE** SPECIFICATION menu by pressing the **TRACE key**.

If **the** STATE TRACE SPECIFICATION menu comes up, refer to "Switching **Between** Analyzers" in thii chapter.

2. Rotate the KNOB to place the cursor in the 30 ns box within the present for> 30 ns line and press SELECT. You will now see the following pop-up:

3. Enter a new value to replace 30.00 with the keypad. When you have entered your desired value, you can change the units type by rotating the KNOB.

Once you have selected the new value and the units, close the **pop-up** by pressing **SELECT. The new** value and the units will now **be** displayed in the **present for >** \_\_\_\_\_ field.

### Assignment/ Specification Menus

There are a number of pop-up menus in which you assign or specify what you want the logic analyzer to do. The basic menus of this type consist of:

- Assigning bits to pods

- Specifying patterns

- Specifying edges

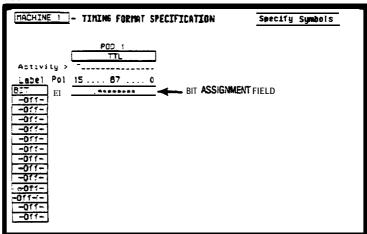

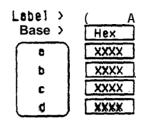

### Assigning **Bits** to **Pods**

The bit assignment fields in both state and timing analyzers work identically. Before starting this exercise you need to know how the logic analyzer knows which bits are assigned and which ones are not assigned. The convention for bit assignment is:

- \*(asterisk) indicates assigned bii . (period) indicates un-assigned bits.

- In the following menu example, bits 0 through 7 are assigned to the label BIT.

- o assign bits:

- 1. Select either the TIMING or STATE FORMAT SPECIFICATION menu

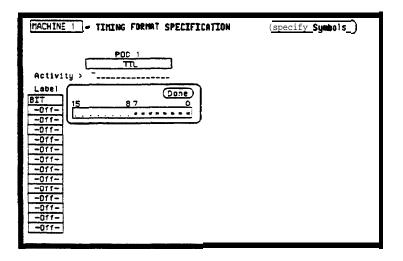

2.Place the cursor on one of the bit assignment fields and press **SELECT.** You will see the following **pop-up menu**.

If you don't see any bit **assignment** fields, it merely means you don't have any pods assigned to this **analyzer**. Either switch analyzers or assign a pod to the analyzer you are working with.

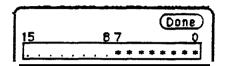

**3.Rotate** the KNOB to **place the** cursor on one of the asterisks or. **periods** in the pop-up and press SELECT. You will notice how the bit assignment toggles to the opposite state of what it was when the pop-up opened.

**4. You** close the pop-up by placing the cursor on Done and pressing SELECT.

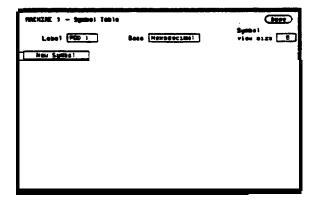

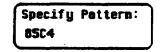

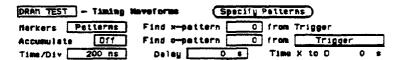

## Specifying Patterns

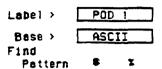

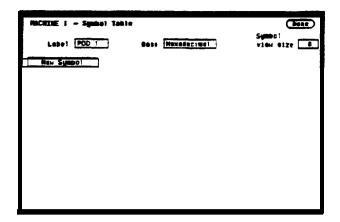

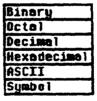

The Specify **Patterns** fields appear in several menus in both the timing and state analyzers Patterns can be **specified** in one of **several** number **bases**; however, for now we'll use hexadecimal (HEX) since it is the **default** base.

Before starting this exercise you need to know how the logic **analyzer knows** which pattern to ignore (doesn't care about). Whenever you see an "X" in this type of menu, it indicates a "don't **care.**"

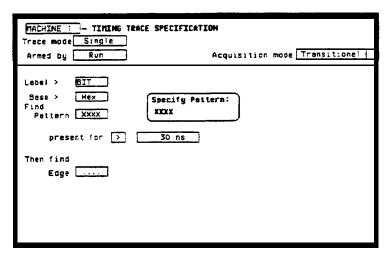

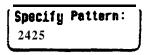

To specify patterns:

- 1. Select the TIMING TRACE SPECIFICATION menu

- 2 Place the cursor on the Find Pattern field and press SELECT. You will see the following pop-up menu.

- 3. Type in **2**, **3**, **4**, and press the DON'T CARE key. You will see 234X in the pop-up. This will be the pattern in **hexidecimal** that you wantthe logic analyzer to **recognize**.

- 4. Close the pop-up by pressing **SELECT.**

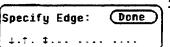

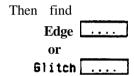

## Specifying Edges

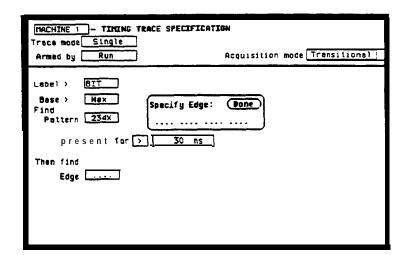

You **specify** edges in **the TIMING TRACE** SPECIFICATION menu by following **these** steps:

- **1.Press** the TRACE key. Switch to the timing **analyzer** if the STATE TRACE **SPECIFICATION** menu is displayed.

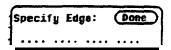

- 2. Place the cursor on the Then find Edge.. field under one of the labels and press SELECT. The following pop-up will appear.

You will notice 16 periods in the pop-up menu Each period represents an unassigned bit for each bit assigned to the label. Don't be alarmed if you have a different number of unassigned bits; it merely means the number of bits in your label is different than the label in this example.

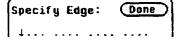

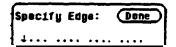

**3.Place** the cursor on one of **the** unassigned bit periods and press **SELECT** once. You will now see **an** arrow pointing down.

| Specify | Edge: | Done |

|---------|-------|------|

| 1.1     |       | J    |

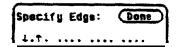

4. Move the cursor to another unassigned bit period and press SELECT twice. You will see an arrow pointing up.

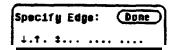

5. Move the cursor to yet another unassigned bit period and press SELECT three times. You will see an arrow pointing both up and down.

You have just selected a positive-going ( $\uparrow$ ), negative-going ( $\downarrow$ ), and either edge ( $\uparrow$ ) for your edge parameter.

6. Place the cursor on Done and press SELECT. The pop-up will close and you will see the following display.

When you close the pop-up after specifying edges, you will see dollar signs (\$\$..) in the Then find Edge field if the logic analyzer can't display the edges correctly. This indicates the logic analyzer can't display the data correctly in the number base you have selected.

HP 1650B/HP 16518 Getting Started Guide Learning the Basic Menus

4-17

### **Summary**

In this chapter you have learned some of the most common pop-up menu types. You will use these pop-up menus as you set up the logic analyzer in the measurement example exercises in chapters 5 through 7.

If you are already familiar with logic analysis and feel you are comfortable enough with the HP 1650B/51B user interface, you may be ready for the HP 1650B/51B Front-Panel Reference.

If you are not familiar with logic analyzers or logic analysis, you should continue with this manual.

### **Using the Timing Analyzer**

#### Introduction

In this chapter you will learn how to use the timing analyzer by setting up the logic analyzer to make a simple measurement. We give you the measurement results as actually measured by the logic analyzer, since you may not have the same circuit available.

The exercise in this chapter is organized in a task format. The tasks are ordered in the same way you will most likely use them once you become an experienced user. The steps in this format are both numbered and lettered. The numbered steps state the step objective. The lettered steps explain how to accomplish each step objective. There is also au example of each menu after it has been properly set up.

How you use the steps depends on how much you remember from chapters 1 through 4. If you can set up each menu by just looking at the menu picture, go ahead and do so. If you need a reminder of what steps you need to perform follow the numbered steps. If you still need more information about "how," use the lettered steps.

When you have finished configuring the logic analyzer for this exercise, you can load a file from the operating system disk. This file configures the logic analyzer the same way it is configured for this exercise. It also loads the same data acquired for this exercise so you can see what it looks like on screen.

In order to learn how to configure the logic analyzer, we recommend that you follow the exercise to "Acquiring the Data" before loading the file from the disk.

You can also compare your configuration with the one on the dish by printing it (if you have a printer) or malting notes before you load the tile.

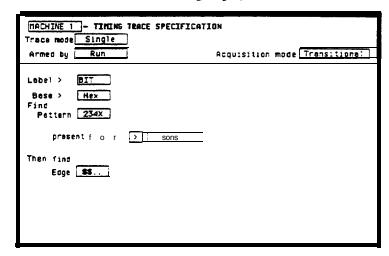

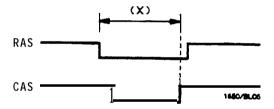

# Problem Solvingwith the Timing Analyzer

In this exercise, assume you are designing a dynamic RAM memory (DRAM) controller and you must verify the timing of the row address strobe (RAS) and the column address strobe (CAS). You are using a 4116 dynamic RAM and the data book specifies that the minimum time from when LRAS is asserted (goes low) to when LCAS is no longer asserted (goes high) is 250 ns. You could use an oscilloscope but you have au HP 1650B/51B on your bench Since the timing analyzer will do just fine when you don't need voltage parametrics, you decide to go ahead and use the logic analyzer.

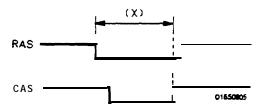

## What Am I Going to Measure?

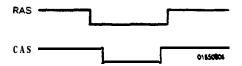

After configuring the logic analyzer and hooking it up to your circuit under test, you will be measuring the time (x) from when the RAS goes low to when the CAS goes high, as shown below.

## How Do I Configure the Logic Analyzer?

In order to make this timing measurement, you must configure the logic analyzer as a timing **analyzer**. By following these steps you **will configure Analyzer 1** as the timing analyzer.

If you are **in** the System **Configuration** menu you are in the right place to get started and **you** can start with step 2; otherwise, start with step 1.

- 1. Using the field in the upper left **corner** of the display, get the system **Configuration** menu on screen

- a. Place the cursor on the field in the upper left comer of the display and **press** SELECT.

- b. Place the cursor on **System** and press SELECT.

- 2. **In** the System **Configuration** menu, change Analyzer 1 type to Timing. **If analyzer** 1 is already a timing analyzer, go on to step 3.

- a Place the cursor on the **Type:** \_\_\_\_\_\_**field** and press SELECT.

- b. Place the cursor on Timing and press **SELECT.**

- 3. Name Analyzer 1 "DRAM TEST (optional)

- a. Place the cursor on the Name: <u>field</u> of Analyzer 1 and press **SELECT**.

- b. With the Alpha Entry pop-up, change the name to "DRAM TEST" (see "Alpha Entry Pop-up Menu" in chapter 4 if you need a reminder).

- 4. Assign pod 1 to the timing analyzer.

- a. Place the cursor on the Pod 1 held and press SELECT.

- b. In the Pod 1 pop-up, place the cursor on Analyzer 1 and press SELECT.

## Connecting the **Probes**

At this point, if you had **a target system with** a 4116 DRAM memory **IC**, you would connect the logic analyzer to your system.

Since you will be assigning Pod 1 bit 0 to the RAS label, you connect Pod 1 bit 0 to the memory IC pin connected to the RAS signal. You connect Pod 1 bit 1 to the IC pin connected to the CAS signal.

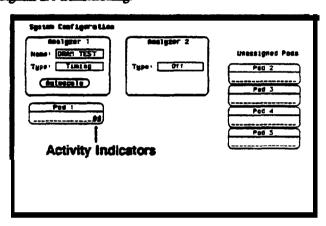

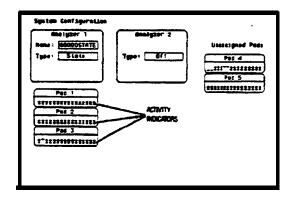

### **Activity Indicators**

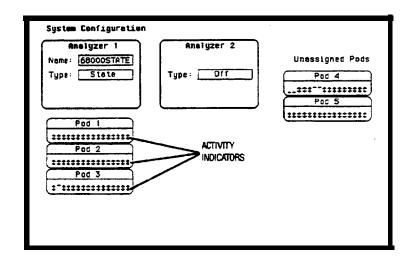

When the logic analyzer is connected and your target system is running, you will see ; at the right-most end (least significant bits) of the Pod 1 field in the System Configuration menu. This indicates the RAS and CAS signals are transitioning.

## **Configuring the Timing Analyzer**

Now that you have **configured** the system, you are ready **to configure** the timing analyzer. You will be:

- Creating two names (labels) for the input signals

- Assigning the channels connected to the input signals

- Specifying a trigger condition

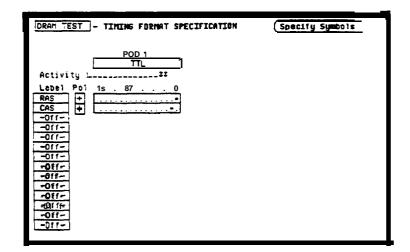

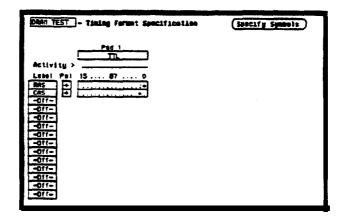

- **1.Display the** TIMING FORMAT SPECIFICATION menu.

- **a.** Press the FORMAT key on the front panel

- 2.Name two labels, one RAS and one CAS.

- a. Place the cursor on the top **field** in the label column and press **SELECT.**

- b. Place the cursor on Modify label and press **SELECT.**

- c. With the Alpha Entry pop-up, change the name of the label to **RAS** (see "Alpha Entry Pop-up Menu" in chapter 4 if you need a reminder).

- **d.** Name the second label **CAS** by repeating steps a through c.

- 3. Assign the channels **connected** to the input signals (Pod 1 bii 0 and 1) to the labels RAS and CAS respectively.

- a. Place the cursor on the bit assignment field below Pod 1 and to **the** right of **RAS and** press SELECT.

- b. Any **combination** of bits may be **assigned** to this **pod**; however, you will want only bit 0 assigned to the RAS **label**. The easiest way to assign bits is to press the CLEAR ENTRY key to un-assign any **assigned** bits before you **start**.

- c. Place the **cursor** on the period under the 0 in the bit assignment **pop-up** and press SELECT. This **will** place an **asterisk** in the pop-up for bit 0 indicating Pod 1 bit 0 is now assigned to the **RAS label**. Place cursor on Done and press **SELECT** to close the **pop-up**.

- d. Assign Pod 1 bit 1 to the CAS label by moving the cursor to bit 1 and pressing SELECT.

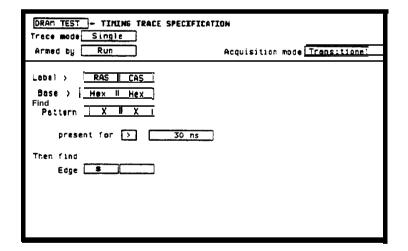

### Specifying a Trigger Condition

To capture the data **and** then place the data of interest in the center of **the** display of the TIMING WAVEFORMS menu, you need to **tell** the logic **analyzer** when to trigger. Since the first event of interest is when the **LRAS** is asserted (negative-going edge of RAS), you need to tell the logic **analyzer** to trigger on a negative-going edge of the RAS signal.

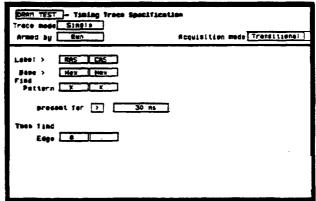

- **1. Select** the TIMING TRACE menu by pressing the TRACE key.

- 2. Set the trigger so that the logic analyzer triggers on the negative-going edge of the **RAS**.

- a. **Place** the cursor on the **Then find** Edge field under the **label** RAS, then press **SELECT.**

- b. Place the cursor on the. (period) in the pop-up **and** press SELECT once. **Pressing SELECT** onceinthispop-up **changes** a period to **which** indicates a negative-going edge.

- c. Place the cursor on Done and press SELECT. The pop-up closes and a \$ will be located in this field. The \$ indicated an edge has been specified even though it can't be shown in the HEX base.

## Acquiring the Data

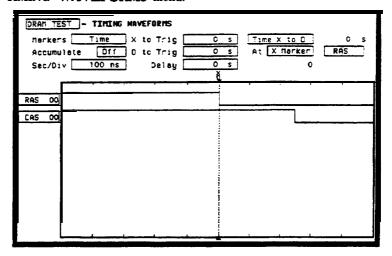

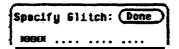

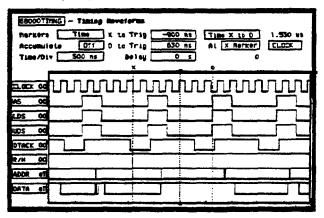

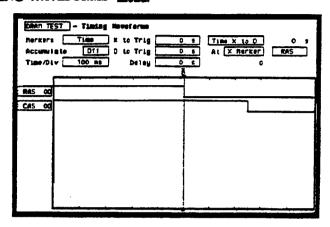

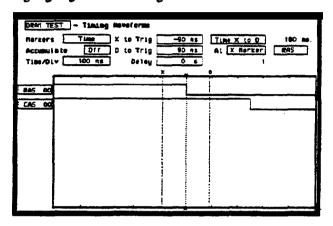

Now that you have configured and connected the logic analyzer, you acquire the data for your measurement by pressing the RUN key. The logic analyzer will look for a negative edge on the RAS signal and trigger if it sees one. When it triggers, the display switches to the TIMING WAVEFORMS menu.

The RAS label shows you the RAS signal and the CAS label shows you the CAS signal Notice the RAS signal goes low at or near the center of the waveform display area (horizontal center).

Now is the time to load the timing measurement demo file from the disk if you wish The file name is TIMINGDEMO. Follow the procedure in Appendix B to load the file.

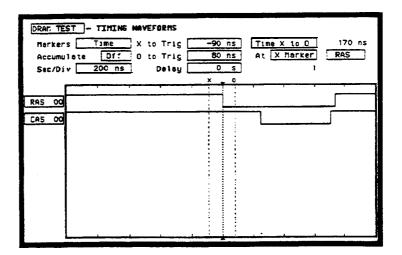

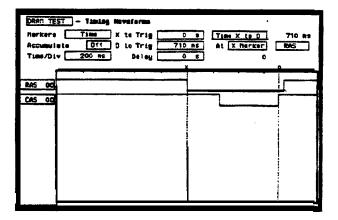

## The **Timing** Waveforms Menu

The **TIMING** WAVEFORMS menu differs from the other menus you have **used** so far in this exercise. Besides displaying the acquired data, it has menu **fields** that you use **to** change the way the **acquired** data is displayed and fields that give you timing answers. Before you can use this menu to **find** answers, you need to know some of the special symbols and their functions. The symbols are:

- The X and O

- The ▼

- The vertical dotted line

both 0.000 s (see example below).

The X and 0 The X and 0 are markers you use to find your answer. You place them on the points of interest on your waveforms, and rhe logic **analyzer** displays the time between the markers. The X and 0 markers will be in the center of the display when X to **trig(ger)** and 0 to **trig(ger)** are

The  $\bigvee$  (inverted triangle) indicates the trace point. Remember, trace point = trigger + delay. Since delay in this example is 0.000 s, you will see the negative-going edge of the RAS signal at center screen under the  $\bigvee$ .

### The Vertical Dotted tine

The vertical dotted line indicates the trigger point you specified in the TIMING TRACE SPECIFICATION menu. The vertical dotted line is at center screen under the ▼ and is superimposed on the negative-going edge of the RAS signal as shown.

## Configuring the Display

Now that you have acquired the RAS and CAS waveforms, you need to configure the TIMING WAVEFORMS menu for best resolution and to obtain your answer.

#### Display Resolution

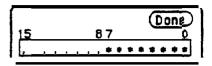

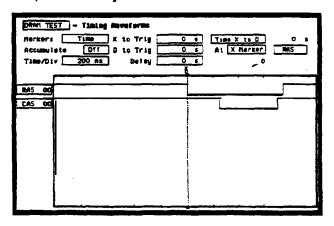

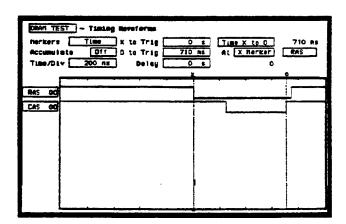

You get the best resolution by changing the Sec/Div to a value that displays one negative-going edge of both the RAS and CAS waveforms. Set the Sec/Div by following these steps.

- 1.Place the cursor on Sec/Div and press SELECT. The Sec/Div pop-up appears, showing you the current setting.

- 2 While the pop-up is present, rotate the KNOB until your waveform shows you only one negative-going edge of the RAS waveform and one positive-going edge of the CAS waveform. (see above). In this example 200 ns is best.

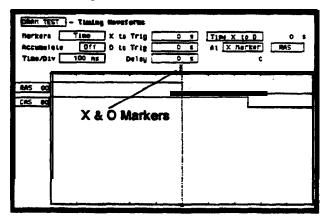

### Making the Measurement

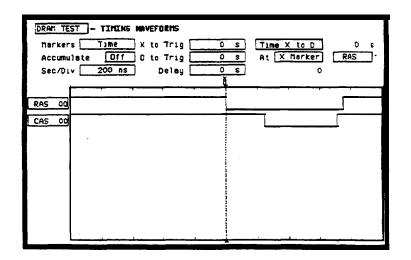

What you want to know is how much time elapses between the time RAS goes low and the time CAS goes high again. You will use the X and 0 markerstoquickly find the answer. Remember, youspecified the negative-going edge of the RAS to be yourtrigger point; therefore, the X marker should be on this edge if X to Trig = 0. If not, follow steps 1 and 2.

- L **Place** the cursor on the X to **Trig field** and press SELECT. A pop-up will appearshowing you the current time from the X marker to the **trigger**; however, you don't need to worry about this number now.

- 2 Rotate the KNOB to place the X marker on the negative-going edge of the RAS waveform and press SELECT. The pop-up closes and displays X to Trig = 0.000 s.

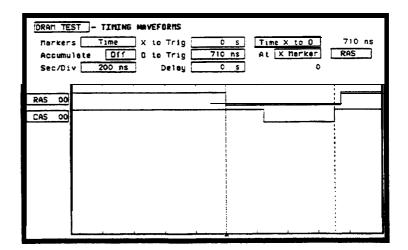

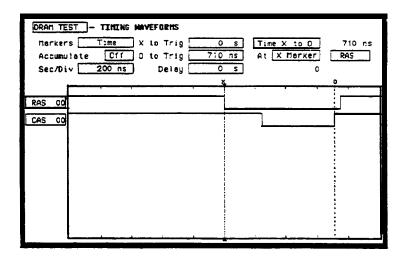

- 3. Place the cursor on 0 to Trig and press SELECT. Repeat step 2 except place the 0 maker on the positive-going edge of the CAS waveform and press **SELECT.** The pop-up closes and displays **O to Trig = 710 ns.**

## Finding the Answer

Your answer could be calculated by adding the X to Trig and O to Trig times, but you don't need to bother. The logic analyzer has already calculated this answer and displays it in the Time X to O \_\_\_\_\_ field.

This example indicated the time is **710 ns. Since the data** book **specifies** a minimum of 250 **ns,** it appears your **DRAM** controller circuit is designed properly.

### Summary

You have just learned how to make a simple timing measurement with the HP **1650B/51B** logic analyzer. You have:

- specified a timing analyzer

- assignedpodl

- assignedbits

- assigned labels

- specified a trigger condition

- learned which probes to **connect**

- · acquired the data

- configured the display

- set the Sec/Div for best resolutions

- positioned the markers for the measurement answer

You have seen how easy it is to use the timing analyzer to make timing measurements that you could have made with a scope. You can use the timing analyzer for any timing measurement that doesn't require voltage **parametrics** or doesn't go beyond the accuracy of the timing analyzer.

The next chapter teaches you how to use the state analyzer. You will go through a simple state measurement **in** the same way you did the **timing** measurement in this **chapter**.

#### Introduction

In this chapter you will learn how to use the state analyzer by setting up the logic analyzer to make a simple state measurement. We give you the measurement results as actually measured by the logic analyzer, since you may not have the same circuit available.

The exercise in this chapter is organized in a task format. The tasks are in the same or&r you will most likely use them once **you** become experienced. The steps in this format are both numbered and lettered The numbered steps state the step **objective.** The lettered steps explain how to accomplish each step objective. There is also an example of each menu after it has been properly set up.

How you use the steps depends on bow much you remember from chapters 1 through 4. If you can set up each menu by just looking at the menu picture, go ahead and do so. If you need a reminder of what steps to perform, follow the numbered steps. If you still need more **information** about "how," use the lettered steps.

When you have finished **configuring** the logic **analyzer** for this exercise, you can load a file from the operating system disk. This file configures the logic analyzer the same way it is configured for this exercise. It also loads the same data acquired for this exercise so you can see what it looks like on screen.

In order to learn how to configure the logic analyzer, we recommend that you follow the exercise to "Acquiring the Data' before loading the file from the disk

You can also compare your configuration with the one on the disk by printing it (if you have a printer) or making notes before you load the file.

# Problem Solving with the State Analyzer

In this example assume you have designed a microprocessor controlled circuit. You have completed the hardware, and the software designer has completed the software and programmed the ROM (read-only memory). When you turn your circuit on for the first lime, your circuit doesn't work properly. You have checked the power supply voltages and the system clock and they are working properly.

Since the circuit has never worked before, you and the software engineer aren't sure if it is a hardware or software problem, You need to do some testing to find a solution

## What Am I Going to Measure?

You decide to start where the microprocessor starts when power is applied. We will descrii a 68000 microprocessor, however, every processor has similar start-up routines.

When you power up a 68000 microprocessor, it is held in reset for a specific length of time before it starts doing anything to stabilize the power supplies. The time the microprocessor is held in reset ensures stable levels (states) on all the devices and buses in your circuit. Wheo this reset period has ended, the 68000 performs a specific routine called "fetching the reset vector."

The **first** thing you check is the time the microprocessor is held in reset. You find the time is correct. The next thing to check is whether the microprocessor fetches the reset vector properly.

The steps of the 68000 reset vector fetch are:

- 1. Set the stack pointer to a location you specify, which is in ROM at address locations 0 and 2.

- 2 Find the first address location in memory where the microprocessor fetches its first instruction. This is also specified by you and stored in ROM at address locations 4 and 6.

What you decide to **find** out is:

- **L What ROM** address does the microprocessor **look** at for the location of the stack pointer, and what is the stack pointer **location stored in ROM?**

- 2 What ROM address does the microprocessor **look** at for the address where **its first instruction** is stored in ROM, and is the **instruction correct?**

- 3. Does the microprocessor then go to the address where its first instruction is stored?

- 4. **Is** the executable **instruction** stored in the first instruction location **correct?**

Your **measurement**, **then**, requires verification of the sequential addresses the **microprocessor** looks at, and of the data in ROM at these addresses. If **the reset vector fetch is correct** (in this example), you will see the following list of numbers in HEX (default base) when your measurement results are displayed

```

+0000 000000 0000

+0001 000002 04FC

+0002 000004 0000

+0003 000006 8048

+0004 008048 3E7C

```

This list of numbers will be explained in detail later in this chapter in "The State Listing."

### How Do I Configure the Logic Analyzer?

In order to make this state measurement, you must configure the logic analyzer as a state analyzer. By following these steps you will configure Analyzer 1 as the state analyzer.

If you are in the System Configuration menu you are in the right place to get started and you can start with step 2; otherwise, start with step 1.

- 1. Using the field in the upper left comer of the display, get the System Configuration menu on screen.

- a Place the cursor on the field in the upper left comer of the display and press SELECT.

- b. Place the cursor on System and press SELECT.

- 2 In the System Configuration menu, change the Analyzer 1 type to State. If Analyzer 1 is already a state analyzer, go on to step 3.

- a. Place the cursor on the Type: \_\_\_\_\_ and press SELECT.

- b. Place the cursor on State and press SELECT.

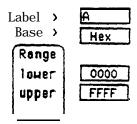

- 3. Name Analyzer 1 68000STATE (optional)

- a. Place the cursor on the Name: \_\_\_\_\_field of Analyzer 1 and press SELECT.

- b. With the Alpha Entry pop-up, change the name to **68000STATE** (see "Alpha Entry Pop-up Menu" in chapter 4 if you need a reminder).

- 4. Assign pods 1, 2, and 3 to the state analyzer.

- a Place the cursor on the Pod 1 field and press SELECT.

- b. In the Pod 1 pop-up, place the cursor on Analyzer 1 and press SELECT.

- c. Repeat steps a and b for pods 2 and 3.

## Connecting the **Probes**

At this point, if you had a target system with a **68000** microprocessor, you would **connect** the logic **analyzer** to your **system**. **Since** you will be **assigning** labels ADDR and DATA, you conned the probes to your **system accordingly**.

- Pod 1 probes 0 through 15 to the data bus lines DO through D15.

- Pod 2 probes 0 through 15 to the address bus lines A0 through A15.

- Pod 3 probes 0 through 7 to the address bus **lines** Al6 through **A23**.

- Pod 1, CLK (J clock) to the address strobe (LAS).

### **Activity Indicators**

When the logic **analyzer** is **connected** and your target **system** is running, you will see 1 in the Pod 1, 2, and 3 fields of the System Configuration menu. This **indicates which signal** lines are **transitioning**.

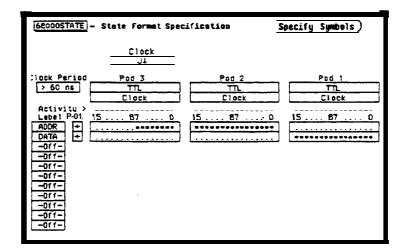

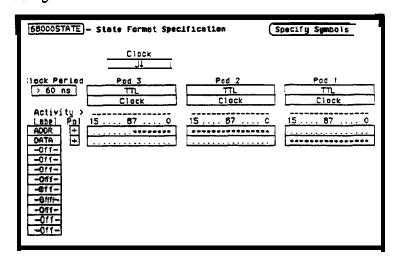

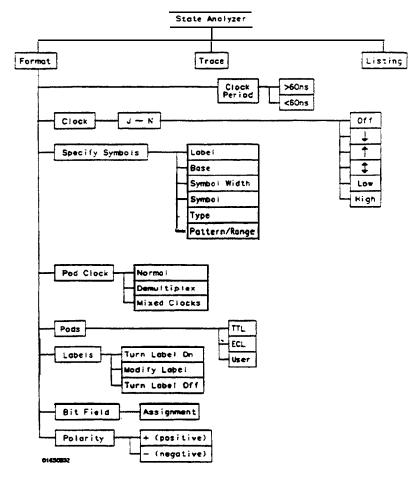

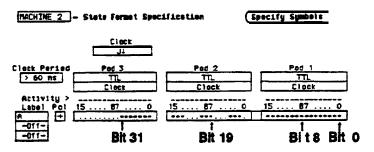

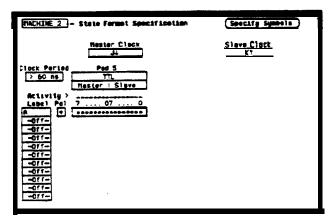

Configuring the Now that you have configured the system, you are ready to configure the State Analyzer. You Will be:

- Creating two names (labels) for the input signals

- Assigning the channels connected to the input signals

- Specifying the State (J) clock

- Specifying a trigger condition

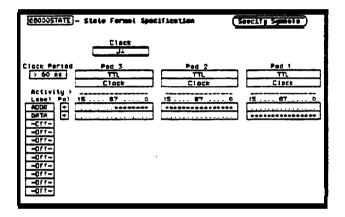

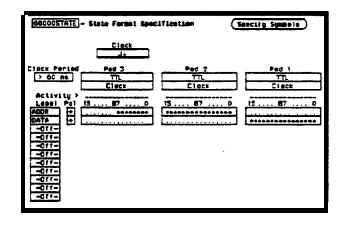

- 1. Display the STATE FORMAT SPECIFICATION menu.

- a. Press the FORMAT key on the front panel.

- 2. Name two labels, one ADDR and one DATA.

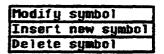

- a. Place the cursor on the top field in the label column and press SELECT.

- b. Place the cursor on **Modify** label and press SELECT.

- c With the Alpha Entry pop-up, change the name of the label to ADDR (see "Alpha Entry Pop-up Menu" in chapter 4 if you need a reminder).

- d. Name the second label-DATA by repeating steps a through c

- 3. Assign Pod 1 bii 0 through 15 to the label DATA

- a. Place the cursor on the bit assignment field below Pod 1 and to the right of DATA and press SELECT.

- b. Any combination of bits may already be assigned to this pod; however, you will want all 16 bits assigned to the DATA label. The easiest way to assign is to press the CLEAR ENTRY key to un-assigned any assigned bits before you start.

- c. Place the cursor on the period under the 15 in the bit assignment pop-up and press SELECT. This will place an asterisk in the pop-up for bii 15, indicating Pod 1 bit 15 is now assigned to the DATA label. Repeat this procedure until all 16 bits have an asterisk under each bit number. Place the cursor on Done and press SELECT to close the pop-up.

- cl. Repeat step c for Pod 2 and the ADDR label to assign all 16 bits.

- e. Repeat step c except you will assign the lower eight bits (0 7) of Pod 3 to the ADDR label.

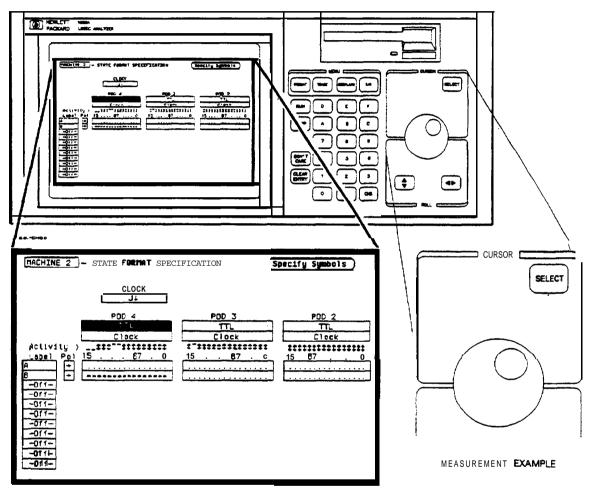

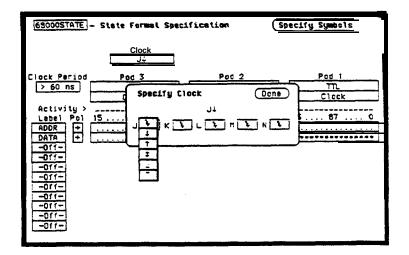

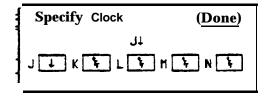

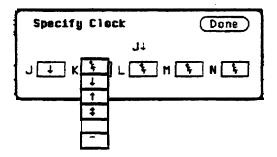

### Specifying the J Clock

If you remember from "What's a State Analyzer" in Feeling Comfortable With Logic Analyzers, the state analyzer samples the data under the control of an external clock, which is "synchronous" with your circuit under test. Therefore, you mast specify which clock probe you will use for your measurement. In this exercise, you will use the J clock, which is accessible through podL

- 1. Select the STATE FORMAT **SPECIFICATION** menu by pressing the FORMAT key.

- 2 Set the J Clock to sample oa a negative-going edge.

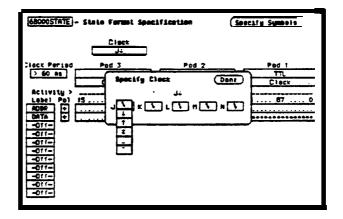

- a. Place the cursor on the CLOCK field and press SELECT.

- b. Place the cursor on the box just to the right of J in the pop-up (labeled OFF) and press SELECT.

- c. Place the cursor on \$\frac{1}{2}\$ and press SELECT.

- d. Place the cursor on **Done** and press **SELECT**.

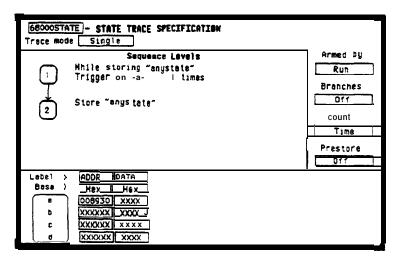

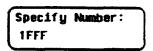

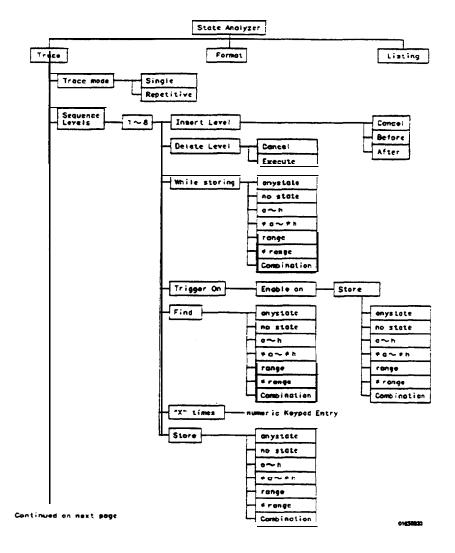

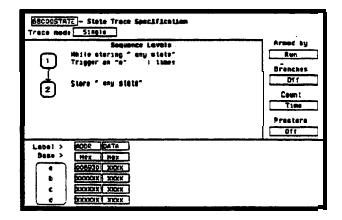

## Specifying a Trigger Condition

To capture the data and place the data of interest in the center of the display of the STATE LISTING menu, you need to tell the state analyzer when to trigger. Since the first event of interest is address 0000, you need to tell the state analyzer to trigger when it detects address 0000 on the address bus.

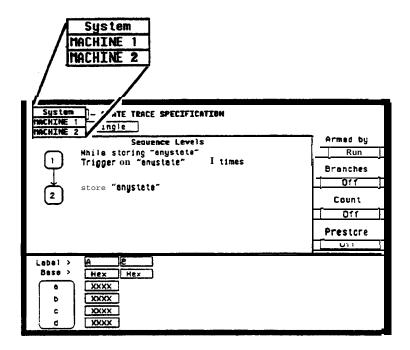

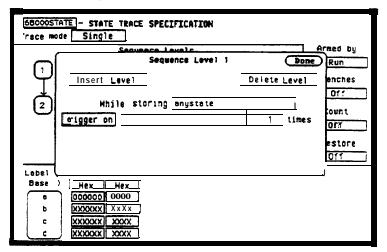

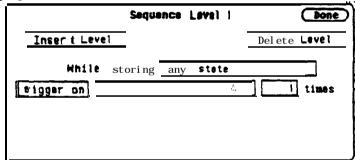

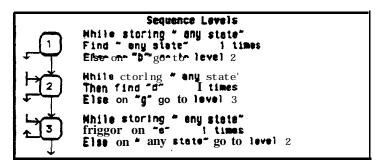

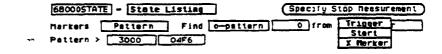

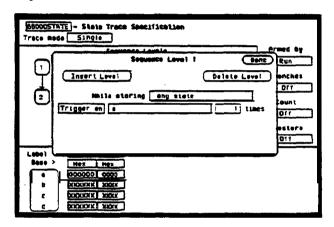

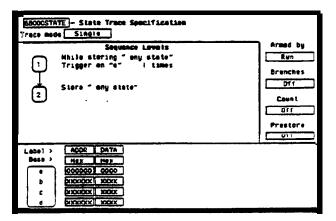

- **1.** Select the STATE **TRACE SPECIFICATION** menu by pressing the TRACE **key**.

- 2. Set the trigger so that the state analyzer triggers on address 0000.

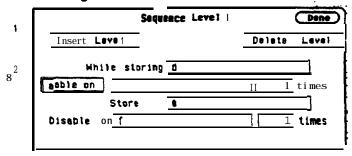

- a Place the cursor on the 1 in the **Sequence Levels field** of the menu and press **SELECT.**

b. Place the cursor on the anystate field to the right of the Trigger on field and press SELECT. Another pop-up appears showing you a list of "trigger on" options. Options a through h are qualifiers. You can assign them a pattern for the trigger specification.

- c. Place the cursor on the a option and press SELECT.

- d. Place the cursor on Done in the Sequence Levels pop-up and press **SELECT**.

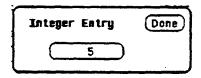

- e. Place the cursor on the field to the right of the a under the label ADDR and press SELECT.

- f. With the keypad, press 0 (zero) until there are all zeros in the Specify Pattern: pop-up and then press SELECT.

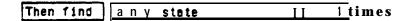

Your trigger specification now states: While storing anystate, trigger on "a" once and then store anystate."

When the state analyzer is connected to your circuit and is acquiring data, it continuously stores until it sees 0000 on the address bus, then it will store anystate until the analyzer memory is filled.

## Acquiring the Data

Since. you want to capture the data when the **microprocessor** sends address 0000 on the bus after power-up, you press the **RUN** key to arm **the** state analyzer and then force a reset of your circuit. When the reset cycle ends, the microprocessor should send address 0000, **trigger** the state analyzer and switch the display to the STATE **LISTING** menu

Well assume this **is what** happens **in** this example, since the odds that the microprocessor won't send address 0000 are **very** low.

Now is the time to load the state measurement demo file from the disk if you wish The **file** name **is** STATEDEMO. Follow the procedure in Appendix B to load the **file**.

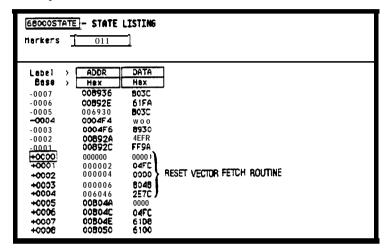

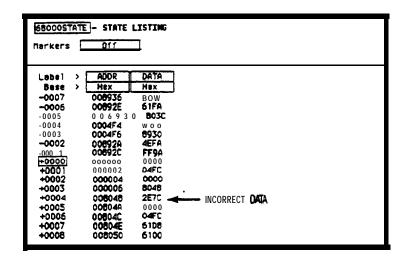

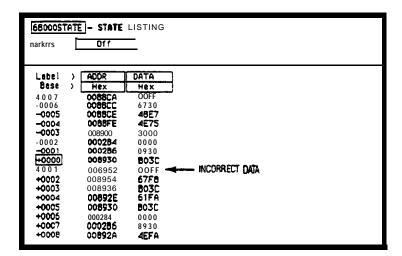

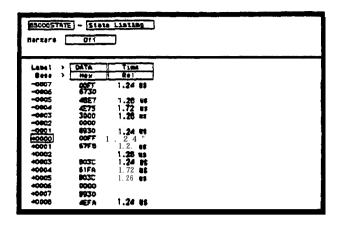

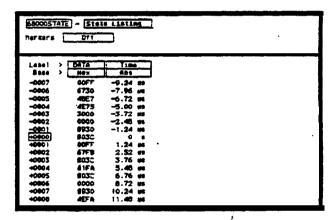

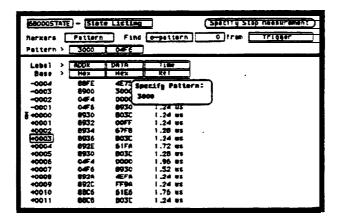

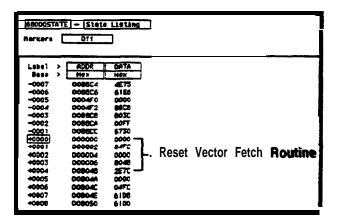

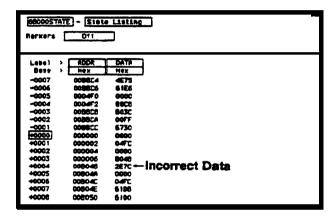

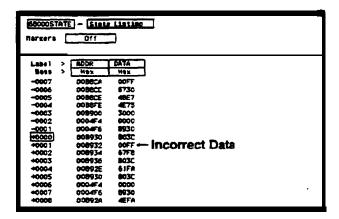

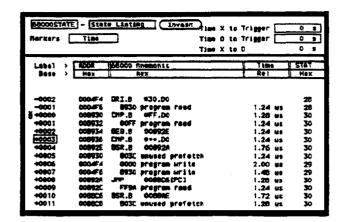

## The State Listing

The state listing displays three columns of numbers as shown:

STATE LOCATIONS

The first column of numbers are the state line number locations as they relate to the trigger point. The trigger state is on line + 0000 in the vertical center of the list area. The negative numbers indicate states occurring before the trigger and the positive numbers indicate states occurring after the trigger.

The second column of numbers are the states (listed in HEX) the state analyzer sees on the address bus. This column is labeled ADDR

The third column of numbers are the states (listed in HEX) the state analyzer sees on the data bus. This column is labeled DATA.

### Finding the Answer

Your answer is now found in the listing of states +0000 through +0004.

The 68000 always reads address locations 0, 2, 4, and 6 to find the stack pointer location and memory location for the **instruction** it fetches after power-up. The 68000 uses two words for each of the locations that it is looking for, a high word and a low word- When the software designer programs the ROM, he must put the stack pointer location at address locations 0 and 2. 0 is the high word location and 2 is the low word location. Similarly, the high word of the instruction fetch location must be in address location 4 and the low word in location 6.

Since the software design calls for the reset vector to:

- 1. set the stack pointer to **04FC**

- 2. read memory address location 8048 for its first instruction fetch,

you are interested in what is on both the address bus and the data bus in states 0 through 3. You look at the following listing and see that states 0 and 1 do contain address locations 0 and 2 under the ADDR label, indicating the **microprocessor** did look at the correct locations for the stack pointer data. You also see that the data contained in these ROM locations are OOUO and **04FC**, which are **correct**.

You then look at states 2 and 3. You see that the next two address locations are 4 and 6, which is correct, and the data found at these locations is 0000 and 8048, which is also correct.

- +0000 000000 0000

- +0001 000002 04FC

- +0002 000004 0000

- +0003 000006 8048

- +0004 008048 3E7C

So far you have verified that the microprocessor has **correctly** performed the reset vector **search**. The next thing **you** must **verify** is **whether the microprocessor addresses the correct location in ROM** that it was instructed to address in state 4 and whether the data is correct in this ROM location. From the listing you see that the address in state 4 is 008048, which is correct, but the instruction found in this location is **2E7C**, which is not **correct**. You have found your problem: incorrect data stored in ROM for the microprocessor's first instruction.

- +00a0 000000 0000 (high word of stack pointer location)

- +0001 WOO2 04FC (low word of stack pointer location)

- +0002 000004 0000 (high word of instruction fetch location)

- **+0003 000006** 8048 **(low word** of instruction fetch location)

- +0004 008048 **2E7C** (first microprocessor instruction)

### **Summary**

You have just learned how to make a simple state measurement with the HP 1650B Logic Analyzer. You have:

- specified a state analyzer

- learned which probes to connect

- assigned pods 1, 2, and 3

- assigned labels

- assigned bits

- specified the J clock

- specified a trigger condition

- acquiredthedata

- interpreted the state listing

You have seen bow easy it is to use the state analyzer to capture the data on the address and data buses. You can use this same technique to capture and display related data on de microprocessor status, control, and various strobe lines. You are not limited to using this technique on microprocessors. You can use this technique any time you need to capture data on multiple lines and need to sample the data relative to a system clock.

The next chapter teaches you how to use the logic analyzer as an interactive timing and state analyzer. You will see a simple measurement that shows you both timing waveforms and state listings audhowthey are correlated.

If you have an HP 1651B, you do not have enough channels to simultaneously capture all the data for a 68000. But, since you probably aren't working with 16-bit microprocessors, this example is still. valuable because it shows you how to make the same kind of measurement on an eight-bit microprocessor.

### Using the Timing/State Analyzer

#### Introduction

In this chapter you will learn how to use the timing and state analyzers interactively by setting up the logic analyzer to make a simple measurement. We give you the measurement results as actually measured by the logic analyzer, since you may not have the same circuit available.

The exercise in this chapter is organized differently than the exercises in the two previous chapters. Since you have already set up both the timing and state analyzers, you should be ready to set them up for this measurement by looking at the menu pictures.

Any new set-ups in this exercise will be explained in task format steps like the previous chapters.

How you use the steps depends On how much you remember from chapters 1 through 4. If you can set up each menu by just looking at the menu picture, go ahead and do so. If you need a reminder of what steps to perform, follow the numbered steps. If you still need more information about "how," use the lettered steps.

When you have finished configuring the logic analyzer for this exercise, you can load a file from the operating system disk. This file configures the logic analyzer the same way it is configured for this exercise. It also loads the same data acquired for this exercise so you can see what it looks like on screen.

In or&r to learn how to configure the logic analyzer, we recommend that you follow the exercise to "Acquiring the Data" before loading the file from the disk.

You can also compare your configuration with the one on the disk by printing it (if you have a printer) or making notes before you load the file.

# Problem Solving with the Timing/State Analyzer

In this example assume you have designed a microprocessor-controlled circuit. You have completed the hardware, and the software designer has completed the software and programmed the ROM (read-only memory). When you turn your circuit on for the first time, your circuit doesn't work properly. You have checked the power supply voltages and the system clock, and they are working properly.

Since the circuit has never worked before, you and the software engineer aren't sure if it is a hardware or software problem. You need to do some testing to find a solution.

You also notice the circuit fails intermittently. More specifically, it only fails when the microprocessor attempts to address a routine that starts at address 8930,

## What Am I Going to Measure?

To see what might be causing the failure, you decide to start where the microprocessor goes to the routine that starts at address 8930.

The first thing you check is whether the microprocessor actually addresses address 8930. The next thii you check is whether the code is correct in all the steps in this routine.

Your measurement, then, requires verification of:

- whether the microprocessor addresses location 8930

- whether all the addresses within the routine are correct

- whether all the data at the addresses in the routine are correct

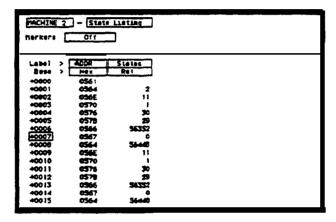

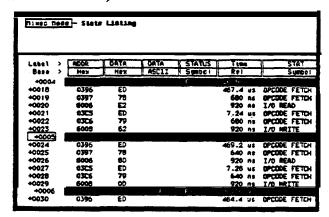

If the routine is correct, the state listing will display

+0000 008930 B03C +0001 008932 61FA +0002 008934 67F8 +0003 008936 B03C

+0004 00892E 61FA

## How Do I Configure the Logic Analyzer?

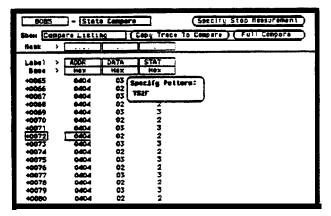

In order to make this measurement, you must configure the logic analyzer as a state analyzer because you want to trigger on a specific state (8930). You also want to verify that the addresses and data are correct in the states of this routine.

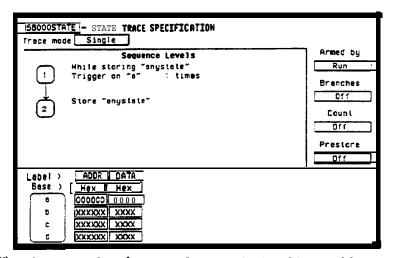

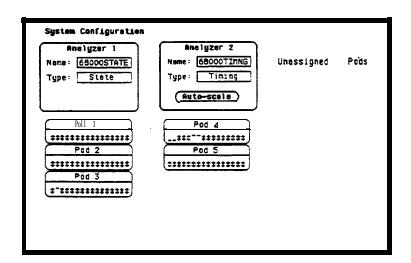

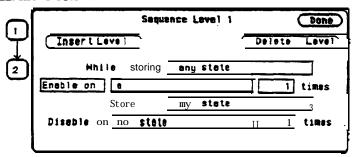

Configure the logic analyzer so that Analyzer 1 is a state analyzer as shown:

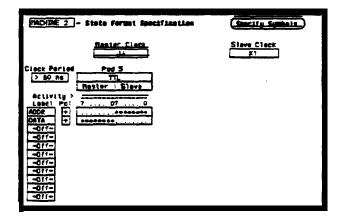

## **Configuring the State Analyzer**

Now that you have configured the system, you are ready to configure **the state analyzer.**

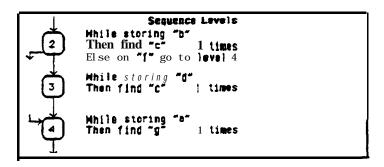

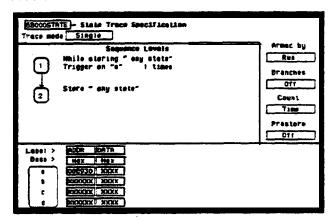

**Configure the STATE FORMAT** SPECIFICATION menu as shown:

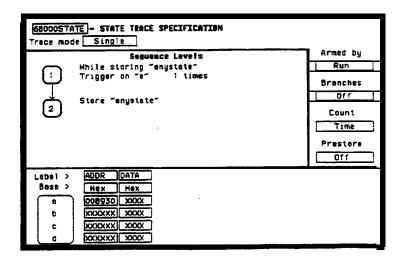

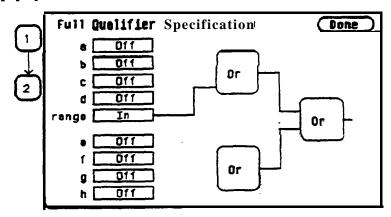

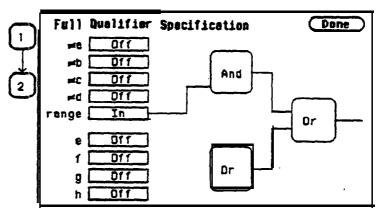

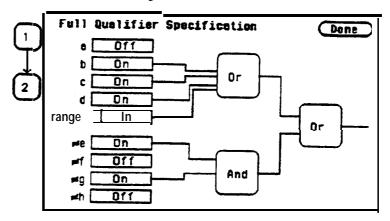

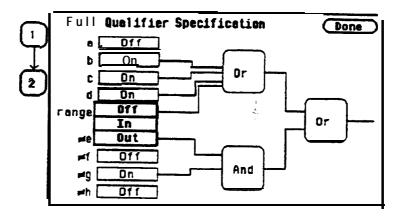

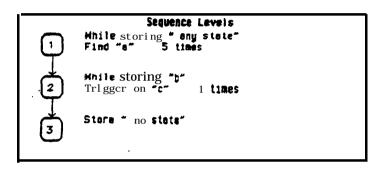

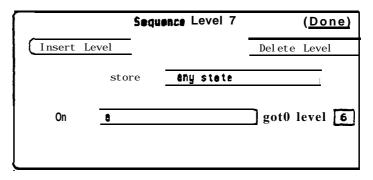

Configure the STATE TRACE SPECIFICATION menu as shown:

### Connecting the **Probes**

At **this** point, if you had **a** target system with a 68000 microprocessor, **you would connect** the logic analyzer to your system. **Since** you **will be assigning labels** ADDR and DATA, you will hook the probes to your **system accordingly**.

- Pod 1 probes 0 through 15 to the data bus lines D0 through D15

- Pod 2 probes 0 through 15 to the address bus lines A0 through A15

- Pod 3 probes 0 through 7 to the address bus lines A16 through A23

- Pod 1, CLK (J clock) to the address strobe (LAS)

### Acquiring the Data

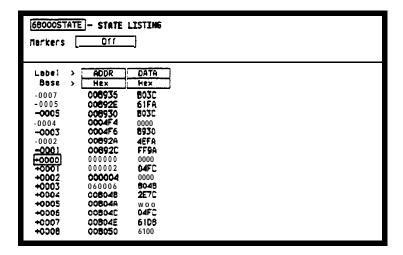

Since you want to capture the data when the **microprocesso**r sends **address 8930 on the** bus, you press the RUN key to arm the state analyzer. If the microprocessor sends address 8930, it will trigger the state analyzer and switch **the** display to the STATE **LISTING** menu.

Well assume this is what happens in this example.

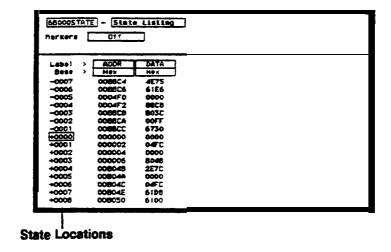

## Finding the **Problem**

You look at this listing to see what the data is in states +0000 through +0004. You know your routine is five states long.

The **68000** does address location 8930, so you know that the routine is addressed. Now you **need** to compare the state listing with the following **correct** addresses and data:

```

+0000 008930 B03C

+0001 008932 61FA

+0002 008934 67F8

+0003 008936 B03C

+0004 00892E 61FA

```

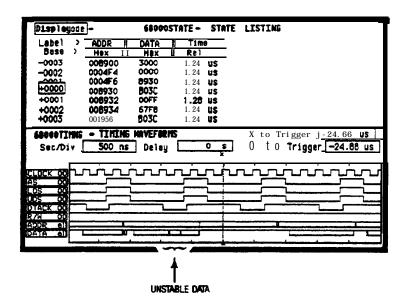

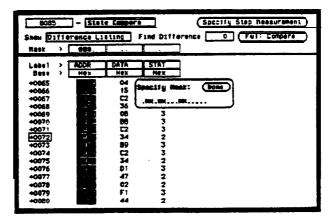

As you compare the state **listing** (shown below) with the **above** data, you **notice** the data at address 8932 is **incorrect.** Now you need to find out **why.**

Your first assumption is that incorrect data is stored to this memory location. Assume this routine is in ROM since it is part of the operating system for your circuit. Since the ROM is programmed by the software designer, you have the software designer verify whether or not the data at address 8932 is correct. The software designer tells you that the data is correct. Now what do you do?

Now it's time to look at the hardware to see if it is causing incorrect data when the microprocessor reads this memory address. You decide you want to see what is happening on the address and data buses during this routine in the time domain

In order to see the time domain, you need the timing analyzer.

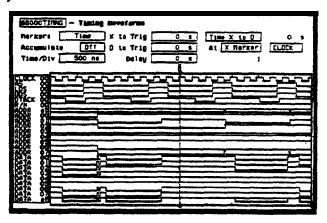

### What Additional Measurements Must | Make?

Since the problem exists during the routine that starts at address 8930, you decide you want to see the timing waveforms on the address and data bus when the routine is running. You also want to see the control signals that control the read cycle. You will then compare the waveforms with the timing diagrams in the 68000 data book.

Your measurement, then, requires verification of:

- correct timing of the control signals

- stable addresses and data during the memory read

The control signals you must check are:

- systemclock

- address strobe (AS)

- lower and upper data strobes (LDS and UDS)

- data transfer acknowledge (DTACK)

- read/write (R/W)

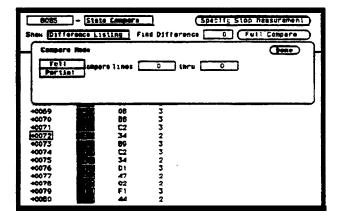

# How Do I Re-configure the Logic Analyzer?

In order to make this **measurement**, you must **re-configure** the logic **analyzer so Analyzer 2** is a timing analyzer. You leave Analyzer 1 as a state analyzer since you will use the state **analyzer** to trigger on address 8930.

Configure the logic analyzer so Analyzer 2 is a timing analyzer as shown:

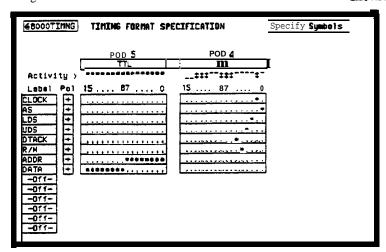

# Connecting the Timing Analyzer Probes

At this point you would connect the probes of pods 4 and 5 as follows:

- Pod 4 bit 0 to address strobe (AS)

- Pod 4 bit 1 to the system clock

- Pod 4 bit 2 to low data strobe (LDS)

- Pod 4 bit 3 to upper data strobe (UDS)

- Pod 4 bit 4 to the read/write (R/W)

- Pod 4 bit 5 to data transfer acknowledge (DTACK)

- Pod 5 bits 0 through 7 to address lines A0 through A7

- Pod 5 bits 8 through 15 to data lines D0 through D7

## Configuring the Timing Analyzer

Now that you have configured the system, you are ready to configure the timing analyzer.

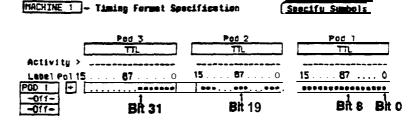

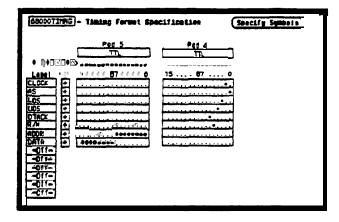

Configure the TIMING FORMAT SPECIFICATION mean as shown:

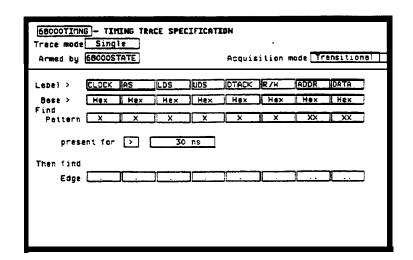

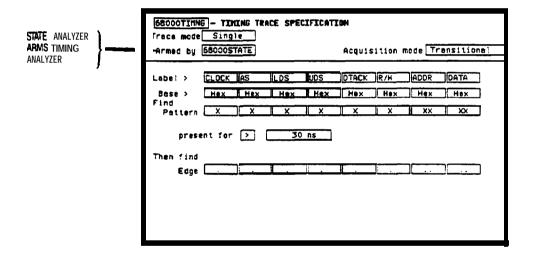

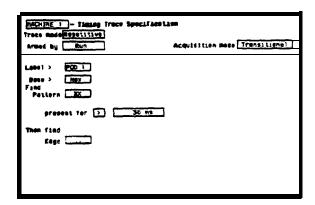

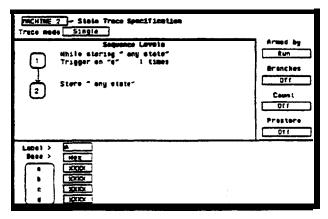

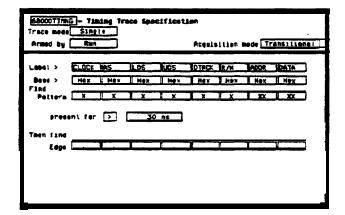

Configure the TIMING TRACE SPECIFICATION as shown:

HP 1650B/HP 1651B Getting Started Guide Using the liming/State Analyzer 7-9

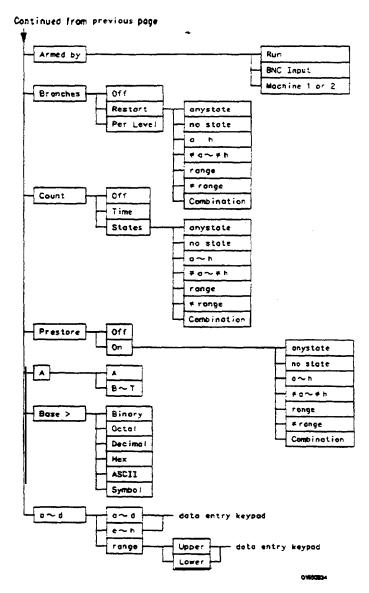

# Setting the Timing Analyzer Trigger

Your timing measurement requires the timing analyzer to display the timing waveforms present on the buses when the routine is running. Since you triggered the state analyzer on address 8930, you want to trigger the timing analyzer so the timing waveforms can be time correlated with the state listing.

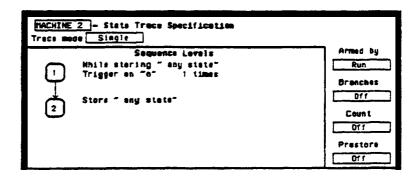

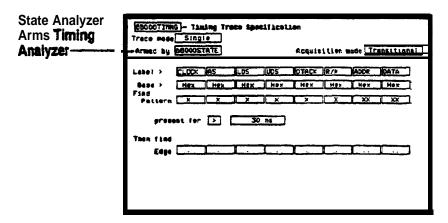

To set up the logic analyzer so that the state analyzer triggers the timing analyzer, perform these steps

- 1. Display the TIMING TRACE SPECIFICATION menu

- 2. Place the cursor on the Armed by field and press SELECT.

- 3. Place the cursor on the **68000STATE** option in the pop-up and press SELECT.

Your timing trace specification should match the menu shown:

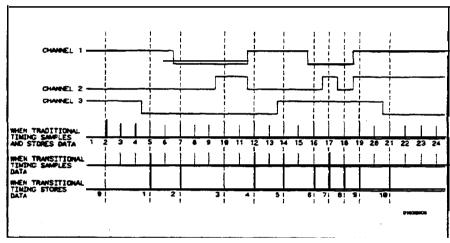

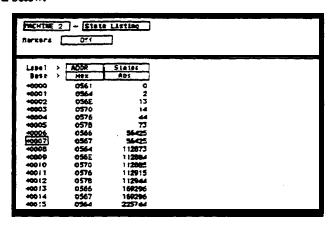

### T i m e Correlating the Data

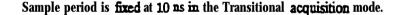

In order to time correlate the data, the logic analyzer must store the timing relationships between states. Since the timing analyzer samples asynchronously and the state analyzer samples synchronously, the logic analyzer must use the stored timing relationship of the data to reconstruct a time correlated display.

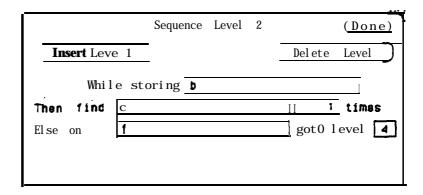

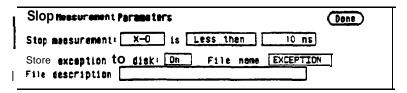

To set up the logic analyzer to keep track of these timing relationships, turn on a counter in the STATE TRACE SPECIFICATION menu The following steps show you how,

- 1. Display the **STATE TRACE** SPECIFICATION menu

- 2. Place the cursor in the field just below Count on the right side of the display and press SELECT.

- Place the cursor on the Time option and press SELECT. The counter will now be able to keep track of time for the time correlation.

### Re-acquiring the Data

After you connect the probes of pods 4 and 5 to your circuit, all yon have to do is press RUN. When the logic analyzer acquires the data, it switches the display to the STATELISTING menumless youswitched one of the other menus to the timing analyzer after reconfiguring the STATETRACE menu Regardless of which menu is displayed, change the display to the Mixed mode.

Now is the time to load the mixed measurement demo file from the disk if you wish. The file name is MIXEDDEMO. Follow the procedure in **Appendix B** to load the file.

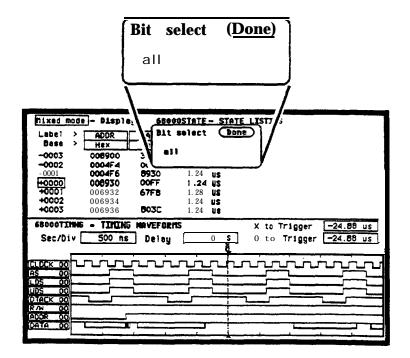

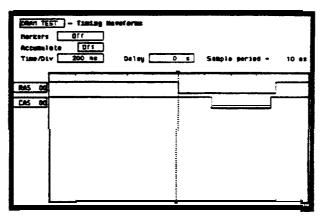

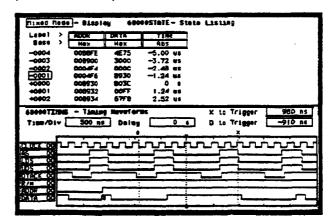

## Mixed Mode Display

The Mixed mode display shows you both the STATE **LISTING** and TIMING WAVEFORMS menus **simultaneously**. To change the **display to the Mixed mode**:

- LPlace the cursor on the field in the upperleft corner of the display and press**SELECT.**

- 2. Place the cursor on Mixed mode and pressSELECT.

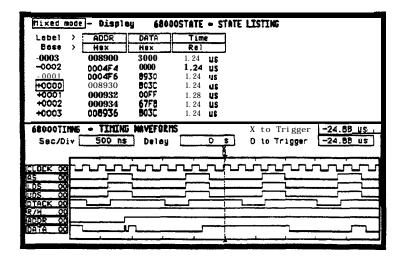

You will now see the mixed display as shown:

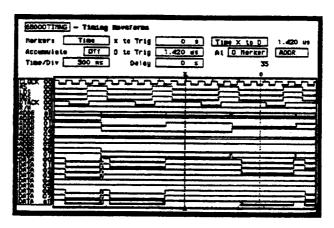

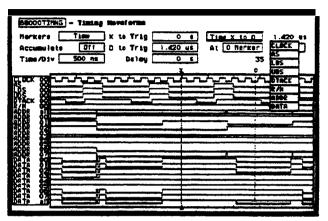

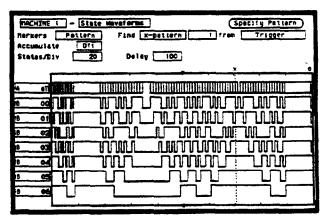

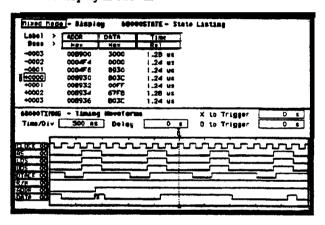

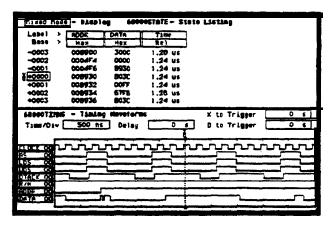

### Interpreting the Display

In the Mixed mode display the state listing is in the top half of the screen and the timing Waveforms are in the lower half. The important thing to remember is that you time correlated this display so you could see what is happening in the time domain during the faulty routine.

Notice that the trigger point in both parts of the display is the same as it was when the displays were separate. The trigger in the state listing is in the box containing +0000 and the trigger of the timing waveform is the vertical dotted line.

As you look at the mixed display, you notice nothing wrong except the data at address 8932 is incorrect. However, you are seeing only one bit each of the address and the data. To see all the data and addresses in the timing waveform part of the display, you must overlap them.

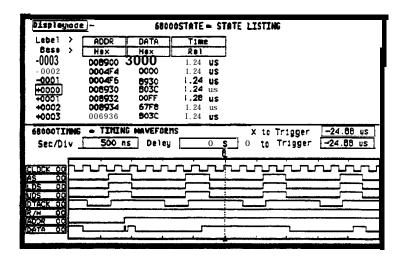

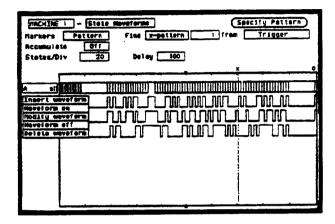

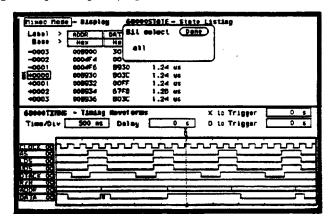

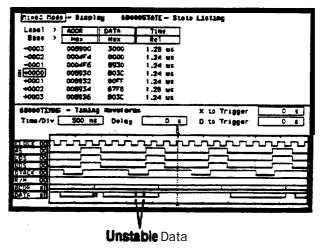

## Overlapping Timing Waveforms

Since you see nothing wrong with the timing waveform so far, you think unstable data may be on the data lines during the read cycle. In order to see unstable data, you must be able to see. all the data lines during the read and look for transitions. Overlapping the waveforms allows you to do this. To overlap waveforms, follow these steps:

- 1. Place the cursor on the 00 of the ADDR 00 label and press SELECT. The following pop-up opens in which you specify the bit or bits of the address bus you want to overlap.

- 2. Rotate the KNOB until all is displayed and press SELECT. All the address bits will be overlapped on one line.

- 3. Repeat step 2 except overlap the data bits.

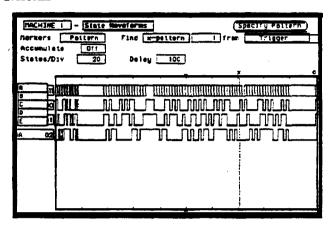

## Finding the Answer

As you look at the overlapping waveforms, you notice there are transitions on the data lines during the read cycle, indicating the data is unstable. You have found the probable cause of the problem in this routine. Additional troubleshooting of the hardware will identify the actual cause.

### **Summary**