# Agilent TS-8989 PXI Functional Test System

**Diagnostics User's Guide**

#### **Notices**

© Agilent Technologies Inc. 2014

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies Inc. as governed by United States and international copyright laws.

#### **Manual Part Number**

U8989-90003

#### **Edition**

First Edition, January 22, 2014 Printed in Malaysia

Agilent Technologies Microwave Products (Malaysia) Sdn. Bhd. Bayan Lepas Free Industrial Zone 11900, Penang, Malaysia

#### Warranty

The material contained in this document is provided "as is," and is subject to change, without notice, in future editions. Further, to the maximum extent permitted by the applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

#### **Technology Licenses**

The hardware and or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### **Restricted Rights Legend**

U.S. Government Restricted Rights. Software and technical data rights granted to the federal government include only those rights customarily provided to end user customers. Agilent provides this customary commercial license in Software and technical data pursuant to FAR 12.211 (Technical Data) and 12.212 (Computer Software) and, for the Department of Defense, DFARS 252.227-7015 (Technical Data - Commercial Items) and DFARS 227.7202-3 (Rights in Commercial Computer Software or Computer Software Documentation).

#### **Safety Notices**

#### **CAUTION**

A **CAUTION** notice denotes a hazard. It calls attention to an operating procedure, practice, or the likes of that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a **CAUTION** notice until the indicated conditions are fully understood and met.

#### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the likes of that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARN-ING notice until the indicated conditions are fully understood and met.

#### **Table of Contents**

### Warranty 2 **Technology Licenses** Restricted Rights Legend 3 Service and Support Agilent on the web Agilent by phone **Safety and Regulatory Information** 2 Safety Summary Safety Notices **General Safety Considerations** 7 **Environmental Conditions** Before Applying Power **Ground the System Fuses** 9 **Operator Safety Information** Safety Symbols and Regulatory Markings 11 **Declaration of Conformity** Electrostatic Discharge (ESD) Precautions 14 End of Life: Waste Electrical and Electronic Equipment (WEEE) Directive 2002/96/EC 15 **Running Diagnostics** 3 Overview of Diagnostics Testplans 18

**Legal Information**

1

|   | Standard instruments and the system.ust file 18 Configuring the system.ust file in the System Configuration Editor 20 |

|---|-----------------------------------------------------------------------------------------------------------------------|

|   | Configuring and Running the DGN Testplan 21                                                                           |

|   | Configuring and Running the CEDGN Testplan 23                                                                         |

|   | Installing the Diagnostic Test Fixtures 25 Installing the CEDGN fixture kit bracket 32                                |

|   | Resolving Test Failures 36                                                                                            |

| 4 | Diagnostic Testing Details                                                                                            |

|   | DGN Testplan Description and Flow 38                                                                                  |

|   | Sequence 00: Global Reset 38                                                                                          |

|   | Sequence 01: SLU Detection 38                                                                                         |

|   | Sequence 02: PXI and PCI Modules Detection 38                                                                         |

|   | Sequence 03: Instrument Matrix Detection 38                                                                           |

|   | Sequence 04: DMM Detection and Test 39                                                                                |

|   | Sequence 05: Pin Matrix Switching Test 39                                                                             |

|   | CEDGN Testplan Description and Flow 48                                                                                |

|   | Sequence 00: Global Reset 48                                                                                          |

|   | Sequence 01: SLU Detection 48                                                                                         |

|   | Sequence 02: PXI & PCI Modules Detection 48                                                                           |

|   | Sequence 03: Instrument Matrix Detection 48                                                                           |

|   | Sequence 04: DMM Detection & Test 49                                                                                  |

|   | Sequence 05: Pin Matrix Switching Test 49                                                                             |

|   | Sequence 06: SLU Utility Test 49                                                                                      |

|   | Sequence 07: PXI Modules Test 50                                                                                      |

|   | Sequence 08: PCI Modules Test 58                                                                                      |

|   | Sequence 09: Load Card Test 60                                                                                        |

| 5 | Diagnostic Test Fixture Details                                                                                       |

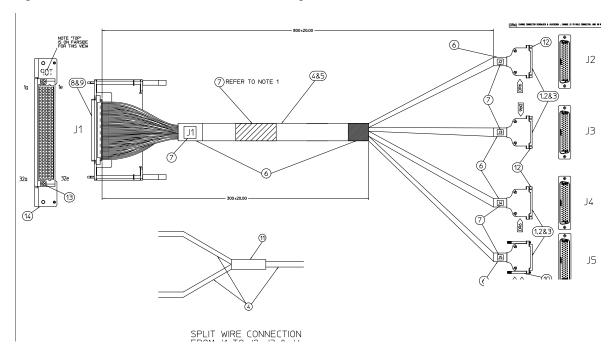

|   | U8989-61625 E8792A/E8793A Pin Matrix Cable 96                                                                         |

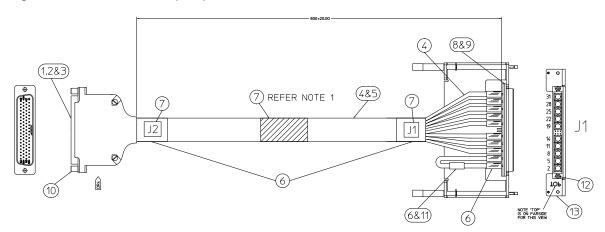

| U8989-61619 E8782A/E8783A Pin Matrix Cable 9     | 98      |

|--------------------------------------------------|---------|

| U8989-61620 SLU Utility Cable 101                |         |

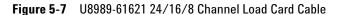

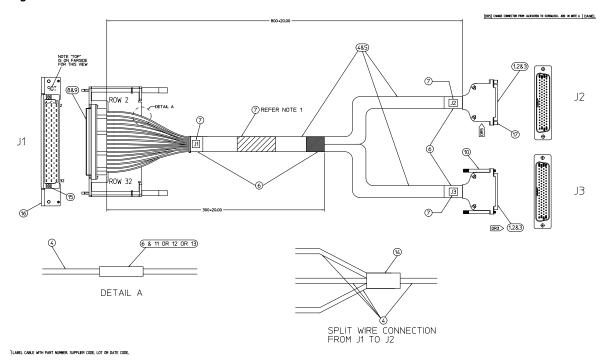

| U8989-61621 24/16/8 Channel Load Card Cable      | 103     |

| U8989-61622 48 Channel Load Card Cable 106       |         |

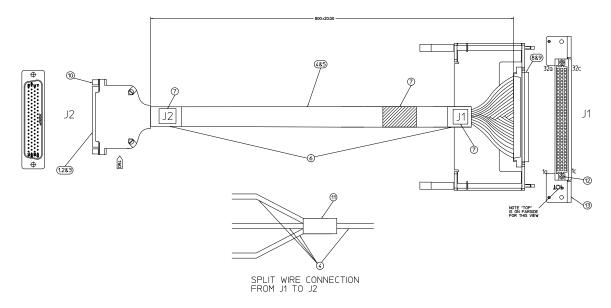

| U8989-61623 Universal Instrument Routing Card Ca | ble 109 |

| 118989-61624 Heavy Duty Load Card Cable 113      |         |

THIS PAGE HAS BEEN INTENTIONALLY LEFT BLANK.

## **List of Figures**

| igure 2-1                  | Examples of exposed connectors 10                                                                 |

|----------------------------|---------------------------------------------------------------------------------------------------|

| igure 3-1                  | Configure DUT power supply in the CEDGN testplan 24                                               |

| igure 3-2                  | Installing the U8989-61625 CEDGN Test Fixture 25                                                  |

| igure 3-3                  | Installing the SLU Utility U8989-61620 CEDGN Test                                                 |

|                            | Fixture with a U8989-61625 CEDGN Pin Matrix                                                       |

|                            | Cable 26                                                                                          |

| igure 3-4                  | Installing the Load Card U8989-61 1 CEDGN Test Fixture                                            |

|                            | with a U8989-61625CEDGN Pin Matrix Cable 27                                                       |

| igure 3-5                  | Installing the Load Card ISense U8989-61621 CEDGN                                                 |

|                            | Test Fixtures with a U8989-61625 CEDGN Pin Matrix                                                 |

|                            | Cable 28                                                                                          |

| igure 3-6                  | Installing the Heavy Duty Load Card U8989-61624                                                   |

|                            | CEDGN Test Fixture with a U8989-61625 CEDGN Pin                                                   |

|                            | Matrix Cable 29                                                                                   |

| igure 3-7                  | Installing the 48-Channel Load Card U8989-61622                                                   |

|                            | CEDGN Test Fixture with a U8989-61625 CEDGN in                                                    |

|                            | Matrix Cable 30                                                                                   |

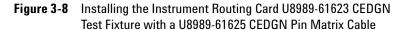

| igure 3-8                  | Installing the Instrument Routing Card U8989-61623                                                |

|                            | CEDGN Test Fixture with a U8989-61625 CEDGN Pin                                                   |

| -: 0.0                     | Matrix Cable 31                                                                                   |

| igure 3-9                  | Overview of the CEDGN Fixture Kit Bracket 32                                                      |

| igure 3-10                 | CEDGN Fixture Kit Bracket Installation Step 1 33                                                  |

| igure 3-11                 | CEDGN Fixture Kit Bracket Installation Step 2 33                                                  |

| Figure 3-12                | CEDGN Fixture Kit Bracket Installation Step 3 34 CEDGN Fixture Kit Bracket Installation Step 4 34 |

| Figure 3-13<br>Figure 3-14 | CEDGN Fixture Kit Bracket Installation Step 4 34 CEDGN Fixture Kit Bracket Installation Step 5 35 |

| Figure 3-14                | CEDGN Fixture Kit Bracket Installation Step 9 35                                                  |

| igure 3-13                 | Instrument Matrix Inst1 and Inst2 Pin Test 40                                                     |

| igure 4-1                  | ABUS Short Test 41                                                                                |

| Figure 4-3                 | Instrument Matrix Inst3 and Inst4 Pin Test 41                                                     |

| Figure 4-4                 | Instrument Matrix DAC Relay Test 42                                                               |

| igure 4-5                  | Instrument Rows Open/Short Test 43                                                                |

| Figure 4-6                 | Measurement Rows Open/Short Test 44                                                               |

| igure 4-7                  | Bypass Relays Test 45                                                                             |

| igure 4-8                  | Pin Matrix Fixture Test (Row Pin) 46                                                              |

|                            |                                                                                                   |

```

Figure 4-9 Pin Matrix Fixture Test (Aux Pin) 47

Figure 4-10 DAC Output Port Test 51

Figure 4-11 DAC Output Sense Port Test 51

Figure 4-12 DAC Trigger Port Test 52

Figure 4-13 DMM Internal Switching Connection Test 53

Figure 4-14 VI Voltage and Current Test - VI Interlock

Connection 54

Figure 4-15 DIO DI DO Test 55

Figure 4-16 DIO GND Test 56

Figure 4-17 DIO Vex Test 56

Figure 4-18 DAQ Input Port Test 57

Figure 4-19 DAQ Aux Port Test 58

Figure 4-20 AD1750 Test 59

Figure 4-21 Softing CAN Test 60

Figure 4-22 E6175A Unpowered Load Card Test 62

Figure 4-23 E6175A Powered Load Card Test 63

Figure 4-24 E6175A Current Sense Test 64

Figure 4-25 E6176A Unpowered Load Card Test 66

Figure 4-26 E6176A Powered Load Card Test 67

Figure 4-27 E6176A Current Sense Test 68

Figure 4-28 E6177A Unpowered Load Card Test 70

Figure 4-29 E6177A Powered Load Card Test 71

Figure 4-30 U7177A Unpowered Load Card Test 73

Figure 4-31 U7177A Powered Load Card Test 74

Figure 4-32 U7177A Current Sense Test 75

Figure 4-33 N9377A Unpowered Load Card Test 77

Figure 4-34 N9377A Powered Load Card Test 78

Figure 4-35 N9377A Current Sense Test 79

Figure 4-36 N9378A Unpowered Load Card Test 81

Figure 4-37 N9378A Powered Load Card Test 82

Figure 4-38 U7179A Unpowered Load Card Test 84

Figure 4-39 U7179A Powered Load Card Test 85

Figure 4-40 U7179A Current Sense Test 86

Figure 4-41 N9379A Unpowered Load Card Test 88

Figure 4-42 E6178B Unpowered Load Card Test 90

Figure 4-43 E6178B Current Sense Test 91

Figure 4-44 U7178A Unpowered Load Card Test 93

Figure 4-45 U7178A Current Sense Test 94

```

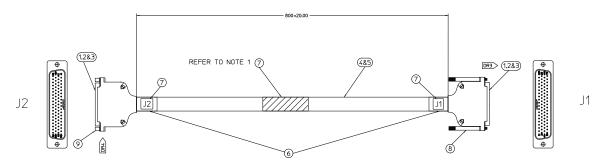

| igure 5-1  | U8989-61625 | E8792A/E8793A Pin Matrix C          | able | 96    |

|------------|-------------|-------------------------------------|------|-------|

| igure 5-2  | U8989-61625 | E8792A/E8793A Pin Matrix C          | able |       |

|            | Schematic   | 96                                  |      |       |

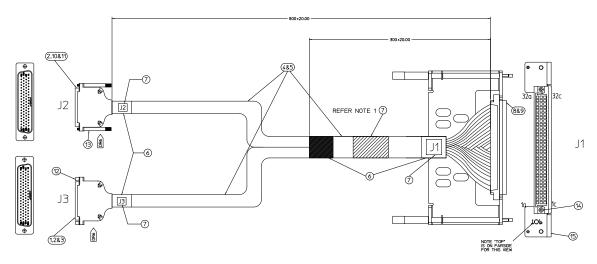

| igure 5-3  | U8989-61619 | E8782A/E8783A Pin Matrix C          | able | 98    |

| igure 5-4  | U8989-61619 | E8782A/E8783A Pin Matrix C          | able |       |

|            | Schematic   | 99                                  |      |       |

| igure 5-5  |             | SLU Utility Cable 101               |      |       |

| igure 5-6  | U8989-61620 | SLU Utility Cable Schematic         | 101  |       |

| igure 5-7  | U8989-61621 | 24/16/8 Channel Load Card C         | able | 103   |

| igure 5-8  | U8989-61621 | 24/16/8 Channel Load Card C         | able |       |

|            | Schematic   |                                     |      |       |

| igure 5-9  | U8989-61622 | 48 Channel Load Card Cable          | 106  |       |

| igure 5-10 | U8989-61622 | 48 Channel Load Card Cable          |      |       |

|            | Schematic   |                                     |      |       |

| igure 5-11 | U8989-61623 | <b>Universal Instrument Routing</b> | Card |       |

|            | Cable 109   |                                     |      |       |

| igure 5-12 | U8989-61623 | <b>Universal Instrument Routing</b> | Card | Cable |

|            | Schematic   | 110                                 |      |       |

| •          |             | Heavy Duty Load Card Cable          | 113  |       |

| igure 5-14 |             | Heavy Duty Load Card Cable          |      |       |

|            | Schematic   | 113                                 |      |       |

THIS PAGE HAS BEEN INTENTIONALLY LEFT BLANK.

## **List of Tables**

| Table 2-1 | General environmental requirements 8                  |

|-----------|-------------------------------------------------------|

| Table 2-2 | Safety symbols and regulatory markings 11             |

| Table 2-3 | Suggested anti-static solutions for site planning 14  |

| Table 3-1 | List of standard instruments in the TS-8989 system 19 |

| Table 4-1 | V/I source output value 53                            |

| Table 5-1 | U8989-61625 Cable Pinout 97                           |

| Table 5-2 | U8989-61619 Cable Pinout 100                          |

| Table 5-3 | U8989-61620 Cable Pinout 102                          |

| Table 5-4 | U8989-61621 Cable Pinout 105                          |

| Table 5-5 | U8989-61622 Cable Pinout 108                          |

| Table 5-6 | U8989-61623 Cable Pinout 111                          |

| Table 5-7 | U8989-61624 Cable Pinout 114                          |

THIS PAGE HAS BEEN INTENTIONALLY LEFT BLANK.

TS-8989 PXI Functional Test System Diagnostics User's Guide

1

Legal Information

Warranty 2

Technology Licenses 2

Restricted Rights Legend 3

Service and Support 4

Agilent on the web 4

Agilent by phone 4

#### 1 Legal Information

Warranty

## Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions.

Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose.

Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein.

Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

## **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

## **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication, or disclosure of Software is subject to Agilent Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2)(June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2)(November 1995), as applicable in any technical data.

#### 1 Legal Information

Service and Support

## **Service and Support**

Any adjustment, maintenance, or repair of this product must be performed by qualified personnel. Contact your customer engineer through your local Agilent Service Center.

## Agilent on the web

You can find information about technical and professional services, product support, and equipment repair and service on the web: http://www.agilent.com/

Double-click the link to **Test & Measurement**. Select your country from the drop-down menus. The web page that appears next has contact information specific for your country.

## **Agilent by phone**

If you do not have access to the Internet, call one of the numbers in the "Contact us" section at the end of this manual.

|   | TS-8989 PXI Functional Test System Diagnostics User's Guide |

|---|-------------------------------------------------------------|

|   | • 2                                                         |

|   | Safety and Regulatory Information                           |

|   | Safety Summary 6                                            |

| • | Safety Notices 6                                            |

|   | General Safety Considerations 7                             |

|   | Environmental Conditions 8                                  |

|   | Before Applying Power 9                                     |

|   | Ground the System 9                                         |

|   | Fuses 9                                                     |

|   | Operator Safety Information 10                              |

Declaration of Conformity 13

2002/96/EC 15

Safety Symbols and Regulatory Markings 11

Electrostatic Discharge (ESD) Precautions 14

End of Life: Waste Electrical and Electronic Equipment (WEEE) Directive

Safety Summary

## **Safety Summary**

The following general safety precautions must be observed during all phases of operation of this instrument. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the instrument. Agilent Technologies, Inc. assumes no liability for the customer's failure to comply with these requirements.

## **Safety Notices**

CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like, that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

## **General Safety Considerations**

This product is provided with a protective earth terminal. The protective features of this product may be impaired if it is used in a manner not specified in the operation instructions.

#### WARNING

- DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE. Do not operate the product in the presence of flammable gases or flames.

- DO NOT REMOVE RACK PANELS OR INSTRUMENT COVERS.

Operating personnel must not remove any rack panels or instrument covers. Component replacement and internal adjustments must be made only by qualified service personnel.

Products that appear damaged or defective should be made inoperative and secured against unintended operation until they can be repaired by a qualified service personnel.

- The protection provided by the TS-8989 system may be impaired if the system is used in a manner not specified by Agilent.

#### 2 Safety and Regulatory Information

**Environmental Conditions**

## **Environmental Conditions**

The TS-8989 Automotive Electronics PXI Functional Test System is designed for indoor use only. Table 2-1 shows the general environmental requirements.

Table 2-1

General environmental requirements

| Environment condition | Requirement                                                                                           |

|-----------------------|-------------------------------------------------------------------------------------------------------|

| Maximum altitude      | 2000 meters                                                                                           |

| Operating temperature | 5 °C to 40 °C                                                                                         |

| Relative humidity     | The test system is designed to operate in the range from 5% to 80% relative humidity (non-condensing) |

CAUTION

This product is designed for use in Installation Category II and Pollution Degree 2, per IEC 61010-1 and 664 respectively.

## **Before Applying Power**

Verify that the product is set to match the available line voltage and that all safety precautions are taken. Note the external markings of the instruments described in "Safety Symbols and Regulatory Markings".

## **Ground the System**

Agilent chassis' are provided with a grounding-type power plug. The instrument chassis and cover must be connected to an electrical ground to minimize shock hazard. The ground pin must be firmly connected to an electrical ground (safety ground) terminal at the power outlet. Any interruption of the protective (grounding) conductor or disconnection of the protective earth terminal will cause a potential shock hazard that could result in personal injury.

### **Fuses**

Use only fuses with the required rated current, voltage, and specified type (fast acting). Do not use repaired fuses or short-circuited fuse holders. Doing so could cause a shock or fire hazard.

WARNING

To avoid electrical hazards, all system internal fuses must be replaced by trained and qualified personnel.

**Operator Safety Information**

## **Operator Safety Information**

### WARNING

Module connectors and test signal cables connected to them cannot be operator-accessible.

Cables and connectors are considered inaccessible if a tool (such as a screwdriver, wrench, or socket) or a key (for equipment in a locked cabinet) is required to gain access to a conductive surface connected to any cable conductor (High, Low, or Guard).

WARNING

Do not touch the exposed connector pins or remove connected cables while the system is powered ON (see Figure 2-1).

Figure 2-1 Examples of exposed connectors

## **Safety Symbols and Regulatory Markings**

Symbols and markings on the system, in manuals, and on instruments alert you to potential risks, provide information about conditions, and comply with international regulations. Table 2-2 defines the symbols and markings you may find in a manual or on an instrument.

**Table 2-2** Safety symbols and regulatory markings

| Symbol       | Description                                                          |  |  |

|--------------|----------------------------------------------------------------------|--|--|

| Safety symb  | Safety symbol                                                        |  |  |

| A            | Warning: risk of electrical shock.                                   |  |  |

|              | Warning: hot surface.                                                |  |  |

| Ŵ            | Caution: refer to accompanying documents.                            |  |  |

| *            | Laser radiation symbol: marked on products that have a laser output. |  |  |

| $\sim$       | Alternating current.                                                 |  |  |

| $\sim$       | Both direct and alternating current.                                 |  |  |

| 3~           | 3-phase alternating current.                                         |  |  |

| <del>-</del> | Earth (ground) terminal.                                             |  |  |

|              | Protective earth (ground) terminal.                                  |  |  |

#### 2 Safety and Regulatory Information

Safety Symbols and Regulatory Markings

Table 2-2

Safety symbols and regulatory markings (continued)

| Symbol             | Description                                                                                                                                                                                                                                                                   |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\rightarrow$      | Frame or chassis terminal.                                                                                                                                                                                                                                                    |

|                    | Terminal is at earth potential. Used for measurement and control circuits designed to be operated with one terminal at earth potential.                                                                                                                                       |

| Ν                  | Terminal for a neutral conductor on permanently installed equipment.                                                                                                                                                                                                          |

| L                  | Terminal for a line conductor on permanently installed equipment.                                                                                                                                                                                                             |

| மு                 | Standby (supply); units with this symbol are not completely disconnected from the AC mains when this switch is turned off. To completely disconnect the unit from the AC mains, either disconnect the power cord, or have a qualified electrician install an external switch. |

| Regulatory i       | marking                                                                                                                                                                                                                                                                       |

| CE<br>ISM 1-A      | The CE mark is a registered trademark of the European Community. If it is accompanied by a year, it indicates the year the design was proven.                                                                                                                                 |

| © ®                | The CSA mark is a registered trademark of the Canadian Standards Association.                                                                                                                                                                                                 |

| <b>C</b><br>N10149 | The C-tick mark is a registered trademark of the Spectrum Management Agency of Australia. This signifies compliance with the Australian EMC Framework regulations under the terms of the Radio Communications Act of 1992.                                                    |

| ISM - 1A           | This text indicates that the instrument is an Industrial Scientific and Medical Group 1 Class A product (CISPER 11, Clause 4).                                                                                                                                                |

## **Declaration of Conformity**

The Declaration of Conformity (DoC) for this instrument is available on the Agilent website. You can search the DoC by its product model or description at the web address below.

http://regulations.corporate.agilent.com/DoC/search.htm

NOTE

If you are unable to search for the respective DoC, contact your local Agilent representative.

## **Electrostatic Discharge (ESD) Precautions**

Static electricity is destructive to your production process and the TS-8989. Careless handling and poor site planning can cause system reliability problems and reduce your product yield. The system may not be as easily damaged as the modules you will be testing, but good anti-static planning will help ensure high reliability.

The ESD symbol below indicates areas where ESD caution must be exercised. This is to prevent damage to instruments and/or test disruption.

#### Caution: static sensitive

Electrostatic discharge in this area may cause equipment damage and/or test disruption.

While not an exhaustive list of anti-static precautions, Table 2-3 provides suggestions to consider as you plan your system area.

**Table 2-3** Suggested anti-static solutions for site planning

| Precaution           | Suggested solution                                                                                   |  |

|----------------------|------------------------------------------------------------------------------------------------------|--|

| Anti-static flooring | Plan to use an anti-static floor covering or mats.                                                   |  |

| Grounding straps     | Plan for foot straps in conjunction with anti-static flooring and wrist straps for system operators. |  |

## End of Life: Waste Electrical and Electronic Equipment (WEEE) Directive 2002/96/EC

This instrument complies with the WEEE Directive (2002/96/EC) marking requirement. This affixed product label indicates that you must not discard this electrical or electronic product in domestic household waste.

#### **Product Category:**

With reference to the equipment types in the WEEE directive Annex 1, this instrument is classified as a "Monitoring and Control Instrument" product.

The affixed product label is as shown below.

#### Do not dispose in domestic household waste.

To return this unwanted instrument, contact your nearest Agilent Service Center, or visit

www.agilent.com/environment/product

for more information.

| THIS PAGE HAS BEEN INTE | ENTIONALLY LEFT BLANK. |  |

|-------------------------|------------------------|--|

|                         |                        |  |

|                         |                        |  |

End of Life: Waste Electrical and Electronic Equipment (WEEE) Directive 2002/96/EC

2

**Safety and Regulatory Information**

TS-8989 PXI Functional Test System Diagnostics User's Guide

## Running Diagnostics

Overview of Diagnostics Testplans 18

Standard instruments and the system.ust file 18

Configuring the system.ust file in the System Configuration Editor 20

Configuring and Running the DGN Testplan 21

Configuring and Running the CEDGN Testplan 23

Installing the Diagnostic Test Fixtures 25

Resolving Test Failures 36

This chapter describes the overview of the diagnostic testplans, the DGN testplan, and the CEDGN testplan. It also teaches you to use the diagnostics test fixtures to verify the operation of the system equipment.

NOTE

Diagnostic testing is intended to verify basic connectivity and instrument functionality. It does not provide a full functional test of instrumentation and specifications.

#### 3 Running Diagnostics

Overview of Diagnostics Testplans

## **Overview of Diagnostics Testplans**

Standard diagnostic testplans are shipped with each system. There are two different testplans to test the system, from functionality to internal connections, to connections on the Test System Interface.

The first testplan, called the DGN, is used to verify both the core system instrument operation and internal test paths. No hardware is required to run this testplan. It verifies about 50% of the system functionality.

The second testplan, the "Customer Engineer Diagnostics" testplan or simply CEDGN, is used to complete the test coverage. This test requires external hardware, which is packaged as a CEDGN kit, because it verifies the internal connections out to the Test System Interface.

The tests are executed in the Agilent TestExec SL software and the TS-8989 system programming environment using both standard and specialized test actions. The testplans only cover standard instruments in the system. If there is a special case where non-standard equipment are incorporated into the system, tests for these equipment would have to be added.

## Standard instruments and the system.ust file

Before running the DGN or CEDGN testplans, instruments in the system have to be added to the *system.ust* file. Testplans can access and control instruments only if they have been added into the *system.ust* file.

Standard instruments in the TS-8989 are included in the DGN and CEDGN testplans. A  $\checkmark$  (tick) next to an instrument shows that it is included in the DGN or CEDGN testplan.

Table 3-1

List of standard instruments in the TS-8989 system

| P/N         | Description                                                    | DGN      | CEDGN    |

|-------------|----------------------------------------------------------------|----------|----------|

| E6198B      | 21-Slot Switch/Load Unit                                       | ~        | <b>✓</b> |

| E8792A      | 32 Measurement Channels and 16 Instrument Channels Matrix Card | <b>✓</b> | <b>✓</b> |

| E8793A      | 32-Pin Matrix Card                                             | <b>✓</b> | V        |

| E8782A      | 40 Measurement Channels and 24 Instrument Channels Matrix Card | <b>✓</b> | V        |

| E8783A      | 64-Pin Matrix Card                                             | <b>✓</b> | ~        |

| E6175A      | 8-Channel Load Card                                            |          | V        |

| E6176A      | 16-Channel Load Card                                           |          | ~        |

| E6177A      | 24-Channel Load Card                                           |          | ~        |

| E6178B      | 8-Channel Load Card                                            |          | ~        |

| U7177A      | 24-Channel Load Card with Current Sense                        |          | ~        |

| U7178A      | 8-Channel Heavy Duty Load Card                                 |          | ~        |

| U7179A      | 16-Channel High Current Load Card                              |          | ~        |

| N9377A      | 16-Channel Dual-Load Load Card                                 |          | ~        |

| N9378A      | 24-Channel Low Resistance Load Card                            |          | ~        |

| N9379A      | 48-Channel High-Density Load Card                              |          | ~        |

| M9182A      | DMM                                                            | <b>✓</b> | ~        |

| M9183A      | DMM                                                            | ~        | ~        |

| M9186A      | V/I Source                                                     | ~        | ~        |

| M9185A      | 8-Channel/16-Channel DAC                                       | ~        | ~        |

| M9216A      | 32-Channel HV-DAQ                                              | ~        | ~        |

| M9187A      | 32-Channel PXI DIO                                             | ~        | ~        |

| AD1750      | 32-Channel PCI DIO                                             | ~        | ~        |

| Softing CAN | 2 Channel CAN                                                  | <b>V</b> | V        |

## Configuring the system.ust file in the System Configuration Editor

**1** Start the System Configuration Editor by clicking this icon on your desktop:

- **2** Click on the *detected on system* button. The screen will show instruments detected on the system. Any instrument in Table 3-1 which is in your system should be detected.

- **3** Double-click on the instrument name to add it to the *system.ust* file. It is recommended that you add instruments in the following order:

- i the SLU,

- ii the first pin matrix card in the SLU, and

- iii other instruments in any order.

#### NOTE

At least 1 SLU, 1 Pin Matrix, and 1 DMM must be in the system and in the *.ust* file for the DGN and CEDGN testplans to run.

**4** Once the instruments have been added, click **Save** or **Save As** if you would like to change the name of your .ust file.

#### NOTE

Ensure that you have added all the standard instruments you would like to test. The DGN and CEDGN testplans will only test instruments in the .ust file.

## **Configuring and Running the DGN Testplan**

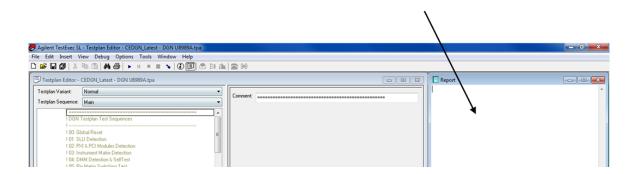

**1** Start the Agilent TestExec SL (version 7.1 or greater) by clicking this icon on your desktop:

**2** Load the *DGN U8989A.tpa* testplan into the TestExec SL. The testplans are located in this directory:

C:\Program Files\Agilent\TS-5000 System

Software\testplan\dgn

or

C:\Program Files (x86)\Agilent\TS-5000

System Software\testplan\dgn

**3** Press the play button (shown by the arrow in the figure below) to run the testplan.

**4** During certain sequences, message boxes will pop up with instructions on putting on fixtures or taking them out. Follow these instructions carefully to avoid any test errors.

#### **3 Running Diagnostics**

Configuring and Running the DGN Testplan

**5** The test report will be printed in the report window (shown by the arrow in the figure below).

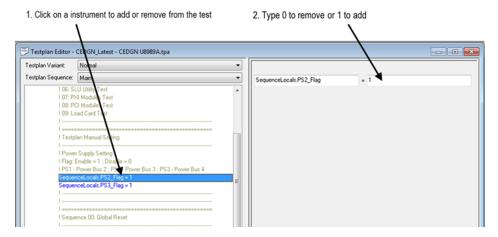

## **Configuring and Running the CEDGN Testplan**

1 Start the Agilent TestExec SL (version 7.1 or greater) by clicking this icon on your desktop:

**2** Load the *CEDGN U8989A.tpa* testplan into the TestExec SL. The testplans are located in this directory:

C:\Program Files (x86)\Agilent\TS-5000

System Software\Service\U8989A\Testplans

or

C:\Program Files (x86)\Agilent\TS-5000

System Software\Service\U8989A\Testplans

**3** The CEDGN testplan will perform the test according to the settings set in the system topology file.

However, the DUT power supply needs to be configured in the CEDGN testplan as shown in Figure 3-1.

Place a 1 next to instruments you want to test and a 0 next to the instruments you do not want to test (or instruments that are not in your system).

#### 3 Running Diagnostics

Configuring and Running the CEDGN Testplan

Figure 3-1 Configure DUT power supply in the CEDGN testplan

**4** Press the play button (shown by the arrow in the figure below) to run the testplan.

The testplan will run tests on each instrument configured in the system topology file and also the instruments specified in step 3. The results of the tests are displayed.

**5** Follow the instructions appearing on the display throughout the test.

# **Installing the Diagnostic Test Fixtures**

Specific diagnostic test fixtures are required to be connected to the Test System Interface based on the messages prompted while running the CEDGN testplan. The DGN testplan only requires external fixture connections for the Pin Matrix Card tests, whereas the CEDGN testplan would most likely require more types of fixtures. The number of fixtures required would depend on the instruments installed in the system.

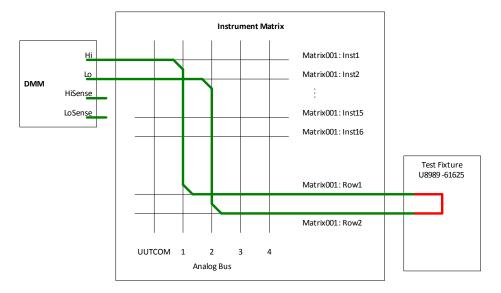

Figure 3-2 shows the U8989-61625 CEDGN Test Fixture connected to the Pin Matrix's slot (1-4 and 6-9). This fixture connection is used to test the connectivity and Pin Matrix functionality. This fixture is the only one required for DGN tests.

Figure 3-2 Installing the U8989-61625 CEDGN Test Fixture

### **3 Running Diagnostics**

Installing the Diagnostic Test Fixtures

Figure 3-3 shows a U8989-61620 CEDGN Test Fixture connected to the SLU Utility slot with a U8989-61625 CEDGN Pin Matrix Cable connected to Slot 21.

This fixture connection is used to test the SLU Utility functionality.

Figure 3-3 Installing the SLU Utility U8989-61620 CEDGN Test Fixture with a U8989-61625 CEDGN Pin Matrix Cable

Figure 3-4 shows a U8989-61621 CEDGN Test Fixture connected to the Load Card Slot with a U8989-61625 CEDGN Pin Matrix Cable connected to Slot 21.

This fixture connection is used to test the SLU Load Card (24-/16-/8-Channel) functionality.

Figure 3-4 Installing the Load Card U8989-61 1 CEDGN Test Fixture with a U8989-61625CEDGN Pin Matrix Cable

### 3 Running Diagnostics

Installing the Diagnostic Test Fixtures

Figure 3-5 shows a U8989-61621 CEDGN Test Fixture connected to the SLU Utility Slot with a U8989-61625 CEDGN Pin Matrix Cable connected to Slot 21.

This fixture connection is used to test the Load Card ISense functionality.

Figure 3-5 Installing the Load Card ISense U8989-61621 CEDGN Test Fixtures with a U8989-61625 CEDGN Pin Matrix Cable

Figure 3-6 shows a U8989-61624 CEDGN Test Fixture connected to the Heavy Duty Load Card with a U8989-61625 CEDGN Pin Matrix Cable connected to Slot 21.

This fixture connection is used to test the Heavy Duty Load Card functionality.

Figure 3-6 Installing the Heavy Duty Load Card U8989-61624 CEDGN

Test Fixture with a U8989-61625 CEDGN Pin Matrix Cable

### 3 Running Diagnostics

Installing the Diagnostic Test Fixtures

Figure 3-7 shows a U8989-61622 CEDGN Test Fixture connected to the 48-Channel Load Card with a U8989-61625 CEDGN Pin Matrix Cable connected to Slot 21.

This fixture connection is used to test the 48-Channel Load Card functionality.

Figure 3-7 Installing the 48-Channel Load Card U8989-61622 CEDGN

Test Fixture with a U8989-61625 CEDGN in Matrix Cable

Figure 3-8 shows a U8989-61623 CEDGN Test Fixture connected to the Instrument Routing Card with a U8989-61625 CEDGN Pin Matrix Cable connected to Slot 21.

This fixture connection is used to test the PXI/PCI Modules functionality.

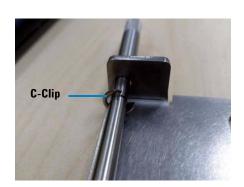

## **Installing the CEDGN fixture kit bracket**

The CEDGN fixture kit bracket is used to secure the DIN connector onto the SLU. It utilizes a thumb screw mechanism to mount the DIN connector onto the SLU. The holes on the mounting plate helps secure the the cables on the fixture kit bracket with the help of cable ties (see Figure 3-9).

Figure 3-9 Overview of the CEDGN Fixture Kit Bracket

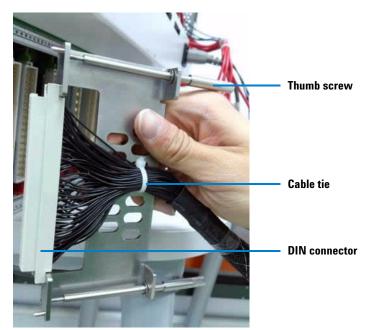

**1** Before connecting the fixture kit bracket, ensure that the C-Clip is in contact with the back of the mounting plate, as shown in Figure 3-10.

Figure 3-10 CEDGN Fixture Kit Bracket Installation Step 1

**2** When connecting the fixture kit bracket to the SLU, ensure that the guiding pin is on the screw hole of the SLU.

Figure 3-11 CEDGN Fixture Kit Bracket Installation Step 2

### 3 Running Diagnostics

Installing the Diagnostic Test Fixtures

**3** Connect the fixture kit bracket completely and ensure that there is no big gap between the SLU and the mounting plate, as shown in Figure 3-12.

Figure 3-12 CEDGN Fixture Kit Bracket Installation Step 3

**4** Secure the fixture kit bracket onto the SLU by tightening the thumb screw.

Figure 3-13 CEDGN Fixture Kit Bracket Installation Step 4

**5** When removing the fixture kit bracket from the SLU, make sure to unscrew the bracket using the thumb screw *completely* until the the C-Clip is in contact with the back of the mounting plate, as shown in Figure 3-14.

Figure 3-14 CEDGN Fixture Kit Bracket Installation Step 5

C-Clip is in contact with the back of the mounting plate.

**6** Pull the fixture kit bracket away from the SLU by pulling the mounting plate, not the fixture cable.

Figure 3-15 CEDGN Fixture Kit Bracket Installation Step 6

### 3 Running Diagnostics

Resolving Test Failures

# **Resolving Test Failures**

Test failures can be caused by improper switch settings on the Diagnostic Test Fixture, improperly specifying the system equipment, or by an actual test system instrument failure.

Before troubleshooting the system equipment, verify that the test fixture switches are properly set and that the test system instrumentation was properly specified. If the problem seems to be the system equipment, swap the instrument and/or the cable between the instrument and the Test System Interface.

Chapter 4 contains detailed descriptions of each test that may help in isolating equipment problems to a particular component.

**DGN Testplan Description and Flow**

# **DGN Testplan Description and Flow**

The DGN testplan comprises basic tests to verify the system internal connections and the basic functions of the instruments.

## Sequence 00: Global Reset

This section include IPC information queries, instrument initializations, and reset. This section also clears the parameter in the symbol tables.

## **Sequence 01: SLU Detection**

This section first checks the presence of the SLU in the system topology file. The SLU must be detected to continue the test. Otherwise, the testplan will stop. This section will list down all the cards present in the SLU from slot 11 to slot 21.

## Sequence 02: PXI and PCI Modules Detection

This section first checks the presence of the PXI and PCI modules in the system topology file and lists down the present modules. This section will also display the modules serial number.

### **Sequence 03: Instrument Matrix Detection**

This section detects the presence of the Instrument Matrix in the system topology file. The Instrument Matrix must be present in the SLU on slot 21 to continue the test. Otherwise, the testplan will stop.

## **Sequence 04: DMM Detection and Test**

This section detects the presence of a DMM in the system topology file. At least one DMM must be present in the system to continue the test. Otherwise, the testplan will stop.

Upon successful detection, the testplan will set the detected DMM(s) to run the self-test sequentially.

## **Sequence 05: Pin Matrix Switching Test**

This section will detect and test all the pin matrix cards present in the system topology file, and it comprises four tests: Instrument Matrix DMM Mux Test, Instrument Matrix DAC Relay Test, Pin Matrix Non-Fixture Test, and Pin Matrix Fixture Test.

- "Instrument Matrix DMM Mux Test" on page 39

- "Instrument Matrix DAC Relay Test" on page 42

- "Pin Matrix Non-Fixture Test" on page 43

- "Pin Matrix Fixture Test" on page 46

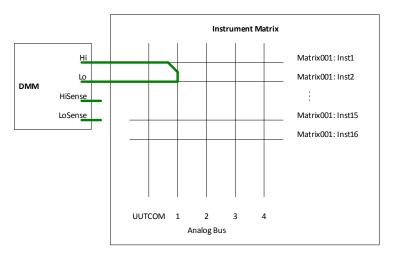

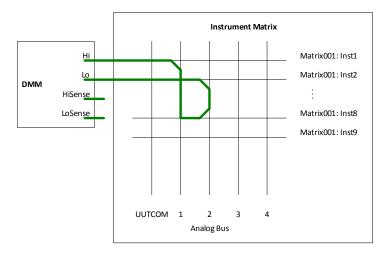

#### Instrument Matrix DMM Mux Test

Instrument Matrix

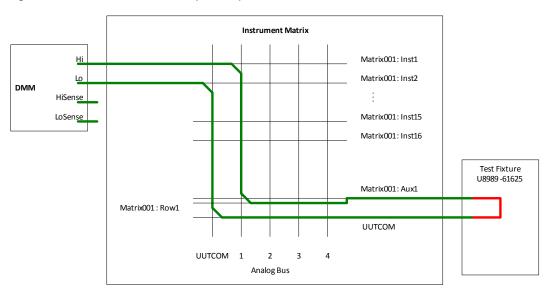

Connect/Disconnect matrix1:Inst1 | matrix1:ABus1 and Inst1 and Inst2 Pin

Test

matrix1:Inst2 | matrix1:ABus1, and measure the path resistance. See Figure 4-1 on page 40. Repeat test for ABus2, ABus3. ABus4. and UUTCommon.

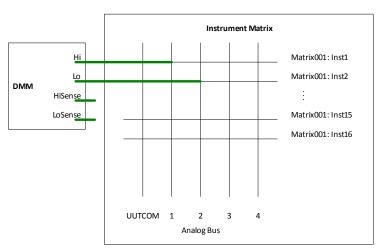

ABUS Short Test

Connect and measure the path resistance between matrix1:Inst1 | ABus1 and matrix1:Inst2 | ABus2. See Figure 4-2 on page 41. There should not be any connection between the two ABUS. Repeat the test for ABus3 and ABus 4.

**DGN Testplan Description and Flow**

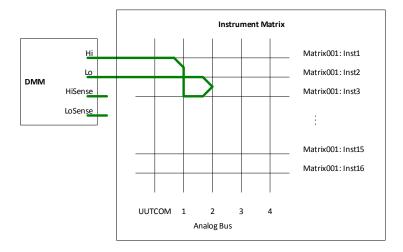

Test

Instrument Matrix Connect/Disconnect matrix1:Inst1 | matrix1:ABus1, Inst3 and Inst4 Pin matrix1:Inst2 | matrix1:ABus2, matrix1:Inst3 | matrix1:ABus1 and matrix1:Inst3 | matrix1:ABus2, and measure the path resistance. See Figure 4-3 on page 41. Repeat the test for ABus3, ABus4, and UUTCommon for both Inst3 and Inst4 Pin.

Instrument Matrix Inst1 and Inst2 Pin Test Figure 4-1

Figure 4-2 ABUS Short Test

Figure 4-3 Instrument Matrix Inst3 and Inst4 Pin Test

**DGN Testplan Description and Flow**

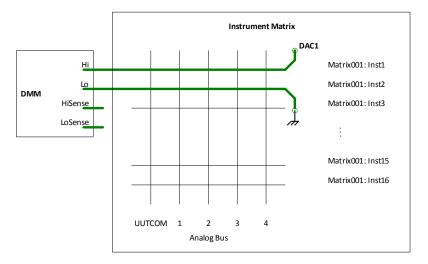

### **Instrument Matrix DAC Relay Test**

Connect/Disconnect the DAC1 relay; output the DAC to 16 V and measure the voltage level. See Figure 4-4. Repeat for the DAC2 relay.

Figure 4-4 Instrument Matrix DAC Relay Test

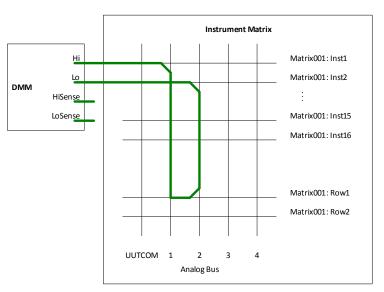

#### **Pin Matrix Non-Fixture Test**

Instrument Rows Open/Short Test

Connect/Disconnect DMM Hi | ABus1 | Matrix001:Inst5 and DMM Lo | ABus2 | Matrix001:Inst5, and measure the path resistance. See Figure 4-5 on page 43. Repeat the test for instrument rows 6 to 40. This test starts from instrument row 5 because instrument rows 1 to 4 are allocated for DMM Hi, Lo, ISrc Hi, and ISrc Lo.

Measurement Test

Connect/Disconnect DMM\_Hi | ABus1 | Matrix001:RowX Rows Open/Short and DMM\_Lo | ABus2 | Matrix001:RowX, and measure the path resistance. See Figure 4-6 on page 44. Repeat the test for the remaining Row Relays.

**Bypass Relays** Test

Open/Close the Pin Matrix Bypass relays, and measure the path resistance. See Figure 4-7 on page 45. The protection

resistor values are 200 Ohms.

Figure 4-5 Instrument Rows Open/Short Test

DGN Testplan Description and Flow

Figure 4-6 Measurement Rows Open/Short Test

Figure 4-7 Bypass Relays Test

**DGN Testplan Description and Flow**

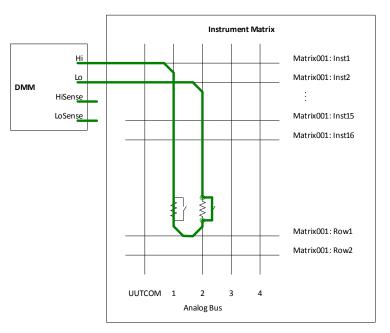

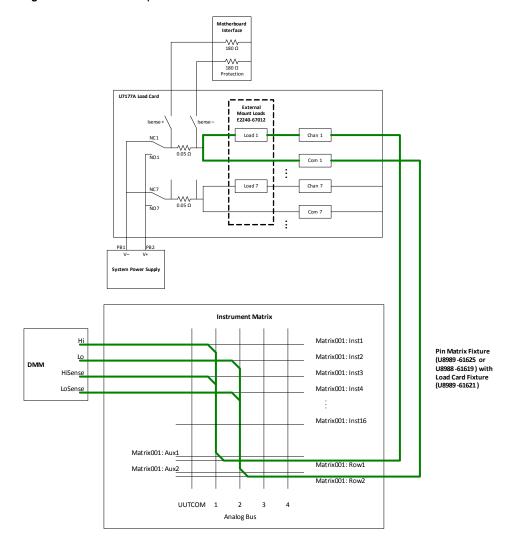

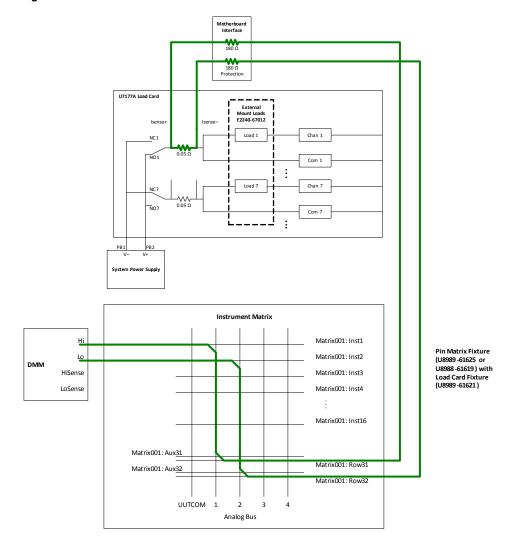

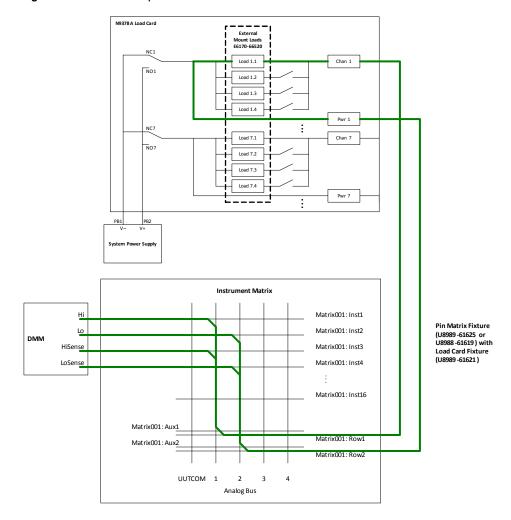

#### **Pin Matrix Fixture Test**

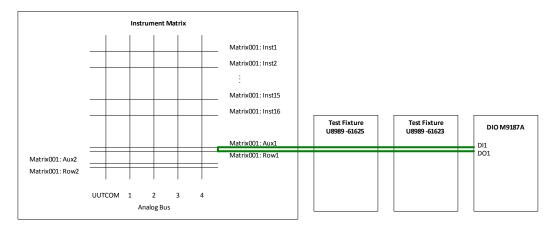

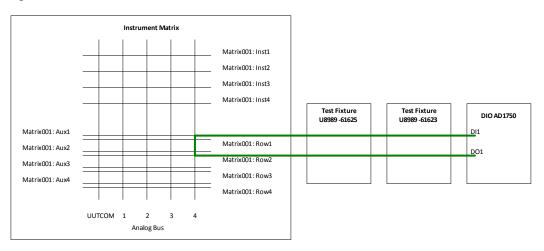

This section requires the external fixture and loopback cable to test the relays open/short between pin matrix ROW and AUX. Figure 4-8 and Figure 4-9 illustrates the internal and external connections for this test.

There are two types of loopback cable, U8989-61625 for the E879xA pin matrix and U8989-61619 for the E878xA pin matrix.

Using the loopback cable, pin matrix Row1 will be shorted to Row2, Row3 to Row 4, and so on. The DMM should measure SHORT when the internal switching is done. See Figure 4-8.

For the AUX test, the loopback cable connects AUX1 via the UUTCOM, similarly for AUX2, AUX3 and so on. The DMM should measure SHORT when the internal switching is done. See Figure 4-9.

Figure 4-8 Pin Matrix Fixture Test (Row Pin)

Figure 4-9 Pin Matrix Fixture Test (Aux Pin)

**CEDGN Testplan Description and Flow**

# **CEDGN Testplan Description and Flow**

## Sequence 00: Global Reset

This sequence includes IPC information queries, instrument initializations, and reset. This sequence also clears the parameter in the symbol tables.

## **Sequence 01: SLU Detection**

This sequence first checks the presence of the SLU in the system topology file. The SLU must be detected to continue the test. Otherwise, the testplan will stop. This sequence will list down all the cards present in the SLU from slot 11 to slot 21.

## **Sequence 02: PXI & PCI Modules Detection**

This sequence first checks the presence of the PXI and PCI modules in the system topology file and list down the present modules.

### **Sequence 03: Instrument Matrix Detection**

This sequence detects the presence of the Instrument Matrix in the system topology file. The Instrument Matrix must be present in the SLU on slot 21 to continue the test. Otherwise, the testplan will stop.

## **Sequence 04: DMM Detection & Test**

This sequence detects the presence of a DMM in the system topology file. At least one DMM must be present in the system to continue the test. Otherwise, the testplan will stop.

Upon successful detection, the testplan will set the detected DMMs to run the self-test sequentially.

## **Sequence 05: Pin Matrix Switching Test**

This sequence will detect and test all the pin matrix cards present in the system topology file. It requires the external fixture and loopback cable to test the relays open/short between pin matrix ROW and AUX. Figure 4-8 and Figure 4-9 illustrates the internal and external connections for this test.

There are two types of loopback cable, U8989-61625 for E879xA pin matrix and U8989-61619 for E878xA pin matrix.

Using the loopback cable, pin matrix Row1 will be shorted to Row2, Row3 to Row 4, and so on. The DMM should measure SHORT when the internal switching is done. See Figure 4-8.

For the AUX test, the loopback cable connects AUX1 via the UUTCOM, similarly for AUX2, AUX3 and so on. The DMM should measure SHORT when the internal switching is done. See Figure 4-9.

## **Sequence 06: SLU Utility Test**

This sequence verifies the connectivity of the SLU Fixture ID, Digital IO, Power Bus Sense, ISense, System Ground Pin, Inst DAC, and VDC Supply (+12 V and -12 V).

**CEDGN Testplan Description and Flow**

## **Sequence 07: PXI Modules Test**

This test sequence will detect all the PXI modules present in the system topology. A test will be performed on the detected PXI modules.

- "DAC M9185A Test" on page 50

- "VI M9168A Test" on page 52

- "DIO M9187A Test" on page 54

- "DAQ M9216A Test" on page 57

- "AD1750 Test" on page 58

- "Softing CAN Test" on page 59

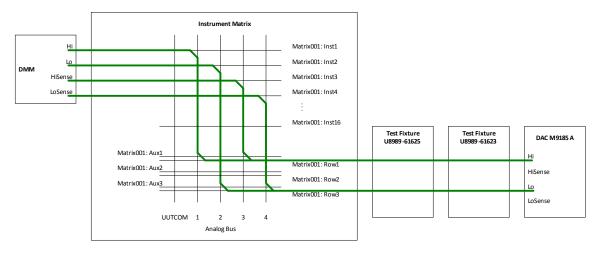

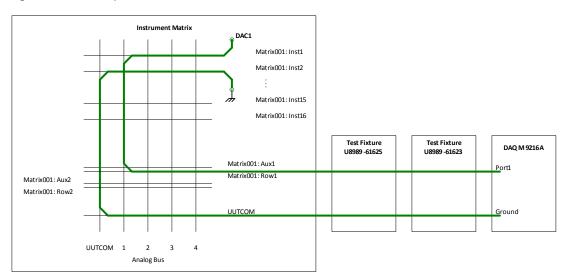

#### DAC M9185A Test

This test verifies the physical connection between the M9185A DAC and the instrument routing card.

Figure 4-10 illustrates the internal switching connection to test DAC Channel 1. Each DAC channel is set to output voltage +16 V) and a DMM will measure the respective channel under test. Note that the DAC sense lines are not connected at this stage. The same test is repeated with the DAC sense lines connected, see Figure 4-11.

Finally, the DAC trigger function is checked with the SLU DAC1 as the trigger source. The DAC output should only be present upon trigger from the SLU DAC1. See Figure 4-12.

This test requires a pin matrix fixture (U8989-61625 or U8989-61619) and a U8989-61623 cable.

Figure 4-11 DAC Output Sense Port Test

**CEDGN Testplan Description and Flow**

Instrument Matrix DAC1 Matrix001: Inst1 Matrix001: Inst2 Matrix001: Inst15 Matrix001: Inst16 Test Fixture Test Fixture DAC M9185 A U8989-61625 U8989 -61623 Matrix001: Aux1 Trigger Matrix001: Row1 Matrix001: Aux2 Ground Matrix001: Row2 Matrix001: Aux3 Matrix001: Row3 UUTCOM 1 Analog Bus

Figure 4-12 DAC Trigger Port Test

### VI M9168A Test

This test verifies the physical connection between the M9186A V/I Source and the instrument matrix.

Table 4-1 shows the output value of the V/I source-under-test in voltage or current mode, low or high range. Figure 4-13 illustrates the internal switching connection for the DMM to measure the voltage and current output from the V/I source-under-test. Figure 4-14 shows the connection of the V/I Interlock through pin matrix.

This test requires a pin matrix fixture (U8989-61625 or U8989-61619) and a U8989-61623 cable.

Table 4-1 V/I source output value

| /I source under test | Output 1 | Output 2 |

|----------------------|----------|----------|

| ow Voltage:          |          |          |

| 0 $\Omega$ path      | –16 V    | 16 V     |

| 10 $\Omega$ path     | –16 V    | 16 V     |

| 100 $\Omega$ Path    | –16 V    | 16 V     |

| 1 kΩ Path            | –16 V    | 16 V     |

| 10 kΩ Path           | –16 V    | 16 V     |

| gh Voltage:          |          |          |

| 0 Ω Path             | –10 V    | 100 V    |

| 100 $\Omega$ Path    | –10 V    | 100 V    |

| ow Current           | −0.02 A  | 0.02 A   |

| igh Current          | -0.2 A   | 0.2 A    |

Figure 4-13 DMM Internal Switching Connection Test

**CEDGN Testplan Description and Flow**

Instrument Matrix Hi Matrix001 · Inst1 Matrix001: Inst2 DMM HiSense Matrix001 · Inst3 LoSense Matrix001: Inst4 Matrix001: Inst13 Matrix001: Inst14 HiSense Matrix001 · Inst15 LoSense Matrix001: Inst16 Test Fixture Test Fixture U8989-61625 U8989-61623 Matrix001: Aux1 Matrix001: Row1 Matrix001: Aux2 Matrix001: Row2 Matrix001: Aux3 Matrix001: Row3 UUTCOM 1 2 Analog Bus

Figure 4-14 VI Voltage and Current Test - VI Interlock Connection

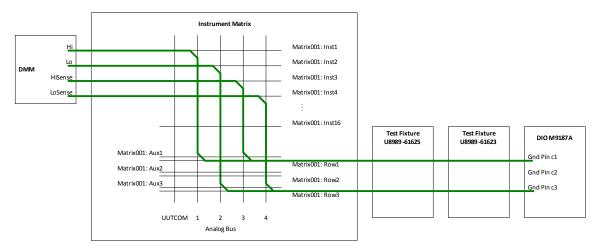

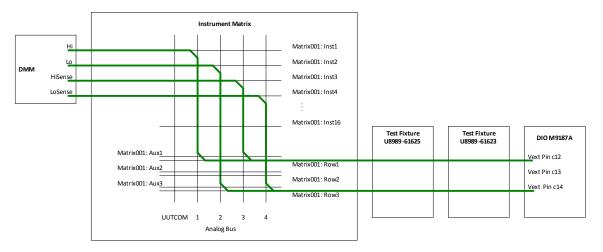

#### DIO M9187A Test

This test verifies the physical connection between the M9187A DIO and the instrument routing card.

This test requires voltage input from the SLU DAC to the DIO Vext to power up the Digital Output Signal.

Figure 4-15 illustrates the internal switching connection of pin matrix AUX to short the Digital Input and Digital Output of the M9187A. The test will conduct by writing data to the specified output ports and reading back the data from the specified input ports.

Figure 4-16 illustrates the internal switching connection to test the Gnd Pin of the M9187A. The DMM will measure each Gnd Pin through the pin matrix and fixtures to ensure that the Gnd Pin connections are connected.

Figure 4-17 illustrates the internal switching connection to test the Vext Pin of the M9187A. The DMM will measure each Vext Pin through the pin matrix and fixtures to ensure that the Vext Pin connections are connected.

This test requires pin a matrix fixture (U8989-61625 or U8989-61619) and a U8989-61623 cable.

**CEDGN Testplan Description and Flow**

Figure 4-16 DIO GND Test

Figure 4-17 DIO Vex Test

#### DAQ M9216A Test

This test verifies the physical connection between the M9216A HV-DAQ and the system ICA.

SLU DAC1 is set to output voltage and the HV-DAQ will measure the voltage. Figure 4-18 illustrates the internal and external switching connections to test the basic functions of the HV-DAQ.

The CEDGN test kit provides the loopback between the HV-DAQ and its respective AUX, see Figure 4-19.

Both tests require a pin matrix fixture (U8989-61625 or U8989-61619) and a U8989-61623 cable.

Figure 4-18 DAQ Input Port Test

**CEDGN Testplan Description and Flow**

Instrument Matrix Matrix001: Inst1 Matrix001: Inst2 Matrix001: Inst15 Matrix001: Inst16 Test Fixture Test Fixture DAQ M 9216A U8989 -61625 U8989 -61623 Matrix001 · Aux1 Matrix001: Row1 Matrix001: Aux2 Matrix001: Row2 Matrix001: Aux3 Aux11 Matrix001: Row3 Matrix001 · Aux30 Port3 Matrix001: Row30 UUTCOM Ground UUTCOM 1 2 Analog Bus

Figure 4-19 DAQ Aux Port Test

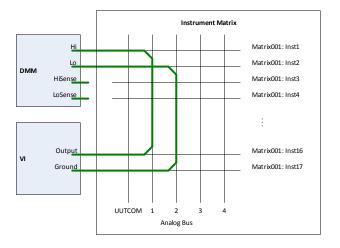

# **Sequence 08: PCI Modules Test**

#### AD1750 Test

This test verifies the physical connection between the PCI 1750 DIO card and the instrument routing card by writing digital data to the specified output ports, and reading back the data from the specified input ports.

Figure 4-20 illustrates the internal switching connection of pin matrix AUX and Row to short the Digital Input and Digital Output of the AD1750.

This test requires a pin matrix fixture (U8989-61625 or U8989-61619) and a U8989-61623 cable.

Figure 4-20 AD1750 Test

### **Softing CAN Test**

This test verifies the physical connections between the Softing CAN card and the instrument routing card through a loopback test. Specific data bytes are sent and read back from the serial port under test.

Figure 4-21 illustrates the internal switching connection of pin matrix AUX to short Channel 1 and Channel 2 of Softing CAN.

This test requires a pin matrix fixture (U8989-61625 or U8989-61619) and a U8989-61623 cable.

**CEDGN Testplan Description and Flow**

Instrument Matrix Matrix001: Inst1 Matrix001: Inst2 Matrix001: Inst3 Matrix001: Inst4 **Test Fixture** Test Fixture Softing CAN U8989 -61623 Matrix001: Aux1 CH1.CAN\_H Matrix001: Row1 Matrix001: Aux2 CH2.CAN\_H Matrix001: Row2 Matrix001: Aux3 CH1.CAN\_L Matrix001: Row3 Matrix001: Aux4 CH2.CAN\_L Matrix001: Row4 CH1.GND CH2.GND UUTCOM UUTCOM 1 2 Analog Bus

Figure 4-21 Softing CAN Test

# **Sequence 09: Load Card Test**

- "E6175A Load Card Test" on page 61

- "E6176A Load Card Test" on page 65

- "E6177A Load Card Test" on page 69

- "U7177A Load Card test" on page 72

- "N9377A Load Card Test" on page 76

- "N9378A Load Card Test" on page 80

- "U7179A Load Card Test" on page 83

- "N9379A Load Card Test" on page 87

- 1 0

- "E6178B Load Card Test" on page 89

- "U7178A Load Card Test" on page 92

#### **E6175A Load Card Test**

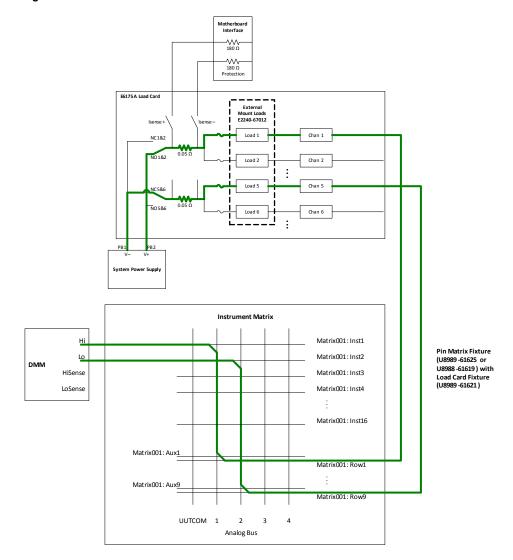

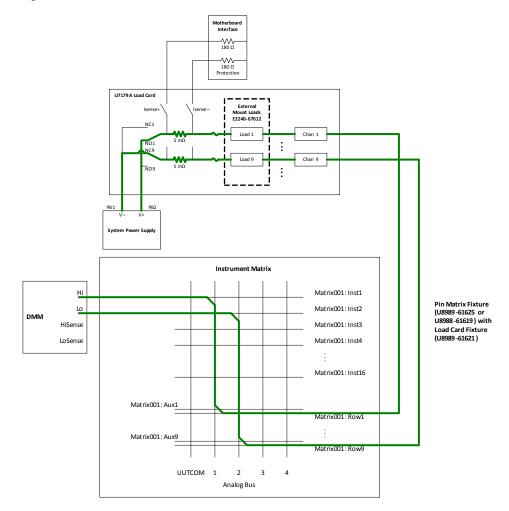

This test verifies the physical connections between the E6175A Load Card, power supply, and system ICA.

This test consists of an unpowered load card test, a powered load card test, and a current sense test.

Load relay switches are tested in the unpowered load card test. In this test, an external mount load with an effective load resistance of 28.86  $\Omega$  (E2240-67012) is mounted on the E6175A J1 connector. Use a DMM to measure the resistance path between channel 1 and channel 2, similarly between channel 3 and channel 4, and so on until channel 7 and channel 8. Figure 4-22 illustrates the resistance measurement path for the E6175A unpowered load card test.

The powered load card test requires the a DUT power supply. If no DUT power supply is present, this test will be skipped. The DUT power supply is set to output +5 V (current limit at 0.1 A) and the DMM will measure the voltage via the load card channels, NC, and NO. Figure 4-23 illustrates the measurement path for the E6175A powered load card test.

Figure 4-24 illustrates the internal and external switching connections to test the E6175A current sense. This test measures the resistance of the current sense path via the SLU backplane.

Motherboard Interface 180 Ω Protection E6175 A Load Card External Mount Loads E2240-67012 Chan 1 Load 1 NC1&2 NO 1&2 Chan 2 Load 5 Chan 5 0.05 Ω NO5&6 PB1 PB2 Instrument Matrix Matrix001: Inst1 Pin Matrix Fixture Matrix001: Inst2 (U8989-61625 or DMM U8988 -61619) with HiSense Matrix001: Inst3 Load Card Fixture (U8989 -61621) LoSense Matrix001: Inst4 Matrix001: Inst16 Matrix001: Aux1 Matrix001: Row1 Matrix001: Aux2 Matrix001: Row2 Matrix001: Aux3 Matrix001: Row3 UUTCOM 1 Analog Bus

Figure 4-22 E6175A Unpowered Load Card Test

Figure 4-23 E6175A Powered Load Card Test

Motherboard Interface E6175 A Load Card External Mount Loads E2240-67012 Load 1 Chan 1 NO1&2 Chan 2 Load 5 Chan 5 0.05 Ω NO5&6 PB1 PB2 Instrument Matrix Matrix001: Inst1 Pin Matrix Fixture Matrix001: Inst2 (U8989-61625 or DMM U8988 -61619) with Matrix001: Inst3 HiSense Load Card Fixture (U8989 -61621) LoSense Matrix001: Inst4 Matrix001: Inst16 Matrix001: Aux31 Matrix001: Row31 Matrix001: Aux32 Matrix001: Row32 UUTCOM 1 2 Analog Bus

Figure 4-24 E6175A Current Sense Test

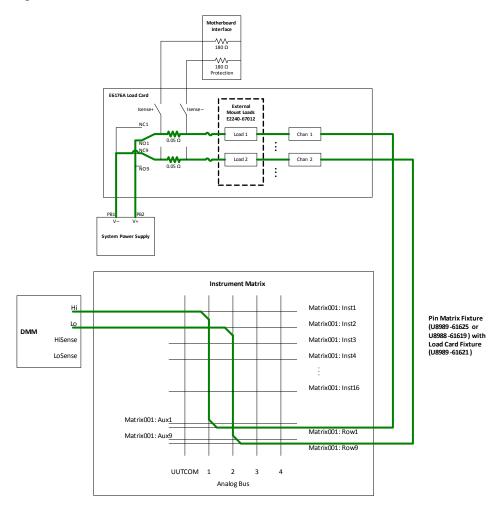

#### E6176A Load Card Test

This test sequence verifies the physical connection between the E6176A Load Card, power supply, and system ICA.

This test consists of an unpowered load card test, a powered load card test, and a current sense test.

Load relay switches are tested in the unpowered load card test. In this test, an external mount load with an effective load resistance of 28.86  $\Omega$  (E2240-67012) is mounted on the E6176A J1 and J2 connector. Use a DMM to measure the resistance path between channel 1 and channel 9 via the load card channels, NC and NO, similarly for channel 2 and channel 10, and so on until channel 8 and channel 16. Figure 4-25 illustrates the resistance measurement path for the E6176A unpowered load card test.

The powered load card test requires a DUT power supply. If no DUT power supply is present, this test will be skipped. The DUT power supply is set to output +5 V (current limit at 0.1 A) and the DMM will measure the voltage via the load card channels, NC and NO. Figure 4-26 illustrates the measurement path for the E6176A powered load card test.

Figure 4-27 illustrates the internal and external switching connections to test the E6176A current sense. This test measures the resistance of the current sense path via the SLU backplane.

Motherboard Interface 180 Ω Protection E6176A Load Card External Mount Loads Chan 1 NO1 NO9 Instrument Matrix Matrix001: Inst1 Pin Matrix Fixture (U8989 -61625 or Matrix001: Inst2 DMM U8988 -61619) with Matrix001: Inst3 HiSense Load Card Fixture (U8989-61621) LoSense Matrix001: Inst4 Matrix001: Inst16 Matrix001: Aux1 Matrix001: Row1 Matrix001: Aux2 Matrix001: Row2 UUTCOM 1 2 3 Analog Bus

Figure 4-25 E6176A Unpowered Load Card Test

Figure 4-26 E6176A Powered Load Card Test

Motherboard Interface 180 Ω Protection E6176A Load Card External Mount Loads E2240-67012 Load 1 Chan 1 NO1 NC9 Chan 2 System Power Supply Instrument Matrix Hi Matrix001: Inst1 Pin Matrix Fixture Matrix001: Inst2 (U8989-61625 or DMM U8988 -61619) with HiSense Matrix001: Inst3 Load Card Fixture (U8989 -61621) LoSense Matrix001: Inst4 Matrix001: Inst16 Matrix001: Aux31 Matrix001: Row31 Matrix001: Aux32 Matrix001: Row32 UUTCOM 1 2 Analog Bus

Figure 4-27 E6176A Current Sense Test

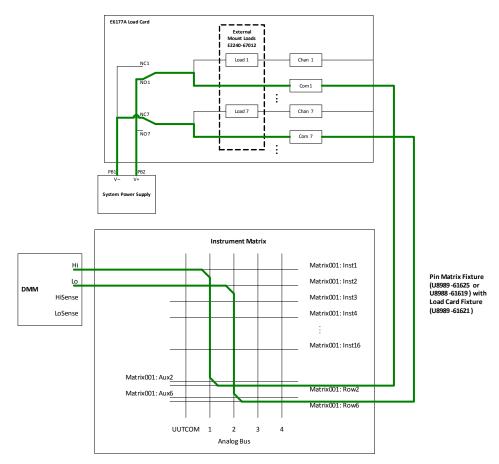

### **E6177A Load Card Test**

This test verifies the physical connection between the E6177A Load Card, power supply, and system ICA.

This test consists of an unpowered load card test and a powered load card test.

The load relay switches are tested in the unpowered load card test. In this test, an external mount load with an effective load resistance of 86.6  $\Omega$  (E2240-67012) is mounted on the E6177A J1 connector. Use a DMM to measure the resistance path between channel 1 and common 1 (or channel power 1), similarly for between channel 2 and common 2, and so on until between channel 24 and common 24. Figure 4-28 illustrates the resistance measurement path for the E6177A unpowered load card test.

The powered load card test requires a DUT power supply. If no DUT power supply is present, this test will be skipped. The DUT power supply is set to output +5 V (current limit at 0.1 A) and the DMM will measure the voltage via the load card channels, NC and NO. Figure 4-29 illustrates the measurement path for the E6177A powered load card test.

E6177A Load Card External NO1 Com 1 Chan 7 Load 7 NO7 Com 7 Instrument Matrix Hi Matrix001: Inst1 Pin Matrix Fixture Matrix001: Inst2 (U8989 -61625 or U8988 -61619 ) with DMM Matrix001: Inst3 HiSense Load Card Fixture (U8989 -61621) Matrix001: Inst4 Matrix001: Inst16 Matrix001: Aux1 Matrix001: Row1 Matrix001: Aux2 Matrix001: Row2 UUTCOM 1 2 3 Analog Bus

Figure 4-28 E6177A Unpowered Load Card Test

Figure 4-29 E6177A Powered Load Card Test

**CEDGN Testplan Description and Flow**

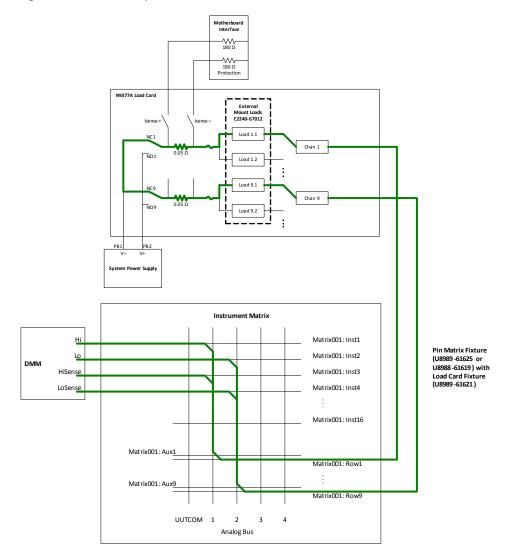

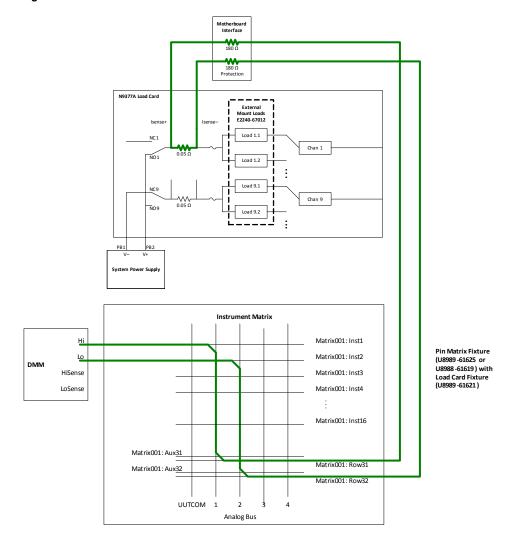

#### **U7177A Load Card test**

This test verifies the physical connection between the U7177A Load Card, power supply, and system ICA.

This test consists of an unpowered load card test, a powered load card test, and a current sense test.

The load relay switches are tested in the unpowered load card test. In this test, an external mount load with an effective load resistance of 86.6  $\Omega$  (E2240-67012) is mounted on the U7177A J1 connector. Use a DMM to measure the resistance path between channel 1 and common 1, similarly between channel 2 and common 2, and so on until between channel 24 and common 24. Figure 4-30 illustrates the resistance measurement path for the U7177A unpowered load card test.

The powered load card test requires a DUT power supply. If no DUT power supply is present, this test will be skipped. The DUT power supply is set to output +5 V (current limit at 0.1 A) and the DMM will measure the voltage via the load card channels, NC and NO. Figure 4-31 illustrates the measurement path for the U7177A powered load card test.

Figure 4-32 illustrates the internal and external switching connections to test the U7177A current sense. This test measures the resistance of the current sense path via the SLU backplane.

Figure 4-30 U7177A Unpowered Load Card Test

Motherboard Interface 180 Ω Protection U7177A Load Card External Mount Loads E2240-67012 Load 1 Chan 1 Load 7 Chan 7 NO 7 Instrument Matrix Matrix001: Inst1 Pin Matrix Fixture Matrix001: Inst2 (U8989-61625 or DMM U8988 -61619) with Matrix001: Inst3 HiSense Load Card Fixture (U8989 -61621) LoSense Matrix001: Inst4 Matrix001: Inst16 Matrix001: Aux2 Matrix001: Row2 Matrix001: Aux6 Matrix001: Row6 UUTCOM 1 Analog Bus

Figure 4-31 U7177A Powered Load Card Test

Figure 4-32 U7177A Current Sense Test

**CEDGN Testplan Description and Flow**

#### N9377A Load Card Test

This test verifies the physical connection between the N9377A Load Card, power supply, and system ICA.

This test consists of an unpowered load card test, a powered load card test, and a current sense test.

The load relay switches are tested in the unpowered load card test. In this test, the external mount load, E2240-67012 is mounted on the N9377A, J1 and J2 connector. The effective load resistance on load X.1 is 28.86  $\Omega$  and on load X.2 is short (0  $\Omega$ ). X represents the channel number from 1 to 16. Use a DMM to measure the resistance path between channel 1 and channel 9 via load1.1 and NC. The expected reading is 60.6588  $\Omega$  Next, measure the short (0  $\Omega$ ) between channel 1 and channel via load1.2 and NO. This test is repeated until channel 8 and channel 16. Figure 4-33 illustrates the resistance measurement path for the N9377A unpowered load card test.

The powered load card test requires a DUT power supply. If no DUT power supply is present, this test will be skipped. The DUT power supply is set to output +5 V (current limit at 0.1 A) and the DMM will measure the voltage via the load card channels, NC and NO. Figure 4-34 illustrates the measurement path for the N9377A powered load card test.

Figure 4-35 illustrates the internal and external switching connections to test the N9377A current sense. This test measures the resistance of the current sense path via the SLU backplane.

Figure 4-33 N9377A Unpowered Load Card Test

Motherboard Interface 180 Ω Protection N9377A Load Card External Mount Loads E2240-67012 Chan 1 Load 1.2 Load 9.1 Chan 9 NO9 Load 9.2 Instrument Matrix Matrix001: Inst1 Pin Matrix Fixture Matrix001: Inst2 (U8989-61625 or DMM U8988 -61619) with Matrix001: Inst3 HiSense Load Card Fixture (U8989 -61621) LoSense Matrix001: Inst4 Matrix001: Inst16 Matrix001: Aux1 Matrix001: Row1 Matrix001: Aux9 Matrix001: Row9 UUTCOM 1 Analog Bus

Figure 4-34 N9377A Powered Load Card Test

Figure 4-35 N9377A Current Sense Test

**CEDGN Testplan Description and Flow**

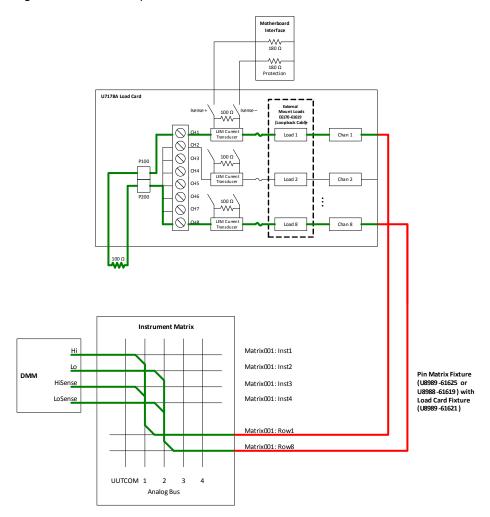

#### N9378A Load Card Test

This test verifies the physical connections between the N9378A Load Card, power supply, and system ICA.

This test consists of an unpowered load card test and a powered load card test.

The load relay switches are tested in the unpowered load card test. In this test, an external mount load with an effective load resistance of 820  $\Omega$  (E6170-66520) is mounted on the N9378A. Use a DMM to measure the resistance path between channel 1 and Pwr 1 via Load1.1. This test is repeated until channel 24 with loadX.1, loadX.2, loadX.3 and loadX.4. X represents the channel number from 1 to 24.

Figure 4-36 illustrates the resistance measurement path for the N9378A unpowered load card test.

The powered load card test requires a DUT power supply. If no DUT power supply is present, this test will be skipped. There are four power groups for this test, Pwr 1-6, Pwr 7-12, Pwr 13-18, and Pwr 19-24. The DUT power supply is set to output +5 V (current limit at 0.1 A) and the DMM will measure the voltage via the load card power groups, NC and NO. For example, Pwr 1-6 connects to NC, while Pwr 7-12 connects to NO and the DMM measures the voltage. The test then repeats with Pwr 1-6 connected to NO and Pwr 7-12 connected to NC. This sequence is repeated until all load channels are tested. Figure 4-37 illustrates the measurement path for the N9378A powered load card test.

Figure 4-36 N9378A Unpowered Load Card Test

N9378 A Load Card External Mount Loads E6170-66520 Load 1.1 Chan 1 Load 1.3 Load 1.4 Pwr 1 Chan 7 NO7 Load 7.2 Load 7.3 Load 7.4 Instrument Matrix Hi Matrix001: Inst1 Pin Matrix Fixture Matrix001: Inst2 (U8989 -61625 or U8988 -61619) with DMM Matrix001: Inst3 HiSense Load Card Fixture (U8989 -61621) LoSense Matrix001: Inst4 Matrix001: Inst16 Matrix001: Aux2 Matrix001: Row2 Matrix001: Aux6 Matrix001: Row6 UUTCOM 1 Analog Bus

Figure 4-37 N9378A Powered Load Card Test

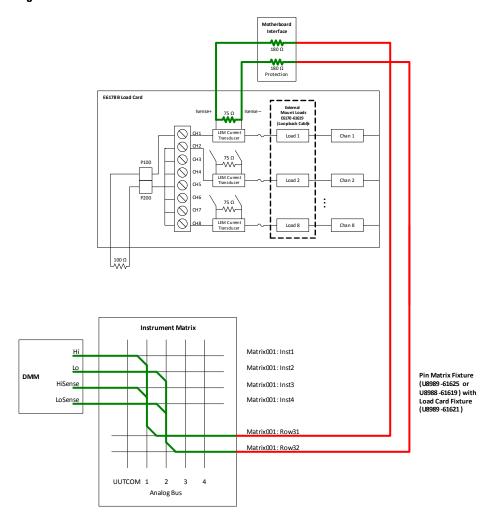

#### **U7179A Load Card Test**

This test verifies the physical connections between the U7179A Load Card, power supply, and system ICA.

This test consists of an unpowered load card test, a powered load card test, and a current sense test.

The load relay switches are tested in the unpowered load card test. In this test, an external mount load with an effective load resistance of 28.86  $\Omega$  (E2240-67012) is mounted on the U7179A, J1 and J2 connector. Use a DMM to measure the resistance path between channel 1 and channel 9 via NC and NO, similarly for channel 2 and channel 10, and so on until channel 8 and channel 16. Figure 4-38 illustrates the resistance measurement path for the U7179A unpowered load card test.

The powered load card test requires a DUT power supply. If no DUT power supply is present, this test will be skipped. The DUT power supply is set to output +5 V (current limit at 0.1 A) and the DMM will measure the voltage via the load card channels, NC and NO. Figure 4-39 illustrates the measurement path for the U7179A powered load card test.

Figure 4-40 illustrates the internal and external switching connections to test the U7179A current sense. This test measures the resistance of the current sense path via the SLU backplane.

Motherboard Interface 180 Ω Protection U7179 A Load Card External Mount Loads Chan 1 NO1 NO9 System Power Supply Instrument Matrix Hi Matrix001: Inst1 Pin Matrix Fixture Matrix001: Inst2 (U8989-61625 or DMM U8988 -61619) with HiSense Matrix001: Inst3 Load Card Fixture (U8989-61621) Matrix001: Inst4 Matrix001: Inst16 Matrix00X: Aux1 Matrix00X: Row1 Matrix00X: Aux9 Matrix00X: Row9 UUTCOM 1 2 3 Analog Bus

Figure 4-38 U7179A Unpowered Load Card Test

Figure 4-39 U7179A Powered Load Card Test

Motherboard Interface U7179A Load Card External Mount Loads E2240-67012 Load 1 Chan 1 NO1 NO9 PB1 PB2 System Power Supply Instrument Matrix Hi Matrix001: Inst1 Pin Matrix Fixture Matrix001: Inst2 (U8989-61625 or DMM U8988 -61619) with HiSense Matrix001: Inst3 Load Card Fixture (U8989-61621) Matrix001: Inst4 LoSense Matrix001: Inst16 Matrix001: Aux31 Matrix001: Row31 Matrix001: Aux32 Matrix001: Row32 UUTCOM 1 Analog Bus

Figure 4-40 U7179A Current Sense Test

#### **N9379A Load Card Test**

This test verifies the physical connections between the N9379A Load Card, power supply, and system ICA.

This test sequence consists of an unpowered load card test, and a powered load card test.

The load relay switches are tested in the unpowered load card test. In this test, an external mount load with an effective load resistance of 820  $\Omega$  (E6170-66520) is mounted on the N9379A. Use a DMM to measure the resistance path between channel X and com X via loadX.1 follow by loadX.2. X represents the channel number from 1 to 48. Figure 4-41 illustrates the resistance measurement path for the N9379A unpowered load card test.