### **FEATURES**

- On-Chip Latches for Both DACs

- +5 V to +15 V Operation

- DACs Matched to 1%

- Four Quadrant Multiplication

- 15 V CMOS Compatible

- See MP7529A or MP7529B for Improved Performance

### **APPLICATIONS**

- Microprocessor Controlled Gain Circuits

- Microprocessor Controlled Attenuator Circuits

- Microprocessor Controlled Function Generation

- Precision AGC Circuits

- Bus Structured Instruments

#### **GENERAL DESCRIPTION**

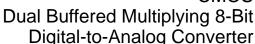

The MP7528 is a dual 8-bit digital/analog converter designed using EXAR's proven decoded DAC architecture. It features excellent DAC-to-DAC matching and guaranteed monotonicity.

Separate on-chip latches are provided for each DAC to allow easy microprocessor interface.

Data is transferred into either of the two DAC data latches via a common 8-bit TTL/CMOS compatible input port. Control input

DACA/DACB determines which DAC is to be loaded. The MP7528's load cycle is similar to the write cycle of a random access memory and the device is bus compatible with most 8-bit microprocessors.

The device operates from a +5V to +15V power supply with only 2 mA of current (maximum).

Both DACs offer excellent four quadrant multiplication characteristics with a separate reference input and feedback resistor for each DAC.

### SIMPLIFIED BLOCK AND TIMING DIAGRAM

## ORDERING INFORMATION

| Package<br>Type | Temperature<br>Range | Part No.  | INL<br>(LSB) | DNL<br>(LSB) | Gain Error<br>(LSB) |

|-----------------|----------------------|-----------|--------------|--------------|---------------------|

| Plastic Dip     | –40 to +85°C         | MP7528JN  | <u>+</u> 1   | <u>+</u> 1   | <u>+</u> 6          |

| Plastic Dip     | –40 to +85°C         | MP7528KN  | <u>+</u> 1/2 | <u>+</u> 1   | <u>+</u> 4          |

| Plastic Dip     | –40 to +85°C         | MP7528LN  | <u>+</u> 1/4 | <u>+</u> 1   | <u>+</u> 3          |

| SOIC            | –40 to +85°C         | MP7528JS  | <u>+</u> 1   | <u>+</u> 1   | <u>+</u> 6          |

| SOIC            | –40 to +85°C         | MP7528KS  | <u>+</u> 1/2 | <u>+</u> 1   | <u>+</u> 4          |

| SOIC            | –40 to +85°C         | MP7528LS  | <u>+</u> 1/4 | <u>+</u> 1   | <u>+</u> 3          |

| PLCC            | -40 to +85°C         | MP7528JP  | <u>+</u> 1   | <u>+</u> 1   | <u>+</u> 6          |

| PLCC            | –40 to +85°C         | MP7528KP  | <u>+</u> 1/2 | <u>+</u> 1   | <u>+</u> 4          |

| PLCC            | –40 to +85°C         | MP7528LP  | <u>+</u> 1/4 | <u>+</u> 1   | <u>+</u> 3          |

| Ceramic Dip     | –40 to +85°C         | MP7528AD  | <u>+</u> 1   | <u>+</u> 1   | <u>+</u> 6          |

| Ceramic Dip     | –40 to +85°C         | MP7528BD  | <u>+</u> 1/2 | <u>+</u> 1   | <u>+</u> 4          |

| Ceramic Dip     | –40 to +85°C         | MP7528CD  | <u>+</u> 1/4 | <u>+</u> 1   | <u>+</u> 3          |

| Ceramic Dip     | −55 to +125°C        | MP7528SD* | <u>+</u> 1   | <u>+</u> 1   | <u>+</u> 6          |

| Ceramic Dip     | −55 to +125°C        | MP7528TD* | <u>+</u> 1/2 | <u>+</u> 1   | <u>+</u> 4          |

<sup>\*</sup>Contact factory for non-compliant military processing

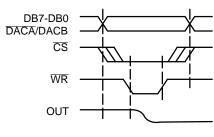

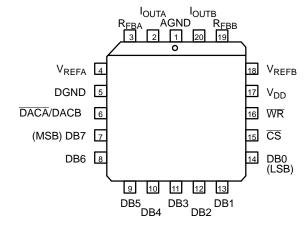

### **PIN CONFIGURATIONS**

See Packaging Section for Package Dimensions

20 Pin CDIP, PDIP (0.300") D20, N20 20 Pin SOIC (Jedec, 0.300") S20

13

12

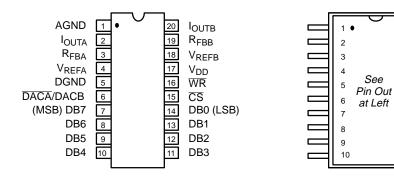

# PIN CONFIGURATIONS (CONT'D)

20 Pin PLCC P20

## **PIN OUT DEFINITIONS**

| PIN NO. | NAME              | DESCRIPTION                 |

|---------|-------------------|-----------------------------|

| 1       | AGND              | Analog Ground               |

| 2       | I <sub>OUTA</sub> | Current Out DAC A           |

| 3       | R <sub>FBA</sub>  | Feedback Resistor for DAC A |

| 4       | $V_{REFA}$        | Reference Input for DAC A   |

| 5       | DGND              | Digital Ground              |

| 6       | DAC A/<br>DAC B   | DAC Select                  |

| 7       | DB7 (MSB)         | Data Input Bit 7            |

| 8       | DB6               | Data Input Bit 6            |

| 9       | DB5               | Data Input Bit 5            |

| 10      | DB4               | Data Input Bit 4            |

| 11      | DB3               | Data Input Bit 3            |

| 12      | DB2               | Data Input Bit 2            |

| 13      | DB1               | Data Input Bit 1            |

| 14      | DB0 (LSB)         | Data Input Bit 0            |

| 15      | CS                | Chip Select                 |

| 16      | WR                | Write                       |

| 17      | $V_{DD}$          | Power Supply                |

| 18      | $V_{REFB}$        | Reference Input for DAC B   |

| 19      | R <sub>FBB</sub>  | Feedback Resistor for DAC B |

| 20      | I <sub>OUTB</sub> | Current Out DAC B           |

# **ELECTRICAL CHARACTERISTICS**(VDD = + 5 V, VREF = +10 V unless otherwise noted)

| Parameter                                                                                        | Symbol                                          | Min    | 25°C<br>Typ Max                        | Tmin t<br>Min | o Tmax<br>Max      | Units                 | Test Conditions/Comments                                                                                                  |

|--------------------------------------------------------------------------------------------------|-------------------------------------------------|--------|----------------------------------------|---------------|--------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE <sup>1</sup>                                                                  |                                                 |        |                                        |               |                    |                       |                                                                                                                           |

| Resolution (All Grades)                                                                          | N                                               | 8      |                                        | 8             |                    |                       | Bits                                                                                                                      |

| Integral Non-Linearity (Relative Accuracy) J, A, S K, B, T L, C                                  | INL                                             |        | ±1<br>±1/2<br><u>+</u> 1/4             |               | ±1<br>±1/2<br>±1/4 | LSB                   | End Point Linearity Spec.                                                                                                 |

| Monotonicity                                                                                     |                                                 |        |                                        |               |                    |                       | Guaranteed over temp                                                                                                      |

| Differential Non-Linearity J, A, S K, B, T L, C                                                  | DNL                                             |        | <u>+</u> 1                             |               | <u>+</u> 1         | LSB                   | All grades monotonic over full temperature range.                                                                         |

| Gain Error<br>J, A, S<br>K, B, T<br>L, C                                                         | GE                                              |        | <u>+</u> 4<br><u>+</u> 2<br><u>+</u> 1 |               | ±6<br>±4<br>±3     | LSB                   | Using Internal R <sub>FB</sub><br>Digital Inputs = V <sub>INH</sub>                                                       |

| Gain Temperature Coefficient <sup>2</sup>                                                        | $TC_GE$                                         |        |                                        |               | <u>+</u> 70        | ppm/°C                | $\Delta$ Gain/ $\Delta$ Temperature                                                                                       |

| Power Supply Rejection Ratio                                                                     | PSRR                                            |        | <u>+</u> 200                           |               | <u>+</u> 400       | ppm/%                 | $ \Delta Gain/\Delta V_{DD}  \Delta V_{DD} = \pm 5\%$<br>Digital Inputs = $V_{INH}$                                       |

| Output Leakage Current (Pin 2)                                                                   | I <sub>OUT1</sub>                               |        | <u>+</u> 50nA                          |               | <u>+</u> 400nA     | nA                    | Digital Inputs = V <sub>INL</sub>                                                                                         |

| Output Leakage Current (Pin 20)                                                                  | I <sub>OUT2</sub>                               |        | <u>+</u> 50nA                          |               | <u>+</u> 400nA     | nA                    | Digital Inputs = V <sub>INH</sub>                                                                                         |

| Input Resistance                                                                                 | V <sub>REFA</sub><br>V <sub>REFB</sub>          | 8<br>8 | 15<br>15                               | 8<br>8        | 15<br>15           | kΩ<br>kΩ              | TC = $-300$ ppm/°C max.<br>11 kΩ typical                                                                                  |

| Input Resistance Matching                                                                        |                                                 |        | <u>+</u> 1                             |               | <u>+</u> 1         | %                     |                                                                                                                           |

| DYNAMIC PERFORMANCE <sup>2</sup>                                                                 |                                                 |        |                                        |               |                    |                       | $R_L=100\Omega$ , $C_L=13pF$                                                                                              |

| Harmonic Distortion<br>Digital Crosstalk                                                         | THD<br>Q                                        |        | -85<br>30                              |               |                    | dB<br>nVs             | V <sub>IN</sub> = 6V <sub>RMS</sub> @ 1 KHz<br>Measured for code transition<br>Z <sub>S</sub> to F <sub>SS</sub>          |

| Channel-to-Channel Isolation AC Feedthrough at I <sub>OUT1</sub> Glitch Energy Propagation Delay | CCI<br>F <sub>T</sub><br>Egl<br>t <sub>PD</sub> |        | –77<br>–70<br>160<br>220               | -65<br>270    |                    | dB<br>dB<br>nVs<br>ns | $V_{REF}$ = 10kHz, 20 Vp-p, sinewave $Z_S$ to $F_S$ Input Change From digital input to 90% of final analog output current |

# **ELECTRICAL CHARACTERISTICS (CONT'D)**

| Parameter                                                                                                                                                                                                     | Symbol                                                                                                          | Min                                       | 25°C<br>Typ Max        | Tmin to                                   | o Tmax<br>Max                  | Units                      | Test Conditions/Comments                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------|-------------------------------------------|--------------------------------|----------------------------|------------------------------------------------------------------------------------------|

| DIGITAL INPUTS <sup>3</sup>                                                                                                                                                                                   | -                                                                                                               |                                           |                        |                                           |                                |                            |                                                                                          |

| Logical "1" Voltage<br>Logical "0" Voltage<br>Input Leakage Current<br>Input Capacitance <sup>2</sup><br>Data<br>Control                                                                                      | V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>LKG</sub><br>C <sub>IN</sub><br>C <sub>IN</sub>                    | 2.4                                       | 0.8<br>±1<br>10<br>15  | 2.4                                       | 0.8<br><u>+</u> 10<br>10<br>15 | V<br>V<br>μA<br>pF<br>pF   |                                                                                          |

| ANALOG OUTPUTS <sup>2</sup>                                                                                                                                                                                   |                                                                                                                 |                                           |                        |                                           |                                |                            |                                                                                          |

| Output Capacitance                                                                                                                                                                                            | C <sub>OUTA</sub> C <sub>OUTA</sub> C <sub>OUTB</sub> C <sub>OUTB</sub>                                         |                                           | 120<br>50<br>120<br>50 |                                           | 120<br>50<br>120<br>50         | pF<br>pF<br>pF<br>pF       | DAC Inputs all 1's<br>DAC Inputs all 0's<br>DAC Inputs all 1's<br>DAC Inputs all 0's     |

| POWER SUPPLY <sup>5</sup>                                                                                                                                                                                     |                                                                                                                 |                                           |                        |                                           |                                |                            |                                                                                          |

| Functional Voltage Range <sup>2</sup><br>Supply Current                                                                                                                                                       | V <sub>DD</sub><br>I <sub>DD</sub>                                                                              | 4.5                                       | 15.75<br>2<br>2        | 4.5                                       | 15.75<br>2<br>2                | V<br>mA<br>mA              | All digital inputs = 0 V or all = 5 V<br>All digital inputs = $V_{IL}$ or all = $V_{IH}$ |

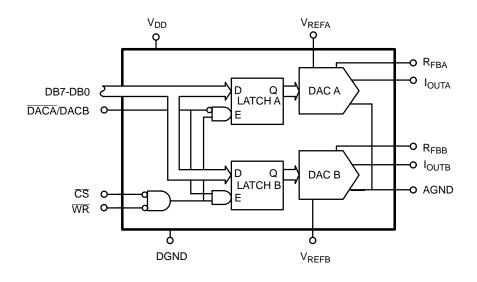

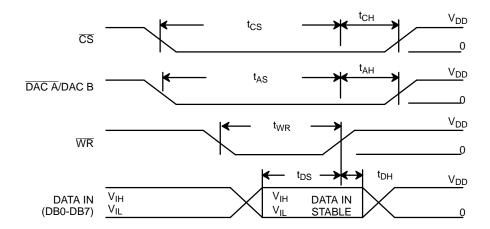

| SWITCHING<br>CHARACTERISTICS <sup>4</sup>                                                                                                                                                                     |                                                                                                                 |                                           |                        |                                           |                                |                            |                                                                                          |

| Chip Select to Write Set-Up Time Chip Select to Write Hold Time DAC Select to Write Set-Up Time DAC Select to Write Hold Time Data Valid to Write Set-Up Time Data Valid to Write Hold Time Write Pulse Width | t <sub>CS</sub> t <sub>CH</sub> t <sub>AS</sub> t <sub>AH</sub> t <sub>DS</sub> t <sub>DH</sub> t <sub>WR</sub> | 200<br>20<br>200<br>20<br>110<br>0<br>180 |                        | 230<br>30<br>230<br>30<br>130<br>0<br>200 |                                | ns<br>ns<br>ns<br>ns<br>ns |                                                                                          |

### NOTES:

- <sup>1</sup> Full Scale Range (FSR) is 10V for unipolar mode.

- Guaranteed but not production tested.

- Digital input levels should not go below ground or exceed the positive supply voltage, otherwise damage may occur.

- See timing diagram.

- 5 Specified values guarantee functionality. Refer to other parameters for accuracy.

Specifications are subject to change without notice

## **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = + 15 \text{ V}, V_{REF} = +10 \text{ V} \text{ unless otherwise noted})$

| Parameter                                                                                                                | Symbol                                   | Min    | 25°C<br>Typ      | Max                                        | Tmin t     | o Tmax<br>Max                          | Units                    | Test Conditions/Comments                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------|------------------|--------------------------------------------|------------|----------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE <sup>1</sup>                                                                                          | -,                                       |        | -71              |                                            |            |                                        |                          |                                                                                                                                                 |

|                                                                                                                          |                                          |        |                  |                                            |            |                                        |                          |                                                                                                                                                 |

| Resolution (All Grades)                                                                                                  | N                                        | 8      |                  |                                            | 8          |                                        |                          | Bits                                                                                                                                            |

| Integral Non-Linearity (Relative Accuracy) J, A, S K, B, T L, C                                                          | INL                                      |        |                  | <u>+</u> 1<br><u>+</u> 1/2<br><u>+</u> 1/4 |            | ±1<br>±1/2<br>±1/4                     | LSB                      | End Point Linearity Spec.                                                                                                                       |

| Monotonicity                                                                                                             |                                          |        |                  | <u>.</u> .,, .                             |            | <u>.</u> .,, .                         |                          | Guaranteed over temp                                                                                                                            |

| Differential Non-Linearity J, A, S K, B, T L, C                                                                          | DNL                                      |        |                  | <u>+</u> 1<br><u>+</u> 1<br><u>+</u> 1     |            | ±1<br>±1<br>±1                         | LSB                      | All grades monotonic over full temperature range.                                                                                               |

| Gain Error<br>J, A, S<br>K, B, T<br>L, C                                                                                 | GE                                       |        |                  | <u>+</u> 4<br><u>+</u> 2<br><u>+</u> 1     |            | <u>+</u> 5<br><u>+</u> 3<br><u>+</u> 1 | LSB                      | Using Internal R <sub>FB</sub><br>Digital Inputs = V <sub>INH</sub>                                                                             |

| Gain Temperature Coefficient <sup>2</sup>                                                                                | TC <sub>GE</sub>                         |        |                  |                                            |            | <u>+</u> 35                            | ppm/°C                   | $\Delta$ Gain/ $\Delta$ Temperature                                                                                                             |

| Power Supply Rejection Ratio                                                                                             | PSRR                                     |        |                  | <u>+</u> 100                               |            | <u>+</u> 200                           | ppm/%                    | $ \Delta Gain/\Delta V_{DD}  \Delta V_{DD} = \pm 5\%$<br>Digital Inputs = $V_{INH}$                                                             |

| Output Leakage Current (Pin 2)                                                                                           | I <sub>OUT1</sub>                        |        | 4                | <u>-</u> 50nA                              |            | <u>+</u> 200nA                         | nA                       | Digital Inputs = V <sub>INL</sub>                                                                                                               |

| Output Leakage Current (Pin 20)                                                                                          | I <sub>OUT2</sub>                        |        | <u> </u>         | <u>-</u> 50nA                              |            | <u>+</u> 200nA                         | nA                       | Digital Inputs = V <sub>INH</sub>                                                                                                               |

| Input Resistance                                                                                                         | V <sub>REFA</sub><br>V <sub>REFB</sub>   | 8<br>8 |                  | 15<br>15                                   | 8<br>8     | 15<br>15                               | kΩ<br>kΩ                 | TC = $-300 \text{ ppm/}^{\circ}\text{C max}$ .<br>11 k $\Omega$ typical                                                                         |

| Input Resistance Matching                                                                                                |                                          |        |                  | <u>+</u> 1                                 |            | <u>+</u> 1                             | %                        |                                                                                                                                                 |

| DYNAMIC PERFORMANCE <sup>2</sup>                                                                                         |                                          |        |                  |                                            |            |                                        |                          | R <sub>L</sub> =100Ω, C <sub>L</sub> =13pF                                                                                                      |

| Harmonic Distortion Digital Crosstalk Channel-to-Channel Isolation                                                       | THD<br>Q<br>CCI                          |        | -85<br>60<br>-77 |                                            |            |                                        | dB<br>nVs<br>dB          | $V_{IN}$ = 6 $V_{RMS}$ @ 1 KHz<br>Measured for code transition<br>ZS to F <sub>S</sub>                                                          |

| AC Feedthrough at I <sub>OUT1</sub> Glitch Energy Propagation Delay                                                      | F <sub>T</sub><br>Egl<br>t <sub>PD</sub> |        | -70<br>440       | 80                                         | <b>-65</b> | 100                                    | dB<br>nVs<br>ns          | $V_{REF}$ = 10kHz, 20 Vp-p, sinewave<br>ZS to F <sub>S</sub> Input Change<br>From 50% of digital input to 90%<br>of final analog output current |

| DIGITAL INPUTS <sup>3</sup>                                                                                              |                                          |        |                  |                                            |            |                                        |                          |                                                                                                                                                 |

| Logical "1" Voltage<br>Logical "0" Voltage<br>Input Leakage Current<br>Input Capacitance <sup>2</sup><br>Data<br>Control | VIH<br>VIL<br>IILKG<br>CIN               | 13.5   |                  | 1.5<br>±1<br>10<br>15                      | 13.5       | 1.5<br>±10<br>10<br>15                 | V<br>V<br>μA<br>pF<br>pF |                                                                                                                                                 |

# **ELECTRICAL CHARACTERISTICS (CONT'D)**

| Parameter                                                                                                                                                                                                     | Symbol                                                                           | Min                       | 25°C<br>Typ Max        | Tmin to<br>Min                        | Tmax<br>Max            | Units                            | Test Conditions/Comments                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------|------------------------|---------------------------------------|------------------------|----------------------------------|---------------------------------------------------------------------------------------|

| ANALOG OUTPUTS <sup>2</sup>                                                                                                                                                                                   |                                                                                  |                           |                        |                                       |                        |                                  |                                                                                       |

| Output Capacitance                                                                                                                                                                                            | C <sub>OUTA</sub><br>C <sub>OUTA</sub><br>C <sub>OUTB</sub><br>C <sub>OUTB</sub> |                           | 120<br>50<br>120<br>50 |                                       | 120<br>50<br>120<br>50 | pF<br>pF<br>pF<br>pF             | DAC Inputs all 1's<br>DAC Inputs all 0's<br>DAC Inputs all 1's<br>DAC Inputs all 0's  |

| POWER SUPPLY <sup>5</sup> Functional Voltage Range <sup>2</sup> Supply Current                                                                                                                                | V <sub>DD</sub><br>I <sub>DD</sub>                                               | 4.5                       | 15.75<br>2<br>2        | 4.5                                   | 15.75<br>2<br>2        | V<br>mA<br>mA                    | All digital inputs = 0 V or all = 5 V All digital inputs = $V_{IL}$ or all = $V_{IH}$ |

| SWITCHING CHARACTERISTICS Chip Solort to Write Set Lip Time                                                                                                                                                   |                                                                                  | 60                        |                        | 80                                    |                        | 50                               |                                                                                       |

| Chip Select to Write Set-Up Time Chip Select to Write Hold Time DAC Select to Write Set-Up Time DAC Select to Write Hold Time Data Valid to Write Set-Up Time Data Valid to Write Hold Time Write Pulse Width | tcs<br>tch<br>tas<br>tah<br>tos<br>toh<br>twr                                    | 10<br>60<br>10<br>30<br>0 |                        | 80<br>15<br>80<br>15<br>40<br>0<br>80 |                        | ns<br>ns<br>ns<br>ns<br>ns<br>ns |                                                                                       |

#### NOTES:

- <sup>1</sup> Full Scale Range (FSR) is 10V for unipolar mode.

- Guaranteed but not production tested.

- Digital input levels should not go below ground or exceed the positive supply voltage, otherwise damage may occur.

- See timing diagram.

- Specified values guarantee functionality. Refer to other parameters for accuracy.

#### Specifications are subject to change without notice

## ABSOLUTE MAXIMUM RATINGS (TA = +25°C unless otherwise noted)<sup>1, 2, 3</sup>

| V <sub>DD</sub> to GND+17 V                  | V <sub>RFBA</sub> , V <sub>RFBB</sub> to GND  |

|----------------------------------------------|-----------------------------------------------|

| AGND to DGND                                 | Storage Temperature65°C to +150°C             |

| (Functionality Guaranteed <u>+</u> 0.5 V)    | Lead Temperature (Soldering, 10 secs.) +300°C |

| Digital Input Voltage to DGND0.5 V, +17 V    | Package Power Dissipation Rating to 75°C      |

| $V_{PIN2}$ , $V_{PIN20}$ to GND              | CDIP, PDIP, SOIC, PLCC 900mW                  |

| V <sub>REFA</sub> , V <sub>REFB</sub> to GND | Derates above 75°C                            |

## NOTES:

- Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies.

- 3 GND refers to AGND and DGND.

**TQM**

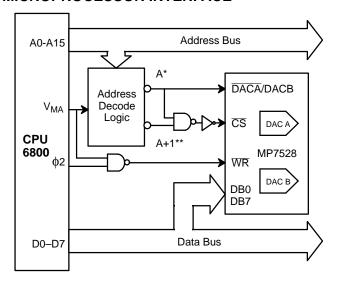

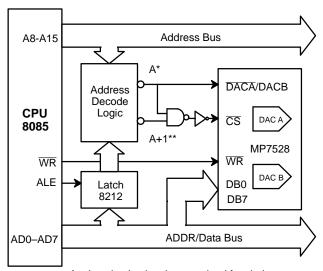

### INTERFACE LOGIC INFORMATION

DAC Selection: Both DAC latches share a common 8-bit input port. The control input DACA/DACB selects which DAC can accept data from the input port.

Mode Selection: Inputs  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  control the operating mode of the selected DAC. See Mode Selection Table below:

Write Mode: When  $\overline{CS}$  and  $\overline{WR}$  are both low the selected DAC is in the write mode. The input data latches of the selected DAC are transparent and its analog output responds to activity on DB0-DB7.

Hold Mode: The selected DAC latch retains the data which was present on DB0-DB7 just prior to  $\overline{CS}$  and  $\overline{WR}$  assuming a high state. Both analog outputs remain at the values corresponding to the data in their respective latches.

| DAC A/DAC B | CS | WR | DAC A | DAC B |

|-------------|----|----|-------|-------|

| L           | L  | L  | Write | Hold  |

| H           | L  | L  | Hold  | Write |

| X           | H  | X  | Hold  | Hold  |

| X           | X  | H  | Hold  | Hold  |

L = LOW state, H = HIGH state, X = Don't care state

**Table 1. Mode Selection Table**

#### NOTES:

- 1. All input signal rise and fall times measured from 10% to 90% of V<sub>DD</sub>. V<sub>DD</sub> = +5 V,  $t_r$  =  $t_f$  = 20 ns V<sub>DD</sub> = +15 V,  $t_r$  =  $t_f$  = 40 ns

- 2. Timing measurement reference level is  $V_{IH} + V_{IL} / 2$

Figure 1. Write Cycle Timing Diagram

### MICROPROCESSOR INTERFACE

Analog circuitry has been omitted for clarity \*A = Decoded 7528 DAC A Address \*\*A + 1 = Decoded 7528 DAC B Address

Figure 2. MP7528 Dual DAC to 6800 CPU Interface

Analog circuitry has been omitted for clarity \*A = Decoded 7528 DAC A Address \*\*A + 1 = Decoded 7528 DAC B Address

#### NOTE:

8085 instruction SHLD (store H & L direct) can update both DACS with data from H and L registers

Figure 3. MP7528 Dual DAC to 8085 CPU Interface

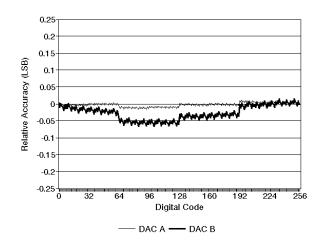

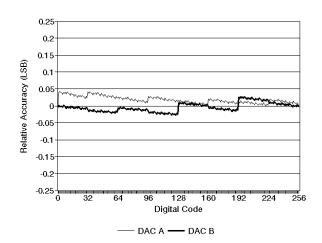

## PERFORMANCE CHARACTERISTICS

Graph 1. Relative Accuracy vs. Digital Code 5 V

Graph 2. Relative Accuracy vs. Digital Code 15 V

This page left blank

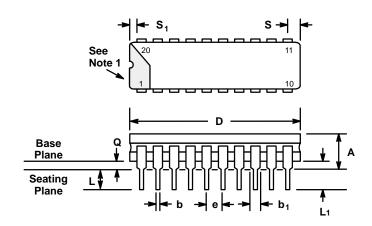

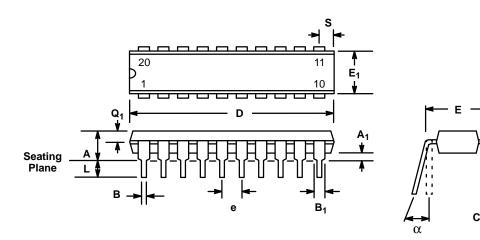

## 20 LEAD CERAMIC DUAL-IN-LINE (300 MIL CDIP) D20

|                | INCHES |        | MILLIN | MILLIMETERS |       |  |  |

|----------------|--------|--------|--------|-------------|-------|--|--|

| SYMBOL         | MIN    | MAX    | MIN    | MAX         | NOTES |  |  |

| А              |        | 0.200  |        | 5.08        |       |  |  |

| b              | 0.014  | 0.023  | 0.356  | 0.584       | _     |  |  |

| b <sub>1</sub> | 0.038  | 0.065  | 0.965  | 1.65        | 2     |  |  |

| С              | 0.008  | 0.015  | 0.203  | 0.381       | _     |  |  |

| D              | _      | 1.060  |        | 26.92       | 4     |  |  |

| Е              | 0.220  | 0.310  | 5.59   | 7.87        | 4     |  |  |

| E <sub>1</sub> | 0.290  | 0.320  | 7.37   | 8.13        | 7     |  |  |

| е              | 0.10   | 00 BSC | 2.5    | 4 BSC       | 5     |  |  |

| L              | 0.125  | 0.200  | 3.18   | 5.08        | _     |  |  |

| L <sub>1</sub> | 0.150  |        | 3.81   | _           | _     |  |  |

| Q              | 0.015  | 0.070  | 0.381  | 1.78        | 3     |  |  |

| S              | _      | 0.080  | _      | 2.03        | 6     |  |  |

| S <sub>1</sub> | 0.005  | _      | 0.13   | _           | 6     |  |  |

| α              | 0°     | 15°    | 0°     | 15°         | _     |  |  |

## NOTES

- Index area; a notch or a lead one identification mark is located adjacent to lead one and is within the shaded area shown.

- 2. The minimum limit for dimension  $b_1$  may be 0.023 (0.58 mm) for all four corner leads only.

- 3. Dimension Q shall be measured from the seating plane to the base plane.

- 4. This dimension allows for off-center lid, meniscus and glass overrun.

- The basic lead spacing is 0.100 inch (2.54 mm) between centerlines.

- 6. Applies to all four corners.

- 7. This is measured to outside of lead, not center.

## 20 LEAD PLASTIC DUAL-IN-LINE (300 MIL PDIP) N20

|                    | INC   | HES    | MILLIN | METERS |

|--------------------|-------|--------|--------|--------|

| SYMBOL             | MIN   | MAX    | MIN    | MAX    |

| А                  |       | 0.200  | _      | 5.08   |

| A <sub>1</sub>     | 0.015 | _      | 0.38   | _      |

| В                  | 0.014 | 0.023  | 0.356  | 0.584  |

| B <sub>1</sub> (1) | 0.038 | 0.065  | 0.965  | 1.65   |

| С                  | 0.008 | 0.015  | 0.203  | 0.381  |

| D                  | 0.945 | 1.060  | 24.0   | 26.92  |

| Е                  | 0.295 | 0.325  | 7.49   | 8.26   |

| E <sub>1</sub>     | 0.220 | 0.310  | 5.59   | 7.87   |

| е                  | 0.10  | 00 BSC | 2.5    | 4 BSC  |

| L                  | 0.115 | 0.150  | 2.92   | 3.81   |

| α                  | 0°    | 15°    | 0°     | 15°    |

| Q <sub>1</sub>     | 0.055 | 0.070  | 1.40   | 1.78   |

| S                  | 0.040 | 0.080  | 1.02   | 2.03   |

Note: (1) The minimum limit for dimensions B1 may be 0.023" (0.58 mm) for all four corner leads only.

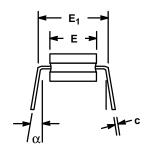

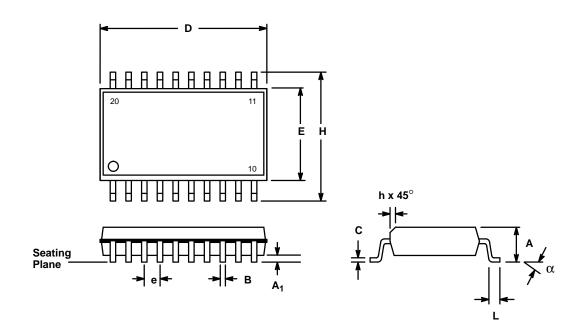

## 20 LEAD SMALL OUTLINE (300 MIL JEDEC SOIC) S20

|                | INC    | CHES   | MILLIN | METERS |

|----------------|--------|--------|--------|--------|

| SYMBOL         | MIN    | MAX    | MIN    | MAX    |

| А              | 0.097  | 0.104  | 2.464  | 2.642  |

| A <sub>1</sub> | 0.0050 | 0.0115 | 0.127  | 0.292  |

| В              | 0.014  | 0.019  | 0.356  | 0.483  |

| С              | 0.0091 | 0.0125 | 0.231  | 0.318  |

| D              | 0.500  | 0.510  | 12.70  | 12.95  |

| Е              | 0.292  | 0.299  | 7.42   | 7.59   |

| е              | 0.0    | 50 BSC | 1.2    | 7 BSC  |

| Н              | 0.400  | 0.410  | 10.16  | 10.41  |

| h              | 0.010  | 0.016  | 0.254  | 0.406  |

| L              | 0.016  | 0.035  | 0.406  | 0.889  |

| α              | 0°     | 8°     | 0°     | 8°     |

# **Notes**

# **Notes**

## NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contains here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright EXAR Corporation Datasheet April 1995

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.

**T**@M"

# This datasheet has been downloaded from:

www. Data sheet Catalog.com

Datasheets for electronic components.