## United States Patent [19]

#### Nakai et al.

[11] Patent Number:

4,477,164

[45] Date of Patent:

Oct. 16, 1984

#### [54] CAMERA SYSTEM OPERABLE IN ACCORDANCE WITH STORED MEMORY

[75] Inventors: Masaaki Nakai, Nara; Masayoshi

Sahara, Sennan; Nobuyuki Taniguchi,

Tondabayashi, all of Japan

[73] Assignee: Minolta Camera Kabushiki Kaisha,

Osaka, Japan

[21] Appl. No.: 448,834

[22] Filed: Dec. 10, 1982

[30] Foreign Application Priority Data

Dec. 17, 1981 [JP] Japan ...... 56-204972

[51] Int. Cl.<sup>3</sup> ...... G03B 17/00

[58] Field of Search ....... 354/23 D, 286, 412,

354/289.1, 286

[56] References Cited

#### U.S. PATENT DOCUMENTS

| 4.297.011 | 10/1981  | Adams, Jr    | 354/22 TX |

|-----------|----------|--------------|-----------|

| .,_,,,,,, | 10, 1,01 | 1 Mullio, 51 | 334/43 LJ |

| 4.309.089 | 1/1982   | Harvey       | 354/22 D  |

| 1,505,005 | 1, 1,02  | 1141 VCy     | 334/23 1  |

| 4 400 072 | 8/1083   | Suzuki et al | 254/22 D  |

| 7,700,072 | 0/1903   | Suzuki et al | 334/23 D  |

#### FOREIGN PATENT DOCUMENTS

54-108628 8/1979 Japan .

#### OTHER PUBLICATIONS

Microcomputer Dictionary and Guide by Sippl, p. 41.

Primary Examiner-Russell E. Adams

Attorney, Agent, or Firm-Jackson, Jones & Price

### [57] ABSTRACT

A camera system is provided that permits memory data dedicated to particular camera accessories to be transmitted to the camera body for enabling the operation of the camera. The camera accessories can carry dedicated information or variable information to the camera body. Synchronization between the camera accessory and the camera body can be provided by a train of clock pulses. Information can be programmed in a fixed memory circuit to insure that only a particular accessory so designated will provide information to the camera body to prevent any erroneous inputting of data from a plurality of camera accessories that are contemplated for use with a particular camera body.

## 29 Claims, 19 Drawing Figures

Fig. 3(a)

Fig.

Fig. 5

Fig. 6 (a)

Sheet 7 of 19

Fig. 6 (b)

Fig. 8(a)

Fig. 8(b)

Fig. 11(a)

# CAMERA SYSTEM OPERABLE IN ACCORDANCE WITH STORED MEMORY

## BACKGROUND OF THE INVENTION

The present invention generally relates to a photographic system in which desired photographing functions are effected while signals are applied or received between a camera body and camera accessories such as an interchangeable lens, an extension ring, a motor-drive unit, an electronic flash, etc. which are mounted on or attached to said camera body, and more particularly to a camera system for deriving fixed memories stored in the respective accessories.

Generally, in a high class photographic camera such as a single lens reflex camera and the like, it has been so arranged, in many cases, that, with camera accessories such as the interchangeable lens, motor-drive unit, electronic flash unit, etc. coupled to the camera body, func- 20 tionings of the respective camera accessories are controlled by a control system provided at the side of the camera body or an arrangement provided within the camera body is controlled based on information from the camera, accessories. In the latter case as described 25 above, if various data of the respective camera accessories are adapted to be transmitted electrically, coupling portions between the camera body and the camera accessories may be simplified for convenience in use, as compared with mechanical signal transmission conven- 30 tionally adopted.

Meanwhile, it has been recently proposed to effect control of the camera body and camera accessories by a inicrocomputer, and in the above case, there may be conceived an arrangement in which with a fixed memory circuit such as a ROM (read only memory) provided in each of the camera accessories so as to keep data specific to the camera accessory stored therein, an address within the fixed memory circuit is designated from the side of the camera body for reading the data of the designated address into the camera body.

## SUMMARY OF THE INVENTION

Accordingly, an essential object of the present invention is to provide a camera system operable in accordance with stored memory, and arranged to apply and receive signals between a camera body and camera accessories attached thereto, in which the number of terminals for signal transmission therebetween is reduced as far as possible.

Another important object of the present invention is to provide a camera system of the above described type which is free from any confusion in the signal impression and reception between the camera body and camera accessories regardless of reduction in the number of terminals.

A further object of the present invention is to provide a camera system of the above described type in which the most rational system capable of effecting necessary 60 functions by the smallest number of signal lines is pursued for effecting impression and reception of signals between the camera body and camera accessories in an efficient manner.

In accomplishing these and other objects, according 65 to one preferred embodiment of the present invention, there is provided a camera system operable in accordance with memory data by means of carrying the

memory data from a camera accessory to a camera body, and characterized in that it includes:

first means for carrying electric power from the camera body to the camera accessory to power the camera accessory;

second means for carrying a train of clock pulses from the camera body to the camera accessory to synchronize the camera accessory with the camera body;

third means for serially carrying address data from the camera body to the camera accessory to locate the memory data;

fourth means for serially carrying the memory data corresponding to the address data from the camera accessory to the camera body; and

fifth means for carrying an initiating signal from the camera body to the camera accessory to control the timing of reading the memory data corresponding to the address data.

More specifically, the camera system according to the present invention is further characterized in that, with a plurality of kinds of separate camera accessories connected to the camera body, when the memories stored in the respective camera accessories are to be read into the camera body, the address data to be fed into the camera accessories from said camera body are adapted to be different according to the kinds of the camera accessories. By the above arrangement, such problems that, when the plurality of kinds of camera accessories are simultaneously coupled to one camera body and one address signal is produced from the camera body, the plurality of camera accessories are undesirably addressed, with wrong data from unexpected camera accessories being read into the camera body, may be avoided.

Other specific features of the camera system according to the present invention are such that the reading functions of the data from the particular camera accessory are repeatedly effected, whereby, in the presence of variable data such as manual setting data, etc. in the camera accessory, the camera body is capable of renewing the read-in data into the latest data at all times so as to cope with data alterations at the side of the camera accessories.

Still further features of the camera system according to the present invention reside in that, since there are some camera accessories having no data to be read, without necessity for reading into the side of the camera body, the camera system of the present invention is particularly so arranged that, in order to cope with the above situation, common data are stored in the particular address of each camera accessory and thus, at the side of the camera body, it is possible to make judgement as to whether or not the camera accessory is one having the data to be read by feeding a signal for starting the reading from the camera body side, depending on whether or not the common data as described above are fed from the side of the camera accessory.

## BRIEF DESCRIPTION OF THE DRAWINGS

These and other objects and features of the present invention will become apparent from the following description taken in conjunction with the preferred embodiment thereof with reference to the accompanying drawings, in which;

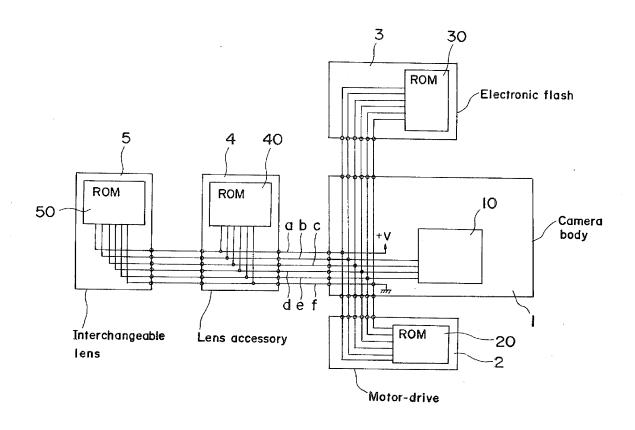

FIG. 1 is a block diagram explanatory of the principle of a camera system according to the present invention,

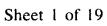

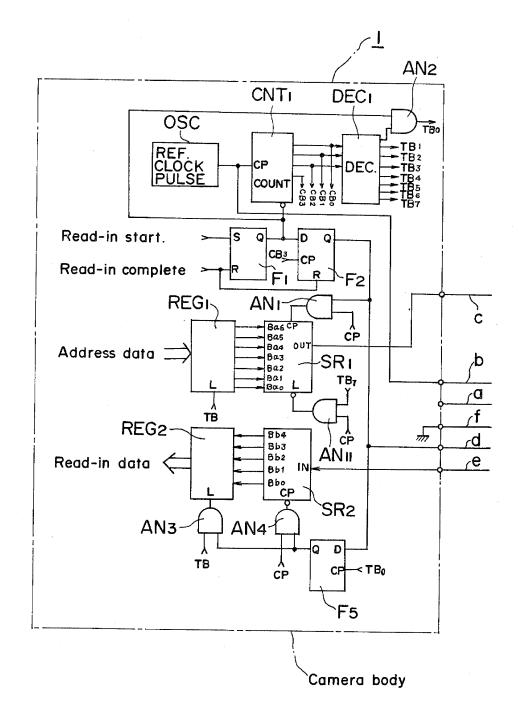

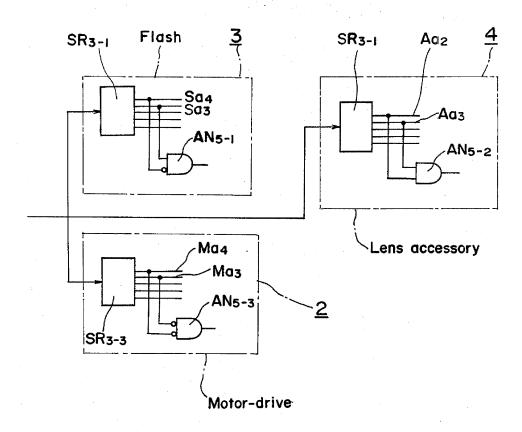

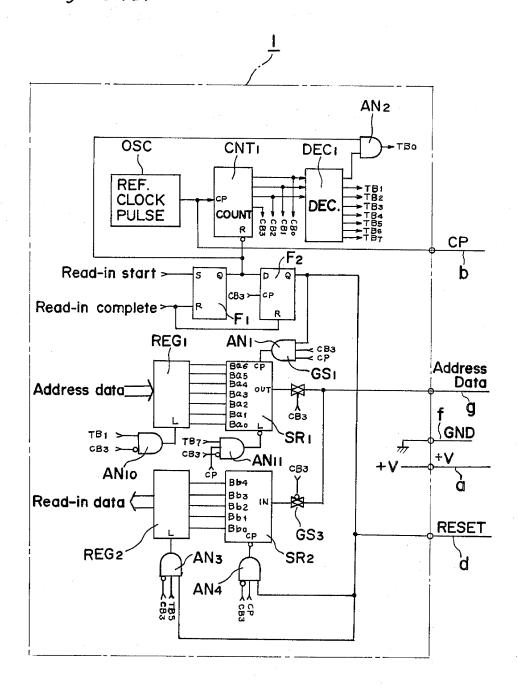

FIG. 2 is a block diagram showing a circuit construction at the side of a camera body in the camera system of FIG. 1,

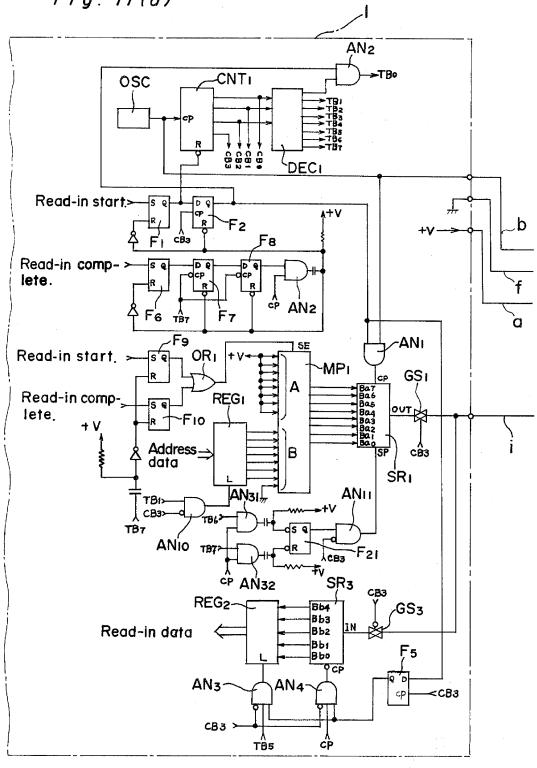

FIGS. 3(a) and 3(b) are block diagrams showing a circuit construction for part of a data input and output 5 portion at the side of the camera body, and that for a data output device at the side of a camera accessory, with the circuit of FIG. 3(a) being coupled with the circuit of FIG. 3(b) through terminals c, b, a, f, d and e

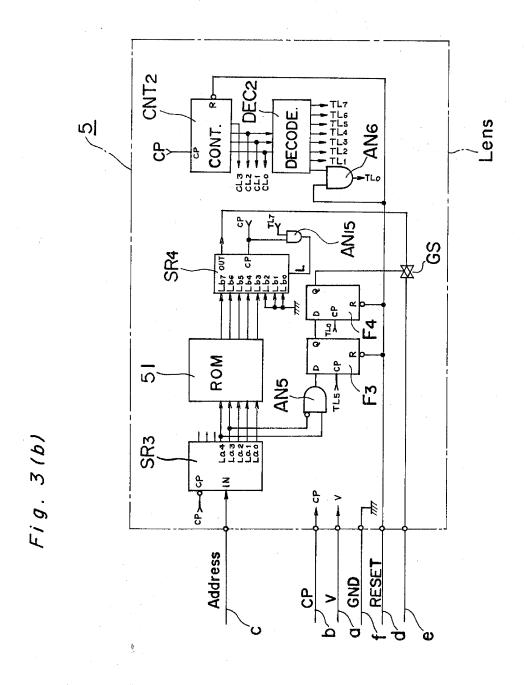

FIG. 4 is a time-chart explanatory of the functionings of the arrangement of FIGS. 3(a) and 3(b),

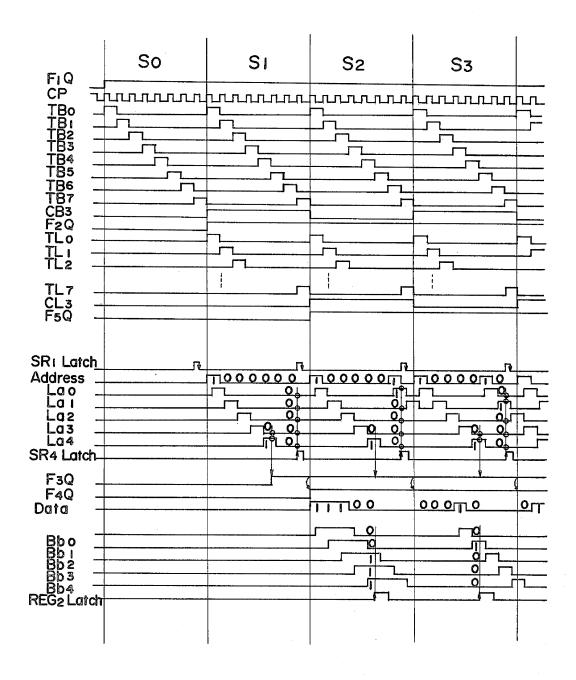

FIG. 5 is a circuit connection diagram showing an example of connections to other camera accessories,

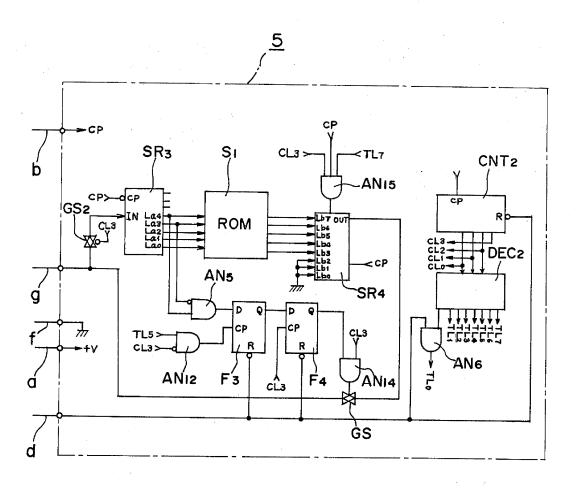

FIGS. 3(a) and 3(b), which particularly show a modification thereof, with the circuit of FIG. 6(a) being coupled with the circuit of FIG. 6(b) through terminals b, g, f, a and d as indicated,

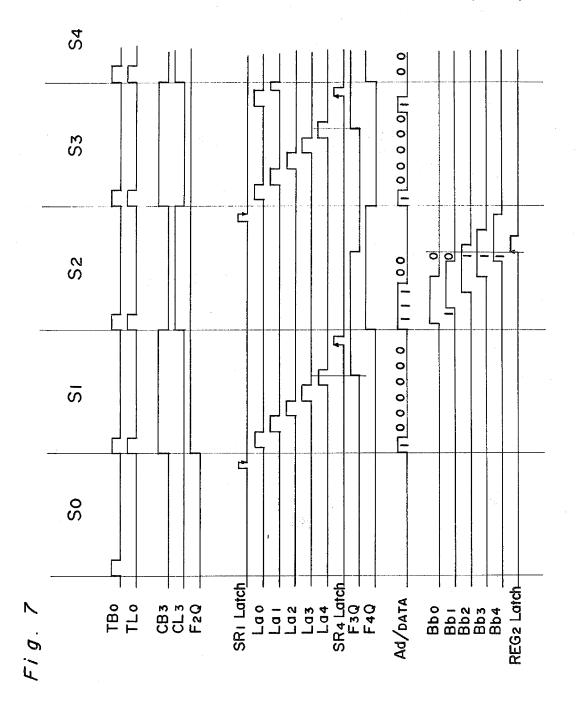

FIG. 7 is a time-chart explanatory of functionings of 20 the arrangement of FIGS. 6(a) and 6(b),

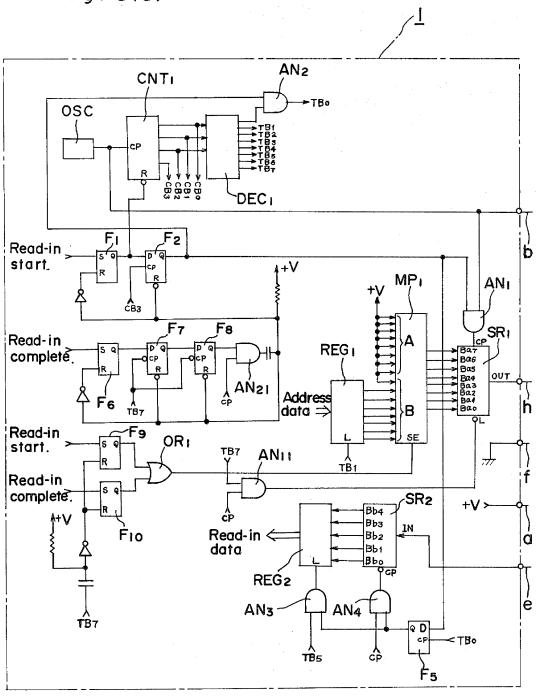

FIGS. 8(a) and 8(b) are block diagrams similar to FIGS. 3(a) and 3(b) which particularly show another modification thereof, with the circuit of FIG. 8(a) being coupled with the circuit of FIG. 8(b) through terminals 25 b, h, f, a and e as indicated,

FIGS. 9 and 10 are time-charts explanatory of functionings of the arrangement of FIGS. 8(a) and 8(b),

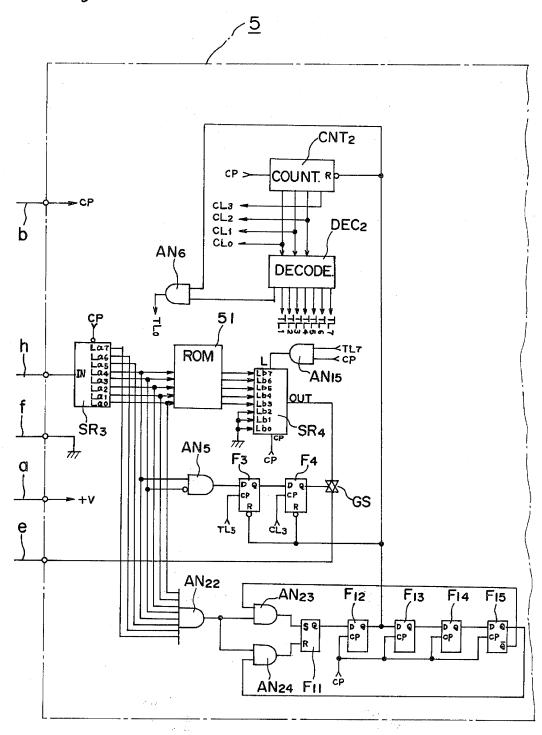

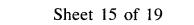

FIGS. 11(a) and 11(b) are block diagrams similar to FIGS. 3(a) and 3(b), which particularly show still an- 30 other modification thereof, with the circuit of FIG. 11(a) being coupled with the circuit of FIG. 11(b)through terminals b, f, a and i as indicated,

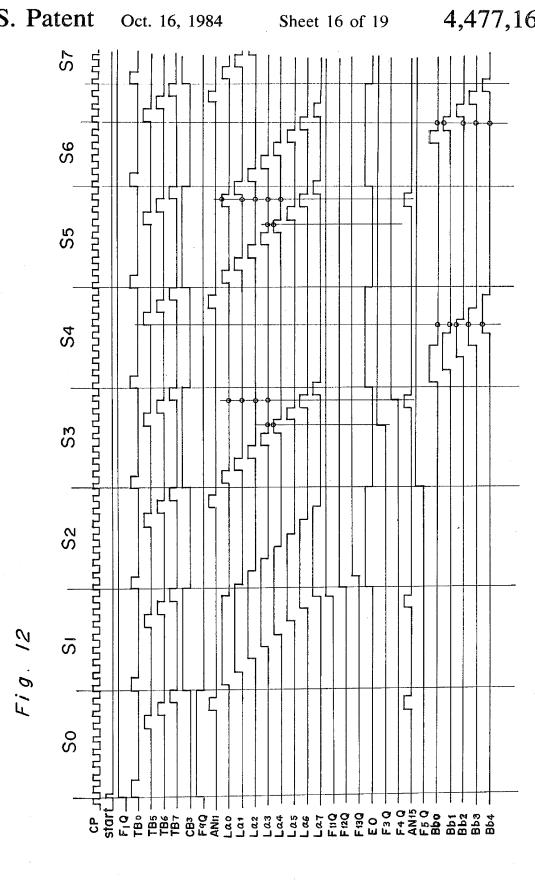

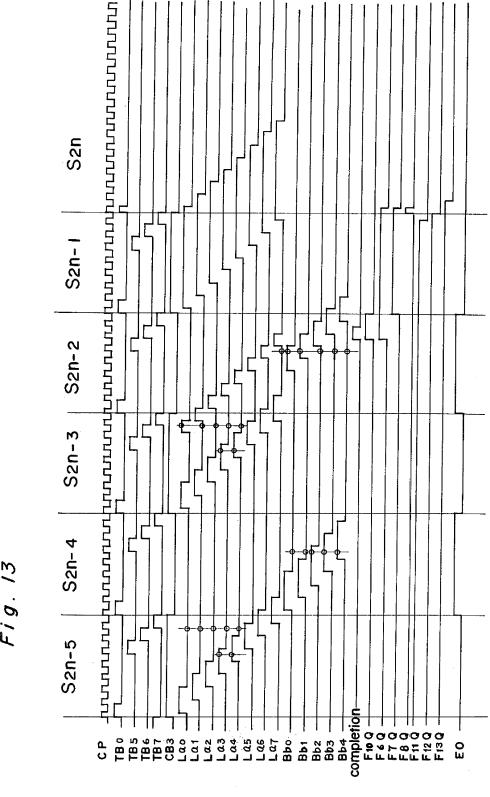

FIGS. 12 and 13 are time charts explanatory of functionings of the circuit of FIGS. 11(a) and 11(b),

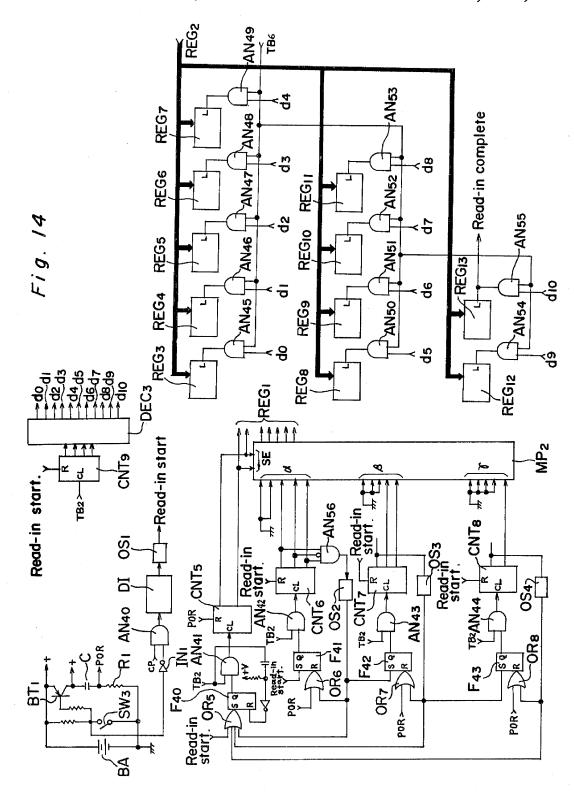

FIG. 14 is a circuit diagram showing a circuit construction at portions other than the data input and output portion at the camera body side in FIG. 3(a), and

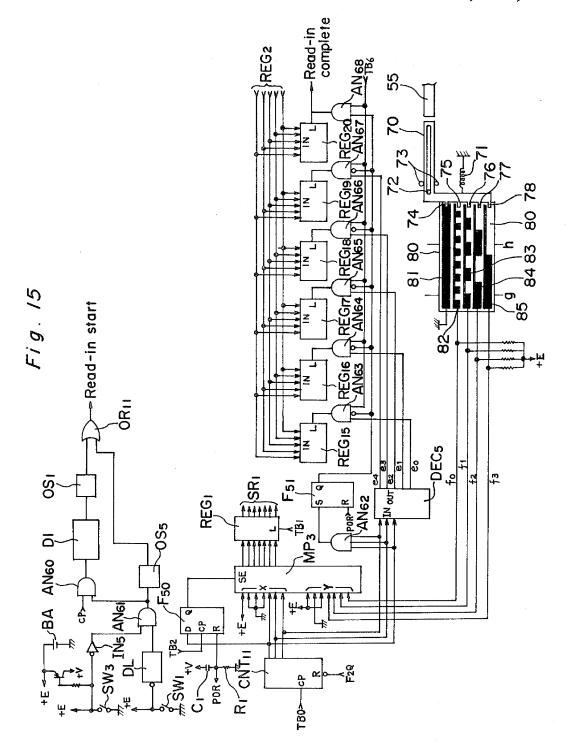

FIG. 15 is a circuit diagram similar to FIG. 14, which particularly shows another modification thereof.

#### DETAILED DESCRIPTION OF THE INVENTION

Before the description of the present invention prolike reference numerals throughout the accompanying drawings.

Referring now to the drawings, there is shown in FIG. 1 a block diagram representing an entire photographing system applied with the present invention. 50 The photographing system of FIG. 1 generally includes a camera body 1 having a central control circuit 10 provided therein for applying address data to camera accessories mounted on or attached to said camera body, and for receiving data from the camera accesso- 55 ries, an electrical driving accessory 2 (i.e. motor-drive and the like) in which a data output unit 20 is provided for producing data specific to the motor-drive, a camera accessory 3 for flash photography (e.g. electronic flash or the like) having a data output unit 30 incorporated 60 therein for outputting data specific to an electronic flash, a lens accessory 4 such as an extension tube, bellows, converter lens or the like in which a data output unit 40 is provided for producing data specific to the lens accessory, and an interchangeable lens 5 having a 65 data output unit 50 provided therein for producing data specific to the interchangeable lens, with the camera body 1 and the respective camera accessories 2, 3 and 4,

and the camera accessories 4 and 5 being electrically connected to each other through terminals a, b, c, d, e and f respectively as shown.

In the above arrangement, electric power, a train of reference clock pulses, address data and, reset signals are supplied from the camera body 1 to the respective output units 20, 30, 40 and 50 of the camera accessories 2, 3, 4 and 5 through the terminals a, b, c and d in a manner as described in detail later, while the data spe-10 cific to the respective camera accessories 2 to 5 are fed from the data output units 20 to 50 of said camera accessories 2 to 5 to the camera body 1 through the terminal e, with the terminal f being connected to the ground.

Reference is also made to FIG. 2 showing a block FIGS. 6(a) and 6(b) are block diagrams similar to 15 diagram of a central control unit 10 of the camera body 1 as coupled to the data output unit 50 of the interchangeable lens 5.

> The central control unit 10 in FIG. 2 generally includes a power source control circuit 11 coupled, for example, to the data output unit 50 of the interchangeable lens 5 through the terminal a, parallel connection of switches SWI, SW2 and SW3 which are coupled with a timing circuit 12 which is connected to an address output device 13, and also, to the data output device 50 through the terminals b and d, with the address output device 13 being connected to the data output unit 50 through the terminal c, a data input device 14 connected to the data output unit 50 through the terminal e, and also, to the timing circuit 12 and a calculation circuit 15 which is further coupled to an aperture control device 16, a shutter control device 17 and a display unit 18 as shown.

The power source control circuit 11 supplies electric power to the data output unit 50 of the camera acces-35 sory, for example, the interchangeable lens 5 in this embodiment through the terminal a. The switch SW1 is arranged to be closed when the interchangeable lens 5 (referred to merely as a lens hereinbelow) is attached to the camera body 1. The switch SW2 is a release switch 40 for starting an exposure control function, while the switch SW3 is a light measuring switch for starting a light measuring function, and these switches SW2 and SW3 are so arranged, for example, that the light measuring switch SW3 is closed at a first stage of depression ceeds, it is to be noted that like parts are designated by 45 of a shutter release button (not particularly shown), and the release switch SW2 is closed at a subsequent second stage of depression of the shutter release button. The light measuring switch SW3 may be of a type which is arranged, upon touching of the shutter release button by a finger of an operator, to be closed in response to electric current flowing through the finger or resistance variation of a pressure sensitive element produced by the pressure applied by the finger. The timing circuit 12 is arranged to apply timing signals to the address output device 13 and the data input device 14 based on the closing of the switches SWI, SW2 and SW3 for controlling timings of the address data output and the data input respectively, and also, to feed a train of reference clock pulses to the terminal b, and reset signal to the terminal d. The address output device 13 is controlled by the timing circuit 12, and successively produces address data serially per each bit from the terminal c. The data input device 14 is adapted to read the data specific to the respective camera accessories and successively input serially per each bit from the terminal e for conversion into parallel data to be fed to the calculation circuit 15, which calculates the data for exposure control, etc. based on the above data so as to be applied respectively to the aperture control device 16, shutter control device 17 and display device 18.

Table 1 given below shows examples of contents in ROM provided in each of the data output devices of the respective camera accessories for storing the data inherent in the camera accessories, while Table 2 denotes the relations between the above data produced from the ROM and the meanings represented by said data.

In Table 1, upper 2 bits (a6) and (a5) of the address data relate to data that show which camera accessory

i.e. which ROM should be selected, and are represented by "10" when the selected camera accessory is an interchangeable lens, "01" when the selected camera accessory is an electronic flash, "11" if the selected camera accessory is a lens accessory such as an extension ring, bellows or the like, and "00", in the case of the motor-drive, although not particularly shown. The lower 5 bits (a4), (a3), (a2), (a1) and (a0) of the address data designate the address of ROM.

TABLE 1

|                                |        |        |                                         |                                                                         |                  |                                                               |                                                          |                                                                                         | TABLE               | <u> </u>    |                                 |           |                     |

|--------------------------------|--------|--------|-----------------------------------------|-------------------------------------------------------------------------|------------------|---------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------|-------------|---------------------------------|-----------|---------------------|

|                                |        |        |                                         |                                                                         |                  | E                                                             | amp                                                      | le of conten                                                                            | ts of ROM fo        | r each came | ra accessory                    |           |                     |

| Accessory ad- a6 dress code a5 |        |        |                                         |                                                                         |                  |                                                               |                                                          |                                                                                         |                     | 1<br>0      |                                 |           |                     |

| _Da                            | ata ac | ldre   | ss c                                    | ode                                                                     | ^_               | Addre                                                         | ess                                                      | (Ex.) 50 mm                                                                             | n F1.4 lens         | (Ex.) 135 m | m F3.5 lens (Ex.) 28 mm F2 lens |           |                     |

| a4                             | a3     | a2     | a1                                      | a0                                                                      | С                | ontei                                                         | nts                                                      | Data code                                                                               | Contents            | Data code   | Contents                        | Data code | Contents            |

| 0                              | 0      | 0      | 0                                       | 0                                                                       |                  | Chec                                                          |                                                          | 11100                                                                                   |                     | 11100       |                                 | 11100     |                     |

| 0                              | 0      | 0      | 0                                       | 1                                                                       |                  | Avo                                                           |                                                          | 00010                                                                                   | F1.4                | 00110       | F3.5                            | 00100     | F2                  |

| 0                              | 0      | 0      | 1                                       | 0                                                                       | 4                | A.vm:                                                         |                                                          | 01111                                                                                   | F16                 | 10001       | F22                             | 10001     | F22<br>Distance     |

| 0                              | 0      | 0      | 1                                       | 1                                                                       |                  | lens<br>type                                                  |                                                          | 00000                                                                                   | Distance<br>present | 00000       | Distance<br>present             | 00001     | absent              |

| 0                              | 0      | 1      | 0                                       | 0                                                                       |                  | Foca                                                          |                                                          | 00110                                                                                   | 40-60               | 01001       | 120-180                         | 00101     | 25-40               |

|                                |        |        |                                         |                                                                         |                  | lengt                                                         | h                                                        |                                                                                         |                     | •           |                                 |           |                     |

|                                |        |        |                                         |                                                                         |                  |                                                               |                                                          |                                                                                         |                     |             |                                 |           |                     |

| 1                              | 0      | Ö      | 0                                       | 0                                                                       |                  |                                                               |                                                          | 11111                                                                                   | ∞                   | 11111       | œ                               |           |                     |

| 1                              | 0      | 0      | 0                                       | 1                                                                       |                  |                                                               |                                                          | 01101                                                                                   | 4 m                 | 10110       | 19 m                            |           | ÷                   |

| 1                              | 0      | 0      | 1                                       | 0                                                                       |                  |                                                               |                                                          | $01001 \\ 00111$                                                                        | 2<br>1.4            | 10011       | 11<br>6.7                       |           |                     |

| 1                              | ő      | 1      | ò                                       | ó                                                                       |                  |                                                               |                                                          | 00110                                                                                   | 1.2                 | 01111       | 5.6                             |           |                     |

| 1                              | 0      | 1      | 0                                       | 1                                                                       |                  | Data                                                          |                                                          | 00101                                                                                   | 1                   | 01110       | 4.5                             |           |                     |

| 1                              | 0      | 1      | 1                                       | 0<br>1                                                                  |                  | len                                                           |                                                          | 00100                                                                                   | 0.85<br>0.7         | 01100       | 3.5<br>2.8                      |           |                     |

| i<br>1                         | 0      | 1<br>0 | 0                                       | 0                                                                       |                  | sion                                                          |                                                          | 00011                                                                                   | 0.6                 | 01011       | 2.8                             |           |                     |

| i                              | 1      | Õ      | 0                                       | 1                                                                       |                  | amoı                                                          |                                                          | 00010                                                                                   | 0.6                 | 01010       | 2.5                             |           |                     |

| 1                              | 1      | 0      | 1                                       | . 0                                                                     |                  |                                                               |                                                          | 00001                                                                                   | 0.5                 | 01010       | 2.5                             |           |                     |

| 1.                             | 1<br>1 | 0      | 1                                       | 1                                                                       |                  |                                                               |                                                          | $00001 \\ 00001$                                                                        | 0.5<br>0.5          | 01001       | 2<br>2                          |           |                     |

| 1                              | ì      | 1      | 0                                       |                                                                         |                  |                                                               |                                                          | 00001                                                                                   | 0.5                 | 01000       | 11                              |           |                     |

| , 1,                           | 1      | 1      | 1                                       | . 0                                                                     |                  |                                                               |                                                          | 00001                                                                                   | 0.5                 | 01000       | 1.7                             |           |                     |

| 1                              | 1      | 1      | 1                                       | 1                                                                       |                  |                                                               |                                                          | 00001                                                                                   | 0.5                 | 00111       | 1.4                             |           |                     |

|                                |        |        |                                         | cesso<br>ress                                                           |                  |                                                               | a6<br>a5                                                 |                                                                                         | 0<br>1              |             |                                 | 1<br>1    |                     |

|                                |        |        |                                         |                                                                         |                  | SS CO                                                         |                                                          | Address                                                                                 | (Ex.) Ele           | ec. flash A | Address                         | (Ex.) Rea | r converter         |

|                                |        | -      | a4                                      | <b>a</b> 3                                                              | a2               | al                                                            | a0                                                       | Contents                                                                                | Data code           | e Contents  | Contents                        | Data code | Contents            |

|                                |        |        | 0                                       | 0                                                                       | 0                | Q                                                             | 0                                                        | check<br>code                                                                           | 11100               |             | check<br>code                   | 11100     |                     |

|                                |        |        | 0                                       | 0                                                                       | 0                | 0                                                             | 1                                                        | GNO.<br>mini                                                                            | 00010               | 1.4         | Kind of accessory               | 00011     | Rear con-<br>verter |

| ٠.                             |        |        | 0                                       | 0                                                                       | 0                | 1                                                             | 0                                                        | GNO.                                                                                    | 10010               | 28          | accessor y                      |           |                     |

|                                |        |        | 0                                       | 0                                                                       | 0                | 1                                                             | 1                                                        | Orienta-                                                                                | 00001               | 45° 60°     |                                 |           |                     |

|                                |        |        |                                         |                                                                         |                  |                                                               |                                                          | tion char-                                                                              |                     |             |                                 |           |                     |

|                                |        |        | Λ                                       | Ω                                                                       |                  | 0                                                             | 0                                                        |                                                                                         |                     |             |                                 |           |                     |

|                                |        |        | U                                       | U                                                                       |                  | U                                                             | . 0                                                      | ·                                                                                       |                     |             |                                 |           |                     |

|                                |        |        |                                         |                                                                         | ν <sub>1</sub> - |                                                               |                                                          | Given be-                                                                               |                     |             |                                 |           |                     |

|                                |        |        |                                         | ó                                                                       |                  | 0                                                             | 0                                                        |                                                                                         |                     |             |                                 |           |                     |

|                                |        |        | 1                                       |                                                                         | _                | -                                                             |                                                          |                                                                                         |                     |             |                                 |           |                     |

|                                |        |        | 1                                       | 0                                                                       | 0                | 1                                                             | 0                                                        | for other                                                                               |                     |             |                                 |           |                     |

|                                |        |        | 1                                       | 0                                                                       | 0                | 1                                                             | 1                                                        | informa-                                                                                |                     |             |                                 |           |                     |

|                                |        |        |                                         |                                                                         |                  |                                                               |                                                          | tion                                                                                    |                     |             |                                 |           |                     |

|                                |        |        | 1                                       | 0                                                                       | 1                | i                                                             | 0                                                        |                                                                                         |                     |             |                                 |           |                     |

|                                |        |        | 1                                       | 0                                                                       | 1                | 1                                                             | 1                                                        |                                                                                         |                     |             |                                 |           |                     |

|                                |        |        | i<br>t                                  |                                                                         |                  |                                                               |                                                          |                                                                                         |                     |             |                                 |           |                     |

|                                |        |        | 1                                       | 1                                                                       | 0                | 1                                                             | 0                                                        |                                                                                         |                     |             |                                 |           |                     |

|                                |        |        | 1                                       | 1                                                                       | 0                | 1                                                             | 1                                                        |                                                                                         |                     |             |                                 |           |                     |

|                                |        |        | 1                                       | 1                                                                       | I                | 0                                                             | 0                                                        |                                                                                         |                     |             |                                 |           |                     |

|                                |        |        |                                         |                                                                         | 1                |                                                               |                                                          |                                                                                         |                     |             |                                 |           |                     |

|                                |        |        | 1                                       | 1                                                                       | İ                | 1                                                             | 1                                                        |                                                                                         |                     |             |                                 |           |                     |

|                                |        |        | O 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1 | 1                | 0<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>0<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | tion char-<br>acteris-<br>tic  Given be-<br>low are<br>those re-<br>served<br>for other | 00001               | 45° 60°     |                                 |           |                     |

TABLE 2

|           |       |          |           | TABL               |           |                |              |                 |

|-----------|-------|----------|-----------|--------------------|-----------|----------------|--------------|-----------------|

|           |       |          |           | List of data of co | ntents in | ROM            |              |                 |

|           |       |          | •         | 100 m              | Elec      | tronic flash   |              | Lens accessory  |

|           |       |          | Lens      |                    |           | Orientation    | Winder       | Kind of         |

| Data code | FNO.  | Distance | Lens type | Focal Length       | GNO.      | Characteristic | Frame speed  | accessory       |

| 00000     | F 1.2 |          | Distance  |                    | 1.0       | 20° 28°        | 1 Frame/sec. |                 |

|           |       |          | present   |                    |           |                |              |                 |

| 00001     | 1.4   | 0.5 m    |           |                    | 1.2       | 45° 60°        | 1.5          | Bellows         |

|           |       |          | absent    |                    |           |                | _            | <b>.</b>        |

| 00010     | 1.7   | 0.6      |           | Less than 8 mm     | 1.4       | 53° 70°        | 2            | Reverse adapter |

| 00011     | 2     | 0.7      |           | 8-17               | 2.0       | 60° 78°        | 2.5          | Rear converter  |

| 00100     | 2.5   | 0.85     |           | 17-25              | 1.7       |                | 3            | Extension ring  |

| 00101     | 2.8   | 1        |           | 25-40              | 2.8       |                | 3.5          |                 |

| 00110     | 3.5   | 1.2      |           | 40-60              | 3.5       |                | 4            |                 |

| 00111     | 4     | 1.4      |           | 60-90              | 4.0       |                | 4.5          |                 |

| 01000     | 4.5   | 1.7      |           | 90-120             | 4.5       |                | 5            |                 |

| 01001     | 5.6   | 2        |           | 120-180            | 5.6       |                | 5.5          |                 |

| 01010     | 6.7   | 2.5      |           | 180-250            | 6.7       |                | 6            |                 |

| 01011     | 8     | 2.8      |           | 250-450            | 8         |                | 6.5          |                 |

| 01100     | 9.5   | 3.5      |           | 450-700            | 9.5       |                | 7            |                 |

| 01101     | 11    | 4        |           | 700-1000           | 11        |                |              |                 |

| 01110     | 13    | 4.5      |           | More than 1000     | 13        |                |              |                 |

| 01111     | 16    | 5.6      |           |                    | 16        |                |              |                 |

| 10000     | 19    | 6.7      |           |                    | 19        |                |              |                 |

| 10001     | 22    | 8        |           |                    | 22        |                |              |                 |

| 10010     | 27    | 9.5      |           |                    | 28        |                |              |                 |

| 10011     | 32    | 11       |           |                    | 32        |                |              |                 |

| 10100     | 40    | 13       |           |                    | 40        | •              |              |                 |

| 10101     | 45    | 16       |           |                    | 45        |                |              |                 |

| 10110     | 10    | 19       |           |                    |           |                |              |                 |

| 10111     |       | 22       |           |                    |           |                |              |                 |

| 11000     |       | 27       |           |                    |           |                |              |                 |

| 11001     |       | 32       |           |                    |           |                |              |                 |

| 11010     |       | 40       |           |                    |           |                |              |                 |

| 11010     |       | 45       |           |                    |           |                |              |                 |

| 11100     |       | 54       |           |                    |           |                |              |                 |

|           |       | 64       |           |                    |           |                |              |                 |

| 11101     |       | 80       |           |                    |           |                |              |                 |

| 11110     |       |          |           |                    |           |                |              |                 |

| 11111     |       | 00       |           |                    |           |                |              |                 |

Subsequently, based on Tables 1 and 2 given above, 35 input data in the case where various camera accessories are attached to the camera body will be described hereinbelow. By way of example, explanation will be given with reference to the case where an interchangeable lens capable of producing distance information corresponding to an amount of extension of the lens is attached to the camera body besides an interchangeable lens having a focal length of 50 mm, fully open aperture value of F1.4 and minimum aperture value of F16.

In the first place, as described earlier, it is when the 45 upper 2 bits (a6) and (a5) of the address data are of "10" that the data inherent in or specific to a lens are produced from said lens. When the lower 5 bits (a4), (a3), (a2), (a1) and (a0) become "00000", data "11100" for check code are produced from the interchangeable lens 50 to show that said lens has been attached to the camera body 1. Therefore, if the data "11100" are input to the camera body upon designation of the address "1000000" from the camera body 1, it is ensured that the interchangeable lens has been attached. Similarly, as shown 55 in Table 1, if the data "11100" are applied to the camera body 1 upon designation of the address "0100000", it is indicated that an electronic flash has been attached to the camera body 1, and when the data "11100" are applied to the camera body 1 upon designation of the 60 address "1100000", it is shown that a lens accessory has been mounted on the camera body 1.

In the next step, when the address of "1000001" is designated, the address for the ROM in which data for the full aperture value Av0 are stored is to be desig-65 nated, and the data "00010" for the fully open aperture value at F1.4 are fed to the camera body 1. Subsequently, when the address of "1000010" is designated,

data "01111" for the minimum aperture value Av<sub>max</sub>, for example, at F16 are fed to the camera body 1. The above data are equivalent to the aperture value F16 as shown in Table 2. Upon designation of the address for "1000011", there is produced a signal indicating whether or not the interchangeable lens mounted on the camera body 1 is of a lens arranged to produce the distance information described earlier. For example, in the case of the lens of F1.4 with a focal length of 50 mm in Table 1, data of "00000" are produced, since said lens is capable of producing the distance information, while in the case of a lens of F2.0 with a focal length of 28 mm, data of "00001" are produced, since no distance information is produced therefrom.

Subsequently, when the address "1000100" is designated, the address of the ROM in which the data of the focal length have been stored is to be designated, and since the focal length is 50 mm in the case of the lens of 50 mm F1.4, data "00110" indicating that the focal length is within the range of 40 to 60 mm are produced. Moreover, data for the amount of extension of the lens to be described later are employed as the address data of the ROM for said lens, and based on the above address data, the distance information referred to earlier is produced. It the data for the lens extension amount are "10000", address of "1010000" is designated so as to produce data "11111" corresponding to an infinite distance, and if the lens extension amount data are "11111", address for "1011111" is designated for producing data "00111" corresponding to a distance of 1.4

Meanwhile, in the case where the flash source, e.g. electronic flash is attached to the camera body, if the address of "0100000" is designated, in the similar manner as in the case of the interchangeable lens, check code "11100" is applied to the camera main body, and 5 thus, it is ensured that the electronic flash has been attached to the camera body. Subsequently, address of "0100001" is designated, in which address, the data for the minimum guide number are stored so as to produce, for example, data for the minimum guide number 14. In 10 the next step, when address of "0100010", in which, data for the maximum guide number are stored, is designated, for example data "10010" for the guide number 28 are produced. Thereafter, if the address of "0100011", in which, data for orientation characteristic 15 are stored, is designated, data of "00001" are produced in this instance. The data indicate that angles are 45° in a longitudinal direction and 60° in a lateral direction.

In the case where a lens accessory has been mounted to the camera body, the check code of "11100" is ap- 20 plied to the camera body upon designation of the address "1100000" for the confirmation that the lens accessory has been attached to the camera body, while, when the data "00011" are applied upon designation of the address "1100001", it is ensured that a tele-con- 25 verter i.e. rear converter has been attached. Similarly, as shown in Table 2, it may be ensured that a bellows has been attached to the camera body, if the data are "00001", a reverse adaptor, if the data are "00010", and

able lens 5 in this embodiment by way of example, and also to FIG. 4 showing a time-chart for explaining functionings of the arrangement of FIGS. 3(a) and 3(b).

In FIGS. 3(a) and 3(b), there is provided at the side of the camera body 1, a reference clock pulse output circuit OSC which is coupled to a decoder DEC 1 through a counter CNT 1, and also to the lens 5 through a terminal b. A train of clock pulses CP (FIG. 4) from the circuit OSC are applied to the counter CNT 1 and also to the lens 5 via said terminal b. The counter CNT 1 is arranged to count the clock pulses CP, while the decoder DEC 1 decodes data from outputs CB0, CB1 and CB2 of said counter CNT 1, which serve as timing signals TB0 to TB7 shown in FIG. 4. On the other hand, at the side of the interchangeable lens 5 (FIG. 3(b), there are provided a counter CNT 2 and a decoder DEC 2 coupled to each other, and having constructions generally similar to those of the counter CNT 1 and the decoder DEC 1 provided at the side of the camera body 1. The outputs of the decoder DEC 2 form timing signals TL0 to TL7 shown in FIG. 4. Since the outputs of the two decoders DEC 1 and DEC 2 decode the outputs of the counters CNT 1 and CNT 2 which count the same clock pulses CP, similar timing signals are produced therefrom for synchronization of the circuits at the sides of the camera body 1 and the lens 1.

Table 3 given below shows the relation of outputs between the counters CNT 1 and CNT 2 and the decoders DEC 1 and DEC 2.

TABLE 3

| 111000     |            |            |        |            |                           |            |            |            |            |            |            |      |

|------------|------------|------------|--------|------------|---------------------------|------------|------------|------------|------------|------------|------------|------|

| Coun       | ters (CN   | VT 1), (C  | ONT 2) |            | Decoders (DEC 1), (DEC 2) |            |            |            |            |            |            |      |

| CB0<br>CL0 | CB1<br>CL1 | CB2<br>CL2 | СВЗ    | TB0<br>TL0 | TB!<br>TL1                | TB2<br>TL2 | TB3<br>TL3 | TB4<br>TL4 | TB5<br>TL5 | TB6<br>TL6 | TB7<br>TL7 | Step |

| 0 '        | 0          | 0          | 0 -    | 1          | 0                         | 0          | 0          | 0          | 0          | 0          | 0          | SO   |

| 1          | 0          | 0          | 0      | 0          | 1                         | 0          | 0          | 0          | 0          | 0          | 0          |      |

| . 0        | 1          | 0          | 0      | . 0        | 0 .                       | 1          | 0          | 0          | 0          | 0          | 0          |      |

| 1          | 1          | 0          | 0      | 0          | 0                         | 0          | 1          | 0.         | 0          | 0          | Ō          |      |

| 0          | 0          | 1          | 0.     | 0          | 0                         | 0          | 0          | 1          | . 0        | 0          | ō          |      |

| 1          | . 0        | 1          | 0      | 0          | 0                         | 0          | 0          | 0          | 1          | 0          | 0          |      |

| 0          | 1          | 1          | 0      | 0          | 0                         | 0          | 0          | 0          | 0          | 1          | Õ          |      |

| - 1        | 1          | 1          | 0      | 0 -        | 0                         | 0          | 0          | 0          | Ō.         | 0          | ĭ          |      |

| 0 .        | 0          | 0          | Ī      | 1          | 0                         | 0          | 0          | 0          | 0          | 0          | ō          | SI   |

| 1          | 0          | 0          | 1      | 0          | 1                         | 0          | 0          | 0          | Ô          | ō          | ō          | ٠.   |

| 0          | 1          | 0          | 1      | 0          | 0                         | -1         | 0          | 0          | 0          | 0          | ō          |      |

| 1          | 1          | 0          | 1      | 0          | 0                         | 0          | 1          | 0          | 0          | .0         | Ô          |      |

| 0 .        | 0          | 1          | 1      | 0          | 0                         | 0          | 0          | 1          | 0          | ō          | õ          |      |

| 1          | 0          | -1         | 1      | 0          | 0                         | 0          | 0          | 0 -        | 1          | ó          | ō          |      |

| 0          | 1          | 1          | 1      | 0          | 0                         | 0          | 0          | Ó          | 0          | 1          | Õ          |      |

| 1          | 1          | 1          | 1      | 0          | 0                         | 0          | 0          | Õ          | ō          | Ô          | ĭ          |      |

an extension ring, if the data are "00100".

winder (or motor-drive) is mounted on the camera body, the winder applies data specific to the winder to the camera body, if the upper 2 bits (a6) and (a5) are "00". In the similar manner as in the other camera accessories, upon designation of the address "0000000", 55 the check code "11100" is applied to the camera body, and when the address of "0000001" is designated, data for the number of frames which can be exposed for photographing per second are input. As shown in Table 2, if the data are "00000", the number of frames is one 60 frame/sec. and if the data are "01100", the number of frames will be seven frames/sec.

Reference is made to FIGS. 3(a) and 3(b) showing a circuit diagram representing part of a circuit for the address output device 13 and part of a circuit for the 65 data input device 14 at the side of the camera body 1, and a specific example of the data output device at the side of the camera accessory, which is an interchange-

When a read-in start signal is produced in the camera Although not particularly shown in Table 1, if a 50 body 1, a flip-flop F1 connected to the counter CNT 1 and another flip-flop F2 is set (FlQ in FIG. 4), with the counter CNT 1 released from the reset state, whereby the counter CNT 1 starts counting of the clock pulses, while the decoder DEC 1 starts producing the timing signals TB0 to TB7. It is to be noted here that, since the outputs of the decoders DEC 1 and DEC 2 to AND circuits AN2 and AN6 respectively coupled therewith are "High" when the outputs of the counters CNT 1 and CNT 2 are "000", the AND circuits AN2 and AN6 are so arranged that the timing signals TB0 and TL0 of "High" level are output only after the starting of the counting by the counters CNT 1 and CNT 2.

Firstly, in a step S0 in FIG. 4 (i.e. a period from output of the read-in start signal to output of the first timing signal TB7), the address data "1000000" are latched in a register REG 1 coupled with a shift register SR1 which is connected to the flip-flop F2 through an AND circuit AN1, and also to an AND circuit AN11.

and further to a shift register SR3 provided at the side of the lens 5 via a terminal c, at the timing by which the timing signal TB1 rises to "High", while said data are further latched in the shift register SR1 at the timing by which the output of the AND circuit AN11 falls to 5 "LOW", with the timing signal of TB7 being produced. During the period for the above step S0, other circuits are out of functionings, since Q output of the flip-flop F2 (F2Q in FIG. 4) is "Low". When the step S0 is shifted to a step SI, i.e. upon counting of a ninth clock 10 pulse CP, the D input of the flip-flop F2 is taken in due to rising of the output CB3 of the counter CNT 1 to "High" (CB3 in FIG. 4), with the output Q of the flipflop F2 becoming "High" (F2Q in FIG. 4), whereby the AND circuit AN1 is enabled to feed the clock pulses to 15 the shift register, while the circuit at the side of the interchangeable lens 5 is released from the reset state through a terminal d. The shift register SR1 successively produces serially per one bit, the earlier described address data "1000000" latched in synchroniza- 20 tion with the positive edge of the clock pulses from the terminal c. The data thus produced are successively taken into the shift register SR3 at the side of the interchangeable lens 5 in synchronization with the negative edge of the clock pulses so as to be sequentially pro- 25 duced from terminals La0, La1, La2, La3 and La4 (La0 to La4 in FIG. 4) of the shift register SR3. Thus, at the timing by which a terminal TL5 for a flip-flop F3 coupled with a flip-flop F4 and connected, at its D input, to the terminals La4 and La3 through an AND gate AN5, becomes "High", the outputs of the terminals La4 and La3 become "10", with the output of the AND circuit AN5 assuming a "High" state, and thus, the Q output of the flip-flop F3 receiving the above output at its D input becomes "High" (F3Q in FIG. 4).

At the positive edge of the signal at the terminal TL7 of the decoder DEC 2 on the side of the lens 5, the data of the output terminals La4, La3, La2, La1 and La0 of the shift register SR3 bears the data of the lower 5 bits ("00000" in the case of the step S1) of the address data, 40 and thus, the address "00000" of the ROM 51 is designated. By the above address designation, the data for the check code "11100" earlier described are produced from the ROM 51.

The above data from the ROM 51 are latched in the 45 shift register SR4 due to a positive edge at a terminal TL7.

Since the O output of the flip-flop F3 has become "High" at the time point of the timing pulse TL5, when flip-flop F4 takes in the Q output of the flip-flop F3 to render said Q output to be "High" (F4Q in FIG. 4), whereby a switch circuit GS coupled to said Q output and the output of the shift register SR4 and also, to the input of a shift register SR2 at the side of the camera 55 body through a terminal e is conducted, and thus, the above data "11100" are brought into a state where they may be produced from the terminal e.

The data taken in the shift register SR4 are applied to the terminal e in the order of "11100" through said 60 switch circuit GS in synchronization with the clock pulses, and at the side of the camera body 1, the above data are taken into the shift register SR2 (Bb0 to Bb4 in FIG. 4) in synchronization with the negative edge of the clock pulses. In the above case, since the Q output of 65 the flip-flop F2 has become "High", a flip-flop F5 connected to the flip-flop F2, and to the shift register SR2 and a register REG 2 through AND circuits AN3 and

AN4 respectively, has its Q output at "High" when the subsequent timing pulse TB0 rises to "High" (positive edge of TB0 at the step S2). Accordingly, after the step S2, the AND circuits AN3 and AN4 are enabled, and at the positive edge of pulse TB5, the output of the shift register SR2 is latched in the register REG 2.

In the step S2, the data "11100" as described above are taken in, and simultaneously, the subsequent address data "1000001" are transferred to the interchangeable lens 5, while, in a step S3, the lens data "00010" by the above address designation are transferred to the camera body 1, and also, the subsequent address data "1000010" are transferred to the lens 5. Thereafter, addresses and data are successively transferred in a similar manner.

As shown in Table 1, since the upper address of the lens is "10", this is arranged to be judged by the data output device 50 of the lens 5 for conduction of the switch circuit GS, but in the case of other camera accessories such as the electronic flash, lens accessories, motor-drive, etc., input voltage level for the input terminal of an AND circuit AN5 is transformed in correspondence with each accessory as shown in FIG. 5. More specifically, arrangements are so made that, in the case of an electronic flash, the upper address data are "01", and therefore, upon input of this signal, the output of an AND circuit AN5-1 becomes "High", and in the case of a lens accessory, since the address data are "11", the output of an AND circuit AN5-2 becomes "High", while in the case of a motor-drive, the address data are "00", and therefore, the output of an AND circuit AN<sub>5-3</sub> becomes "High". Other circuit constructions in these accessories are generally similar to those in the interchangeable lens 5.

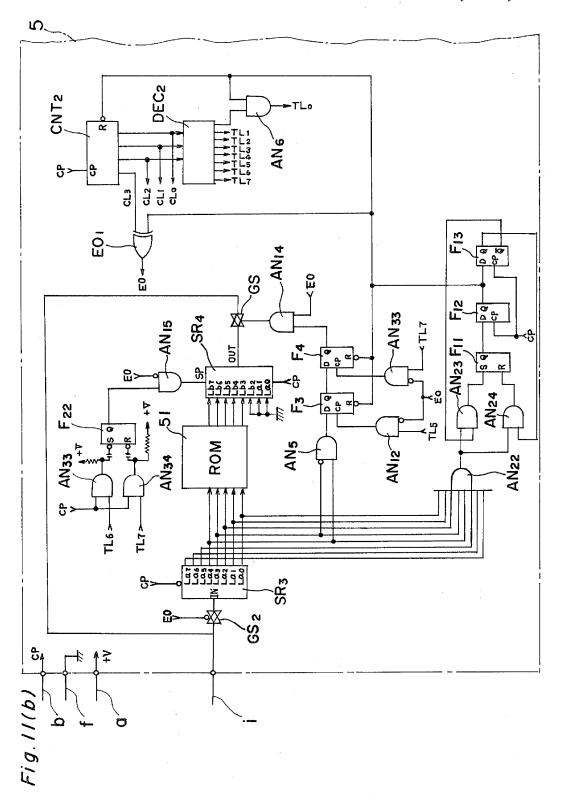

In the circuit arrangement of FIG. 3, it is necessary to provide six terminals in total between the camera body 1 and the interchangeable lens 5, i.e. the clock pulse terminal b, address data terminal c, power source terminal a, ground terminal f, reset terminal d, and data terminal e. However, the number of such connecting terminals should preferably be as small as possible. Therefore, in a modification shown in FIGS. 6(a) and 6(b) and 7(a) and 7(b), the number of terminals is reduced by one through common use of the terminals c and e for the address data and the data. Meanwhile, in another modification shown in FIGS. 8(a) and 8(b), and 9 and 10, the number of terminals is similarly reduced by one through common use of the terminals for the address data and the resetting.

Although the circuit constructions in FIGS. 6(a) and the subsequent timing pulse TL0 rises to "High", the 50 6(b) are fundamentally similar to those in FIGS. 3(a) and 3(b), with like parts being designated by like reference symbols and numerals, since the address data transfer line and data transfer line are arranged to be common at a terminal g, there is added a circuit for changing over the timings for delivery of the addresses and the data, and it is so arranged that, to the terminal g, the address data are fed when the terminal CB3 of the counter CNT 1 is "High" (steps S1, S3, S5, ...), while the data of the camera accessories are applied, when the terminal CL3 of the counter CNT 2 is "High" (steps S2, S4, S6, . . . ).

In the step S0, the address data are latched in the register REG 1 at the time point where the timing signal TB1 rises "High" in the similar manner as in FIGS. 3(a) and 3(b) and further, the address data from the register REG 1 are latched in the shift register SR1 at the time point where the output of the AND circuit AN11 falls "Low". In the next step S1, a switch circuit GS1 inserted between the output of the shift register SR1 and the terminal g and further coupled with the input of the shift register SR2 through a switch circuit GS3, is conducted, since the terminal CB3 of the counter CNT 1 becomes "High", and in synchronization with the clock 5 pulses from the AND circuit AN1, the address data latched in the shift register SR1 are successively output to the terminal g per one bit. In the above case, the switch circuit GS3 is in a state of non-conduction contrary to the above switch circuit GS1, and there is no 10 possibility that the address data are input to the shift register SR2. The address data applied to the lens 5 through the terminal g are sequentially fed into the shift register SR3 (La0 to La4 in FIG. 7) due to conduction of a switch circuit GS2 inserted between the terminal g 15 and the input of said shift register SR3, owing to the "Low" state of the terminal CL3 of the counter CNT 2, and by signal from the AND circuit AN15 coupled to the shift register SR4 at the positive edge at the terminal TL7 of the decoder DEC2, data from the ROM 51 are 20 latched in the shift register SR4 (SR4 Latch in FIG. 7). Meanwhile, by the timing at which the timing pulse TL5 becomes "High", the output of an AND circuit AN<sub>12</sub> coupled to the flip-flop F3 rises, and in this case, if the upper 2 bits of the address data are of "10", the Q 25 output of the flip-flop F3 becomes "High" (F3Q in FIG. 7), since the output of the AND circuit AN5 is in the state of "High". In the step S2, the terminal CL3 of the counter CNT 2 becomes "High" (CL3 in FIG. 7), with the terminal CB3 of the counter CNT 1 becoming 30 "Low" (CB3 in FIG. 7). When the terminal CL3 becomes "High", the switch circuit GS2 is rendered to be non-conductive, while, by the rising of the terminal CL3 to "High", the flip-flop F4 takes in the D input, i.e. the Q output of the flip-flop F3 and thus, the Q output 35 of the flip-flop F4 becomes "High" (F4Q in FIG. 7). Accordingly, the output of an AND circuit AN14 inserted between the Q output of the flip-flop F4 and the switch circuit GS becomes "High" for conduction of said switch circuit GS so as to allow the data from the 40 shift register SR4 to be applied to the terminal g. On the other hand, due to falling of the output of the terminal CB3 of the counter CNT 1 to "Low", the switch circuit GS1 becomes non-conductive, with the switch circuit GS3 being conducted. Thus, in synchronization with 45 the clock pulses from the AND circuit AN4, the shift register SR2 takes in the data from the shift register SR4 (Bb0 to Bb4 in FIG. 7), and by the rising signal of the terminal TB5 through the AND circuit AN3, the data taken in the shift register SR2 are latched in the register 50 REG 2 (REG 2 Latch in FIG. 7). Meanwhile, at the step S2, since the subsequent address data are taken in the shift register SR1 at the timing of falling of clock pulses when the terminal TB7 becomes "High", the address is applied from the terminal g to the lens 5 at the 55 step S3, and thereafter, functionings similar to those in the previous steps S1 and S2 are repeated.

In FIGS. 8(a) and 8(b), there is shown one example of the circuit construction in which the address data transfer line c and the reset signal line d in FIGS. 3(a) and 60 3(b) are replaced by a common line h, while FIGS. 9 and 10 illustrate time-charts for the circuit arrangement of FIGS. 8(a) and 8(b).

In the arrangement of FIGS. 8(a) and 8(b), upon input of the read-in start signal (start in FIG. 9), the flip-flop 65 F1, and a flip-flop F9 coupled with a flip-flop F10 and connected, through an OR circuit OR1, to a multiplexer MP1 inserted between the register REG 1 and the shift

register SR1, are set (F1Q, F9Q set in FIG. 9) for starting functions. As the Q output of the flip-flop F9 becomes "High", the output of the OR circuit OR1 also becomes "High", and the multiplexer MP1 produces as an output, the input "1111111" from its portion A, and this output is latched in the shift register SR1 by the falling (SR1 Latch in FIG. 9) of the output of an AND circuit AN11 connected to said shift register SR1. Since the flip-flop F9 is reset (F9Q in FIG. 9) by the negative edge of the timing pulse TB7, the multiplexer MP1 thereafter produces the ordinary address data (output of the register REG 1) from a portion B. It is to be noted here that the data "11111111" from the portion A of the multiplexer MP1 are the data not corresponding to the address of any of the camera accessories, and therefore, by judging the input of the above data, the circuit in the camera accessory 5 is to be released from the reset state.

The data latched in the shift register SR1 are successively produced from the terminal h per bit based on the clock pulses from the AND circuit AN1 so as to be taken into the shift register SR3 at the side of the interchangeable lens 5 (La0 to La7 in FIG. 9). Thus, when the terminal La7 has become "High", all the outputs of the shift register SR3 become "High", and the output of an AND circuit AN22 coupled to the shift register SR3 and the ROM 51 rises to "High", and in this case, a flip-flop F15 coupled to the AND circuit AN22 through flip-flops F14, F13, F12 and F11 and AND gates AN23 and AN24 as shown, is reset. Since the  $\overline{Q}$ output thereof is "High", the output of the AND circuit AN23 rises to set the flip-flop F11 (F11Q in FIG. 9). Thus, the Q output of the flip-flop F12 becomes "High" by the positive edge of the next clock pulse (F12Q in FIG. 9) whereby the circuit is released from the reset state. Subsequently, by the positive edge of the clock pulses, the Q outputs of the flip-flops F13, F14 and F15 sequentially become "High" (F13Q, F14Q, F15Q in FIG. 9). As the Q output of the flip-flop F15 becomes "High" and the  $\overline{Q}$  output thereof becomes "Low", the AND circuit AN23 is disabled, with the AND circuit AN24 being enabled on the contrary, and upon subsequent rising of the output from the AND circuit AN22 to "High", the flip-flop F11 is brought into a state for resetting. Subsequently, reception and delivery of the address and data are effected in the similar manner as in FIGS. 3(a) and 3(b).

The read-in completion signal is produced by the timing signal TB6 as described later, whereby the flipflop F10 is set (F10Q in FIG. 10), and the data "11111111" from the portion A are produced from the multiplexer MP1. The above data are latched in the shift register SR1 by the output of the AND circuit AN11 (SR1 Latch in FIG. 10) so as to be fed from the terminal h to the shift register SR3 at the side of the lens 5. When the output of the AND circuit AN22 becomes "High" (AN22 in FIG. 10), since the AND circuit AN24 is enabled as described earlier, the flip-flop F11 is reset (F11Q in FIG. 10), and the Q output of the flipflop F12 becomes "Low" by the next clock pulse (F12Q in FIG. 10) to bring the circuit at the side of the lens 5 into a reset state. Thus, the Q outputs of the flip-flops F13, F14 and F15 sequentially become "Low" based on the clock pulses (F13Q, F14Q, F15Q in FIG. 10). It should be noted here that hatched portions La0 to La7 in FIG. 10 show that these outputs may take any of the "High" and "Low" states, but since there is no possibility that all become "High" except for the time for out-

putting the read-in signal completion signal, the above functioning is not affected.

On the other hand, at the side of the camera body 1, upon input of the read-in completion signal, a flip-flop F6 coupled to the flip-flops F1 and F2 through flip-flops 5 F7 and F8 and an AND circuit AN21 via a capacitor as shown, is set (F6Q in FIG. 10), and by the negative edge of the next timing pulse TB7, the Q output of the flipflop F7 becomes "High" (F7Q in FIG. 10), and further, by the negative edge of the subsequent timing pulse 10 TB7, the Q output of the flip-flop F8 becomes "High" (F8Q in FIG. 10). Thus, clock pulse is output from the AND circuit AN21, and by the negative edge of this clock pulse, the flip-flops F1, F2, F6, F7, F8 and counter CNT 1 are reset, with the circuit at the side of 15 the camera body 1 being also reset to wait for the subsequent read-in start signal to be input.

In the foregoing embodiment of FIGS. 6(a) and 6(b), the address data transfer line and the data transfer line are combined for common use, while in the embodiment 20 of FIG. 8, the address data transfer line and the reset signal line are replaced by the common line so as to reduce the number of electrical connecting terminals between the camera body 1 and the camera accessory to five pieces.

In the arrangement of FIGS. 11(a) to 11(b) to be described hereinbelow, there is shown a further modification in which the address data transfer line, data transfer line, and reset signal line are combined for common use so as to further reduce the number of the electrical 30 connection terminals to four pieces. FIG. 12 is a timechart during starting of the read-in function of the circuit of FIGS. 11(a) and 11(b), while FIG. 13 shows a time-chart at the completion of the reading-in function of the circuit of FIGS. 11(a) and 11(b).

In the arrangement of FIGS. 11(a) and 11(b), upon input of the read-in start signal, the flip-flops F1 and F9 are set (F1Q, F9Q in FIG. 12) in the similar manner as in FIGS. 8(a) and 8(b), and the counter CNT 1 is rethe circuit. In the above case, since the flip-flop F9 is in the set state, the output of the OR circuit OR1 becomes "High", and the fixed data A of "11111111" are produced from the multiplexer MP1.

A flip-flop F21 coupled, at its Q terminal, to the 45 AND circuit AN11 connected to a parallel input/serial output change-over terminal SP of the shift register SR1 and, at its set and reset terminals, to AND circuits AN31 and AN32 through corresponding capacitors, is set by the negative edge of the output of AND circuit 50 AN31 and reset by the negative edge of the output of AND circuit AN32, while the AND circuit AN11 becomes "High" at the timing shown by AN11 in FIG. 12, since it is enabled when the terminal CB3 of the counter CNT 1 is "Low". The shift register SR1 which receives 55 the above output is parallely applied with the output of the multiplexer MP1 by the positive edge of the clock pulses while the parallel input/serial output changeover terminal SP thereof is in the "High" state, while, during the period in which the output (i.e. the change- 60 over terminal SP) of the AND circuit AN11 is in the "Low" state, the register SR1 serially produces the data at the output terminals in synchronization with the positive edge of the clock pulses.

At the time point where the step S0 is shifted to the 65 step S1, the flip-flop F9 is reset (F9Q in FIG. 12), with the output of the OR circuit OR1 becoming "Low", and thereafter, the address data from the register REG

16