## US005194868A

# United States Patent [19]

## Bahng et al.

[11] Patent Number:

5,194,868

[45] Date of Patent:

Mar. 16, 1993

| [54] | DUAL SLO              | OPE INTEGRATING A/C .<br>ER                               |

|------|-----------------------|-----------------------------------------------------------|

| [75] | Inventors:            | Sam-Yong Bahng; Suk-Ki Kim, both of Buchun, Rep. of Korea |

| [73] | Assignee:             | Samsung Electronics Co., Ltd.,<br>Suweon, Rep. of Korea   |

| [21] | Appl. No.:            | 739,674                                                   |

| [22] | Filed:                | Aug. 2, 1991                                              |

| [30] | Foreig                | n Application Priority Data                               |

| Apı  | r. 13, 1991 <b>[K</b> | R] Rep. of Korea 91-5945                                  |

| [52] | U.S. Cl               |                                                           |

| [56] |                       | References Cited                                          |

|      | U.S. 1                | PATENT DOCUMENTS                                          |

|      |                       | 1977 Neumann                                              |

| 4,568,913 | 2/1986  | Evans          | 341/118 |

|-----------|---------|----------------|---------|

| 4,633,221 | 12/1986 | Bradshaw et al | 341/167 |

| 4,707,680 | 11/1987 | Sparrowhawk    | 341/133 |

| 4,739,305 | 4/1988  | Naito          | 341/118 |

| 4,771,265 | 9/1988  | Okui et al     | 341/167 |

| 4.851.839 | 7/1989  | Reinke         | 341/128 |

Primary Examiner—Marc Hoff

Attorney, Agent, or Firm-Cushman, Darby & Cushman

## [57] ABSTRACT

An improved dual slope integrating analog-to-digital converter for use in a Digital Multi-Meter includes an input portion, an A/D core portion, and a digital portion. The A/D core portion includes an auto zero function capability for automatically compensating for any existing offset voltages in various measurement modes such as voltage, resistance, or current measurement modes. The improved A/D converter of the present invention operates at high speed and with high resolution

## 4 Claims, 7 Drawing Sheets

FIG.1D (PRIOR ART)

3 **SWITCH** SII FIG. 3 <u>ပ</u> 9

FIG. 4

FIG.5

FIG.6

## DUAL SLOPE INTEGRATING A/C CONVERTER

#### BACKGROUND OF THE INVENTION

## 1. Field of the Invention

The present invention relates to an A/D converter for converting an analog signal into a digital signal. Particularly, an A/D converter with a high resolution of "X10 Mode" which is capable of providing a Ratio Metric Reading by cancelling an offset voltage in response to an application of a "Auto-Zero function.

## 2. Description of the Art

In general, a resolution of a dual slope integrating A/D converter employed in a Digital Multi-Meter (DMM) is 3½ digits. But, in a dual slope A/D converter having a 3½ digit resolution, a residual electric charge zero crossing can be charged by a capacitor of predetermined capacitance to multiply a voltage by ten times. The multiplied value is deintegrated again such that the 20 resolution of the dual slope A/D converter is 4½ digits or more.

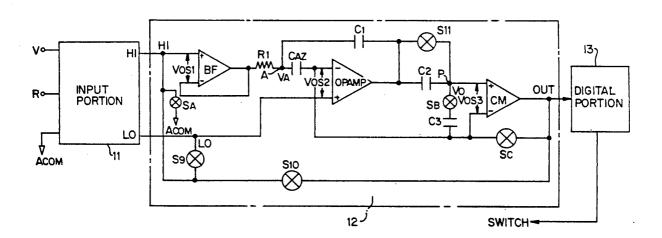

The above mentioned mode is called "X10 Mode". A conventional dual slope integrating A/D converter applying the X10 Mode is shown in FIG. 1A. This  $_{25}$ converter comprises input portion 1, A/D core portion 2, and digital portion 3.

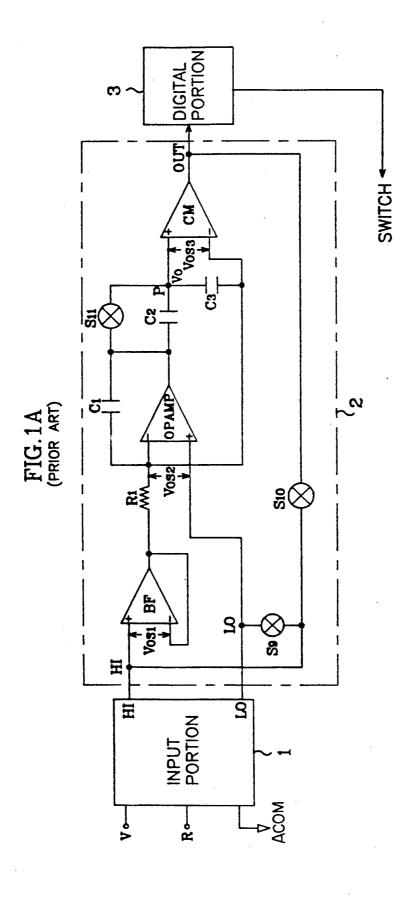

For a voltage measurement, input portion 1 will include mainly two switches S1 and S2 and a reference voltage  $\pm V_{REF}$  as shown in FIG. 1B. For a resistance 30 Therefore, you will find that the voltage  $V_o$  at node P measurement, input portion 1 will include mainly a supply power source, switches S<sub>3</sub> to S<sub>8</sub>, a reference resistor  $R_{fef}$ , a capacitor  $C_x$ , and a measured resistor  $R_x$ as shown in FIG. 1C.

A/D core portion 2 comprises a buffer BF, and oper- 35 ational amplifier (OP AMP), a comparator CM, switches S<sub>9</sub> to S<sub>11</sub>, a resistor R<sub>1</sub>, and a capacitor C<sub>1</sub> to

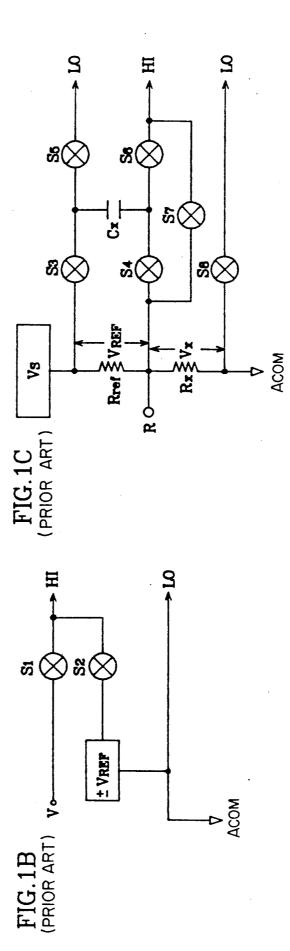

As shown in FIG. 1D, digital portion 3 comprises a clock signal input portion 4, a zero crossing detecting 40 portion 5, a logic control portion 6, a decoder/resistor 8, and a drive/display portion 9.

The conventional dual slope A/D converter comprising the above-mentioned constituent elements for performing a voltage measurement operation, connects the 45 portion measuring voltage between a power source terminal V and a common terminal Acom in FIG. 1B. Reference voltage  $\pm V_{REF}$  is employed as the voltage for discharging the electric charge charged by integrating capacitor C<sub>1</sub> of A/D core portion 2 shown in FIG. 50 1A by way of the common terminal. In this manner, the discharged electric charge quantity can be regulated.

If a measured voltage  $C_{IN}$  has a negative polarity, a reference voltage  $\pm V_{REF}$  is supplied, and if the measured Voltage V<sub>IN</sub> is a positive polarity, a reference 55 The amount of voltage change at the moment a zero voltage - V<sub>REF</sub> is supplied.

For performing a resistance measurement, input portion 1 resembles a ratio metric reading circuit. A supply power source V<sub>s</sub>, a reference resistor R<sub>ref</sub>, a resistance measuring portion (that is, resistor Rx), and common 60 and terminal A<sub>COM</sub> are all connected in series as shown in FIG. 1C. As a current flows through this series circuit, a voltage drop across reference resistor R<sub>ref</sub> will be represented as Vref and a voltage drop across resistor  $R_x$  will be represented as  $V_x$ .

Reference resistor  $R_{ref}$  is connected to capacitor  $C_x$ through switches S<sub>3</sub> and S<sub>4</sub>. One terminal of capacitor  $C_x$  is connected to an output terminal LO through

switch  $S_5$ . The other terminal of capacitor  $C_x$  is connected to an output terminal HI through switch S6.

As input terminal R is connected to output terminal HI through switch S7 and terminal Acom is connected to output terminal LO through switch S<sub>8</sub>, the voltage charge in capacitor  $C_x$  is deintegrated.

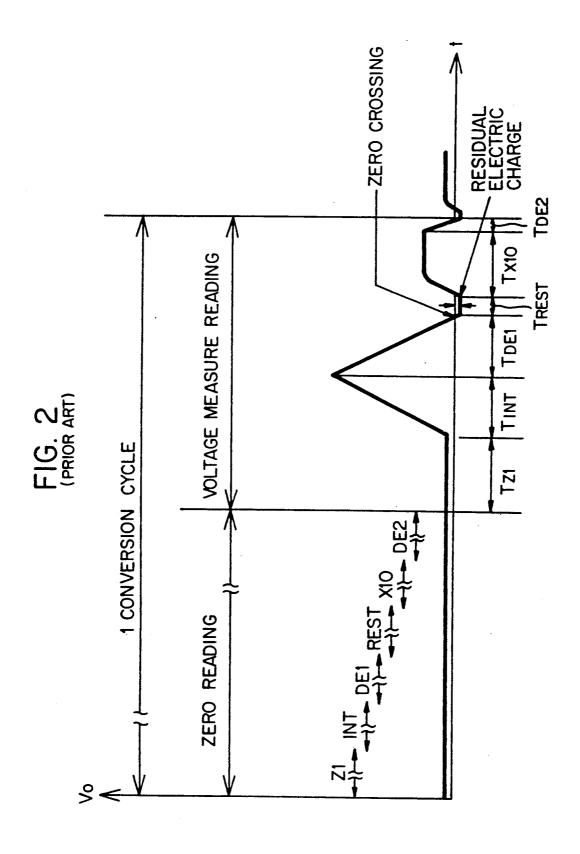

On the other hand, the conversion operation is performed by a conversion cycle defined as shown in FIG. 2. The conversion cycle includes a zero integration phase Z1, an integration phase INT, a first deintegration phase DE1, a REST phase, X10 phase, and a second deintegration phase DE2.

In order to display the difference between the value converting the offset voltage and the value converting the following input  $V_{IN}$  (the measured voltage), first the power source terminal V must be shorted at the common terminal (that is, the zero reading). Then it can receive the input  $V_{IN}$ .

Let us define the operating time during zero integration phase ZI as Tzi. During a voltage measurement operation, if switches So and Sin of A/D core portion 2 in FIG. 1A are closed during zero integration phase Z1, the voltage Vo at node P during zero integration phase Z1 can be expressed by the following equation.

$$V_o|T_{ZI} = \frac{(V_{os1} - V_{os2})}{R_1 \cdot C_1} = T_{ZI} + (V_{os2} + V_{os3})$$

(1)

varies with a change in TzI.

Let us now define the operating time during integration phase INT as TINT.

If switch S<sub>1</sub> in FIG. 1B is closed during integration phase INT, a current will flow through buffer BF, resistor  $R_1$  and capacitor  $C_1$  of A/D core portion 2 in FIG. 1A. As a result, the voltage  $V_0$  at node P is changed. At this time, the change  $(\Delta V_0)$  is expressed by the following equation:

$$V_o|T_{INT} = \frac{(V_{IN} - V_{os1} + V_{os2})}{R_1 \cdot C_1} T_{INT}$$

(2)

The first deintegration phase DE1 is operated from the application of reference voltage  $-V_{REF}$  till the beginning of the zero crossing.

Let us define the operating time in first deintegration phase DE1 as  $T_{DE1}$ . The change  $(\Delta V_o)$  of voltage  $V_o$  at node P can be expressed by the equation:

$$\Delta V_o|T_{DE1} = \frac{(-V_{REF} - V_{os1} + V_{os2})}{R_1 \cdot C_1} T_{DE1}$$

(3)

crossing becomes "0" can be expressed by the equations:

$$V_o|T_{INT}+V_o|T_{DE1}=0 (4)$$

$$T_{DE1} = \left(\frac{-V_{IN} - V_{os1} + V_{os2}}{V_{REF} + V_{os1} - V_{os2}}\right) T_{INT}$$

(5)

In Eq. 5, if reference voltage  $(V_{REF})$  is regulated and  $V_{REF} + V_{os1} - V_{os2}$  equals  $V_{REF}$ , Eq. 5 can be expressed by the equation:

15

$$T_{DE1} = \frac{V_{IN} - V_{os1} + V_{os2}}{V_{REF}'} \tag{6}$$

Therefore, if a zero reading is performed first and

$$T_{DE(zero\ reading)} = \frac{(V_{os1} - V_{os2})}{V_{REF}} T_{INT}$$

the offset voltage can be cancelled by  $T_{DE1}-T_{DE}(zero$ reading).

That is,  $T_{DE}$  is expressed by the equation.

$$T_{DE} = \frac{V_{IN}}{V_{REF}} T_{INT},$$

where  $V_{\textit{REF}}$  equals  $V_{\textit{REF}} + V_{\textit{os2}}$ , and  $T_{\textit{INT}}$  is a fixed

Next, let us define the operating time during the 20 REST phase as TREST. If switch So of A/D core portion 2 in FIG. 1A is closed during the REST phase, the residual electric charge stored in capacitor S<sub>3</sub> will be kept during the REST phase.

At this time, the voltage across capacitor C1 becomes 25 the same voltage as that across capacitor C<sub>3</sub>.

During the X10 phase, switch S10 of A/D core portion 2 is closed and switch  $S_{11}$  is opened. Then, the output of comparator CM is fedback to buffer BF and operational amplifier OP AMP as the residual electric 30 It should be noted that charges in capacitor C<sub>3</sub> is transferred to capacitor C<sub>2</sub>. The multiplied voltage at node P varies with the capacitance of capacitors C<sub>2</sub> and C<sub>3</sub>.

As the capacitance of capacitor C3 reaches a value ten times greater than the capacitance of capacitor C<sub>2</sub>, the 35 voltage applied across capacitor C2 becomes ten times greater than that across capacitor C3.

The Second integration phase DE2 discharges the multiplied voltage Vo at node P and counts the time for zero crossing to begin. As the counted time and time 40  $T_{DE1}$  for first deintegration phase DE1 is calculated, a resolution of X10 can be obtained.

The operating condition of the switches in each conversion cycle is shown by the following table 1.

TABLE 1 The operating condition of the switches during each conversion cycle:

|       | Drawings       |                 |                        |         |                |            |                |                |                |                |                |   |  |

|-------|----------------|-----------------|------------------------|---------|----------------|------------|----------------|----------------|----------------|----------------|----------------|---|--|

|       | F              | IG. 1           | A                      | FIG. 1B |                | FIG. 1C    |                |                |                |                |                |   |  |

|       | Switch         |                 |                        |         |                |            |                |                |                |                |                |   |  |

| Phase | S <sub>9</sub> | S <sub>10</sub> | <b>S</b> <sub>11</sub> | Sį      | S <sub>2</sub> | <b>S</b> 3 | S <sub>4</sub> | S <sub>5</sub> | S <sub>6</sub> | S <sub>7</sub> | S <sub>8</sub> | _ |  |

| ZI    | С              | С               | С                      | О       | 0              | С          | С              | 0              | 0              | 0              | 0              |   |  |

| INT   | О              | О               | С                      | С       | О              | С          | С              | 0              | 0              | C              | С              |   |  |

| DE1   | 0              | 0               | С                      | О       | C              | 0          | 0              | С              | C              | О              | 0              |   |  |

| REST  | С              | 0               | С                      | О       | О              | С          | С              | 0              | О              | 0              | 0              | _ |  |

| X10   | 0              | С               | 0                      | О       | О              | C          | C              | 0              | О              | О              | О              | J |  |

| DE2   | 0              | 0               | С                      | 0       | С              | 0          | О              | С              | С              | 0              | 0              | _ |  |

C represents a switch is closed, and O represents a switch is opened

Up to now we have described the operation for a volt- 60 age measurement operation. A conversion cycle for a resistance measurement operation progresses very much like that for a voltage measurement operation.

For a resistance measurement operation, during the zero integration phase Z1, the measuring register R<sub>x</sub> is 65 connected between input terminal R and common terminal ACOM as shown in FIG. 1C such that supply power source V<sub>s</sub> is applied through reference resistor

$R_{ref.}$  The current  $I_s$  through measuring resistor  $R_x$  is therefore expressed by the following equation:

$$I_{s} = \frac{V_{s}}{R_{ref} + R_{x}}$$

Switches S<sub>5</sub> and S<sub>6</sub> are closed during the integration phase INT such that voltage Vx applied across measuring resistor  $R_x$  is integrated.

Voltage  $V_{REF}$  applied across reference resistor  $R_{REF}$ in FIG. 1C is expressed by the equation:

$$V_{REF} = \frac{V_{s}}{R_{ref} + R_{x}} R_{ref}$$

Switches S<sub>5</sub> and S<sub>6</sub> are closed during the first deintegration phase DE1 such that voltage Vo at node P integrated by voltage  $V_x$  is discharged again.

The first deintegration phase DE1 is operated until the zero crossing begins. At this point, TDE1 is calculated during the first deintegration phase DE1. TDE1 is expressed by the equation:

$$T_{DE1} = \frac{\frac{V_{S}}{R_{ref} + R_{x}} R_{x} - (V_{os1} - V_{os2})}{\frac{V_{S}}{R_{ref} + R_{x}} R_{ref} + (V_{os1} - V_{os2})} T_{INT}$$

$$\frac{V_{s}}{R_{ref} + R_{x}} R_{ref}$$

varies in response to a change of measuring resistor  $R_x$ . Therefore, although it provides the zero reading, the offset voltage  $V_{os1-Vos2}$  is not cancelled.

The conventional dual slope A/D converter has the following problems.

The conventional dual slope A/D converter operating as mentioned above is in need of a zero reading step, therefore the conversion time during each conversion cycle is lengthened. As a result, its operating speed is slow. Further, as the offset voltage is not completely cancelled in a ratio metric reading, it is very difficult to obtain high resolution.

#### SUMMARY OF THE INVENTION

The object of the present invention which overcomes the above-mentioned problems of the conventional dual slope A/D converter is to provide a dual slope integrating A/D converter which has a fast operating speed and a resolution of 4½ digits and up.

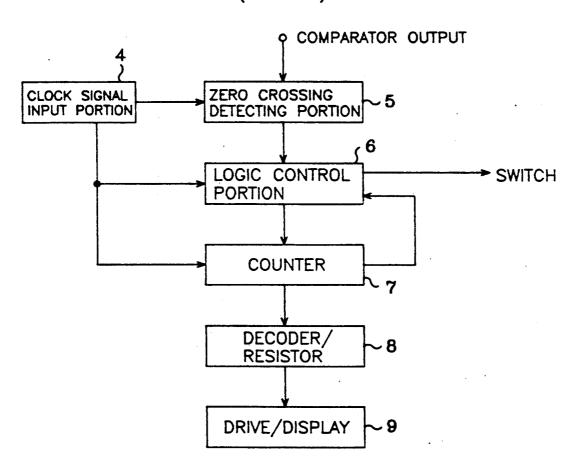

To achieve the above objects, according to the present invention, a dual slope integrating A/D converter comprises an input portion 11; and A/D core portion 12 which includes a buffer BF and an operational amplifier (OP AMP) for respectively receiving an output of input portion 11, a resistor R1 connected to the output terminal of the buffer BF, an auto zero capacitor C<sub>AZ</sub> connected between resistor R1 and operational amplifier OP AMP, a capacitor C<sub>1</sub> for charging an offset voltage and integrating the input voltage using resistor R1, a capacitor C2 for amplifying the voltage Vo at node P with a residual electric charge, a capacitor C<sub>3</sub> for charging the residual electric charge, a comparator CM, and a switch  $S_A$  to  $S_c$  and S9 to  $S_{11}$ ; a digital portion 13 for

5

inputting the output of A/D core portion 12 in which swithces SA to SD and S1 to S11 are driven by generated control signals AZ, INT, DE1, REST, Z10, X10, REX, and DE2.

Here, the constitution of input portion 11 includes the 5 same circuits as that of the conventional input portion 1 shown in FIGS. 1B and 1C for voltage and resistance measurement operations, respectively. The constitution of the digital portion 13 of the present invention also includes the same circuit as that of the conventional 10 digital portion 13 shown in FIG. 1D.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The above object and feature of the present invention will be apparent from the following description of the 15 preferred embodiment with reference to the accompanying drawings.

FIG. 1A is a circuit diagram of a conventional dual slope integrating A/D converter.

FIG. 1B is a detailed circuit diagram of an input 20 portion for performing voltage measurements in a dual slope integrating A/D converter.

FIG. 1C is a detailed diagram of an input portion for performing resistance measurements in a dual slope integrating A/D converter.

FIG. 1D is a schematic block diagram of a digital portion for a dual slope integrating A/D converter.

FIG. 2 is a waveform chart showing an output signal of a conventional dual slope integrating A/D converter.

FIG. 3 is a circuit diagram of a dual slope integrating 30 A/D converter of the present invention.

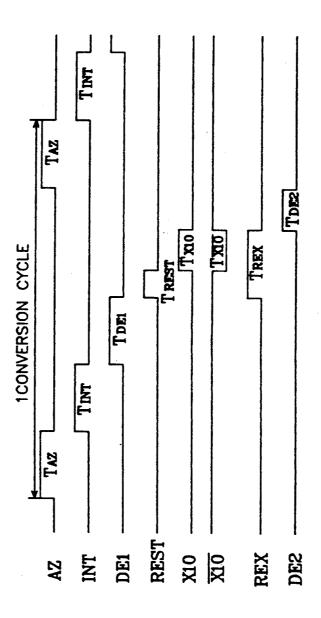

FIG. 4 is a waveform chart of a switch controlling signal.

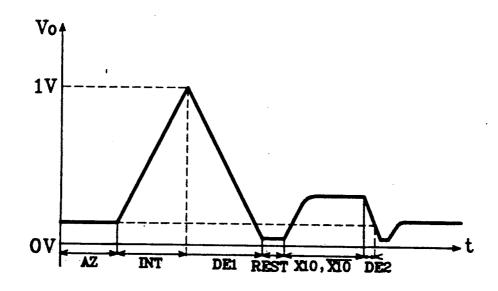

FIG. 5 is a waveform chart illustrating an output signal of the present invention.

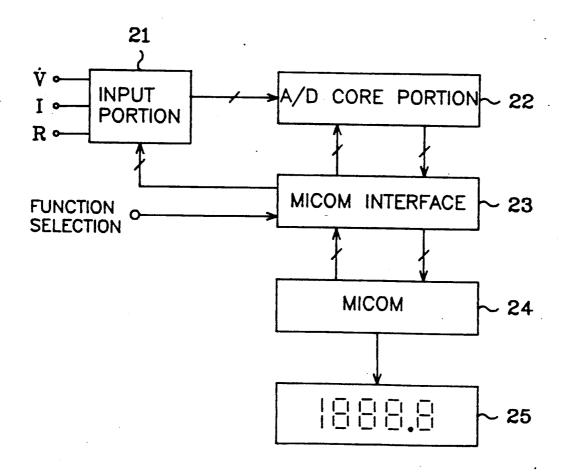

FIG. 6 is a block diagram illustrating a preferred embodiment of applying the present invention to a Digital Multi-Meter (DMM).

#### DESCRIPTION OF THE PREFERRED **EMBODIMENTS**

The constitution, function and effect of the present invention will be explained in detail with reference to the accompanying drawings.

FIG. 3 is a circuit diagram showing a constitution of 45 the dual slope integrating A/D converter of the present invention. FIG. 4 is a waveform diagram showing the controlling signal regulating the switches shown in FIG. 3. FIG. 5 is a waveform diagram showing the output signal of the dual slope integrating A/D con- 50 verter of the present invention.

An offset voltage is charged by auto zero capacitor CAZ and capacitor C1 in A/D core portion 12 during an auto zero phase AZ. Input voltage  $V_{IN}$  is integrated through resistor R1 and capacitor C1 during an integra- 55 voltage Voat node P in the zero crossing is expressed by tion phase INT.

The charged voltage is discharged as reference voltage  $\pm V_{REF}$  during a first deintegration phase DE1. Thereafter, the residual electric charge is charged to capacitor C<sub>3</sub> and proceeds to capacitor C<sub>2</sub> during a 60 REX phase and a REST phase such that the residual electric charge serves to amplify voltage Vo at node P.

First, the operation and constitution of the circuit during the auto zero phase will be explained. Input terminal HI of A/D core portion 12 is connected to 65 common terminal  $A_{COM}$  by switch  $S_A$ . The switch  $S_B$  is opened, and the switch S11 is closed. The output of comparator CM is also feedback to the negative termi6

nal of buffer BF by switch Sc. At such point, capacitor C<sub>3</sub> is separated from the positive input of comparator CM such that capacitor C3 will have no influence on the

Voltage  $V_A$  at node A at time  $T_{AZ}$  is about  $-Vos_1$ . Vos1 represents the offset voltage of buffer BF and a current flows through resistor R1. At that instant, voltage  $V_0$  at node P is expressed by the equation:

$$Vo|T_{AZ}=(V_{os2}+v_{03}) \tag{A}$$

Also, during the integration phase INT, switch S1 shown in FIG. 1B is closed such that the measured input voltage  $V_{IN}$  is integrated. At this point, switches  $S_A$ ,  $S_B$ , and  $S_C$  are opened by switch controlling signals AZ and REX shown in FIG. 4, and voltages  $V_A$  and  $V_Q$ at nodes A and P, respectively during the auto zero phase AZ are as follows:

$$V_A = V_{os1}$$

, and  $V_o = V_{os2} + V_{os3}$

When an input voltage  $V_{IN}$  is applied, the voltage applied across resistor  $R_1$  is  $(V_{IN}-V_{osl})-V_A=V_{IN} V_{osl} - (-V_{osl} = V_{IN})$ , and the offset voltage  $V_{osl}$  is thus cancelled.

At this point, if the change of voltage  $V_o$  at node P is to be represented as  $\Delta V_o$ ,  $\Delta V_o$  can be expressed by the

$$V_o|T_{INT} = \frac{V_{IN}}{R_1 \cdot C_1} \cdot T_{INT},$$

(B)

the voltage at node P being as follows:

$$V_{o}|T_{INT} = \frac{V_{IN}}{R_1 \cdot C_1} T_{INT} + (V_{os2} + V_{os3})$$

(C)

Switch S<sub>2</sub> shown in FIG. 1B is closed by switch controlling signal DE1 during the first deintegration phase DE1. As a result, the electric charge charged to the reference voltage V<sub>REF</sub> is discharged and a zero crossing is performed.

At this point, the zero crossing voltage becomes the voltage at the auto zero phase  $(V_o|T_{AZ}=V_{os2}+V_{os3})$ somewhat the polarity of the reference voltage  $V_{\it REF}$ becomes the opposite of the polarity of the input voltage  $V_{REF}$ , so that the change  $V_o$  of the voltage  $V_o$  at the node P is expressed by the equation:

$$V_o|T_{DE1} = \frac{V_{REF}}{R_1 \cdot C_1} - T_{INT},$$

(D)

the equation:

$$V_o|T_{INT}+T_{DE1}=V_o|T_{AZ}=V_{os2}+V_{0s3}.$$

(E)

Therefore, Eq. (E) can be expressed by the equation:

$$V_o|T_{INT} + T_{DE1} = \frac{V_{IN}}{R_1 \cdot C_1} T_{INT} + (V_{os2} + V_{os3}) +$$

(F)

$$\frac{-VREF}{R_1 \cdot C_1} T_{DE1} = V_{os2} + V_{os3}$$

Thus, if the time of  $T_{DE1}$  satisfying  $V_o|T_{INT}$  $+T_{DE1}=V_O T_{AZ}$  is obtained,  $T_{DE1}$  equals

$$\frac{V_{IN}}{V_{REF}}$$

$T_{INT}$ .

Therefore, the offset voltage is completely cancelled. The offset voltage is cancelled irrespective of the strength of the input voltage VIN or that of the reference voltage  $V_{REF}$ , which is applicable to the ratio <sup>10</sup> metric reading, that is, the resistance measurement operation.

And, during the REST phase, switches S9, S11, and S<sub>B</sub> are closed by the switch controlling signals REST, X10, and REX shown in FIG. 4, such that the residual 15 electric charge is charged by the output voltage at node P after the zero crossing.

During the X10 phase, the switch controlling signals X10 and X10 shown in FIG. 4 close the switch S10 and open the switch S11. However, since the capacitance of 20 capacitor C3 is far more voluminous than that of capacitor C2, the electric charge C3 is far more voluminous than that of capacitor C2, the electric charge of capacitor C3 is transferred to capacitor C2, and the voltage tance value of capacitors C2 and C3.

In order to multiply by ten the voltage Vo at the node P due to the residual electric charge, the capacitance of capacitor C<sub>3</sub> must be ten times in comparison with that of the capacitor  $C_2$ . That is,  $C_3$  must be equal  $10 \times C_2$ .

When the voltage  $V_o$  at the node P is swung by the combination of the capacitors C3 and the auto zero capacitor CAZ during the X10 phase, the swung voltage is again applied to the voltage  $V_A$  at the node A and produces the gain error.

In order to prevent this occurrence, switch  $S_R$  is closed by the switch controlling signal REX shown in FIG. 4 only for the REST phase and the X10 phase and the REX phase is operated.

Also, during the second integration phase DE2, the 40 voltage Vo multiplied by the reference voltage VREF is deintegrated again so that the resolution may be improved.

The operating condition of the switches during a conversion cycle are shown in Table 2.

8 is connected to input portion 21 so as to perform the auto range function.

The constitution of input portion 21 changes according to the selected operating measurement mode (i.e., a voltage V, a resistance R, a current I and so on). The MICOM 24 recognizes the function selection information and changes the constitution of the input portion 21. Here, the circuit must function such that the voltage for converting the common feature in measuring voltage V, resistance R or current I into the appropriate voltage may be output to the A/D core portion 22 and converted in the A/D core portion 22.

The A/D converter, which also includes a reference voltage V<sub>REF</sub> generator, provides the reference voltage V<sub>REF</sub> to the A/D core portion 22 and is regulated with an external minute value.

Also, the A/D core portion 22 converts the inputted voltage and transmits the zero crossing time to the MICOM interface 23.

The MICOM interface 23 transmits all control signals of the MICOM 24 to the input portion 21 and the A/D core portion 22 as well as those signals generated by the A/D core portion 22 to the MICOM 24.

The MICOM 24 generates the respective conversion Vo at the node P is multiplied according to the capaci. 25 cycle according to the constitution of the software, receives and calculates the zero crossing signal, and generates the digital signal or the signal performable display by driving LCD 25.

> Therefore, the present system has the advantage that there can be added digital functions of memory including the specific functions of calculating minimum, maximum, and mean values by classifying a conversion cycle into its respective measuring mode or by utilizing an operation function.

> As explained above, the dual slope integrating A/D converter of the present invention improves the operating speed of the circuit by obviating use of zero reading steps.

> Further, the offset voltage is removed during an auto zero phase such that the dual slope integrating A/D converter of the present invention may be used in a DMM without difficulty.

Also, the present invention is such that the auto zero function can be added with little circuit modification to 45 conventional A/D converter circuits with 3½ digit reso-

TABLE 2

|       |          |             | The c   | peratir | ng con<br>conv |    |    |         | tches      | in a | <u>.                                    </u> |    |           |            |

|-------|----------|-------------|---------|---------|----------------|----|----|---------|------------|------|----------------------------------------------|----|-----------|------------|

|       | Drawings |             |         |         |                |    |    |         |            |      |                                              |    |           |            |

|       |          |             | FIG. 1B |         |                |    | F  | FIG. 1C |            |      |                                              |    |           |            |

|       | Switch   |             |         |         |                |    |    |         |            |      |                                              |    |           |            |

| Phase | \$9      | <b>S</b> 10 | S11     | SA      | SB             | SC | S1 | S2      | <b>S</b> 3 | S4   | <b>S</b> 5                                   | S6 | <b>S7</b> | <b>S</b> 8 |

| AZ    | 0        | 0           | С       | С       | 0              | С  | 0  | 0       | С          | С    | 0                                            | 0  | 0         | 0          |

| INT   | O        | 0           | С       | О       | 0              | 0  | С  | 0       | С          | C    | О                                            | 0  | С         | С          |

| DEI   | O        | 0           | C       | О       | 0              | О  | C  | С       | О          | 0    | С                                            | С  | 0         | О          |

| REST  | C        | 0           | C       | О       | С              | О  | О  | 0       | C          | С    | 0                                            | 0  | 0         | О          |

| REX   | 0        | 0           | C       | 0       | C              | 0  | О  | О       | С          | С    | 0                                            | О  | 0         | О          |

| X10   | О        | C           | О       | 0       | С              | 0  | О  | О       | С          | С    | О                                            | 0  | 0         | 0          |

| X10   | 0        | 0           | C       | O       | С              | О  | 0  | О       | С          | С    | О                                            | 0  | О         | 0          |

| DE2   | 0        | 0           | С       | 0       | 0              | 0  | Ó  | С       | 0          | 0    | С                                            | С  | 0         | О          |

C represents that a switch is closed O represents that a switch is opened

invention. That is, in FIG. 6 is shown the present dual slope integrating A/D converter applied to a DMM of the MICOM type. The reduction function (not shown)

FIG. 6 shows a preferred embodiment of the present 65 lution to serve as an A/D converter with 4½ -digit resolution or more.

> The present invention is not limited to the specifically disclosed embodiments, and variations and modifica

tions may be made without departing from the scope of the present invention.

We claim:

1. A dual slope integrating analog-to-digital converter for cancelling an offset error signal during an <sup>5</sup> auto zero phase of a conversion cycle of operation, said converter comprising:

input means for receiving a measurable input signal and generating a voltage signal in response thereto; 10 means further comprises: analog-to digital core means coupled to said input means and comprising:

- a plurality of selectively disposed switching means responsive to a series of switching control signals, each set of switching control signals in said 15 series corresponding to each of a plurality of phases in said conversion cycle, said analog-todigital core means generating a zero-crossing signal upon completion of the auto phase of said conversion cycle;

- a first capacitor for transferring a residual charge to a second capacitor in response to said offset error signal to multiply said residual charge with said first and second capacitors, after said zerocrossing signal is detected, to generate a reference signal; and

a comparator coupled to said reference signal for generating an output signal in response thereto;

- digital output means for generating said series of switching control signals and for receiving the output signal from said analog-to-digital core means to generate a displayed output in response

- 2. A dual slope integrating analog-to-digital converter as in claim 1, wherein said analog-to-digital core

- a buffer coupled to an operational amplifier;

- a resistor connected to said buffer;

- an auto zero capacitor connected to said resistor and said operational amplifier; and

- an integrating capacitor coupled tot he resistor, the operational amplifier, and the auto zero capacitor for changing the offset error signal and for integrating the voltage signal input from said input means.

- 3. A dual slope integrating analog-to-digital converter as in claim 1, wherein said analog-to-digital core means transfers said residual charge to said second capacitor during a REST phase of the conversion cycle.

- 4. A dual slope integrating analog-to-digital cona voltage at a reference node disposed between 25 verter as in claim 1, wherein the capacitance of said second capacitor is larger than that of said first capaci-

30

35

40

45

50

55

60