# Inter-Chip Supplement to the USB Revision 3.0 Specification

Revision 1.02

May 19, 2014

# **Revision History**

| Revision | Issue Date | Comment                                                                                                                                                                                                                                                                                     |  |  |

|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.0      | 05/03/2012 | Version 1.0 release of the supplement.                                                                                                                                                                                                                                                      |  |  |

| 1.01     | 02/11/2013 | Clarification in Section 2.5.2 about contiguous nature of RRAP and Response Packet behavior.                                                                                                                                                                                                |  |  |

|          |            | Update in Table 2-5 for optional disabling of LUP/LDN and a change in the MPHY.TEST register address space.                                                                                                                                                                                 |  |  |

|          |            | Update in Table 3-2 for value of PM_ENTRY_TIMER and a new entry for tPortConfiguration.                                                                                                                                                                                                     |  |  |

|          |            | Clarification in the implementation note of Section 3.2 regarding TX_ProtDORDY behavior.                                                                                                                                                                                                    |  |  |

|          |            | Clarification in Section 3.8.2.6 for requirements to exit to the MPHY.TEST state.                                                                                                                                                                                                           |  |  |

|          |            | Clarifications in Section 5.1.2 for the operational model of a DSP disconnect.                                                                                                                                                                                                              |  |  |

|          |            | Updates in Section 6 for scope for multi-lane support, addition of<br>Analog Loopback and Tx Compliance modes, clarification of<br>requirements for Receive Burst Testing and a change in the<br>MPHY.TEST register address space.                                                          |  |  |

|          |            | Update to Section 7.3 for a missing label in the figure.                                                                                                                                                                                                                                    |  |  |

| 1.02     | 05/19/2014 | Sec 1.3: Updated reference to M-PHY Spec                                                                                                                                                                                                                                                    |  |  |

|          |            | Table 2-2 & 2-3: Added attributes that are newly defined in [M-PHY] . Modified required value of RX_PWM_Burst_Closure_Length_Capability                                                                                                                                                     |  |  |

|          |            | Sec 2.5.2: Clarified requirements for DSP in MPHY.TEST.     Clarified when Write Responses are to be provided and when registers may be reset.                                                                                                                                              |  |  |

|          |            | Sec 3.2: Clarified normative behavior in implementation note                                                                                                                                                                                                                                |  |  |

|          |            | Sec 3.3: Added note on handling of decode errors                                                                                                                                                                                                                                            |  |  |

|          |            | Sec 3.4: Various modifications to clarity clock compensation rules                                                                                                                                                                                                                          |  |  |

|          |            | Sec 3.6.2.2: Clarified the requirement to use PAIR0 for Warm Reset                                                                                                                                                                                                                          |  |  |

|          |            | <ul> <li>Sec 3.8: Clarified Rx.Detect.Reset requirements for local RESET<br/>assertion. Implementation note added regarding handling of LAU<br/>corruption during U2/U3 entry and support for<br/>RX_Advanced_Granularity_Capability. Various other minor text<br/>modifications</li> </ul> |  |  |

|          |            | Sec 4: Relaxed the accuracy of timestamps reported in ITP packets.                                                                                                                                                                                                                          |  |  |

|          |            | Sec 5: Clarified requirements for local reset assertion during USP disconnect and the RRAP operational model for DSP disconnect. Added a new section that defines Disconnect timing parameters.                                                                                             |  |  |

|          |            | Sec 6: Various clarifications made on the operational behavior of<br>MPHY.TEST. Specified effect of LINE-RESET on MPHY.TEST<br>registers.                                                                                                                                                   |  |  |

|          |            | Sec 7: Figures edited for clarity.                                                                                                                                                                                                                                                          |  |  |

Universal Serial Bus Specification Supplement

Copyright © 2014, Texas Instruments, Hewlett-Packard Company, Intel Corporation, Microsoft

Corporation, Renesas Corporation, ST-Ericsson.

#### All rights reserved

#### INTELLECTUAL PROPERTY DISCLAIMER

THIS SPECIFICATION IS PROVIDED TO YOU "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE. THE AUTHORS OF THIS SPECIFICATION DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS, RELATING TO USE OR IMPLEMENTATION OF INFORMATION IN THIS SPECIFICATION. THE PROVISION OF THIS SPECIFICATION TO YOU DOES NOT PROVIDE YOU WITH ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS.

All product names are trademarks, registered trademarks, or servicemarks of their respective owners.

## **Contributors**

Choate, James Agilent Technologies, Inc.

Chong, Min Jie Agilent Technologies, Inc.

Fleischer-Reumann, Michael Agilent Technologies, Inc.

Herz, Michael Agilent Technologies, Inc.

Marik, Thomas

BitifEye Digital Test Solutions GmbH

Schmitt, Alexander

BitifEye Digital Test Solutions GmbH

Kang, Dae WoonBroadcom Corp.Kasichainula, KishoreBroadcom Corp.Ma, KennethBroadcom Corp.Maiti, ShoumikBroadcom Corp.Turner, TonyBroadcom Corp.Wang, JingBroadcom Corp.

Hackett, Tom Cadence

Nilsson, Daniel Ericsson AB

Olesen, Patrik Ericsson AB

Berkema, Alan Hewlett Packard

Sun, Gilbert Industrial Technology Research Institute

**MCCI** Corporation

**MCCI Corporation**

Chellappan, Satheesh **Intel Corporation** Chen, Huimin **Intel Corporation** Drottar, Ken **Intel Corporation** Dunstan, Robert **Intel Corporation** Froelich, Dan Intel Corporation Harriman, David Intel Corporation Icking, Henrik **Intel Corporation** Ismail, Rahman **Intel Corporation** Knuutila, Kai Intel Corporation Leucht-Roth, Ulrich **Intel Corporation** Mukker, Anoop **Intel Corporation** Ramakrishnan, Sivakumar Intel Corporation Ranganathan, Sridharan **Intel Corporation** Saunders, Brad **Intel Corporation** Vadivelu, Karthi R **Intel Corporation** Galbo, Neal Lexar Media, Inc. Geldman, John Lexar Media, Inc. Hubert, Jonathan Lexar Media, Inc. Tsai, Victor Lexar Media, Inc. Chis, Flaviu **MCCI Corporation**

Knapen, Geert

Yokum, Chris

Aull, Randy Microsoft Corporation

Malayala, Srinivasan Microsoft Corporation

You, Yang Microsoft Corporation

Gillet, Michel Nokia Corporation

Petrie, Richard Nokia Corporation

Atukula, Radha NVIDIA Lai, Luke NVIDIA

Eitam, Ohad Qualcomm, Inc

Gruber, George Qualcomm, Inc

Ly, Thuan Qualcomm, Inc

Remple, Terry Qualcomm, Inc

Rimoni, Yoram Qualcomm, Inc

Wietfeldt, Rick Qualcomm, Inc

Muto, Kiichi Renesas Electronics Corp.

Roux, Steve Renesas Electronics Corp.

Teng, Peter Renesas Electronics Corp.

Bohm, Mark SMSC Monks, Morgan SMSC

Tagami, Shigenori Sony Corporation

Bertholom, CedricST-EricssonChristiansen, MortenST-EricssonGatto, Jean-FrancoisST-EricssonRadulescu, AndreiST-Ericsson

Nagpal, Rajkumar STMicroelectronics

B U, Chandrashekar Synopsys, Inc.

Burns, Adam Synopsys, Inc.

Carvalho, Mara Synopsys, Inc.

Gomes, Joaquim Synopsys, Inc.

Heilman, Kevin Synopsys, Inc.

Kumbhani, Shaileshkumar Synopsys, Inc.

Minwalla, Behram Synopsys, Inc.

Mohammad, Saleem Synopsys, Inc.

Saar, Hezi Synopsys, Inc.

Silva, Sergio Synopsys, Inc.

Wen, Zongyao Synopsys, Inc.

Carlson, Brian Texas Instrumer

Carlson, Brian Texas Instruments

Harris, Will Texas Instruments

Ley, Grant Texas Instruments

Mone, Patrick Texas Instruments

Spetla, Hattie Texas Instruments

# **Table of Contents**

| 1 | Intro | oduction                                            | -  |

|---|-------|-----------------------------------------------------|----|

|   | 1.1   | SSIC Significant Features                           |    |

|   | 1.2   | SSIC and Standard SuperSpeed Comparison             |    |

|   | 1.3   | Related Documents                                   |    |

|   | 1.4   | Terminology                                         |    |

|   | 1.5   | Acronyms and Terms                                  | 12 |

| 2 | Ada   | aptation of M-PHY for the Physical Layer            | 14 |

|   | 2.1   | M-PHY for SSIC Overview                             | 14 |

|   | 2.2   | M-PHY MODULE Capabilities                           | 14 |

|   | 2.3   | M-PHY Configuration Attributes                      | 21 |

|   | 2.4   | M-PHY State Machine                                 | 22 |

|   | 2.5   | LS-MODE Support                                     | 22 |

| 3 | Link  | k Layer                                             | 31 |

|   | 3.1   | Bit and Byte Ordering                               | 31 |

|   | 3.2   | Logical Idle and FLR non-insertion                  | 32 |

|   | 3.3   | Line Coding                                         |    |

|   | 3.4   | Clock Compensation                                  | 34 |

|   | 3.5   | Data Scrambling                                     |    |

|   | 3.6   | PowerOn Reset and Inband Reset                      |    |

|   | 3.7   | Link Layer Timing Requirements                      |    |

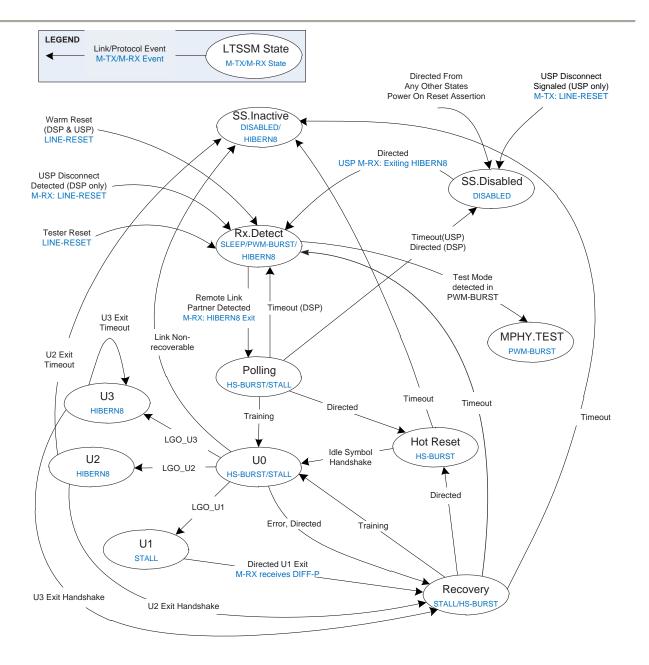

|   | 3.8   | SSIC Link Training and Status State Machine (LTSSM) |    |

| 4 | Prot  | tocol Layer                                         |    |

|   | 4.1   | Port Capability Link Management Packet (LMP)        |    |

|   | 4.2   | Timing Parameters                                   | 51 |

| 5 | Dev   | rice Framework                                      | 53 |

|   | 5.1   | Dynamic Attachment and Removal                      | 53 |

| 6 | MPH   | HY.TEST                                             | 55 |

|   | 6.1   | Overview                                            | 55 |

|   | 6.2   | Entering MPHY.TEST                                  |    |

|   | 6.3   | Loopback Testing                                    | 57 |

|   | 6.4   | Receive Burst Testing                               | 58 |

|   | 6.5   | Tx Compliance Mode                                  | 58 |

|   | 6.6   | Analog Loopback Mode                                | 58 |

|   | 6.7   | MPHY.TEST Block Registers                           | 59 |

| 7 | Tim   | ning Diagrams Appendix (Informative)                | 63 |

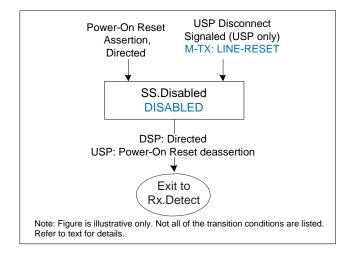

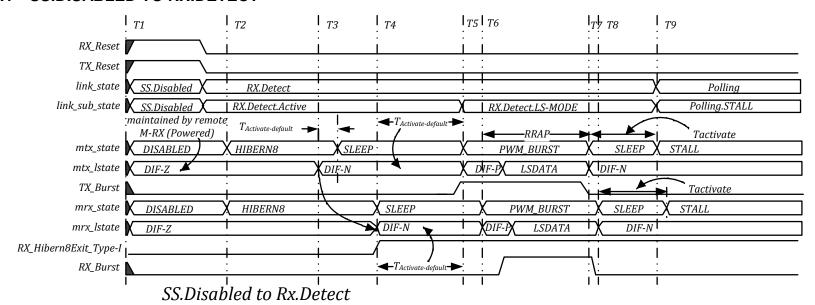

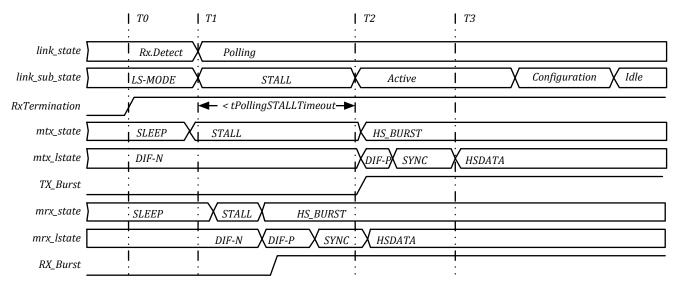

|   | 7.1   | SS.DISABLED TO RX.DETECT                            | 63 |

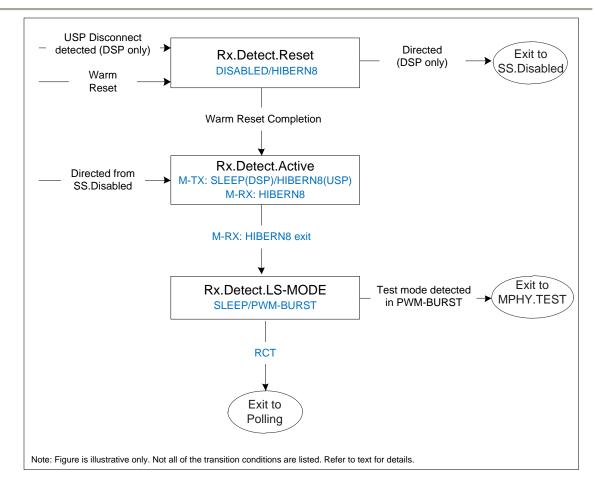

|   | 7.2   | RX.DETECT TO POLLING                                | 64 |

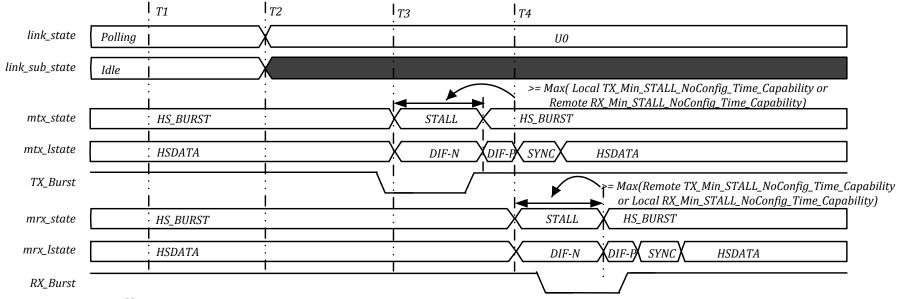

|   | 7.3   | POLLING TO U0                                       | 65 |

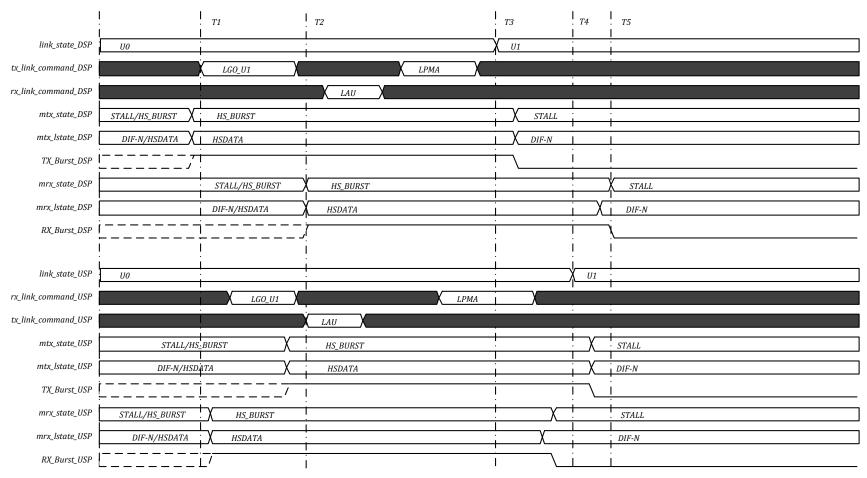

|   | 7.4   | U0 TO U1                                            | 66 |

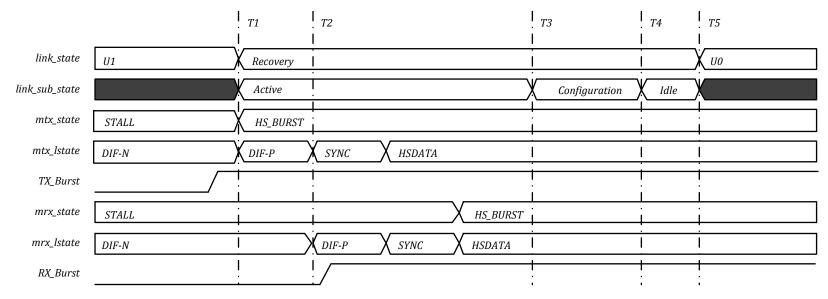

|   | 7.5   | U1 TO U0                                            |    |

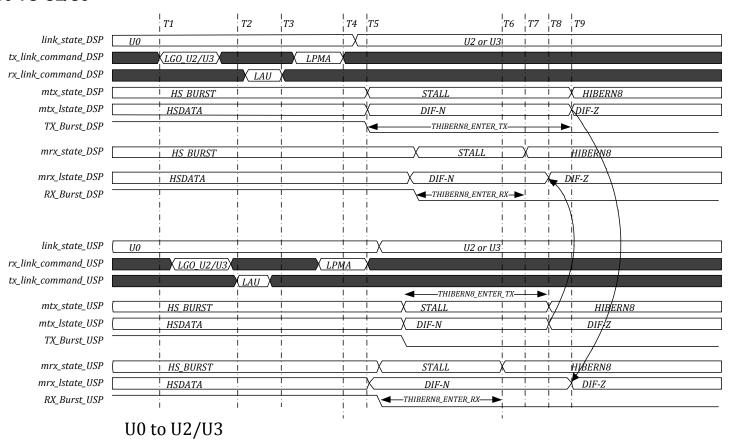

|   | 7.6   | U0 TO U2/U3                                         | 68 |

# Inter-Chip Supplement to the USB Revision 3.0 Specification

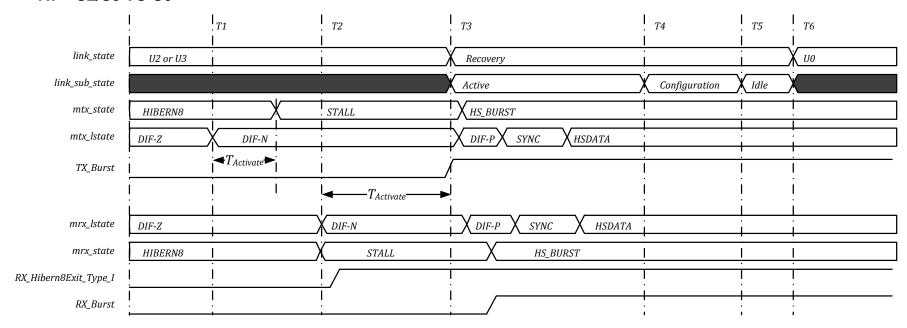

| 7.7 | U2/U3 TO U06   | 9 |

|-----|----------------|---|

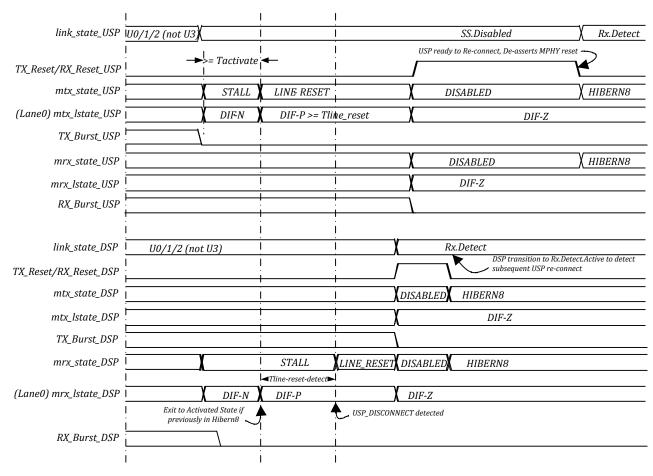

|     | USP Disconnect |   |

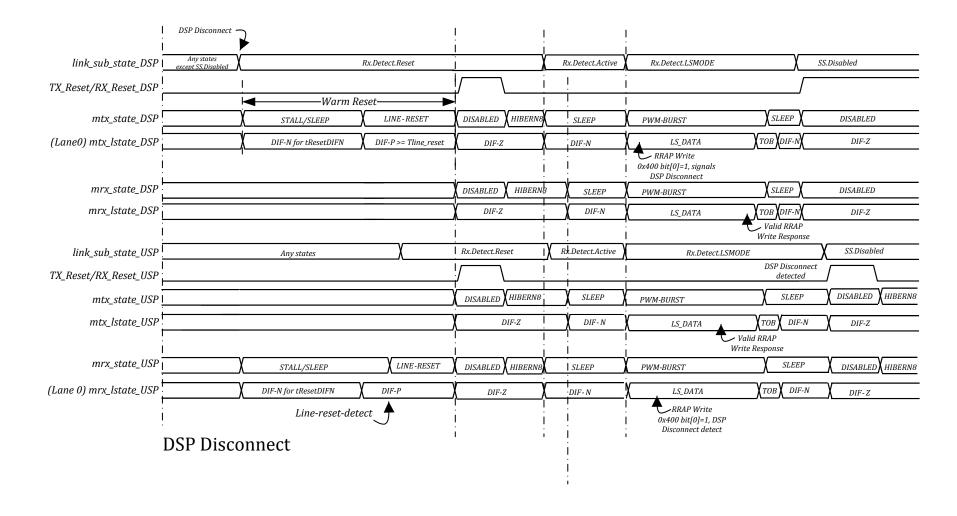

| 7.9 | DSP Disconnect | 1 |

# **Figures**

| Figure 1-2 Example of an implementation with a PHY Adapter Layer to a Standard SS MAC                                                                                                                                                                                                                                                                                | Figure 1-1 SSIC Layers with modifications from [USB3.0] highlighted                   | 10 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----|

| Figure 3-1 Bit Ordering                                                                                                                                                                                                                                                                                                                                              | Figure 1-2 Example of an implementation with a PHY Adapter Layer to a Standard SS MAC | 11 |

| Figure 3-2 Byte Ordering                                                                                                                                                                                                                                                                                                                                             | Figure 2-1 RRAP Packet Types                                                          | 23 |

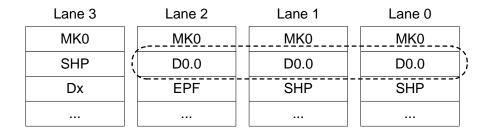

| Figure 3-3 Byte Ordering in a 2 LANE Configuration                                                                                                                                                                                                                                                                                                                   | Figure 3-1 Bit Ordering                                                               | 31 |

| Figure 3-4 Byte Ordering in a 4 LANE Configuration                                                                                                                                                                                                                                                                                                                   | Figure 3-2 Byte Ordering                                                              | 31 |

| Figure 3-5 Two examples of Logical Idle insertion in a 4x LANE configuration                                                                                                                                                                                                                                                                                         | Figure 3-3 Byte Ordering in a 2 LANE Configuration                                    | 32 |

| Figure 3-6 Example of SKP Insertion in a 4x LANE Configuration                                                                                                                                                                                                                                                                                                       | Figure 3-4 Byte Ordering in a 4 LANE Configuration                                    | 32 |

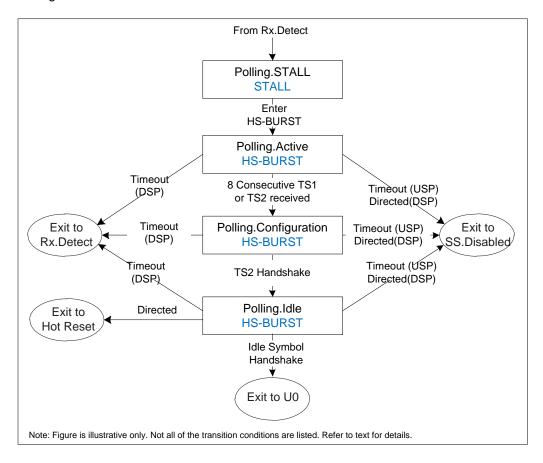

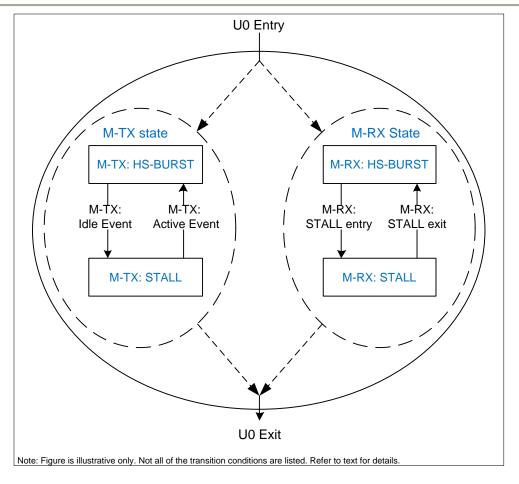

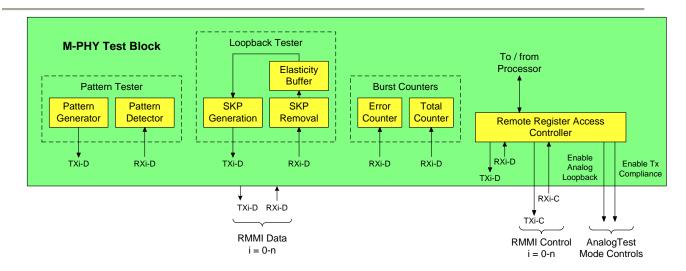

| Figure 3-7 SSIC LTSSM state diagram       40         Figure 3-8 SS.Disabled state       41         Figure 3-9 Rx.Detect Sub-state Machine       42         Figure 3-10 Polling Sub-state Machine       44         Figure 3-11 U0 Sub-state Machine       47         Figure 6-1 MPHY.TEST Overview       55         Figure 6-2 Example of an MPHY.TEST Block       56 | Figure 3-5 Two examples of Logical Idle insertion in a 4x LANE configuration          | 33 |

| Figure 3-8 SS.Disabled state                                                                                                                                                                                                                                                                                                                                         | Figure 3-6 Example of SKP Insertion in a 4x LANE Configuration                        | 35 |

| Figure 3-9 Rx.Detect Sub-state Machine                                                                                                                                                                                                                                                                                                                               | Figure 3-7 SSIC LTSSM state diagram                                                   | 40 |

| Figure 3-10 Polling Sub-state Machine                                                                                                                                                                                                                                                                                                                                | Figure 3-8 SS.Disabled state                                                          | 41 |

| Figure 3-11 U0 Sub-state Machine                                                                                                                                                                                                                                                                                                                                     | Figure 3-9 Rx.Detect Sub-state Machine                                                | 42 |

| Figure 6-1 MPHY.TEST Overview55 Figure 6-2 Example of an MPHY.TEST Block56                                                                                                                                                                                                                                                                                           | Figure 3-10 Polling Sub-state Machine                                                 | 44 |

| Figure 6-2 Example of an MPHY.TEST Block56                                                                                                                                                                                                                                                                                                                           | Figure 3-11 U0 Sub-state Machine                                                      | 47 |

|                                                                                                                                                                                                                                                                                                                                                                      | Figure 6-1 MPHY.TEST Overview                                                         | 55 |

| Figure 6-3 Receive BURST Test Sequence56                                                                                                                                                                                                                                                                                                                             | Figure 6-2 Example of an MPHY.TEST Block                                              | 56 |

|                                                                                                                                                                                                                                                                                                                                                                      | Figure 6-3 Receive BURST Test Sequence                                                | 56 |

# **Tables**

| Table 2-1 Multi-LANE Parameters         | 15 |

|-----------------------------------------|----|

| Table 2-2 M-TX Capability Attributes    | 16 |

| Table 2-3 M-RX Capability Attributes    | 18 |

| Table 2-4 TX Configuration Attributes   | 21 |

| Table 2-5 RRAP Address Map              | 24 |

| Table 2-6 RRAP Timing Parameters        | 30 |

| Table 3-1 Mapping of SS Control Symbols | 33 |

| Table 3-2 Link Layer Timing Parameter   | 38 |

| Table 4-1 Protocol Timing Parameters    | 51 |

| Table 5-1 Disconnect Timing Parameters  | 54 |

| Table 6-1 MPHY.TEST Block Registers     | 59 |

#### 1 Introduction

USB is the ubiquitous peripheral-interconnect of choice for a large number of computing and consumer applications. Many systems provide a comprehensive set of software drivers to support commonly available USB peripherals. In addition there is an existing USB ecosystem that includes USB silicon suppliers, design IP houses and verification and testing vendors that lowers the cost for product manufacturers of USB hosts and peripherals.

These advantages have made USB attractive as a chip-to-chip interconnect within a product (without use of cables or connectors). This usage has been validated by the adoption of the High Speed Inter-Chip Supplement [HSIC] in mobile platforms. HSIC leveraged the benefits of High Speed USB while optimizing the link for power, cost and complexity. However the 480 Mbps bandwidth limitation of HSIC poses a limitation for the next generation of applications that require higher bandwidth.

The USB 3.0 specification adds support for transfer speeds of 5 Gbps to address the need for higher bandwidth. However the USB3.0 specification as-is does not meet the requirements of embedded interchip interfaces with respect to power and EMI robustness. To address this need, this supplement describes Super Speed Inter-Chip (SSIC) as an optimized inter-chip version of USB3.0.

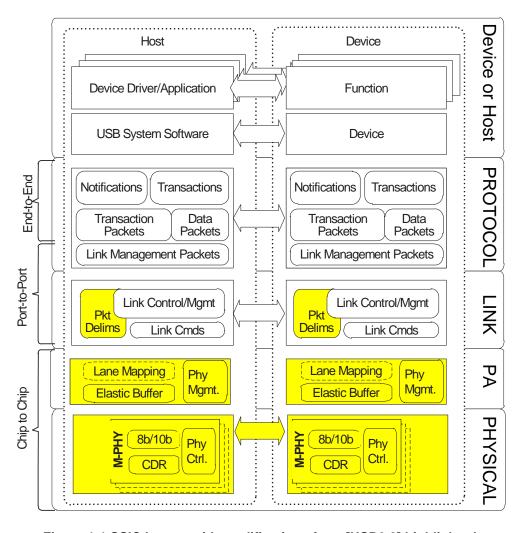

Figure 1-1 SSIC Layers with modifications from [USB3.0] highlighted

As shown in Figure 1-1, SSIC uses the MIPI M-PHY specification as the physical layer of the interconnect to meet the requirements of embedded inter-chip interfaces. The MIPI M-PHY [M-PHY]

specification describes a serial physical layer technology with high bandwidth capabilities, which is specifically developed for mobile applications to obtain low pin count combined with very good power efficiency.

#### 1.1 SSIC Significant Features

The following summarizes the key features of SSIC:

- Support for the SuperSpeed protocol only as defined in [USB 3.0]

- Optimized for power, area, cost and EMI robustness for embedded inter-chip interfaces

- Compliant with the Type-I M-PORTs from the MIPI M-PHY specification [M-PHY]

- Support for x1, x2 and x4 LANE configurations.

This supplement only focuses on peripherals that are directly attached to hosts. Support for hubs is not defined and may be achieved in an implementation-specific manner.

## 1.2 SSIC and Standard SuperSpeed Comparison

SSIC has been designed to replace a standard SuperSpeed Controller and PHY with an implementation that maps the SuperSpeed controller on the MIPI M-PHY. *This supplement does not specify details of any particular implementation* and it is intended that SSIC be implementable in multiple ways, depending on what is appropriate for a particular product.

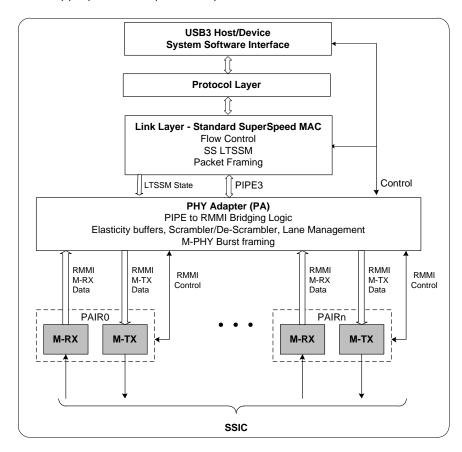

Figure 1-2 Example of an implementation with a PHY Adapter Layer to a Standard SS MAC

Figure 1-2 shows an example of an SSIC implementation that leverages a standard SuperSpeed controller with minimal modifications in the link layer and above. All specifics related to SSIC including bridging logic between the PIPE3 interface of the controller and the Reference M-PHY MODULE

41 Interface (RMMI) of the M-PHY are contained in the PHY Adapter (PA). In such an implementation, it is 42 necessary for the PHY Adapter to implement whatever mechanisms are needed to allow the controller to 43 operate as if it were connected to a SuperSpeed link, for example by tracking the Link Training Status 44 State Machine (LTSSM) and providing the expected responses on the link. Other alternatives to this 45 example may also be designed that are compliant to this supplement. 46 1.3 **Related Documents** 47 48 This is not a stand-alone document. It is a supplement to [USB 3.0]. Any aspects of USB which are not 49 specifically changed by this supplement are governed by [USB 3.0]. 50 The following referenced documents can be found on the USB-IF website www.usb.org: [USB 3.0] Universal Serial Bus Revision 3.0 Specification including ECNs [HSIC] High Speed Inter-Chip USB Electrical Specification including ECNs 51 52 The following referenced documents are published by the MIPI Alliance: MIPI® Alliance Specification for M-PHY<sup>SM</sup> Version 3.0 [M-PHY] [CTS] MIPI M-PHY Conformance Test Suite 53 1.4 Terminology 54 55 "Shall" is normative and used to indicate mandatory requirements which are to be followed strictly in order to conform to this standard. 56 57 "Should" is normative and used to indicate a recommended option or possibility. 58 "May" is normative and used to indicate permitted behavior. 59 "Can" is informative and used to indicate behavior which is possible or may be seen The use of "must" and "will" is deprecated for requirements and shall only be used for statements of fact. 60 61 62 **Acronyms and Terms** 63 This section lists and defines terms and abbreviations used throughout this specification. 64 Acronyms and Terms defined in [USB 3.0] and [M-PHY] are not reproduced here. Except where explicitly

| Acronym/Term | Description                                                                            |

|--------------|----------------------------------------------------------------------------------------|

| DSP          | DownStream Port (DSP) refers to the port of a host to which a peripheral is connected. |

noted, when there is a terminology conflict between the [USB 3.0] and [M-PHY] specifications, the [USB

3.0] definition is used in this document.

65

| Link       | Refers to the Link Layer as defined in [USB 3.0]. To be distinguished from "M-PHY LINK".              |

|------------|-------------------------------------------------------------------------------------------------------|

| M-PHY LINK | Refers to LINK as defined in [M-PHY] .                                                                |

| PA         | PHY Adapter (PA). Term that refers to logic that interfaces the link layer with the M-PHY.            |

| PAIR       | A PAIR consists of a LANE in the downstream SUB-LINK and a counterpart LANE in the upstream SUB-LINK. |

| RRAP       | Remote Register Access Protocol (RRAP) is used while in the PWM-BURST LS-MODE of operation.           |

| SSIC       | SuperSpeed Inter-Chip.                                                                                |

| USP        | UpStream Port (USP) refers to the port that a peripheral uses to connect to a host.                   |

# 2 Adaptation of M-PHY for the Physical Layer

- This document references the MIPI M-PHY [M-PHY] specification for the definition of the physical layer.

- This section includes an overview of the relevant M-PHY features, defines required M-PHY capabilities

- and describes functionality while in the [M-PHY] LS-MODE of operation.

#### 2.1 M-PHY for SSIC Overview

68

72

74

75

76

77

78 79

80

83

84

90

96

- 73 The following summarizes relevant M-PHY features:

- Requirement to implement Type-I M-PHY

- Support for PWM-G1 and HS-G1/G2/G3 BURST mode operation

- SSIC profile definitions to aid in inter-operability of M-PHYs in SSIC implementations

- M-PHY SAVE states mapped appropriately to SuperSpeed link states

- Compliant to M-PHY Symbol coding (8b10b) engine for spectral conditioning and clock recovery

- Ability to operate with shared and non-shared reference clocks.

#### 2.1.1 M-PHY Architecture and the Definition of PAIRs

- The architecture of the M-PHY is defined in terms of LANEs, SUB-LINKs and LINKs. The M-PHY LINK shall comply with the following:

- The two SUB-LINKs of an SSIC implementation shall support the same number of LANEs.

- All LANEs in the M-PHY LINK shall enter and exit HIBERN8 simultaneously.

- In addition this supplement defines the concept of a PAIR.

- 86 A LANE in the downstream SUB-LINK and a counterpart LANE in the upstream SUB-LINK are together

- 87 referred to as a PAIR. A multi-LANE implementation consists of multiple PAIRs and shall have a specific

- PAIR be statically pre-determined as PAIR0. A single-LANE implementation shall consist of only one

- 89 PAIR which shall be PAIR0.

#### 2.2 M-PHY MODULE Capabilities

- 91 The M-PHY specification defines capability, configuration and status attributes for an M-TX and for an M-

- 92 RX MODULE. Capability attributes describe the capability of M-PHY MODULEs and may vary

- 93 depending on the implementation.

- 94 To aid in the inter-operability of devices, this document defines profiles within which specific M-PHY

- 95 Capabilities are mandated.

#### 2.2.1 Profile Definitions

- 97 Profiles are indicated by jointly specifying the speed, the multi-LANE capabilities and the rate series such as:

- 99 SSIC-Ggr-Lt where

- q = 1, 2 or 3 and indicates the specific HS-GEAR that the M-PHY LINK operates in

- 101 r = A or B and indicates the Rate Series that the M-PHY LINK operates in

- 102 l = 1, 2 or 4 and indicates the number of LANEs active in each SUB-LINK (See Section 2.2.2)

- All lanes in an implementation shall only operate at the HS-GEAR that corresponds to the profile that is

- supported. An implementation is permitted to support one or more profiles, however the combination of

- different profiles supported by a specific implementation are out of scope of this specification. For

- example: an SSIC-G2A-L1 may or may not choose to support SSIC-G1B-L1.

An implementation of a profile shall support the corresponding speed, multi-LANE and mandated capabilities of the M-TX and M-RX MODULEs as specified in Section 2.2.3.

Certain M-PHY MODULE configurations attributes are chosen not based on the choice of profile or the mandate of this document but instead are based on implementation-specific constraints. A complete list of such parameters is specified in Section 2.3.

#### 2.2.2 Multi-LANE Capabilities

An implementation may choose to feature one (x1), two (x2) or four (x4) LANEs in each SUB-LINK.

The HS-TX LANE-to-LANE skew shall be established by the receipt of a MK0 symbol at the start of a HS-Burst. Receivers shall accept LANE-to-LANE skew up to the allowed limit.

For multi-LANE M-PHY LINKs, Table 2-1 specifies the required timing parameters.

#### Table 2-1 Multi-LANE Parameters

| Symbol                      | Parameter                                                            | Value  | Comments                                                                                                     |

|-----------------------------|----------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------|

| T <sub>L2L_SKEW_HS_TX</sub> | Permitted skew between any two LANEs measured at the M-TX's pins     | 1300ps | To be measured by the receipt of MK0 at the start of a HS-BURST and as defined in Section 5.1.2.4 of [M-PHY] |

| T <sub>L2L_SKEW_HS_RX</sub> | Permitted skew between any two LANEs measured at the receiver's pins | 4000ps |                                                                                                              |

#### 2.2.3 M-TX and M-RX Capabilities

An implementation shall ensure that the local and remote M-PORTs are configured to the selected profile. M-PORTs are required to support the M-TX and M-RX capabilities required in this section.

Table 2-2 and Table 2-3 define the set of capabilities that are mandated for M-TX and M-RX MODULEs respectively. The tables list attributes for which this supplement imposes specific requirements. Attributes defined by [M-PHY] which are not specified by this supplement may be set to implementation-specific values.

**Table 2-2 M-TX Capability Attributes**

| Attribute                                | AttrID | Description                                                                                       | M-PHY range                                                                                                                                                  | Required Value                                     |

|------------------------------------------|--------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| TX_HSMODE_Capability                     | 0x01   | Specifies support for HS-MODE.                                                                    | 0=no<br>1=yes                                                                                                                                                | 1                                                  |

| TX_HSGEAR_Capability                     | 0x02   | Specifies supported HS-GEARs.                                                                     | 1=HS-G1<br>2=HS-G1/G2<br>3=HS-G1/G2/G3                                                                                                                       | ≥1 for SSIC-G1<br>≥2 for SSIC-G2<br>=3 for SSIC-G3 |

| TX_PWMGEAR_Capability                    | 0x04   | Specifies support for PWM-GEARs other than PWM-G0.                                                | PWM_G1_ONLY = 1,<br>PWM_G1_TO_G2 =<br>2,<br>PWM_G1_TO_G3 =<br>3,<br>PWM_G1_TO_G4 =<br>4,<br>PWM_G1_TO_G5 =<br>5,<br>PWM_G1_TO_G6 =<br>6,<br>PWM_G1_TO_G7 = 7 | ≥ 1                                                |

| TX_Amplitude_Capability                  | 0x05   | Specifies supported signal amplitude levels.                                                      | 1=SA<br>2=LA<br>3=SA and LA                                                                                                                                  | 3 = SA and LA. Both options supported.             |

| TX_ExternalSYNC_Capability               | 0x06   | Specifies support for external SYNC pattern.                                                      | 0=no<br>1=yes                                                                                                                                                | ≥ 0                                                |

| TX_HS_Unterminated_LINE_Drive_Capability | 0x07   | Specifies whether or not M-TX supports driving an unterminated LINE in HS-MODE.                   | 0=no<br>1=yes                                                                                                                                                | ≥ 0                                                |

| TX_LS_Terminated_LINE_Drive_Capability   | 0x08   | Specifies whether or not M-TX supports driving a terminated LINE in LS-MODE.                      | 0=no<br>1=yes                                                                                                                                                | ≥ 0                                                |

| TX_Min_SLEEP_NoConfig_Time_Capability    | 0x09   | Specifies minimum time (in SI) in SLEEP state needed when inline configuration was not performed. | 1 to 15                                                                                                                                                      | ≤ 15                                               |

| Attribute                             | AttrID | Description                                                                                                                                                                                     | M-PHY range                                                                                                                                                                      | Required Value                                                          |

|---------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| TX_Min_STALL_NoConfig_Time_Capability | 0x0A   | Specifies minimum time (in SI) in STALL state needed when inline configuration was not performed.                                                                                               | 1 to 255                                                                                                                                                                         | ≤8                                                                      |

| TX_Min_SAVE_Config_Time_Capability    | 0x0B   | Specifies minimum reconfiguration time (in 40 ns steps). This applies only to SLEEP and STALL states.                                                                                           | 1 to 250 (10000 ns)                                                                                                                                                              | ≤ 125 (5000 ns)                                                         |

| TX_REF_CLOCK_SHARED_Capability        | 0x0C   | Specifies support for a shared reference Clock.                                                                                                                                                 | 0 = no<br>1 = yes                                                                                                                                                                | ≥ 0                                                                     |

| TX_PHY_MajorMinor_Release_Capability  | 0x0D   | Specifies the major and minor numbers of the M-PHY version supported by the M-TX.                                                                                                               | Major version 0 to 9<br>Minor version 0 to 9                                                                                                                                     | Based on M-PHY<br>Spec Rev in<br>Section 1.3                            |

| TX_PHY_Editorial_Release_Capability   | 0x0E   | Specifies the sequence number of the M-PHY version supported by the M-TX.                                                                                                                       | 1 to 99                                                                                                                                                                          | Based on M-PHY<br>Spec Rev in<br>Section 1.3                            |

| TX_Hibern8Time_Capability             | 0x0F   | Specifies minimum time (in 100 µs steps) in HIBERN8 state.                                                                                                                                      | 1 to 128 (100 µs to 12.8 ms)                                                                                                                                                     | 1 (100 µs)                                                              |

| TX_Advanced_Granularity_Capability    | 0x10   | Support and degree of fine granularity steps for a reduced time in HIBERN8 state.  If a finer granularity is specified, all coarser granularities shall be supported.                           | Step size<br>$b00 = 4 \mu s$ ,<br>$b01 = 8 \mu s$ ,<br>$b10 = 16 \mu s$ ,<br>$b11 = 32 \mu s$<br>Supports fine<br>granularity<br>steps:<br>No = 0 (100 $\mu s$ step),<br>Yes = 1 | Step Size No Requirement defined.  Supports fine granularity steps: ≥ 0 |

| TX_Advanced_Hibern8Time_Capability    | 0x11   | Specifies minimum time in HIBERN8 state when advanced granularity is supported in steps defined by TX_Advanced_Granularity_Capability. Existence depends on: TX_Advanced_Granularity_Capability | 1 to 128                                                                                                                                                                         | No Requirement defined.                                                 |

| Attribute                          | AttrID | Description                   | M-PHY range          | Required Value |

|------------------------------------|--------|-------------------------------|----------------------|----------------|

| TX_HS_Equalizer_Setting_Capability | 0x12   | Support for transmit path de- | B[0] = 0:            | B[0] ≥ 0       |

|                                    |        | emphasis for HS-MODE          | De-emphasis of       | B[1] ≥ 0       |

|                                    |        | Existence depends on:         | 3.5dB not supported, |                |

|                                    |        | TX_HSMODE_Capability          | B[0] = 1;            |                |

|                                    |        |                               | De-emphasis of       |                |

|                                    |        |                               | 3.5dB supported,     |                |

|                                    |        |                               | B[1] = 0;            |                |

|                                    |        |                               | De-emphasis of       |                |

|                                    |        |                               | 6dB not supported,   |                |

|                                    |        |                               | B[1] = 1;            |                |

|                                    |        |                               | De-emphasis of       |                |

|                                    |        |                               | 6dB supported        |                |

# **Table 2-3 M-RX Capability Attributes**

| Attribute                               | AttrID | Description                                                                                       | M-PHY Range                                                                                                                                   | Required Value                                     |

|-----------------------------------------|--------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| RX_HSMODE_Capability                    | 0x81   | Specifies support for HS-MODE.                                                                    | 0=no<br>1=yes                                                                                                                                 | 1=yes                                              |

| RX_HSGEAR_Capability                    | 0x82   | Specifies supported HS-GEARs.                                                                     | 1=HS-G1<br>2=HS-G1/G2<br>3=HS-G1/G2/G3                                                                                                        | ≥1 for SSIC-G1<br>≥2 for SSIC-G2<br>=3 for SSIC-G3 |

| RX_PWMGEAR_Capability                   | 0x84   | Specifies support for PWM-GEARs other than PWM-G0.                                                | PWM_G1_ONLY = 1,<br>PWM_G1_TO_G2 = 2,<br>PWM_G1_TO_G3 = 3,<br>PWM_G1_TO_G4 = 4,<br>PWM_G1_TO_G5 = 5,<br>PWM_G1_TO_G6 = 6,<br>PWM_G1_TO_G7 = 7 | ≥ 1                                                |

| RX_HS_Unterminated_Capability           | 0x85   | Specifies support for disconnection of resistive termination in HS-MODE.                          | 0=no<br>1=yes                                                                                                                                 | 0 = no for all profiles                            |

| RX_LS_Terminated_LINE_Drive_Cap ability | 0x86   | Specifies support for enabling resistive termination in LS-MODE.                                  | 0=no<br>1=yes                                                                                                                                 | ≥ 0                                                |

| RX_Min_SLEEP_NoConfig_Time_Capability   | 0x87   | Specifies minimum time (in SI) in SLEEP state needed when inline configuration was not performed. | 1 to 15                                                                                                                                       | ≤ 15                                               |

| Attribute                              | AttrID                                      | Description                                                                                               | M-PHY Range                                  | Required Value                               |

|----------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|

| RX_Min_STALL_NoConfig_Time_Capability  | 0x88                                        | Specifies minimum time (in SI) in STALL state needed when inline configuration was not performed.         | 1 to 255                                     | ≤ 8<br>Please see <b>Note 1</b> .            |

| RX_Min_SAVE_Config_Time_Capability     | 0x89                                        | Specifies minimum reconfiguration time (in 40 ns steps). This applies only to SLEEP and STALL states.     | 1 to 250 (10000 ns)                          | ≤ 125 (5000 ns)                              |

| RX_REF_CLOCK_SHARED_Capability         | 0x8A                                        | Specifies support for a shared reference Clock.                                                           | 0=no<br>1=yes                                | ≥ 0                                          |

| RX_HS_G1_SYNC_LENGTH_Capability        | 0x8B                                        | HS-G1 Synchronization pattern length in SI.                                                               | {Sync range, Sync Length}                    | ≤ {1,4}                                      |

| RX_HS_G1_PREPARE_LENGTH_Capability     | 0x8C                                        | HS-G1 prepare length multiplier for M-RX                                                                  | 0 to 15                                      | ≤ 4                                          |

| RX_LS_PREPARE_LENGTH_Capability        | 0x8D                                        | PWM-BURST or SYS-BURST PREPARE length multiplier for M-RX.                                                | 0 to 15                                      | ≤ 8                                          |

| RX_PWM_Burst_Closure_Length_Capability | 0x8E                                        | Specifies minimum burst closure time (in SI) necessary to guarantee complete data processing inside M-RX. | 0 to 31                                      | ≤ 16                                         |

| RX_Min_ActivateTime_Capability         | 0x8F                                        | Specifies minimum activate time needed in 100us steps                                                     | 1 to 9                                       | 1                                            |

| RX_PHY_MajorMinor_Release_Capability   | 0x90                                        | Specifies the major and minor numbers of the M-PHY version supported by the M-RX.                         | Major version 0 to 9<br>Minor version 0 to 9 | Based on M-PHY<br>Spec Rev in Section<br>1.3 |

| RX_PHY_Editorial_Release_Capability    | 0x91                                        | Specifies the sequence number of the M-PHY version supported by the M-RX.                                 | 1 to 99                                      | Based on M-PHY<br>Spec Rev in Section<br>1.3 |

| RX_Hibern8Time_Capability              | 0x92                                        | Specifies minimum time (in 100 µs steps) in HIBERN8 state.                                                | 1 to 128 (100 µs to 12.8 ms)                 | 1 (100 µs)                                   |

| RX_HS_G2_SYNC_LENGTH_Capability        | HS-G2 Synchronization pattern length in SI. | {Sync range, Sync Length}                                                                                 | ≤ {1,5}                                      |                                              |

| Attribute                               | AttrID | Description                                                                                                                                                                                       | M-PHY Range                                                                                                                                                                     | Required Value                                                          |

|-----------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| RX_HS_G3_SYNC_LENGTH_Capability         | 0x95   | HS-G3 Synchronization pattern length in SI.                                                                                                                                                       | {Sync range, Sync Length}                                                                                                                                                       | ≤ {1,6}                                                                 |

| RX_HS_G2_PREPARE_LENGTH_Capability      | 0x96   | HS-G2 prepare length multiplier for M-RX                                                                                                                                                          | 0 to 15                                                                                                                                                                         | ≤ 4                                                                     |

| RX_HS_G3_PREPARE_LENGTH_Capability      | 0x97   | HS-G3 prepare length multiplier for M-RX                                                                                                                                                          | 0 to 15                                                                                                                                                                         | ≤ 4                                                                     |

| RX_Advanced_Granularity_Capability      | 0x98   | Support and degree of fine granularity steps for THIBERN8 and TACTIVATE.                                                                                                                          | Step size<br>$b00 = 4 \mu s$ ,<br>$b01 = 8 \mu s$ ,<br>$b10 = 16 \mu s$ ,<br>$b11 = 32 \mu s$<br>Supports fine<br>granularity steps<br>No = 0 (100 $\mu s$<br>step),<br>Yes = 1 | Step Size No Requirement defined.  Supports fine granularity steps: ≥ 0 |

| RX_Advanced_Hibern8Time_Capability      | 0x99   | Specifies minimum time in HIBERN8 state when advanced granularity is supported in steps defined by RX_advanced_Granularity_Capabi lity. Existence depends on: RX_Advanced_Granularity_Capabi lity | 1 to 128                                                                                                                                                                        | No Requirement defined.                                                 |

| RX_Advanced_Min_ActivateTime_Capability | 0x9A   | Specifies minimum activate time when advanced granularity is supported in steps defined by RX_Advanced_Granularity_Capabi lity.  Existence depends on: RX_Advanced_Granularity_Capabi lity        | 1 to 14                                                                                                                                                                         | No Requirement defined.                                                 |

**Note 1**: [M-PHY] requires an RMMI based M-RX to output at least two cycles of RX\_SymbolClk after the end of a HS-BURST. An M-RX cannot exit STALL to start a new HS-BURST until after it has output two cycles of RX\_SymbolClk from the previous HS-BURST. Depending on the width of RX\_Symbol (ie 10/20/40 bits), two cycles of RX\_SymbolClk may be either 2, 4 or 8 SIs. For an RX\_Symbol width of 40 bits, the M-RX needs to remain in stall for at least 8 SIs before the start of the next burst.

# 2.3 M-PHY Configuration Attributes

As noted in Annex D.2 in [M-PHY], M-TX Configuration attributes shall be set appropriately to match the corresponding M-RX capability attribute values. Depending on the profile supported by the implementation, default values for the configuration attributes for the M-TX and M-RX MODULE shall be suitably chosen and configured by implementations. Optimizations to the default values for the configuration attributes may be applied in an implementation-specific manner. For more details on the configuration attributes please refer to [M-PHY]

However there are some M-PHY configuration attributes listed in Table 2-4 that are not based on the profile but are instead configured depending on implementation considerations. This section makes note of these implementation-specific configuration parameters. This supplement does not specify recommended values for these parameters and does not mandate a mechanism for configuring and coordinating the values of these parameters across the M-PHY LINK.

**Table 2-4 TX Configuration Attributes**

| Attribute          | AttrID | Description                              | M-PHY range                 | Required Value               |

|--------------------|--------|------------------------------------------|-----------------------------|------------------------------|

| TX_HS_SlewRate     | 0x26   | Slew Rate control of M-TX output driver. | 0 to 255                    | Depending on implementation. |

| TX_DRIVER_POLARITY | 0x2F   | M-TX output driver polarity.             | NORMAL = 0,<br>INVERTED = 1 | Depending on implementation. |

#### 2.4 M-PHY State Machine 146 147 This supplement is in compliance with the State Machine for Type-I MODULEs as described in Figure 7 148 for M-TX and Figure 8 for M-RX in [M-PHY]. However the following is to be noted: 149 The LINE-CFG states are not required for SSIC implementations. 150 Optical Media Converters are not supported. 151 Details regarding the mapping of the SSIC Link Training and Status State Machine (LTSSM) on the M-152 PHY Type-I state machines are provided in Section 3.8. 153 2.5 LS-MODE Support 154 The M-TX and M-RX MODULEs enter the LS-MODE of operation following events such as a power-on-155 156 reset, a warm reset, a USP disconnect or a DSP disconnect. Section 3.8 includes further details on the 157 link layer conditions for entering LS-MODE. 158 The only PWM-GEAR that is used in a PWM-BURST is PWM-G1. The Remote Register Access Protocol (RRAP) defined in Section 2.5.2 shall be implemented for data transmission in this mode. 159 160 Data transmission in a PWM-BURST shall take place in one of the following scenarios: In the Rx.Detect LTSSM state between a USP and a DSP or 161 in the MPHY.TEST LTSSM state when the USP or DSP operates as a DUT under the control of 162 external Test Equipment. 163 The following section details the entry conditions for PWM-BURST in the Rx.Detect state. For details on 164 the entry requirements in the MPHY.TEST state please refer to Section 6.2. 165 166 2.5.1 **PWM-BURST Entry in Rx.Detect** Upon entering the Rx.Detect LTSSM state and the LS-MODE sub-state as described in Section 3.8.2, a 167 DSP and an USP shall: 168 169 Disable Support for LCCs in the M-TX for all PAIRs. Initiate a PWM-BURST as defined in this section. 170 Implementation Note: As per [M-PHY] disabling support for LCC requires configuring a value of "NO = 0" to the LCC ENABLE Configuration Attribute in the Effective Bank and subsequently asserting the TX CfqUpdt signal of the M-TX for all PAIRs. 171 The DSP shall initiate a PWM-BURST as per [M-PHY] on the M-TX MODULE of PAIR0. The DSP shall 172

- The DSP shall initiate a PWM-BURST as per [M-PHY] on the M-TX MODULE of PAIR0. The DSP shall then monitor the M-RX of PAIR0 for the USP to initiate a PWM-BURST.

- The USP shall initiate a PWM-BURST as per [M-PHY] on the M-TX MODULE of PAIR0 after it detects a PWM-BURST on the M-RX of PAIR0.

- 176 In a multi-LANE M-PHY LINK the remaining M-TX MODULEs shall remain in the SLEEP state.

#### 2.5.2 Remote Register Access Protocol (RRAP)

While in the PWM-BURST mode, communication is achieved using the RRAP which consists of the following packet types:

Write Command

177

178179

180

181

182 183

184

185

186

187

188

189

190

191

192

194

195 196

197

198

- Write Response

- Read Command

- Read Response

An RRAP Master shall be capable of issuing Command packets while a RRAP Target shall issue response packets.

#### Write Command

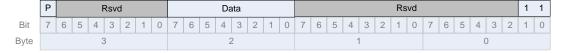

|      | Р |   |   | F | Rsvo | t |   |   |   |   |   | Da | ata |   |   |   |   |   | L | owe | rAdo | dr |   |   | U | ppe | rAdo | dr | Rs | vd | 0 | 0 |

|------|---|---|---|---|------|---|---|---|---|---|---|----|-----|---|---|---|---|---|---|-----|------|----|---|---|---|-----|------|----|----|----|---|---|

| Bit  | 7 | 6 | 5 | 4 | 3    | 2 | 1 | 0 | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | 7 | 6 | 5 | 4   | 3    | 2  | 1 | 0 | 7 | 6   | 5    | 4  | 3  | 2  | 1 | 0 |

| Byte |   |   |   | 3 | 3    |   |   |   |   |   |   | 2  | 2   |   |   |   |   |   |   | ,   | 1    |    |   |   |   |     |      | (  | )  |    |   |   |

#### Write Response

#### **Read Command**

#### **Read Response**

#### Figure 2-1 RRAP Packet Types

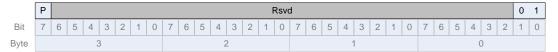

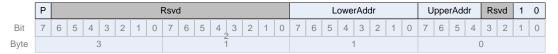

The RRAP packets are described in Figure 2-1 along with the following additional requirements:

- "LowerAddr" and "UpperAddr" values are set based on the address map defined in Table 2-5.

- The "Rsvd" fields shall not be used and shall be set to 0.

- The "P" field functions as an odd-parity bit for the entire packet.

- The entire packet is transmitted continuously without intervening symbols.

The following requirements apply to the RRAP:

- When in PWM-BURST mode and not transmitting a RRAP packet, the M-TX MODULEs in SUB-LINKs shall transmit the FLR symbol as per [M-PHY].

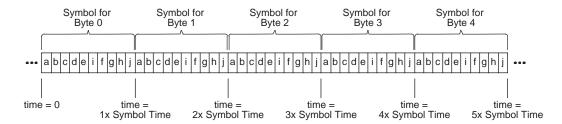

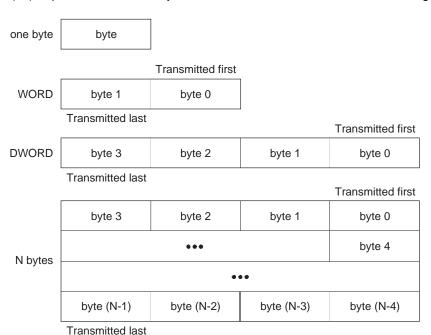

- The RRAP follows the bit and byte ordering rules defined in Section 3.1.

- A DSP shall support RRAP Master functionality.

- 199 200 201

- 202

- 204 205 206

- 207 208 209 210

- 212 213 214 215

- 216 217 218

- 219 220

- 221

- When in PWM-BURST, a DSP that supports the optional MPHY.TEST state shall support the receipt

of a Write Command to enable a transition to that state. All RRAP commands received by a DSP in

the MPHY.TEST state shall be processed per RRAP Target functionality.

- A USP shall only support RRAP Target functionality.

- Test Equipment shall function as a RRAP Master with either the DSP or the USP as the Device Under Test (DUT).

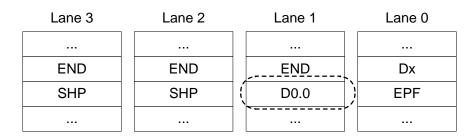

- A DSP serving as a RRAP Master shall only send commands and receive responses on PAIR0.

- A DSP or an USP serving as a RRAP Target shall support receiving commands over any PAIRx and shall return a response on the same PAIRx.

- Test Equipment serving as a RRAP Master may send commands and receive responses on any PAIR.

- Upon receiving a Write Command packet, a Target shall transmit the corresponding response packet within tRRAPTargetResponse. This requirement shall apply for any Write Command received including Writes to Reserved Registers and Registers that are identified in Table 2-5 as having no effect.

- Upon receiving a Read Command packet, a Target shall transmit the corresponding response packet within tRRAPTargetResponse.

- If a Master has issued a Command, then the Master shall not retry the Command or issue another Command until either the Target has provided a Response, or after tRRAPInitiatorResponse has elapsed.

- A Target shall map the attributes of all implemented PAIRs to RRAP addresses as defined in Table 2-5.

- A Target shall not send a response until the RRAP Command is fully received with a valid parity.

#### Implementation Note:

Additional steps to improve the reliability offered by a single parity bit may be taken at the RRAP level using implementation specific means such as redundant write commands or performing reads after writes to ensure the correctness of operations.

#### 222

#### 223

#### Table 2-5 RRAP Address Map

| UpperAddr | LowerAddr | Register Name         | Description                                                                                                                                                                                                                                                                                           |

|-----------|-----------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0       | 0x00-0xFF | As defined in [M-PHY] | Capability, configuration and status attributes for PAIRO. Writes to these registers shall only affect the shadow bank until an RCT is executed. The Target shall provide a Write Response only after the corresponding Register Write specified in the RRAP Command is committed to the shadow bank. |

| 0x1       | 0x00-0xFF | As defined in [M-PHY] | Capability, configuration and status attributes for PAIR1. Writes to these registers shall only affect the shadow bank until an RCT is executed. The Target shall provide a Write Response only after the corresponding Register Write specified in the RRAP Command is committed to the shadow bank. |

| UpperAddr | LowerAddr | Register Name         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|-----------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x2       | 0x00-0xFF | As defined in [M-PHY] | Capability, configuration and status attributes for PAIR2. Writes to these registers shall only affect the shadow bank until an RCT is executed. The Target shall provide a Write Response only after the corresponding Register Write specified in the RRAP Command is committed to the shadow bank.                                                                                                                                                                   |

| 0x3       | 0x00-0xFF | As defined in [M-PHY] | Capability, configuration and status attributes for PAIR3. Writes to these registers shall only affect the shadow bank until an RCT is executed. The Target shall provide a Write Response only after the corresponding Register Write specified in the RRAP Command is committed to the shadow bank.                                                                                                                                                                   |

| 0x4       | 0x00      | DSP_DISCONNECT        | This Register is used by a DSP following a LINE-RESET to signal a DSP Disconnect. This bit is required only for an USP only. A DSP or a USP in the MPHY.TEST state shall ignore writes to this register.                                                                                                                                                                                                                                                                |

|           |           |                       | Read/Write Attributes:                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           |           |                       | • R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           |           |                       | Reset Default:                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           |           |                       | • 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           |           |                       | Bit [0]:                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           |           |                       | <ul> <li>Writing 1'b1 signals a DSP disconnect as detailed in Section 5.1.2.</li> <li>Writing 1'b0 shall have no effect.</li> </ul>                                                                                                                                                                                                                                                                                                                                     |

|           |           |                       | Once the bit is set, it shall only be reset via a LINE-RESET issued either by a DSP (as part of Warm Reset) or by Test Equipment.                                                                                                                                                                                                                                                                                                                                       |

|           |           |                       | Bit [7:1] Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |           |                       | Writes shall be ignored and Reads shall return zero values.                                                                                                                                                                                                                                                                                                                                                                                                             |

|           |           |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0x4       | 0x01      | CONFIGURE_FOR_HS      | This Register is used to direct the Target to update its shadow bank for HS-BURST with the settings that correspond to the SSIC profile supported. As noted in Section 2.2.1 this profile is statically determined and this supplement provides no means for selecting between different profiles if so supported. The Target shall provide a Write Response only after the corresponding Register Write specified in the RRAP Command is committed to the shadow bank. |

| UpperAddr | LowerAddr | Register Name      | Description                                                                                                                                                                                             |

|-----------|-----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |           |                    | A Master may alternatively choose to not use this register in which case it shall rely on a set of implementation-specific RRAP commands to update the shadow bank of the Target for HSBURST operation. |

|           |           |                    | Read/Write Attributes:                                                                                                                                                                                  |

|           |           |                    | • R/W                                                                                                                                                                                                   |

|           |           |                    | Reset Default:                                                                                                                                                                                          |

|           |           |                    | • 0x00                                                                                                                                                                                                  |

|           |           |                    | Bit [0]:                                                                                                                                                                                                |

|           |           |                    | <ul> <li>Writing 1'b1 directs the Target to update its shadow bank with the settings that correspond to its SSIC profile.</li> <li>Writing 1'b0 shall have no effect.</li> </ul>                        |

|           |           |                    | Once the bit is set, it shall only be reset via a LINE-RESET issued either by a DSP (as part of Warm Reset) or by Test Equipment.                                                                       |

|           |           |                    | Bit[7:1] Reserved.                                                                                                                                                                                      |

|           |           |                    | Writes shall be ignored and Reads shall return zero values.                                                                                                                                             |

| 0x4       | 0x02      | BURST_CLOSURE      | This Register is used to direct the Target to                                                                                                                                                           |

|           |           |                    | terminate the PWM-BURST.                                                                                                                                                                                |