# Systematic Design of Analog IP Blocks

J. Vandenbussche G. Gielen M. Steyaert

Kluwer Academic Publishers

## Systematic Design of Analog IP Blocks

#### J. Vandenbussche, G. Gielen, M. Steyaert

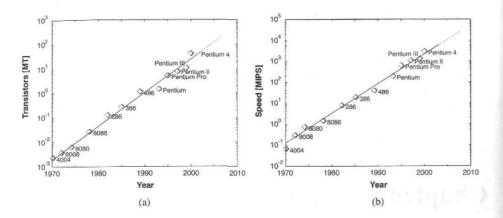

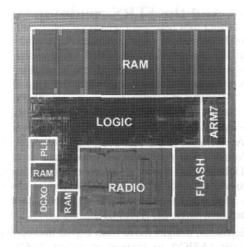

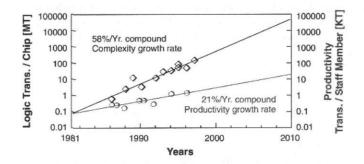

The ever-decreasing feature size has continuously provided improved functionality at a reduced cost. As the feature size decreased, designs moved from digital microprocessors and application specific integrated circuits (ASICs) to systems-on-a-chip (SoC). The design capabilities of the designer however, have not been increased equally. Analog design tools are only just emerging, and the design of the small analog part in the hostile digital environment has become a tremendous bottleneck.

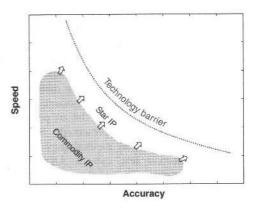

Systematic Design of Analog IP Blocks introduces a design methodology that can help to bridge the productivity gap. Two different types of designs, depending on the design challenge, have been identified: commodity IP and star IP. Each category requires a different approach to boost design productivity. Commodity IP blocks are well-suited to be automated in an analog synthesis environment and provided as soft IP. The design knowledge is usually common knowledge, and re-use is high accounting for the setup time needed for the analog library. Star IP still changes as technology evolves and the design cost can only be reduced by following a systematic design approach supported by point tools to relieve the designer from error-prone, repetitive tasks, allowing him/her to focus on new ideas to push the limits of the design.

To validate the presented methodologies, three different industrial-strength applications have been selected and designed accordingly.

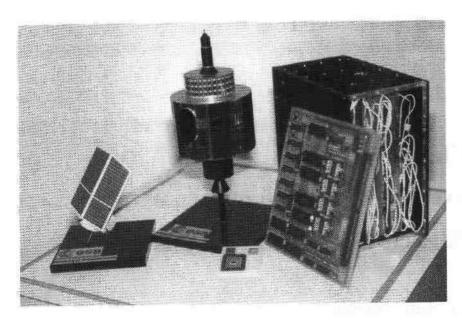

Firstly, a particle detector front-end for space applications has been designed and embedded in the Amgie library for further re-use. Performance compares favorable to an earlier manual design. Starting from specification, a physical layout can be generated within a few days.

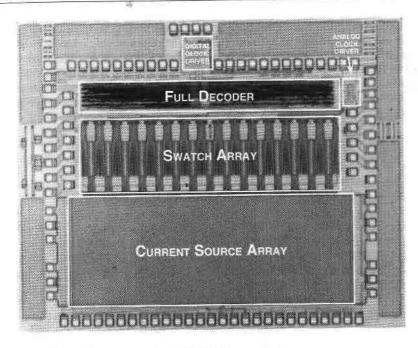

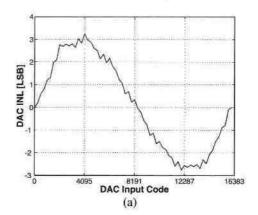

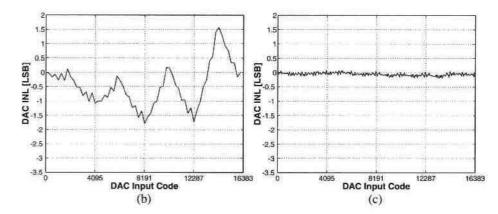

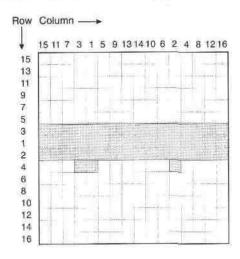

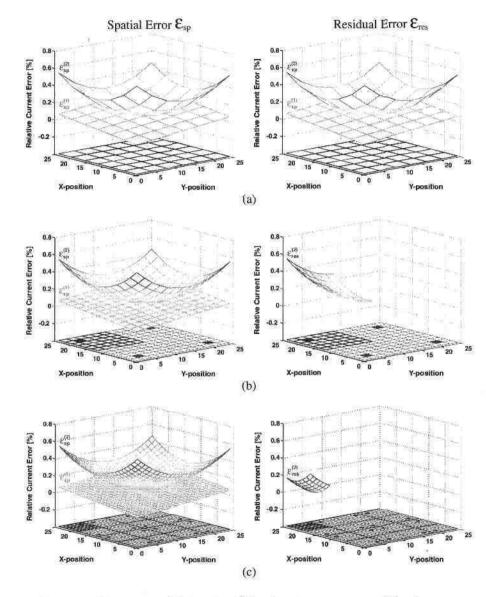

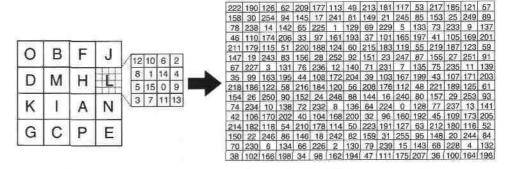

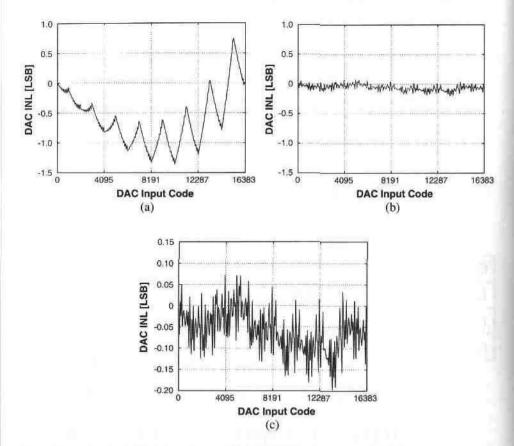

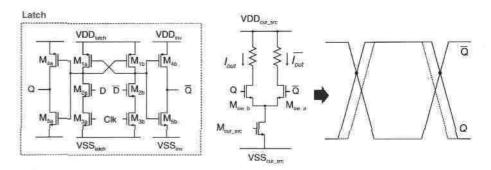

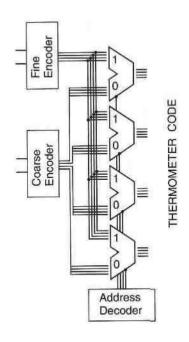

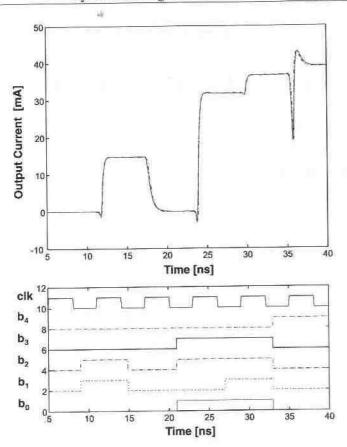

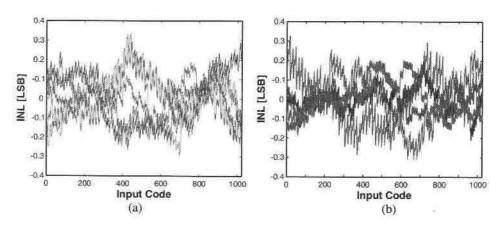

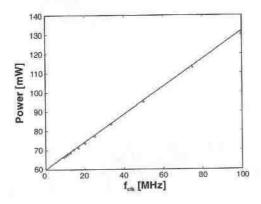

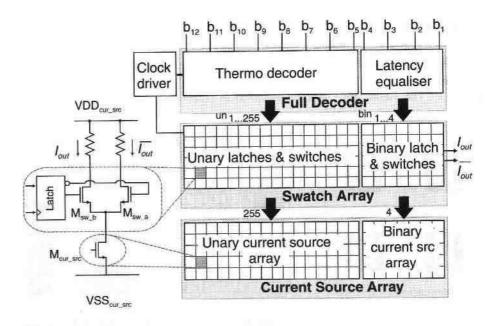

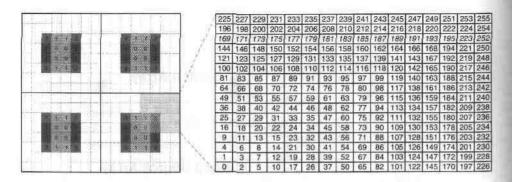

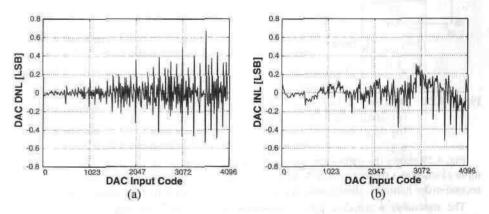

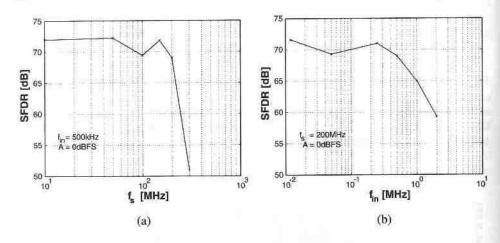

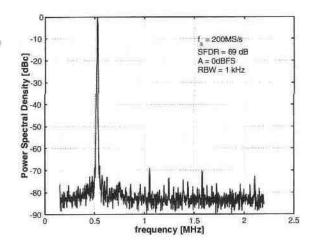

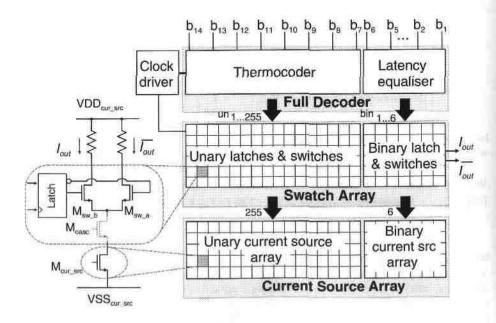

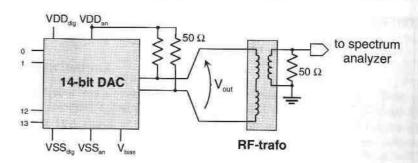

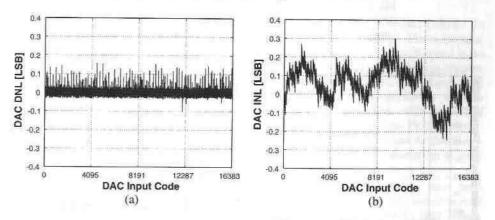

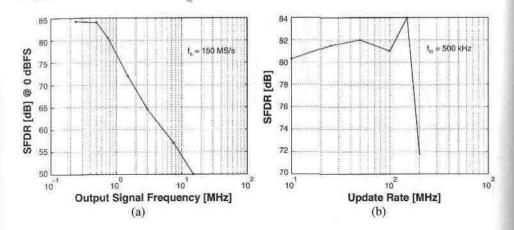

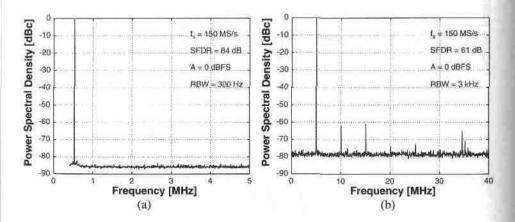

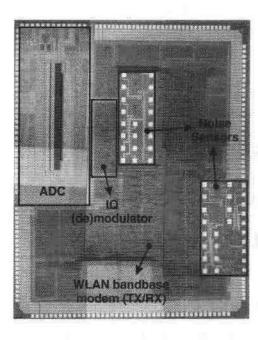

Secondly, current-steering D/A converters have been selected as test-engine for the design methodology of star IP. A novel topology has been developed allowing full flexibility to the designer in terms of switching scheme. This allowed the designer to implement the  $Q^2$  Random Walk switching scheme which averages out random and systematic errors resulting in the first intrinsic 14-bit linear D/A converter in CMOS technology. The overall design time was reduced from 11 to 4 man weeks.

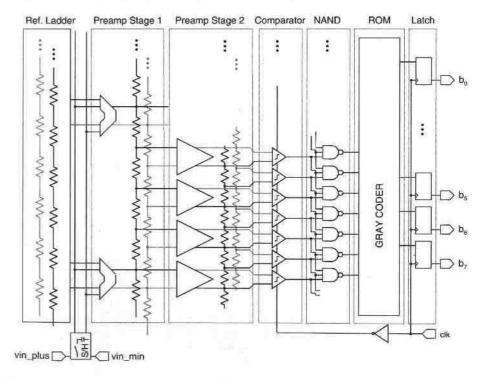

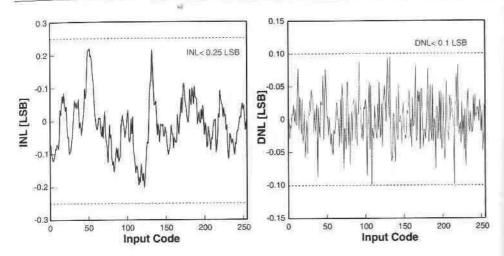

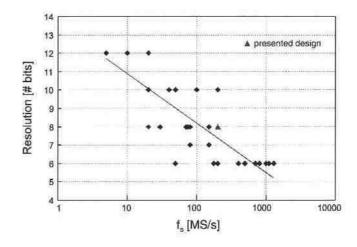

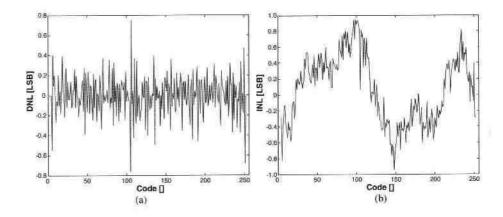

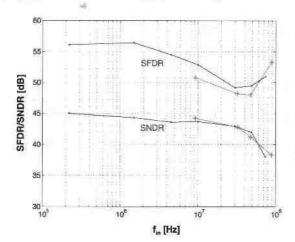

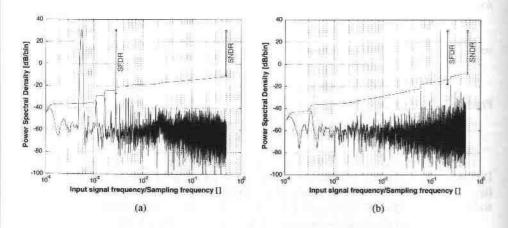

As third and final test-case, an 8-bit 200MS/s interpolating/averaging A/D converter has been designed. Performance and design times compare favorable to an earlier manual design.

All experiments prove that despite a general disbelieve, design cost can be reduced considerably, without compromising performance, by adopting the proper design methodology.

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN 1-4020-7471-9

Published by Kluwer Academic Publishers, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

Sold and distributed in North, Central and South America by Kluwer Academic Publishers, 101 Philip Drive, Norwell, MA 02061, U.S.A.

In all other countries, sold and distributed by Kluwer Academic Publishers, P.O. Box 322, 3300 AH Dordrecht, The Netherlands.

Printed on acid-free paper

All Rights Reserved

© 2003 Kluwer Academic Publishers, Boston

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed in the Netherlands.

## **Contents**

| Abbrev  | riations                                             | ix |

|---------|------------------------------------------------------|----|

| Preface |                                                      | xi |

| Chapte  | r 1 Introduction                                     | 1  |

| 1.1     | Moore's law and the ITRS roadmap revisited           | 1  |

| 1.2     | Bridging the productivity gap                        | 3  |

| 1.2.    | .1 Analog design productivity                        | 4  |

| 1.2.    | 2 Analog IP                                          | 6  |

| 1.3     | Goals of this work                                   | 8  |

| 1.4     | Outline of this work                                 | 8  |

| Chapte  | r 2 Design Methodologies for analog IP               | 11 |

| 2.1     | Used terminology                                     | 11 |

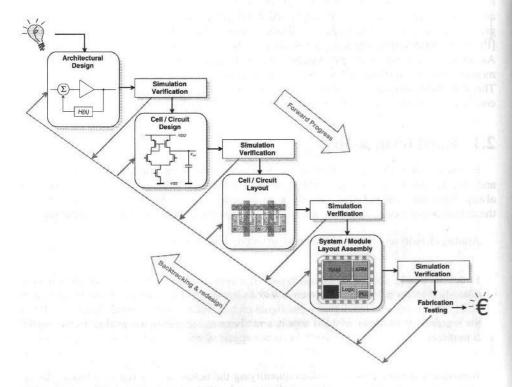

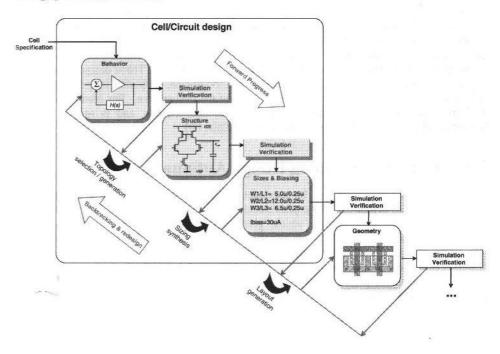

| 2.2     | The analog design process                            | 12 |

| 2.3     | Overview of Analog Design Automation                 | 14 |

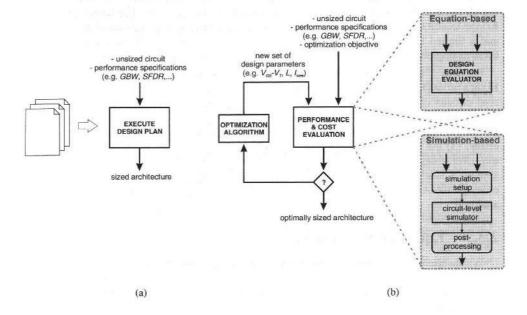

| 2.3.    | 1 Plan-based sizing                                  | 15 |

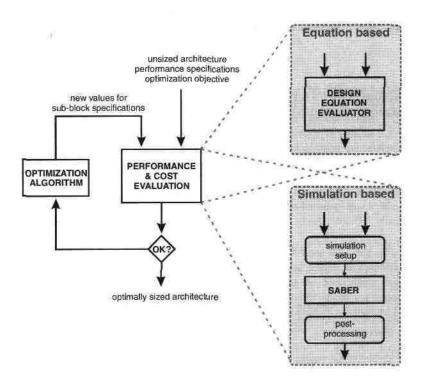

| 2.3.    | 2 Simulation-based sizing                            | 16 |

| 2.3.    | 3 Equation-based sizing                              | 16 |

| 2.      | .3.3.1 Geometric programming                         | 16 |

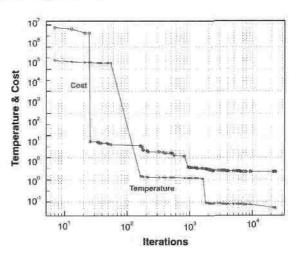

| 2.      | .3.3.2 The AMGIE framework                           | 17 |

| 2.3.    | 4 Research                                           | 18 |

| 2.4     | Commodity IP vs. star IP                             | 18 |

| 2.4.    | 1 Commodity IP                                       | 19 |

| 2.4.    | 2 Star IP                                            | 19 |

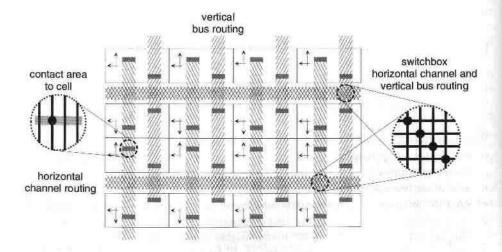

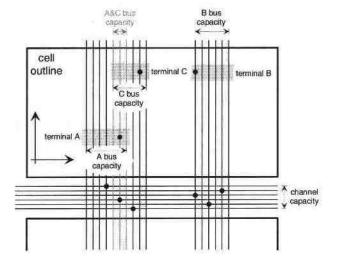

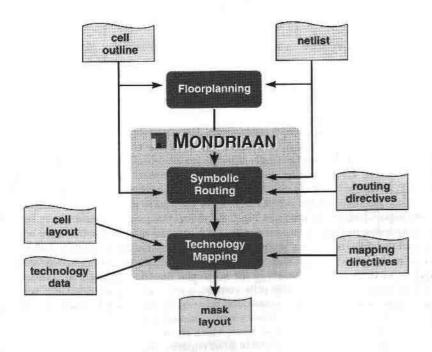

| 2.5     | The MONDRIAAN toolset                                | 22 |

| 2.5.    | 1 Requirements of the MONDRIAAN toolset              | 23 |

| 2.5.    | 2 Description of the Layout Model                    | 24 |

| 2.5.    | 3 Description of the Layout Generation Methodology   | 26 |

| 2.5.    | 4 Productivity gain through the MONDRIAAN toolset    | 29 |

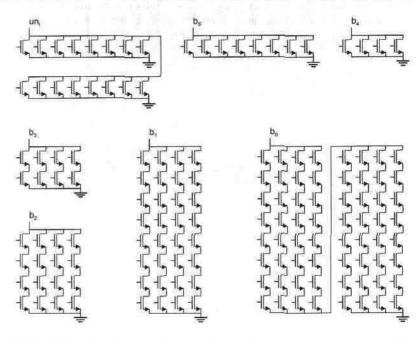

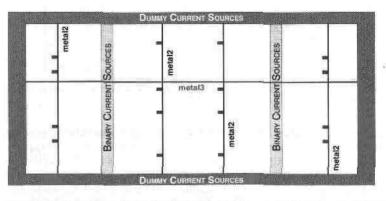

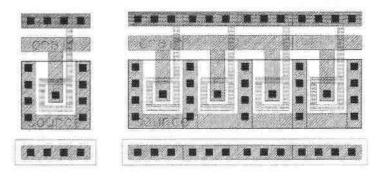

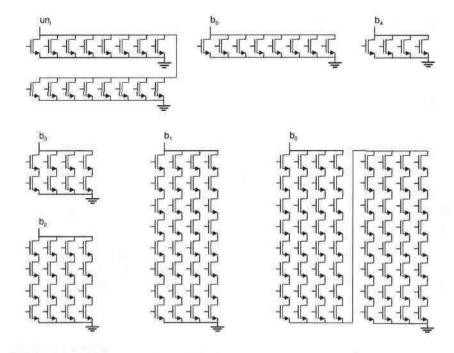

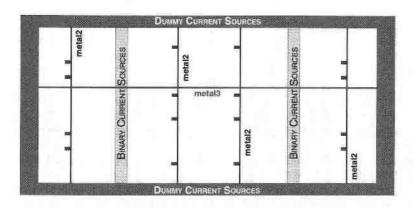

| 2.      | .5.4.1 Current-steering D/A converter modules        | 30 |

| 2.      | .5.4.2 Interpolating/averaging A/D converter modules | 33 |

| 2.6    | Con                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | clusions                                                                                                                                                                                                                                                                                     | 34                                                                            |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Chapte |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                              | 35                                                                            |

| 3.1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                              | 35                                                                            |

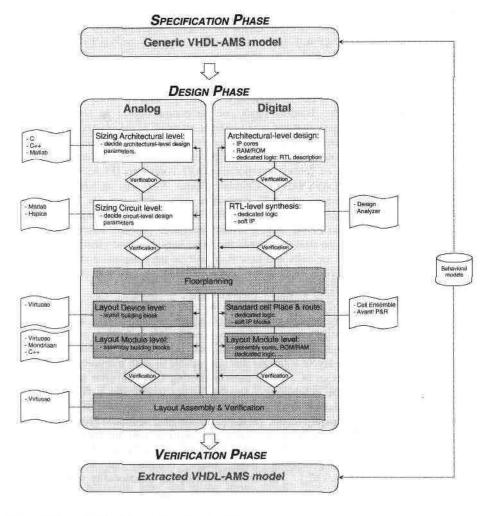

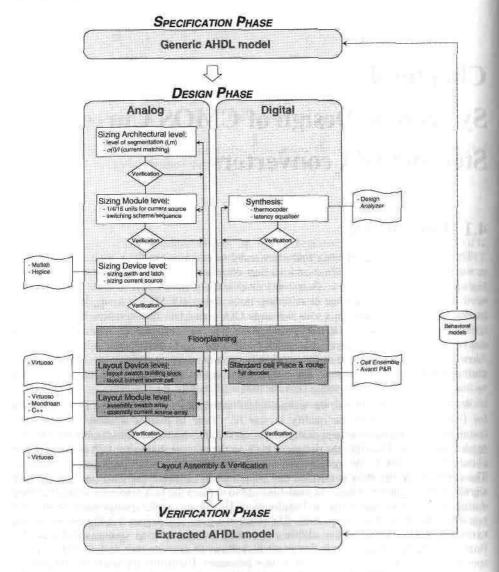

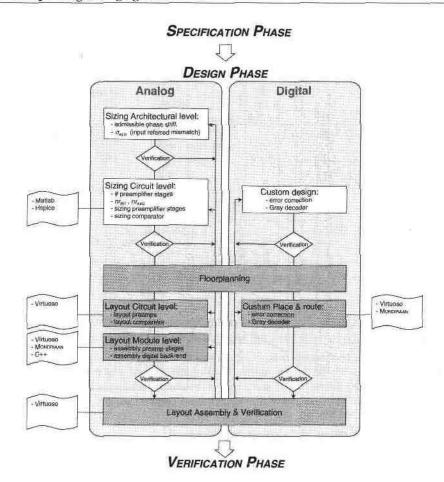

| 3.2    | PDF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | E design flow                                                                                                                                                                                                                                                                                | 37                                                                            |

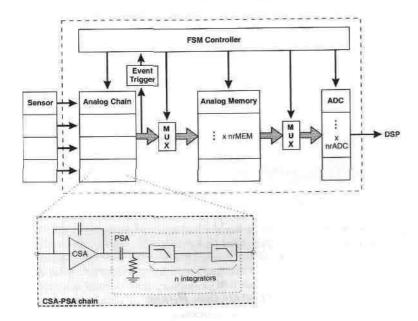

| 3.3    | PDF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | E architecture                                                                                                                                                                                                                                                                               | 38                                                                            |

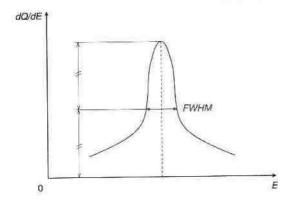

| 3.4    | Beha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | avioral modeling for system-level specification phase                                                                                                                                                                                                                                        | 41                                                                            |

| 3.5    | PDF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | E Design phase                                                                                                                                                                                                                                                                               | 42                                                                            |

| 3.5    | .1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PDFE architectural-level synthesis                                                                                                                                                                                                                                                           | 42                                                                            |

| 3      | .5.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Specifications for the building blocks                                                                                                                                                                                                                                                       | 47                                                                            |

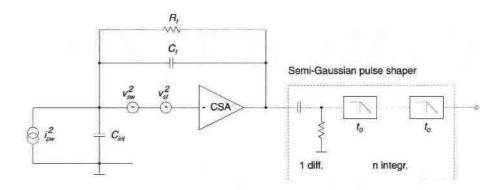

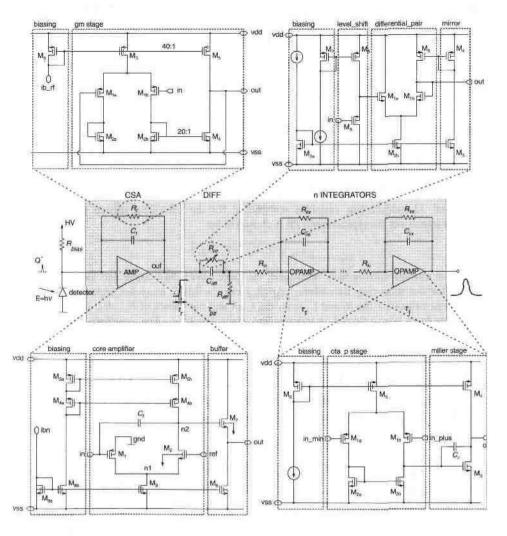

| 3.5    | .2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CSA-PSA circuit-level synthesis                                                                                                                                                                                                                                                              | 49                                                                            |

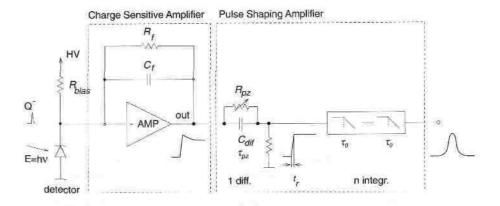

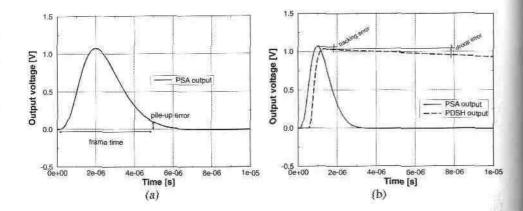

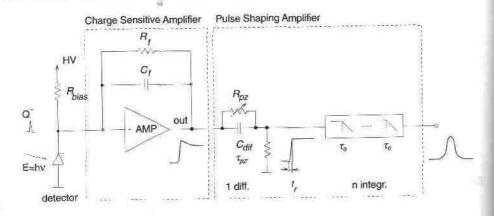

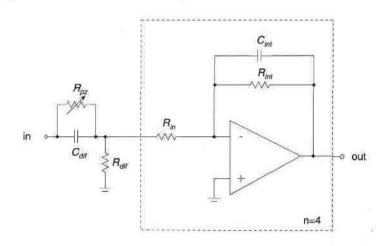

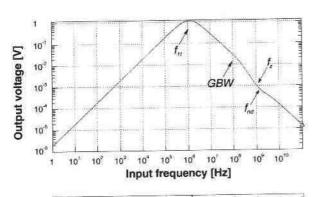

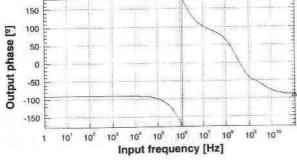

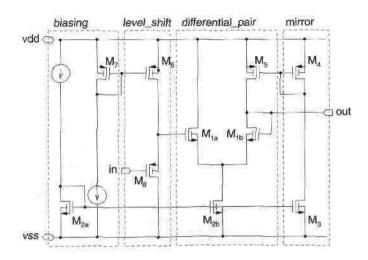

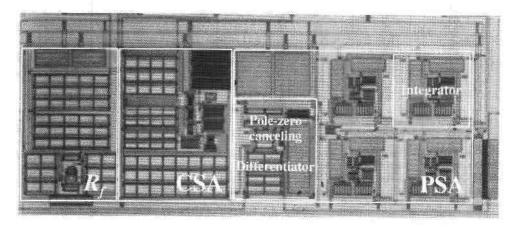

| 3      | .5.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The CSA-PSA architecture                                                                                                                                                                                                                                                                     | 49                                                                            |

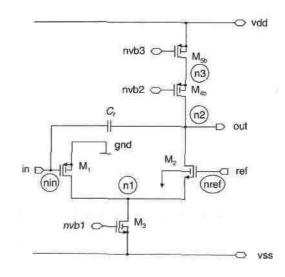

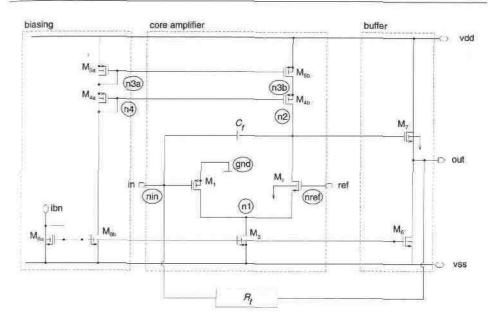

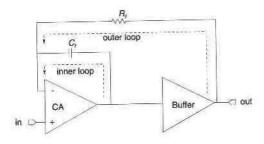

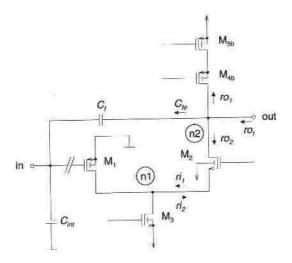

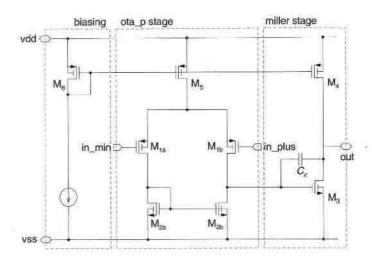

| 3      | .5.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The Charge Sensitive Amplifier                                                                                                                                                                                                                                                               | 50                                                                            |

| 3      | .5.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The Pulse-Shaping Amplifier with pole-zero cancellation                                                                                                                                                                                                                                      | 60                                                                            |

| 3      | .5.2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                              |                                                                               |

| 3      | .5.2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CSA-PSA noise analysis                                                                                                                                                                                                                                                                       | 66                                                                            |

| 3      | .5.2.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The CSA-PSA as soft IP library cell                                                                                                                                                                                                                                                          | 72                                                                            |

| 3.6    | Layo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | out                                                                                                                                                                                                                                                                                          | 77                                                                            |

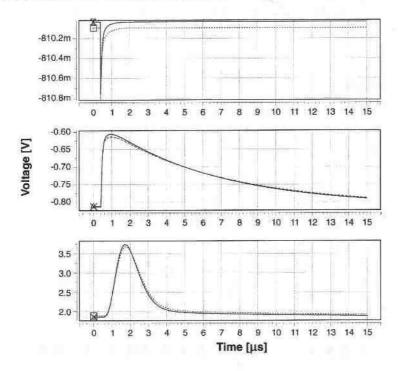

| 3.7    | Extr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | acted model for verification                                                                                                                                                                                                                                                                 | 78                                                                            |

| 3.8    | Expe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | erimental results                                                                                                                                                                                                                                                                            | 78                                                                            |

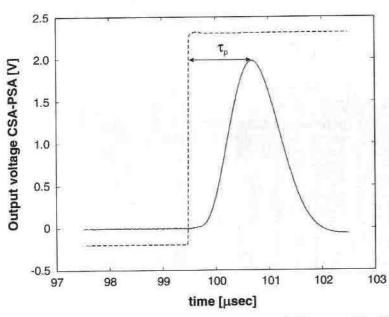

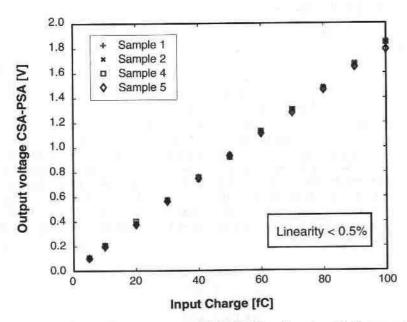

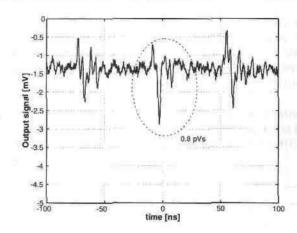

| 3.8    | .1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Functional Testing                                                                                                                                                                                                                                                                           | 79                                                                            |

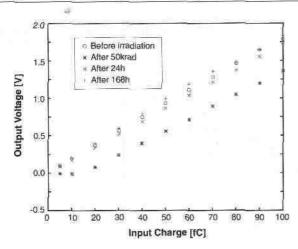

| 3.8    | .2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Radiation Testing                                                                                                                                                                                                                                                                            | 81                                                                            |

| 3.9    | Cone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | clusions                                                                                                                                                                                                                                                                                     | 82                                                                            |

| Chapte | r 4 Sy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | stematic Design of CMOS Current-Steering D/A converters                                                                                                                                                                                                                                      | 83                                                                            |

| 4.1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                              |                                                                               |

| 4.2    | D/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | converter Design Flow                                                                                                                                                                                                                                                                        | 85                                                                            |

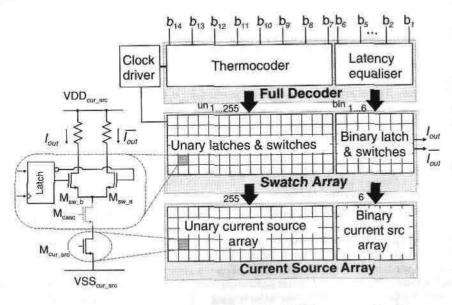

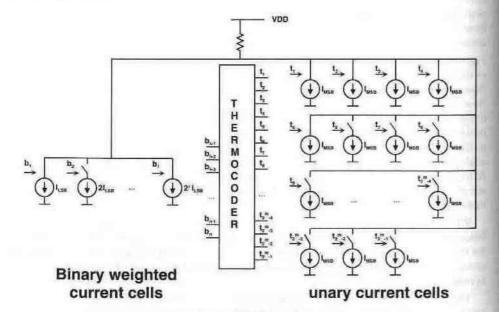

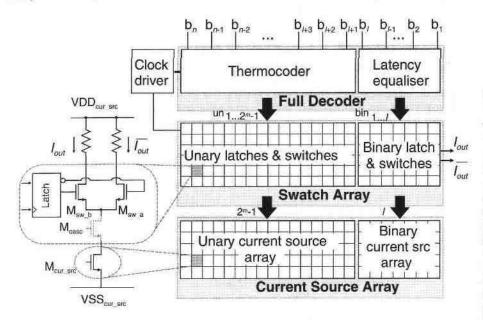

| 4.3    | Curr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ent-steering D/A converter architecture                                                                                                                                                                                                                                                      | 86                                                                            |

| 4.4    | Beha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | avioral Modeling for the Specification Phase                                                                                                                                                                                                                                                 | 89                                                                            |

| 4.4    | .1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Dynamic behavior                                                                                                                                                                                                                                                                             | 89                                                                            |

| 4.4    | .2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Static behavior                                                                                                                                                                                                                                                                              | 91                                                                            |

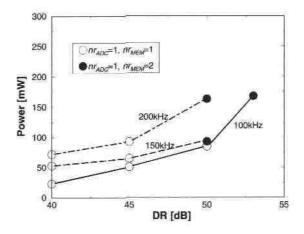

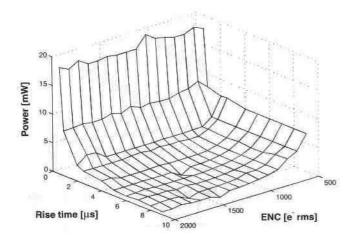

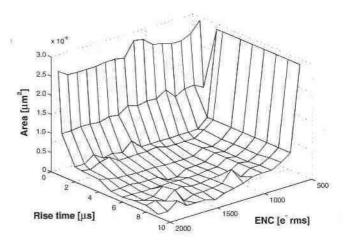

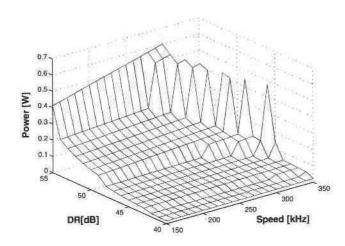

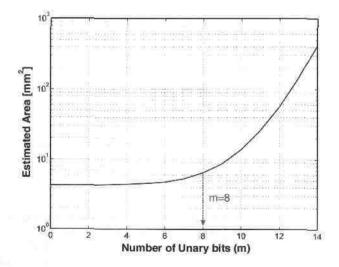

| 4.4    | .3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Power and Area Estimators                                                                                                                                                                                                                                                                    | 92                                                                            |

| 4.5    | Desi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | gn Phase                                                                                                                                                                                                                                                                                     | 93                                                                            |

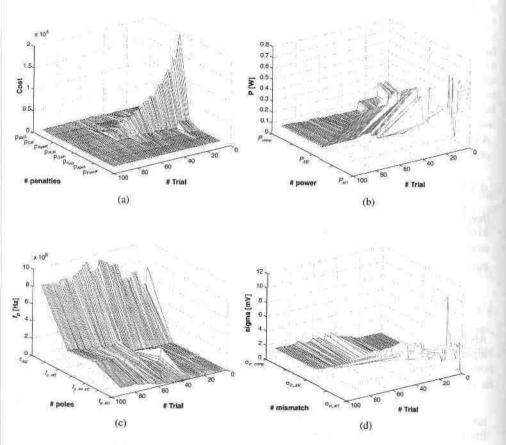

| 4.5    | .1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Architectural-level synthesis                                                                                                                                                                                                                                                                | 93                                                                            |

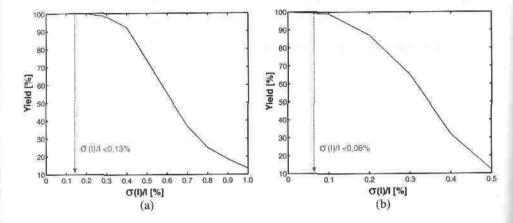

| 4      | .5.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Static performance                                                                                                                                                                                                                                                                           | 93                                                                            |

| 4      | .5.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Dynamic performance                                                                                                                                                                                                                                                                          | 94                                                                            |

| 4.5    | .2 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Module-level synthesis                                                                                                                                                                                                                                                                       | 96                                                                            |

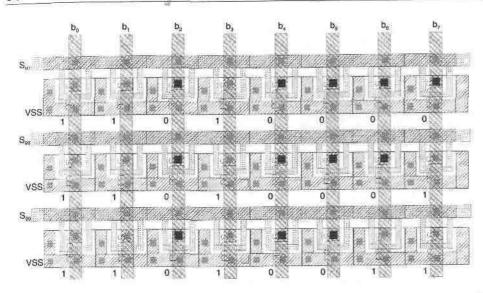

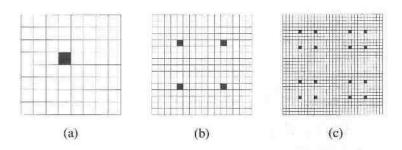

| 4      | .5.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Overview of switching schemes                                                                                                                                                                                                                                                                | 96                                                                            |

| 4      | .5.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Compensating graded and systematic errors                                                                                                                                                                                                                                                    | 99                                                                            |

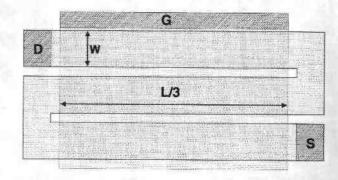

| 4.5    | .3 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Circuit-level synthesis                                                                                                                                                                                                                                                                      | 105                                                                           |

| 4      | .5.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Static Performance                                                                                                                                                                                                                                                                           | 105                                                                           |

|        | Chapte 3.1 3.2 3.3 3.4 3.5 3.5 3.5 3.3 3.5 3.6 3.7 3.8 3.8 3.9 Chapte 4.1 4.2 4.3 4.4 4.4 4.5 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4.5 4 4 4.5 4 4 4.5 4 4 4 4 | 3.1 Intro 3.2 PDF 3.3 PDF 3.3 PDF 3.4 Beh 3.5 PDF 3.5.1 3.5.1.2 3.5.2.1 3.5.2.2 3.5.2.3 3.5.2.4 3.5.2.5 3.5.2.6 3.6 Layo 3.7 Extr 3.8 Expe 3.8.1 3.8.2 3.9 Conc Chapter 4 Sy 4.1 Intro 4.2 D/A 4.3 Curr 4.4 Beh 4.4.1 4.4.2 4.4.3 4.5 Desi 4.5.1.1 4.5.1.2 4.5.2.1 4.5.2.2 4.5.2.2 4.5.3 (6) | Chapter 3 Systematic Design of a Particle Detector Front-End 3.1 Introduction |

| 4.5.3.2            | Dynamic performance                                          | 107 |

|--------------------|--------------------------------------------------------------|-----|

| \$10.00 TWO TO COM |                                                              |     |

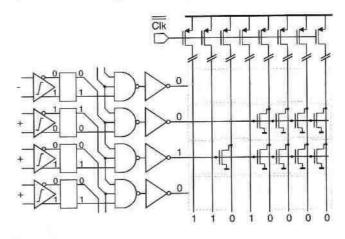

| 4.5.3.3            | Full Decoder Synthesis                                       |     |

| 4.5.4              | Clock Driver Synthesis                                       |     |

| 4.5.5              | cock Driver Synthesis                                        |     |

|                    |                                                              |     |

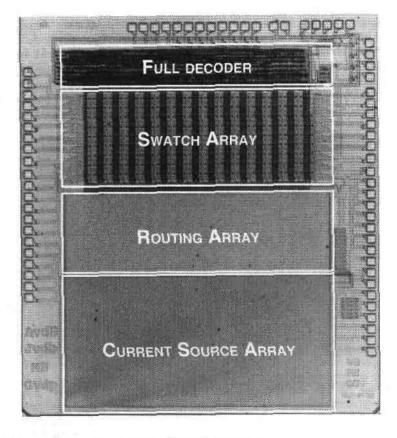

| 4.6.1              | Floorplanning                                                |     |

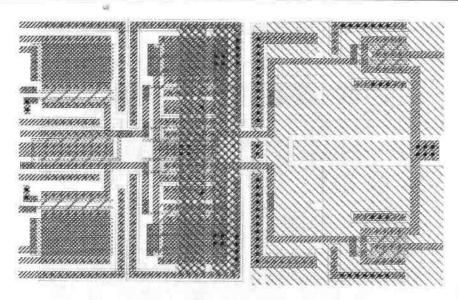

| 4.6.2              | Circuit and Module Layout Generation                         |     |

| 4.6.2.1            | 할 수 없는 사람들은 사람들은 사람들은 사람들은 사람들은 사람들은 사람들은 사람들은               |     |

| 4.6.2.2            |                                                              |     |

| 4.6.2.3            |                                                              |     |

| 4.6.3              | Layout Assembly                                              |     |

|                    | racted (A)HDL model for verification                         |     |

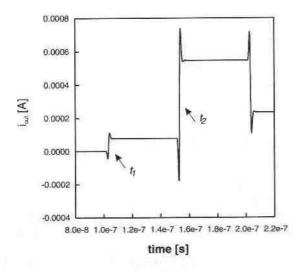

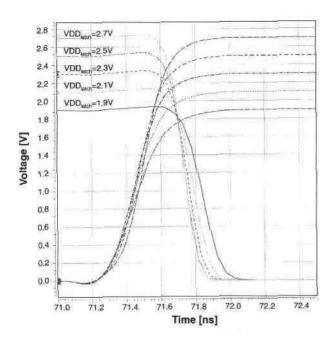

| 4.7.1              | Dynamic behavior                                             |     |

| 4.7.2              | Static behavior                                              |     |

| 4.7.3              | Power and Area Estimators                                    |     |

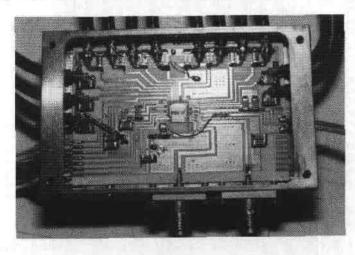

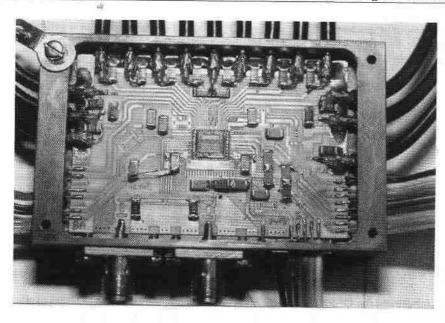

| CONTRACT STREET    | perimental Results                                           |     |

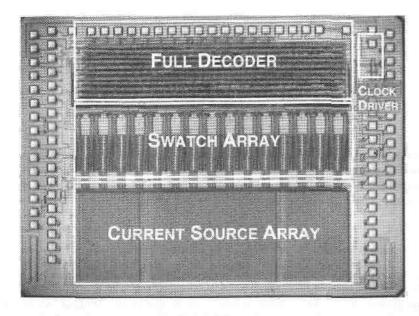

| 4.9 A 1            | 2-bit 200 MS/s CMOS D/A converter                            |     |

| 4.9.1              | Introduction                                                 |     |

| 4.9.2              | D/A converter Architecture                                   |     |

| 4.9.3              | D/A converter Synthesis                                      |     |

| 4.9.4              | Conclusions                                                  |     |

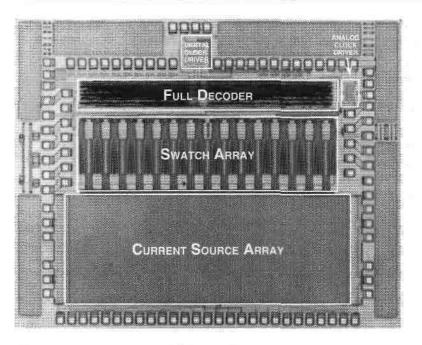

| 4.10 A 1           | 4-bit 150 MS/s Q2 Random Walk CMOS D/A converter             |     |

| 4,10.1             | Introduction                                                 | 126 |

| 4.10.2             | D/A converter Architecture                                   | 127 |

| 4.10.3             | D/A converter Synthesis                                      | 128 |

| 4.10.4             | Conclusions                                                  | 137 |

| 4.11 Co            | nclusions on D/A converter Methodology                       | 137 |

| Chapter 5 S        | ystematic Design of an Interpolating/Averaging A/D Converter | 139 |

| 5.1 Inti           | oduction                                                     | 139 |

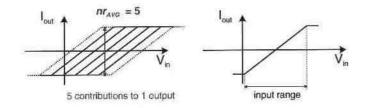

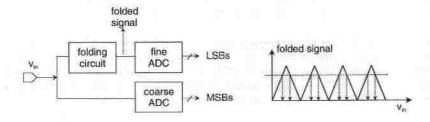

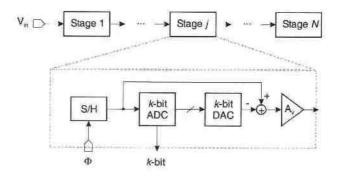

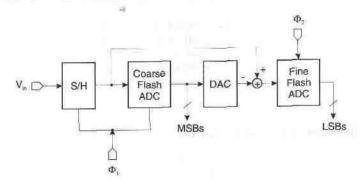

| 5.2 Hig            | ch-speed A/D converter architectures                         | 140 |

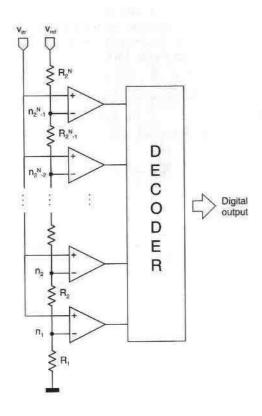

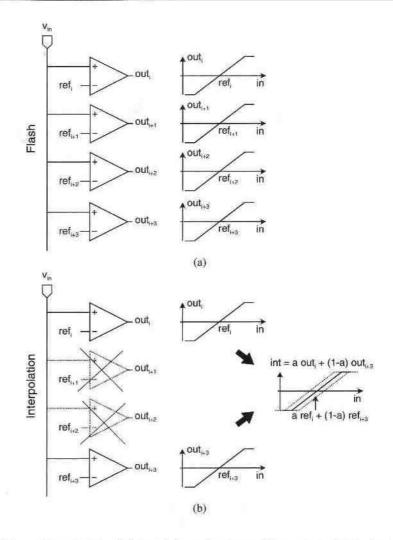

| 5.2.1              | The flash architecture                                       | 141 |

| 5.2.2              | The pipelined architecture                                   | 145 |

| 5.2.3              | Two-step architectures                                       | 145 |

| 5.3 A/I            | O Converter Design Flow                                      | 146 |

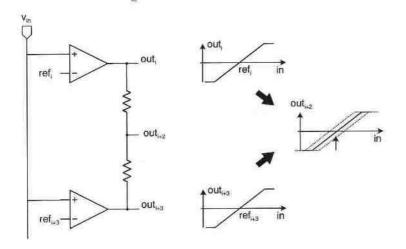

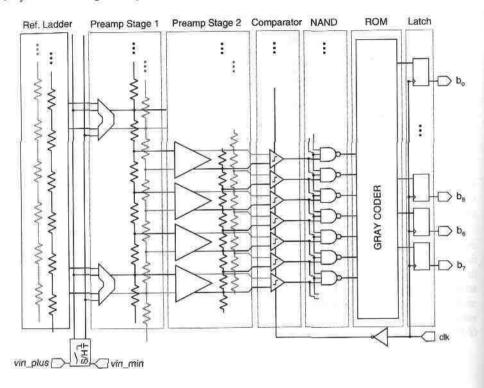

| 5.4 The            | e interpolating/averaging architecture                       | 147 |

| 5.5 Bel            | navioral Modeling for the Specification Phase                | 150 |

| 5.6 De             | sign phase                                                   | 151 |

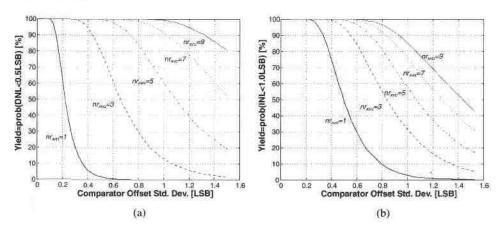

| 5.6.1              | Architectural-level synthesis                                | 151 |

| 5.6.1.1            | Static performance                                           | 151 |

| W. | ď | п | 8 |  |

|----|---|---|---|--|

| v  | 3 | ш |   |  |

|   |              | NI CONTRACTOR OF THE CONTRACTO |

|---|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 5.6.1.2      | Dynamic performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

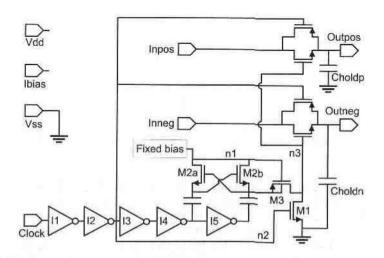

|   | 5.6.2        | Circuit-level synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

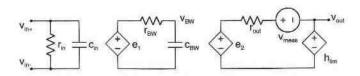

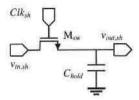

|   | 5.6.2.1      | Sample and hold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

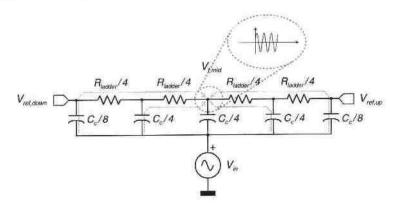

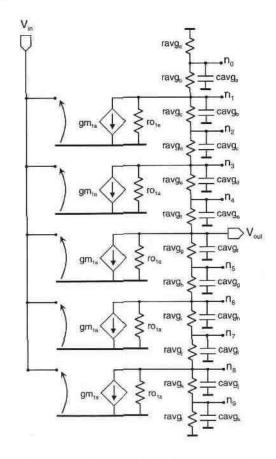

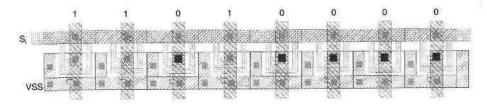

|   | 5.6.2.2      | Reference ladder network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

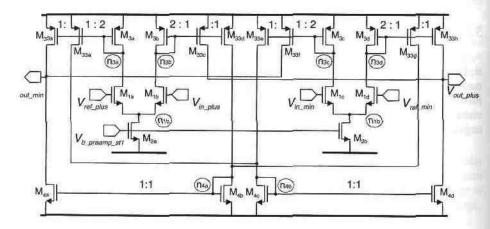

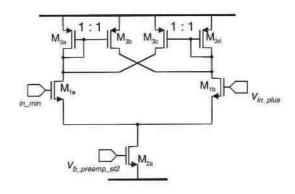

|   | 5.6.2.3      | Preamplifier stage 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 5.6.2.4      | Preamplifier stage 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

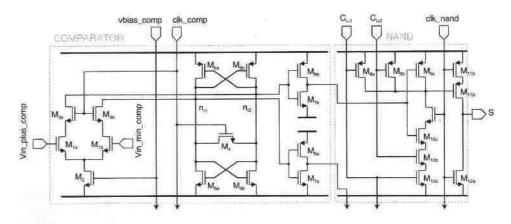

|   | 5.6.2.5      | 1/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 5.6.2.6      | Sizing plan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

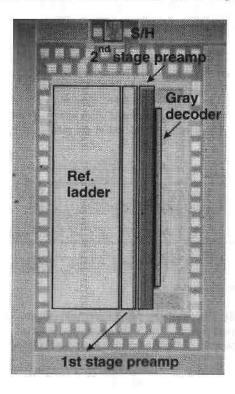

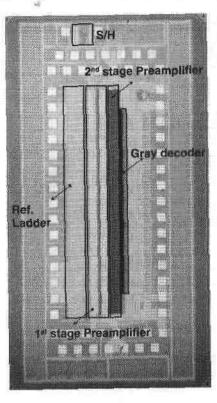

|   | 5.7 Lay      | out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 5.8 Veri     | fication Phase171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

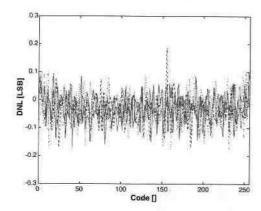

|   | 5.9 Exp      | erimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |