# Analog Dialogue

A forum for the exchange of circuits, systems, and software for real-world signal processing • Volume 49, Number 3, 2015

- 2 Editor's Notes; New Product Introductions

- 3 Four Quick Steps to Production: Using Model-Based Design for Software-Defined Radio Part 1—the Analog Devices/Xilinx SDR Rapid Prototyping Platform: Its Capabilities, Benefits, and Tools

- 10 New Advances in Energy Harvesting Power Conversion

- 13 A Low Power Data Acquisition Solution for High Temperature Electronics Applications

- 19 Analyzing, Optimizing, and Eliminating Integer Boundary Spurs in Phase-Locked Loops with VCOs at up to 13.6 GHz

- 22 Interleaving ADCs: Unraveling the Mysteries

- 27 Zero-Drift Amplifiers: Now Easy to Use in High Precision Circuits

### **Editor's Notes**

#### IN THIS ISSUE

# Four Quick Steps to Production: Using Model-Based Design for Software-Defined Radio

# Part 1—the Analog Devices/Xilinx SDR Rapid Prototyping Platform: Its Capabilities, Benefits, and Tools

This article series examines the advances in platforms and tools that allow developers to quickly simulate and prototype wireless radio systems while establishing and maintaining a deployable path to production. As a real-world walkthrough of the process, the authors will design and prototype a wireless SDR platform that receives and decodes ADS-B aircraft signals. In this first part, the article discusses the Analog Devices/Xilinx® SDR prototyping system, its capabilities and benefits, and a brief description of the tool flow. (Page 3)

#### New Advances in Energy Harvesting Power Conversion

Today many power management integrated circuits are available that were specifically designed for use in energy harvesting applications. They enable systems to run with smaller harvesters or make energy harvesting solutions possible that could not have been designed a few years ago. This article looks at several energy harvesting applications and describes a high efficiency dc-to-dc conversion and voltage regulation solution that solves energy harvesting challenges. (Page 10)

#### A Low Power Data Acquisition Solution for High Temperature Electronics Applications

A growing number of applications require data acquisition systems that must operate reliably at very high ambient environments, such as downhole oil and gas drilling, avionics, and automotive. This article presents a new reference design for high temperature data acquisition, characterized from room temperature to 175°C. (Page 13)

#### Analyzing, Optimizing, and Eliminating Integer Boundary Spurs in Phase–Locked Loops with VCOs at up to 13.6 GHz

A phase-locked loop (PLL) and voltage controlled oscillator (VCO) outputs an RF signal at a certain frequency, and ideally this signal would be the only signal present at the output. In reality, there are unwanted spurious signals and phase noise at the output. This article discusses the simulation and elimination of one of the more trouble-some spurious signals—integer boundary spurs. (Page 19)

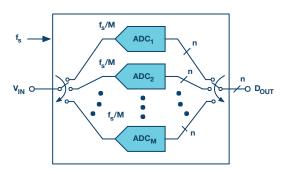

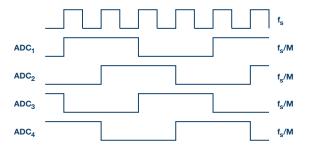

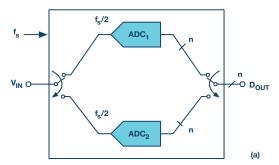

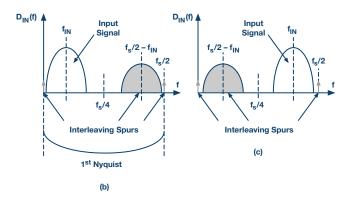

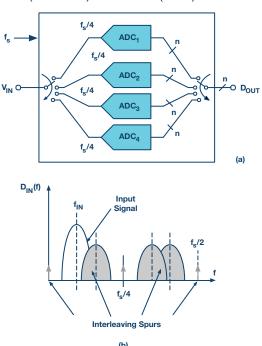

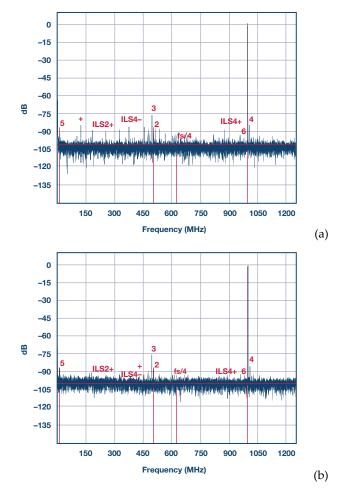

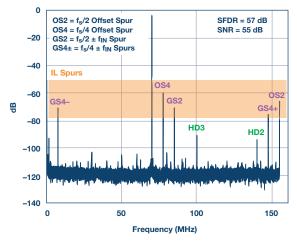

#### Interleaving ADCs: Unraveling the Mysteries

Time interleaving is a technique that allows the use of multiple identical analog-to-digital converters to process regular sample data series at a faster rate than the operating sampling rate of each individual data converter. This technique is frequently utilized in military and electronic instrumentation applications where there is a need to continually push the state-of-the-art in data conversion speeds, resolutions, and performance. This article explains the data converter interleaving technique in technical detail as well as focusing on some of the practical challenges associated with implementing this technique. (Page 22)

## Zero-Drift Amplifiers: Now Easy to Use in High Precision Circuits

A zero-drift amplifier, as the name suggests, is an amplifier with offset voltage drift very close to zero. It uses auto-zero or chopping technology, or a combination of both, to continuously self-correct for dc errors over time and temperature. This enables the amplifier to achieve microvolt level offsets and extremely low offset drifts, making it uniquely suited for signal conditioning circuits that require high gain and precision performance. This article explores the architecture of zero-drift amplifiers and provides insight into considerations for designing with these precision devices in drift-critical applications. (Page 27)

Jim Surber [jim.surber@analog.com]

#### Product Introductions: Volume 49, Number 3

Data sheets for all ADI products can be found by entering the part number in the search box at analog.com.

#### July

| 50 mA/500 mA, high efficiency, ultralow power step-down regulator                               |

|-------------------------------------------------------------------------------------------------|

| August                                                                                          |

| $14\text{-bit}, 1.25 \ GSPS \ JESD204B, \ dual \ analog-to-digital \ converter \mathbf{AD9691}$ |

| 1 MSPS, ultralow power, 12-bit ADC in 10-lead LFCSP and MSOPAD7091R-5                           |

| 31 W, filterless, class-D digital input audio amplifierSSM3515                                  |

| Robust, quad-channel isolator with input disable and 0 reverse channels                         |

| Low power 400 MHz Blackfin+ embedded processor with 256 kB L2 SRAMADSP-BF702                    |

| Low power 400 MHz Blackfin+ embedded processor with 512 kB L2 SRAMADSP-BF704                    |

| Low power 400 MHz Blackfin+ embedded processor with 1 MB L2 SRAMADSP-BF706                      |

| Isolated precision gate driver, 4 A output                                                      |

| Robust, triple-channel isolator with input disable and 0 reverse channels                       |

| Robust, triple-channel isolator with input disable and 1 reverse channel                        |

| Ultracompact, 1 A thermoelectric cooler (TEC) driver for digital control systemsADN8833         |

| Ultracompact, 1.5 A thermoelectric cooler (TEC) controllerADN8834                               |

| Single-/dual-supply high voltage isolated IGBT gate driver with miller clampADuM4135            |

| 18 V, 12 A step-down regulator with programmable current limit                                  |

| 18 V, 12 A step-down regulator with programmable current limit and PFMADP2390                   |

| 800 mA, dc-to-dc inverting regulatorADP5075                                                     |

| Integrated, precision battery sensors for automotive systems                                    |

### Analog Dialogue \_

Analog Dialogue, www.analog.com/analogdialogue, the technical magazine of Analog Devices, discusses products, applications, technology, and techniques for analog, digital, and mixed-signal processing. Published continuously for 49 years—starting in 1967—it is available in two versions. Monthly editions offer technical articles; timely information including recent application notes, circuit notes, newproduct briefs, webinars, and published articles; and a universe of links to important and relevant information on the Analog Devices website, www.analog.com. Printable quarterly issues and ebook versions feature collections of monthly articles. For history buffs, the Analog Dialogue archive, www.analog.com/library/analogdialogue/archives.html, includes all regular editions, starting with Volume 1, Number 1 (1967), and three special anniversary issues. To subscribe, please go to www.analog.com/library/analogdialogue/subscribe.html. Your comments are always welcome: Facebook: www.facebook.com/analogdialogue; EngineerZone: ez.analog.com/blogs/analogdialogue; Email: dialogue. editor@analog.com or Jim Surber, Editor [jim.surber@analog.com].

# Four Quick Steps to Production: Using Model-Based Design for Software-Defined Radio

Part 1—the Analog Devices/Xilinx SDR Rapid Prototyping Platform: Its Capabilities, Benefits, and Tools

By Di Pu, Andrei Cozma, and Tom Hill

#### Abstract

There is a significant gap between the concept of a wireless system and the realization of that working design. Bridging this gap typically involves teams of engineers with a variety of different skill sets (such as RF, SW, DSP, HDL, and embedded Linux®), and in many cases projects get derailed early in the development stage because of the difficulty in coordinating the efforts of these varied design entities.

In this four part article, we will examine the advances in platforms and tools that allow developers to quickly simulate and prototype wireless systems while establishing and maintaining a deployable path to production. As a real-world example of the process, we will prototype a wireless SDR platform that receives and decodes automatic dependent surveillance broadcast (ADS-B) signals to allow us to detect and report the position, altitude, and velocity of the commercial aircraft flying in our vicinity. The resources required in this case are MATLAB® and Simulink and the skills to integrate and embed hardware/software. The hardware platform will be the Analog Devices/Xilinx software-defined radio (SDR) prototyping system. Using MATLAB and Simulink® the following tasks will be performed:

- Design of signal processing algorithms used to decode ADS-B messages

- Simulation of the RF transceiver receiving ADS-B signals

- Generation of C and HDL code

- Verification of the HDL code with recorded and live data on the target transceiver and FPGA

The final result will be a working RF SDR design running on production-worthy hardware, which we will take to a local airport and verify its performance and functionality.

The first part of this four part article will discuss the Analog Devices/Xilinx SDR prototyping system, its capabilities and benefits, and a brief description of the tool flow. The second part will review the automatic dependent surveillance broadcast signals and explain how to decode their information in MATLAB and Simulink in simulation. The third part will describe and showcase how to use hardware in the loop (HIL) and capturing signals with the target transceiver, but still doing the signal processing on the host in Simulink for verification. The fourth part will show how to take the algorithm developed in Part 2, verified in Part 3, and use HDL Coder and Embedded Coder from MathWorks to generate code and deploy it in the production hardware, and finally we'll operate the platform with real-world ADS-B signals at an airport.

#### Introduction

With the exponential growth in the ways and means by which people need to communicate, modifying radio devices easily and cost effectively has become business critical. Based on this requirement, software-defined radio technology has been widely employed recently since it brings the flexibility, cost efficiency, and power to drive communications forward. The purpose of an SDR system is to implement as much as possible of the modulation/demodulation and data processing algorithms in software and reprogrammable logic so that the communication system can be easily reconfigured just by updating the software and the reprogrammable logic and not making any changes to the hardware platform.

With the advent of system on chip (SoC) devices like the Xilinx Zynq® All Programmable SoC that combine the versatility of a CPU and the processing power of an FPGA, designers have the means to consolidate the data processing functions of an SDR system into a single device while integrating additional processing tasks. Processing intensive tasks like the data modulation/demodulation algorithms are offloaded to the programmable logic of the device while tasks like data decoding and rendering, system monitoring and diagnosis, and user interface are deferred to the processing unit.

At the same time, prototyping wireless systems has been a discussion topic for decades but has only in recent years evolved into a complete design flow for FPGAs—from model creation to complete implementation—due to the evolution of the modeling and simulation tools like MATLAB and Simulink from MathWorks. Prototyping wireless systems is transforming the way engineers and scientists work by moving design tasks from the lab and field to the desktop.2 Now the entire wireless system, such as an SDR system, can be modeled, allowing the engineer to observe the system's behavior and to tune it before it is actually implemented in the field. This has several benefits, such as accelerating system integration and reducing the dependency on equipment availability. Moreover, once the Simulink model for the SDR system is complete, C and HDL code can be generated automatically for implementation on Zyng SoCs, saving time and avoiding the introduction of manually coded errors. The risk is further reduced by linking the system model to a rapid prototyping environment that allows the SDR system to be exercised under real-world conditions.

This first part of the four part article series will discuss the Analog Devices/Xilinx SDR rapid prototyping system, its capabilities and benefits, and a brief description of the tool flow. The article showcases how Analog Devices RF IC technology and reference design hardware and software require a reduced design skill subset, thus enabling customers to mitigate risk and shorten their time to market.

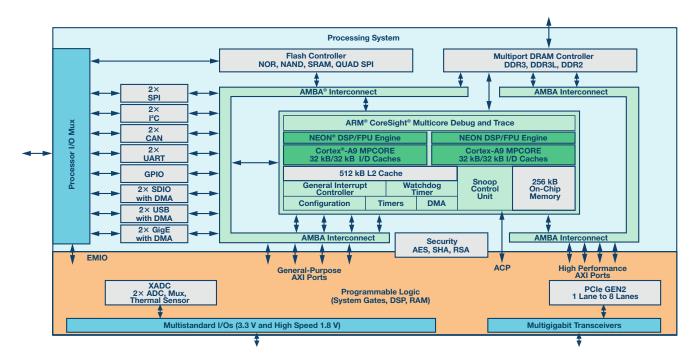

Figure 1. Xilinx Zynq SoC block diagram.

#### Zynq for SDR

Advanced SDR systems are required to execute a combination of data processing, communication, and user interface tasks that have different processing bandwidth requirements and real-time constraints. The hardware platform chosen to implement such a system must be robust and scalable at the same time allowing for future system improvements and expansion. Xilinx Zynq-7000 All Programmable SoCs fulfill these requirements by supplying a high performance processing system combined with programmable logic as shown in Figure 1.<sup>3</sup> The combination of programmable logic and processing system delivers superior parallel processing power, real-time performance, fast computational speeds, and connectivity versatility.

The processing system side of the Zynq SoC consists of a dual-core ARM® Cortex®-A9 processor combined with a NEON coprocessor and floating-point extensions to accelerate software execution. Embedded Linux or real-time operating systems can be deployed on the dual-core ARM processor to fully benefit from the system's capabilities. The processor is self-contained and can be used without the need to configure the programmable logic, which is a critical element for software developers who will want to start developing code in parallel to hardware developers who will design the FPGA fabric.

On the programmable logic side, the device has up to 444,000 logic cells and 2200 DSP slices that supply massive processing bandwidth, allowing the Zynq device to tackle a variety of

challenging signal processing applications. Five high throughput AMBA®-4 AXI high speed interconnects tightly couple the programmable logic to the processing system with the equivalent of more than 3000 pins of effective bandwidth.<sup>4</sup>

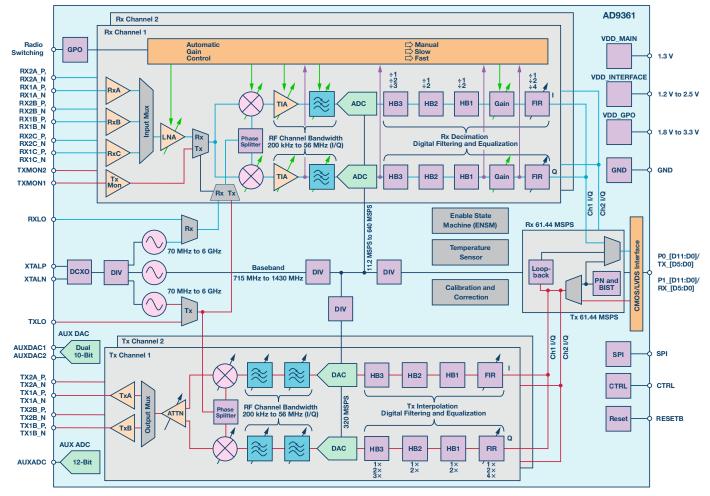

#### AD9361 Agile Wideband RF Transceiver IC for SDR

In recent years, Analog Devices has brought to market revolutionary SDR products to support increasingly evolving SDR requirements and system architectures. Some of the most important Analog Devices products in this field are the AD9361/AD9364 integrated RF agile transceivers. The AD9361  $(2 \times 2)^5$  and AD9364  $(1 \times 1)^6$  are high performance, highly integrated RF transceiver ICs intended for use in SDR architectures in applications such as wireless communications infrastructure, defense electronics systems, RF test equipment and instrumentation, and general software-defined radio platforms. The devices combine an RF front end with a flexible, mixed-signal baseband section and integrated frequency synthesizers, simplifying design-in by providing a configurable digital interface to a processor or FPGA. The chips operate in the 70 MHz to 6 GHz range, covering most licensed and unlicensed bands, and support channel bandwidths from less than 200 kHz to 56 MHz by changing the sample rate, digital filters, and decimation, all programmable within the AD9361 and AD9364 devices. Figure 2 shows the block diagram of a AD9361 device.

Figure 2. AD9361 block diagram.

In order to help customers shorten time to market and overall development effort, Analog Devices has gone a step further by providing SDR solutions within a complete ecosystem of seamless FPGA connectivity, enabling a rapid prototyping and development environment for complete radio system design. The AD-FMCOMMSx-EBZ rapid development and prototyping boards are a family of high speed analog FMC modules, incorporating AD9361 or AD9364 agile RF transceiver ICs or a discrete signal chain that seamlessly connects to the Xilinx FPGA development platform ecosystem. These boards are fully customizable by software without any hardware changes and come with downloadable Linux drivers and bare metal software drivers, schematics, board layout, and design aid reference materials, all contained on their respective Analog Devices wiki sites. Table 1 summarizes the features of the different FMCOMMSx platforms.

**Table 1. FMCOMMSx Platforms**

| Platform        | Features                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD-FMCOMMS5-EBZ | Integrating two AD9361 2 × 2 agile transceiver ICs, this SDR rapid prototyping board provides full synchronization capability for four receiver channels and four transmitter channels, enabling any subset of a 4 × 4 MIMO system to be created. Wideband 70 MHz to 6 GHz and 2.4 GHz tuned ports are accommodated. AD-FMCOM-MS5-EBZ resource wiki page: http://wiki.analog.com/resources/eval/user-guides/ad-fmcomms5-ebz                    |

| AD-FMCOMMS4-EBZ | Integrating the AD9364 agile RF transceiver IC, this 1 × 1 SDR rapid prototyping board can be software configured for highest RF performance in the 2400 MHz to 2500 MHz region, or can be software configured to operate over the AD9364's complete RF tuning range of 70 MHz to 6 GHz for system prototyping and development purposes. AD-FMCOMMS4-EBZ resource wiki page: http://wiki.analog.com/resources/eval/user-guides/ad-fmcomms4-ebz |

| AD-FMCOMMS3-EBZ | Integrating the AD9361 agile RF transceiver IC, this 2 × 2 version of SDR rapid prototyping board supports the AD9361's full RF tuning range of 70 MHz to 6 GHz. This kit is ideal for the wireless communications SDR system architect seeking a unified development platform with wide tuning capabilities. AD-FMCOMMS3-EBZ resource wiki page: http://wiki.analog.com/resources/eval/user-guides/ad-fmcomms3-ebz                            |

| AD-FMCOMMS2-EBZ | Integrating the AD9361 agile RF transceiver IC, this 2 × 2 SDR rapid prototyping board is tuned for highest RF performance in the 2400 MHz to 2500 MHz region. This kit is ideal for the RF engineer seeking optimized system performance meeting AD9361 data sheet specifications within this defined range of RF spectrum. AD-FMCOM-MS2-EBZ resource wiki page: http://wiki.analog.com/resources/eval/user-guides/ad-fmcomms2-ebz            |

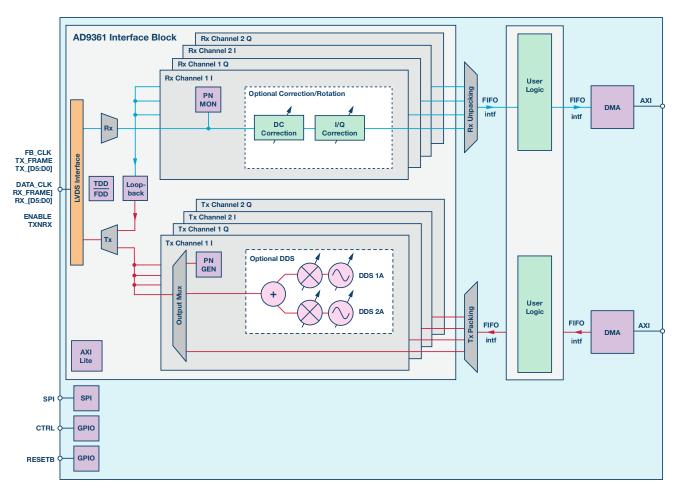

Figure 3. ADI HDL and software infrastructure.

#### Zynq SDR Rapid Prototyping Platform

#### Reference Design

Together with the FMCOMMSx platforms, Analog Devices provides a complete Vivado framework, with a Linux and bare metal software infrastructure that can be used both for prototyping purposes as well as a part of the final production system. Figure 3 shows the Analog Devices Zynq Infrastructure to support the FMCOMMSx boards.

This high level diagram shows how the ADI reference design is partitioned on a Xilinx Zynq SoC. An HDMI output is used to display the Linux interface on a monitor while a keyboard and mouse can be connected to the system on a USB 2.0 port. The ARM Cortex-A9 processing system runs Ubuntu Linux provided by Analog Devices. This includes the Linux IIO drivers needed to interface with the Analog Devices FMCOMMS hardware, the IIO Oscilloscope (Scope)<sup>8</sup> user space application for monitoring and control, a libiio server<sup>9</sup> that allows real-time data acquisition and system control over TCP together with clients running on a remote computer, and optional user applications that incorporate C code generated by the Embedded Coder for the controller's Simulink model.

#### Software Infrastructure

All ADI Linux drivers are based on the Linux Industrial I/O (IIO) subsystem, which is now included in all mainline Linux kernels. The IIO Scope is an open-source Linux application developed by Analog Devices that runs on the dual ARM Cortex-A° cores inside the Xilinx Zynq and has the ability to display real-time data acquired from any Analog Devices FMC card connected to the Xilinx Zynq platform. The data can be displayed either as a time domain, frequency domain,

or constellation plot. Different popular file formats like comma separated values or .mat MATLAB data files are supported to save the captured data for further analysis. The IIO Scope provides a graphical user interface for changing or reading back the configuration of the Analog Devices FMC cards. The libiio server allows real-time data acquisition and system control over transmission control protocol (TCP) together with clients running on a remote computer.<sup>10</sup> The server runs on an embedded target under Linux and manages real-time data exchange over TCP between the target and a remote client. This library abstracts the low level details of the hardware, and provides a simple yet complete programming interface that can be used for advanced projects. Its modular architecture, well designed API, and built-in network capabilities allow the users to create applications that will run on the system not only where the IIO devices are connected, but also remotely through the network. At first targeted at Linux, it can now be used under Windows as well by using the remote back end of the library. Written in C and licensed under the LGPL, it features bindings for C#, Python, and MATLAB. A MathWorks IIO client<sup>11</sup> is available as a system object to be integrated in native MATLAB and Simulink applications. It is designed to exchange data over Ethernet with an ADI hardware system connected to a FPGA/SoC platform running the ADI Linux distribution, which enables a MATLAB or Simulink model to perform the following functions:

- Stream data to and from a target

- · Control the settings of a target

- Monitor different target parameters

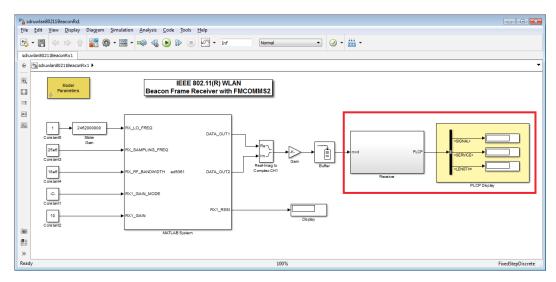

Figure 4. Screen capture of the beacon frame receiver example.

The IIO System Object™ is available in both MATLAB and Simulink, depending on whether the user calls it from a MATLAB script or incorporates it into a MATLAB System Block. The Linux software and HDL infrastructure provided by ADI for the FMCOMMS platforms is a great environment for prototyping SDR applications together with the tools provided by MathWorks and Xilinx, and it also contains production ready components that can be integrated into the SDR system—helping to reduce the time and cost needed to move from concept to production.

In order to help customers ramp up quickly and easily with the IIO System Object, we provide several MATLAB and Simulink examples based on this interface, such as a beacon frame receiver, <sup>12</sup> QPSK transmitter and receiver, <sup>13</sup> as well as a LTE transmitter and receiver. <sup>14</sup> In these examples, FMCOM-MSx platforms are configured by IIO System Object, and are used as RF front ends, which transmit or receive the analog signals over the air. These signals are streamed to or from the target via the IIO System Object. All the other signal processing happens in MATLAB or Simulink. Figure 4 is a screen capture of the beacon frame receiver example, which shows a typical connection between the IIO System Object and the other Simulink blocks.

#### MathWorks Support for Zynq

MathWorks support for Zynq-based SDR comes from the following four aspects:

#### 1. AD9361 Simulink Model

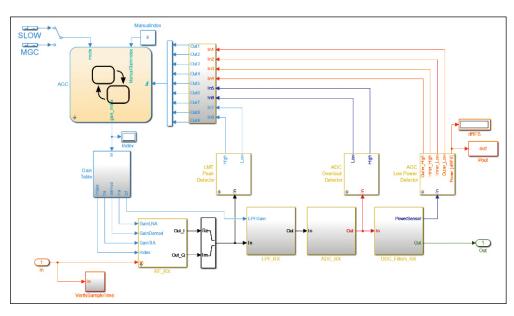

Since the AD9361 is an integrated RF transceiver chip, signal probing and internal operation monitoring is not really possible. For this reason, MathWorks and Analog Devices have codeveloped a SimRF™ model of the AD9361 that allows a simulation of the chip's operation so that customers can see exactly what's going on under the hood and how the chip performs under different test conditions that are hard to replicate in real life. SimRF provides a component library and simulation engine for designing RF systems using equivalent baseband or circuit envelope blocks, such as amplifiers, mixers, and S-parameter blocks. It is a useful and appropriate tool to model the AD9361 RF transceiver. The system-level AD9361 Agile RF Transceiver model, shown in Figure 5, replicates exactly the functionality of the AD9361 and is available to the users as a MathWorks hardware support package.¹5

Figure 5. MathWorks SimRF model of AD9361 Agile RF receiver.

The SimRF models have been validated in a lab with power spectral measurements. The characterization of the transceiver's noise and nonlinearity at different frequencies and power levels are identified. The models are then designed to generate the same characterizations, which validates them across the range of design.

With the AD9361 transceiver SimRF models, the users can do the following:

- Predict the impact of the RF imperfections on the test signals

- Use reference tones and LTE signals

- Generate or import test vectors and evaluate the effects of nonlinearity, noise, gain, and phase imbalance, spectral leakage, and other imperfections introduced by the RF transmitter and receiver

- Add interfering signals and evaluate the results in the time or frequency domains

#### 2. Communications and DSP System Toolbox Functions

MathWorks products such as the *Communications System Toolbox*,<sup>™16</sup> Signal Processing Toolbox,<sup>™17</sup> DSP System Toolbox,<sup>™18</sup> and SimRF<sup>19</sup> provide industry-standard algorithms and apps for systematically analyzing, designing, and tuning SDR systems. All of these tools provide the means to create high fidelity SDR models that can be used to verify the behavior and performance of the *communications* system before moving to the actual physical implementation.

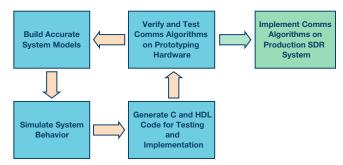

#### 3. Simulink Workflow for Zyng

MATLAB and Simulink from MathWorks are environments for multidomain simulation and model-based design that are well suited to simulating SDR systems with communication algorithms. Communication algorithms adjust gain, frequency offset, timing offset, and other performance variables, often for better synchronization between transmitter and receiver systems. Evaluating communication algorithms using simulation is an effective way to determine the suitability of SDR designs and reduce the time and cost of algorithm development before committing to expensive hardware testing. Figure 6 depicts an efficient workflow for designing a communication algorithm by following these steps:

- Build accurate SDR models using the libraries provided by the model-based design environment.

- Simulate system behavior to verify that the system is performing as expected.

- Generate C code and HDL for real-time testing and implementation.

- Test communication algorithms using prototyping hardware.

Once the performance of the SDR system is proven to be satisfactory through simulation and testing on the prototyping hardware, it is safe to take the system implementation and deploy it onto the final production system.

Figure 6. Workflow for communication algorithm design.

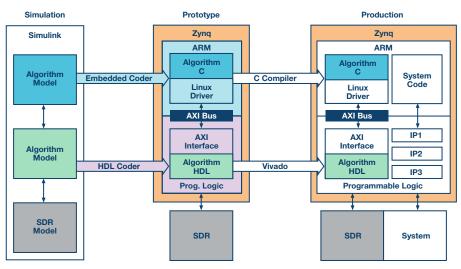

#### 4. Simulink Platform Integration to Zynq SDR Kit

Once the SDR system is fully verified in the simulation environment using tools like the Embedded Coder®20 and the HDL Coder™21 from MathWorks, the user can generate C code with Embedded Coder and VHDL or Verilog using HDL Coder, and then deploy the code to prototyping hardware for testing, and afterward, onto the final production system. At this point, software and hardware implementation requirements are specified, such as fixed-point and timing behavior. Automatic code generation helps to reduce the time needed to move from concept to actual system implementation and avoids the introduction of manual coding errors, ensuring that the actual SDR implementation matches the model. Figure 7 depicts a real-life process of the steps needed to model a SDR system in Simulink and transfer it onto the final production system based on a Xilinx Zynq SoC.

The first step is to model and simulate the SDR system in Simulink. At this stage, the communication algorithm is partitioned into blocks that will be implemented in software and blocks that will be implemented into the programmable logic. Once the partitioning and the simulation are complete the SDR model is converted into C code and HDL using Embedded Coder and HDL Coder. A Zynq-based prototyping system is used to verify the performance of the communication

Figure 7. Path from simulation to production.

algorithm and to help further tune the SDR model before moving to the actual production stage. In the production stage, the automatically generated C code and HDL are integrated into the complex production system framework. This workflow ensures that once the communication algorithm reaches the production stage it is fully verified and tested and provides a lot of confidence in the system's robustness. Zynq Hardware Support Packages for Embedded Coder and HDL Coder make it easier to program the Zynq platform by providing a framework for integrated hardware/software design, simulation, and verification that integrate model-based design into the workflow, enabling rapid design iteration cycles and helping to detect and correct design and specification errors early.22

#### **Conclusions**

This article illustrated the requirements and trends of modern SDR systems and the tools and systems that MathWorks, Xilinx, and Analog Devices bring to the market in order to meet these requirements and help drive toward more performant SDR solutions. By combining the model-based design and automatic code generation tools from MathWorks with the powerful Xilinx Zynq SoCs and Analog Devices integrated RF transceivers, SDR systems design, verification, testing, and implementation can be more effective than ever, leading to higher performance radio systems and reducing the time to market. Analog Devices FMCOMMS platforms paired with the Avnet Zynq-7000 AP SoC provide a great prototyping environment for the SDR algorithms designed using MATLAB and Simulink from MathWorks. The FMCOMMS platforms are accompanied by a set of open source reference designs intended to give a starting point for anyone who wants to evaluate the system and help kick-start any new SDR project.

In the next article in this series, we will advance down the SDR design process as we review the characteristics of automatic dependent surveillance broadcast signals and explain how to decode their information in MATLAB/Simulink in simulation.

For more information about the topics presented in this article, documentation, videos, and reference designs, check out the References section.

#### References

- <sup>1</sup> "What Is Software-Defined Radio?" Wireless Innovation Forum.

- <sup>2</sup> Model-Based Design. MathWorks.

- <sup>3</sup> Zynq-7000 All Programmable SoC. Xilinx.

- <sup>4</sup> Hill, Tom. "Motor Drives Migrate to Zyng SoC with Help from MATLAB." Xcell Journal, Issue 87, Second Quarter, 2014.

- <sup>5</sup> AD9361.

- <sup>6</sup> AD9364.

- 7 "Software-Defined Radio Solutions from Analog Devices." Analog Devices.

- <sup>8</sup> IIO Oscilloscope. Analog Devices Wiki.

- <sup>9</sup> Simulink Libiio. Analog Devices Wiki.

- <sup>10</sup> What Is Libiio? Analog Devices Wiki.

- <sup>11</sup> IIO System Object. Analog Devices Wiki.

- <sup>12</sup> Beacon Frame Receiver Example. Analog Devices Wiki.

- <sup>13</sup> QPSK Transmitter and Receiver Example. Analog Devices Wiki.

- <sup>14</sup> LTE Transmitter and Receiver Example. Analog Devices.

- 15 AD9361.

- <sup>16</sup> "Communications System Toolbox." MathWorks.

- 17 "Signal Processing Toolbox." MathWorks.

- 18 "DSP System Toolbox." MathWorks.

- 19 "SimRF." MathWorks.

- <sup>20</sup> "HDL Coder." MathWorks.

- <sup>21</sup> "Embedded Coder." MathWorks.

- <sup>22</sup> "Xilinx Zynq Support from Simulink." MathWorks.

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

Di Pu [di.pu@analog.com] is a system modeling applications engineer for ADI, supporting the design and development of software-defined radio platforms and systems. She has been working closely with MathWorks to solve mutual end customer challenges. Prior to joining ADI, she received her B.S. degree from Najing University of Science and Technology (NJUST), Nanjing, China, in 2007 and her M.S. and Ph.D. degrees from Worcester Polytechnic Institute (WPI), Worcester, MA, U.S.A., in 2009 and 2013—all in electrical engineering. She is a winner of the 2013 Sigma Xi Research Award for Doctoral Dissertation at WPI.

Di Pu

Andrei Cozma [andrei.cozma@analog.com] is an engineering manager for ADI, supporting the design and development of system level reference designs. He holds a B.S. degree in industrial automation and informatics and a Ph.D. in electronics and telecommunications. He has been involved in the design and development of projects from different industry fields such as motor control, industrial automation, software-defined radio, and telecommunications.

Andrei Cozma

Also by this Author:

FPGA-Based Systems Increase Motor-Control Performance Volume 49, Number 1

Tom Hill

Tom Hill [tom.hill@xilinx.com], system generator product manager, Xilinx, Inc. Tom Hill has over 18 years experience in the EDA industry. Hill oversees all products, strategic, and corporate marketing activities related to Xilinx's Target Design Platforms for DSP. Hill was most recently at AccelChip, Inc., where he was technical marketing manager responsible for product direction and application of high level design methodologies and tools to DSP applications. Prior to AccelChip, Hill held positions as product manager, technical marketing manager, technical marketing engineer, and field applications engineer for various FPGA and ASIC synthesis tools. Hill began his career as a hardware and ASIC design engineer at Allen-Bradley and Lockheed. Hill holds a B.S. in electrical engineering from Cleveland State University.

# New Advances in Energy Harvesting Power Conversion

By Frederik Dostal

Energy harvesting has been around for a very long time. I still remember my 1980s pocket calculator with a solar cell powering the computing unit as well as the LCD display. But even much before that, usable energy was harvested in the early days of the electrical revolution by putting generators on river mills that were powered by running water to generate electricity. Today, when we talk about energy harvesting, we usually use the term for a power source to replace battery cells in electric equipment. So the example of the pocket calculator from the 1980s fits quite well into what we try to achieve today with "energy harvesting."

#### Setup of an Energy Harvesting System

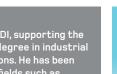

The most important item in energy harvesting systems is obviously a harvester, and the most common one is a solar cell. The electricity generated by the harvester needs to be converted into a useful voltage or current to power the system or charge intermediate energy storage devices such as super capacitors and batteries. When the system is powered, the correct voltage for the electronics needs to be generated. Figure 1 shows the power management unit fulfilling many different tasks. Matching the input impedance to allow for maximum harvested energy, charging an intermediate energy storage, routing power from a conventional primary cell battery, generating the correct output voltage for the system, and monitoring current flows and voltages to generate a reliable system. All these tasks need to be fulfilled at extremely little supply power so that the system can work with a small harvester or sensor. High integration of these functions in the dc-to-dc converter can help to reduce the power needed for such tasks.

The system in Figure 1 shows a typical energy harvesting system for a wireless environmental sensor. These sensors are typically used to sense temperature, humidity, or different gases such as  $\rm CO_2$ . There are many other applications for energy harvesting. Industrial applications can be found in security and surveillance in wireless occupancy sensors or in industrial monitoring such as asset tracking and machine monitoring.

Energy harvesting is also used in consumer electronics such as in portable and in wearable devices. In home healthcare applications, wireless patient monitoring has a need to run without, or extend, battery life.

Today energy harvesting is a very popular topic. Many engineers must evaluate whether or not an energy harvesting solution can replace or complement an existing power solution. The reason why such systems are so popular today is that we are finally reaching a point of equilibrium, where power being harvested from relatively low cost and small size harvesters is enough to power very low energy consumption microcontrollers and RF circuitry. Advances have been made with both electricity generation and in energy consumption in the last few years, so that today many applications that were unrealistic five to 10 years ago are now possible and economically feasible.

Figure 1. Energy harvesting system setup.

#### Different Sources of Energy

There are different sources of energy and the most common ones are photovoltaic (PV), thermoelectric (TEG), electromagnetic, piezoelectric, and RF. Photovoltaic and thermoelectric harvesters generate dc voltages, while electromagnetic, piezoelectric, and RF harvesters generate changing or ac voltages. This makes the requirement for a power conversion technology slightly different.

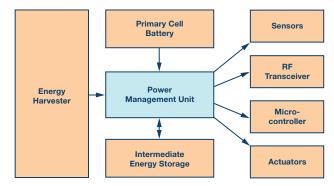

Figure 2 shows different harvesting types and the amount of energy that can roughly be generated with a harvester size of 10 square centimeters. It shows energy generation on the left side and energy consumption for different tasks on the right side. Notice that the power scale in the center is logarithmic. This graph is very important to get a realistic idea of the feasibility of an idea. Often times, designers put work and effort into evaluating an energy harvesting solution only to find out that the harvested energy is not enough to power a given system.

Figure 2. Different sources of energy and the required energy requirements of different applications.

#### The Importance of the DC-to-DC Converter Unit

Power conversion and management is generally the core of modern energy harvesting systems. While some applications do not use sophisticated power devices, many do. Examples of systems without intelligent power management are a stack of daisy-chained solar cells generating a relatively high dc voltage to either directly power a system or with a simple linear regulator in between. Such systems usually do not have the optimum energy efficiency or do not have a supply voltage that is well regulated. While some loads might work with a widely varying supply voltage, others will not. Future, more advanced systems are more likely to require some form of voltage converter and management block.

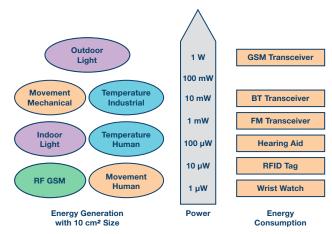

Figure 3. Block diagram of a power management device for energy harvesting applications.

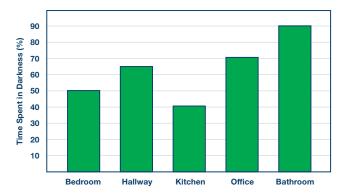

Figure 3 shows the block diagram of a modern power management device for energy harvesting applications. It contains start-up circuitry with a charge pump to allow a start-up voltage of 380 mV on the input. Once the system is running, the internal circuitry of the ADP5090 is powered from the output voltage of the ADP5090. This is the node that powers the load of the energy harvesting system. Once this node is above 1.9 V, the input voltage may go down as low as 80 mV while still being able to harvest energy. This is very helpful in systems that spend a lot of time in suboptimal situations. For example, a solar cell powered indoor sensor. In the morning hours and evening hours, there might be very little light on the solar cell, which generates very little electrical power. Using this time to harvest some energy can help the total power budget in a given time period. One other aspect that helps in such situations is the low quiescent current of the ADP5090. While alert, the current consumption is only 260 nA. Figure 4 shows a typical real-world application. This plot shows different places in a residential building and the typical times a sensor with a solar cell spends in darkness. Certainly this is just a typical case. The amount of light a sensor will see depends on the architecture of the house, including the amount of windows, the amount of electric light that is being used, and the exact location of the sensors. Also the time of year and the location of the house will influence such a chart. The point is, in such varying light conditions, the low power consumption of the ADP5090 helps the total power budget immensely, especially in places that spend most of their time in darkness.

Figure 4. Typical time a sensor spends in darkness in different residential building locations.

The dc-to-dc converter stage in the ADP5090 is quite interesting. It has a regulation loop just like most dc-to-dc converters. However, it does not regulate the output voltage, nor the output current. The regulation loop is primarily set up in a way to regulate the input impedance.

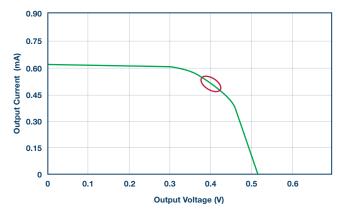

Solar cells have a current and voltage behavior as shown in Figure 5. In an open-loop condition, with no current flow, the provided voltage is at its maximum. Then as current starts to flow, the voltage goes down. At very high currents, the voltage collapses sharply. In the middle of the curve, there is a knee that is the point of peak power. This is the point where the voltage is still relatively high but also where quite a lot of current is drawn. To operate close to the maximum peak power point, we need to track this point. Just setting a fixed current value we draw will not work because the curve of a given solar cell in Figure 5 will shift depending on different light conditions. To track the MPP (maximum peak power point), the ADP5090 stops conducting current on the input, checks the solar cell voltage without it being loaded, and then sets the MPP for the next 16 seconds. After this time period, an open-loop check is performed again. Sixteen seconds turns out to be a good compromise between drifting away from the MPP and interrupting the harvesting action too often.

Figure 5. Voltage and current plot of a typical photovoltaic cell.

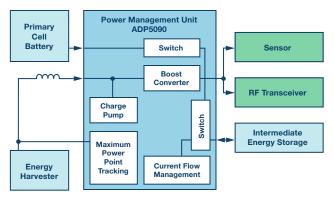

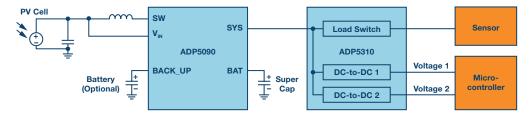

Figure 6. Example of a power management stage for energy harvesting applications.

MPP tracking ensures that the most energy is harvested from a power source, such as a photovoltaic cell or a thermoelectric generator. Still the power management unit has additional tasks. For instance, it needs to control the output voltage in a certain voltage window. The ADP5090 acts like a current source to charge a super cap or a battery. This element is important to decouple energy harvesting with energy consumption. This enables many systems that do not have a constant source of available energy to harvest and perform certain system tasks in set intervals. For example, a sensor in a wireless sensor network that needs to send temperature values every five minutes. If the sensor is powered by a solar cell, it can still operate during dark times due to the intermediate energy storage.

A quite popular architecture today involves attaching energy harvesting to systems that are powered by a primary cell battery. Successful products using a nonrechargeable battery could extend the lifetime of the system by having energy harvesting added. This brings extended operating time without compromising system reliability. For such hybrid systems, the ADP5090 offers the capability to control a primary cell battery. Once there is not enough harvested energy available, the power path from the primary cell battery is routed to power the load directly.

Figure 6 shows a complete energy harvesting power stage with not only the main ADP5090 MPPT energy harvesting IC, but also one second IC, the ADP5310. It is a dc-to-dc converter very efficiently generating two output voltages. The efficiency is close to 90% at 100  $\mu A$  output current. Additionally, the ADP5310 also has one load switch integrated. This load switch can be used to turn off loads that otherwise would constantly consume power, even when they are not in use.

The ADP5310 step-down converter can accept input voltages all the way up to 15 V. This enables the device to be used directly in ac voltage generators, such as piezoelectric or electromagnetic types. All that is needed is a bridge rectifier and the output voltage can be fed directly into the ADP5310.

Today many power management integrated circuits are available that were specifically designed for use in energy harvesting applications. They enable systems to run with smaller harvesters or make energy harvesting solutions possible that could not have been designed a few years ago. System designers have great ideas that are being implemented right now and which we will be able to see and marvel at in the very near future.

Frederik Dostal [frederik.dostal@analog.com] studied microelectronics at the University of Erlangen-Nuremberg, Germany. Starting work in the power management business in 2001, he has been active in various applications positions including four years in Phoenix, Arizona, working on switch mode power supplies. He joined Analog Devices in 2009 and works as a power management technical expert for Europe.

Frederik Dostal

# A Low Power Data Acquisition Solution for High Temperature Electronics Applications

By Jeff Watson and Maithil Pachchigar

#### Introduction

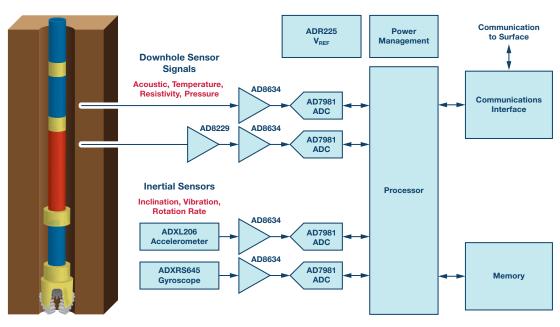

A growing number of applications require data acquisition systems that must operate reliably at very high ambient environments, such as downhole oil and gas drilling, avionics, and automotive. While the end uses in these industries are quite different, there are several common signal conditioning needs. The majority of these systems require precision data acquisition from multiple sensors or require a high sample rate. Furthermore, many of these applications have stringent power budgets because they are running from batteries or cannot tolerate additional temperature rise from self-heating of the electronics. Therefore, a low power analog-to-digital converter (ADC) signal chain that maintains high precision over temperature and can be easily used in a wide variety of scenarios is required. Such a signal chain is shown in Figure 1, which depicts a downhole drilling instrument.

While the number of commercially available ICs rated for 175°C is still small, they are increasing in number in recent years, especially for core functions such as signal conditioning and data conversion. This has enabled electronics engineers to rapidly and reliably design for high temperature applications and achieve performance that was not possible in the past. While many of these ICs are well characterized over temperature, this tends to be limited to the function of that device only. There is clearly a lack of circuit level information for these

components that demonstrates best practices to achieve high performance in real-world systems.

In this article, we present a new reference design for high temperature data acquisition, characterized from room temperature to 175°C. This circuit is intended to be a complete data acquisition circuit building block that will take an analog sensor input, condition it, and digitize it to an SPI serial data stream. It is versatile enough to be used as a single channel, or it can be scaled for multiple channel simultaneous sampling applications. Recognizing the importance of low power consumption, the power consumption of the ADC scales linearly with the sample rate. The ADC can also be directly powered from the voltage reference, eliminating the need for an additional power rail and the associated power conversion inefficiencies. This reference design is available off the shelf to facilitate testing by designers and includes all schematics, bill of material, PCB artwork, and test software.

#### Circuit Overview

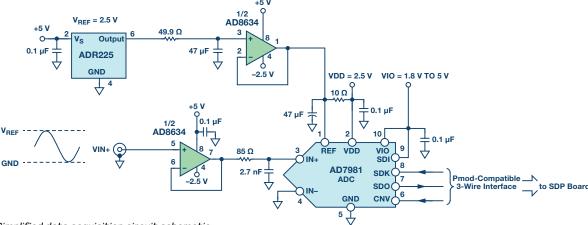

The circuit shown in Figure 1 is a 16-bit, 600 kSPS successive approximation analog-to-digital converter system using devices rated, characterized, and guaranteed at 175°C. Because many harsh environment applications are battery-powered, the signal chain has been designed for low power consumption while still maintaining high performance.

Figure 1. Downhole instrument data acquisition signal chain.

Figure 2. Simplified data acquisition circuit schematic.

This circuit uses the AD7981, a low power (4.65 mW @ 600 kSPS), high temperature, PulSAR® ADC, driven directly from the AD8634 high temperature, low power op amp. The AD7981 ADC requires an external voltage reference between 2.4 V and 5.1 V, and in this application, the voltage reference chosen is the micropower ADR225 precision 2.5 V reference, which is also qualified for high temperature operation and has a very low quiescent current of 60  $\mu A$  maximum at 210°C. All of the ICs in this design have packaging specially designed for high temperature environments, including monometallic wire bonds.

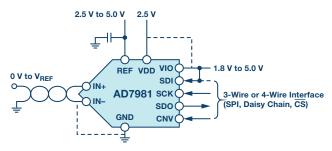

#### Analog-to-Digital Converter

The heart of this circuit is the AD7981, a 16-bit, low power, single-supply ADC that uses a successive approximation architecture (SAR), capable of sampling up to 600 kSPS. As shown in the diagram in Figure 1, the AD7981 uses two power supply pins: a core supply, VDD, and a digital input/output interface supply, VIO. The VIO pin allows a direct interface with any logic between 1.8 V and 5.0 V. The VDD and VIO pins can also be tied together to save on the number of supplies needed in the system, and they are independent of power supply sequencing. A simplified connection diagram is shown in Figure 3.

The AD7981 typically consumes only 4.65 mW at 600 kSPS and powers down automatically between conversions in order to save power. Therefore, the power consumption scales linearly with the sampling rate, making the ADC well suited for both high and low sampling rates—even as low as a few Hz—and enables very low power consumption for battery-powered systems. Additionally, oversampling techniques can be used to increase the effective resolution for low speed signals.

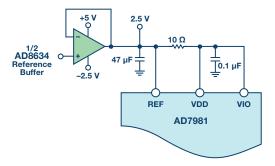

Figure 3. AD7981 application diagram.

The AD7981 has a pseudo differential analog input structure that samples the true differential signal between the IN+ and IN– inputs and rejects the signals common to both inputs. The IN+ input can accept the unipolar, single-ended input signal from 0 V to  $V_{\text{\tiny REF}}$  and the IN– input has a restricted range of GND to 100 mV. The pseudo differential input of AD7981 simplifies the ADC driver requirement and lowers power

dissipation. The AD7981 is available in a 10-lead MSOP rated for 175°C.

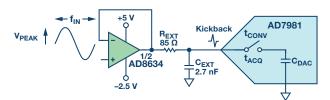

#### **ADC Driver**

The input of AD7981 can be driven directly from low impedance sources, but high source impedances significantly degrade the ac performance, especially total harmonic distortion (THD). Therefore it is recommended to use an ADC driver or op amp, such as AD8634, to drive the input of the AD7981 as shown in Figure 4. At the start of the acquisition time the switch closes, and the capacitive DAC injects a voltage glitch (kickback) on the ADC input. The ADC driver helps to settle this kickback as well as isolate it from the signal source.

The low power (1 mA/amplifier) AD8634 dual precision op amp is suited for this task because its excellent dc and ac specifications are a good fit for sensor signal conditioning and elsewhere in the signal chain. While the AD8634 has rail-to-rail outputs, the input requires 300 mV headroom from the positive and negative rails. This necessitates the negative supply, which was chosen to be -2.5 V. The AD8634 is available in an 8-lead SOIC rated for 175°C and an 8-lead flatpack rated for 210°C.

Figure 4. ADC front-end amplifier circuit.

The RC filter between the ADC driver and AD7981 is used to attenuate the kickback injected at the input of the AD7981 and band limits the noise coming to its input. However, too much band limiting can increase settling time and distortion. Therefore, it is very important to find the optimal RC values for this filter. The calculation is primarily based on the input frequency and throughput rate.

From the AD7981 data sheet, internal sampling cap  $C_{\rm IN}$  = 30 pF and  $t_{\rm CONV}$  = 900 ns, so as described, for a 10 kHz input signal, assuming the ADC is running at 600 kSPS and  $C_{\rm EXT}$  = 2.7 nF, the voltage step for a 2.5 V reference would be:

$$V_{STEP} = \frac{2\pi f_{IN} V_{PEAK} t_{CONV} C_{IN}}{C_{EXT} + C_{IN}}$$

$$V_{STEP} = 7.768e - 4 \text{ V}$$

Therefore, the number of time constants required to settle to  $\frac{1}{2}$  LSB at 16 bits is:

$$N_{TC} = ln\left(\frac{V_{STEP}}{\frac{V_{REF}}{2^{N+1}}}\right) = ln\left(\frac{7.768e - 4}{\frac{2.5 \text{ V}}{2^{16+1}}}\right) = 3.707$$

The acquisition time of AD7981 is

$$t_{ACQ} = \left(\frac{1}{f_S}\right) - t_{CONV} = \left(\frac{1}{600 \text{ kSPS}}\right) - 900 \text{ ns} = 7.67e - 7$$

We can then calculate the bandwidth of the RC filter using the following equation:

$$\tau = \left(\frac{t_{ACQ}}{N_{TC}}\right) = \left(\frac{7.67e - 7}{3.707}\right) = 2.068e - 7$$

$$f_{-3dB} = \left(\frac{1}{2\pi\tau}\right) = 769.5 \text{ kHz} \rightarrow R_{EXT} = 76.6 \Omega$$

This is a theoretical value with first-order approximation that should be verified in the lab. We determined through testing that the optimum values were  $R_{\text{EXT}}$  = 85  $\Omega$  and  $C_{\text{EXT}}$  = 2.7 nF (f<sub>-3dB</sub> = 693.48 kHz), which gave excellent performance over the extended temperature range to 175°C.

In the reference design, the ADC driver is in unity-gain buffer configuration. Adding gain to the ADC driver will reduce the bandwidth of the driver and lengthen the settling time. In this case, the throughput of the ADC may need to be reduced or an additional buffer as a driver should be used after the gain stage.

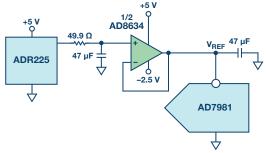

#### Voltage Reference

The ADR225 2.5 V voltage reference uses only 60  $\mu$ A maximum of quiescent current at 210°C and has a very low drift of 40 ppm/°C typical, making it an ideal part for this low power data acquisition circuit. It has an initial accuracy of  $\pm 0.4\%$  and can operate over a wide supply range of 3.3 V to 16 V.

The voltage reference input of the AD7981, like other SAR ADCs, has a dynamic input impedance and should therefore be driven by a low impedance source with efficient decoupling between the REF pin and GND as shown in Figure 5. The AD8634 is well suited as a reference buffer in addition to its ADC driver application.

Another advantage to using a reference buffer is that the noise on the voltage reference output can be further reduced by adding a low-pass RC filter, as shown in Figure 5. In this circuit, a 49.9  $\Omega$  resistor and 47  $\mu$ F capacitor gives a cutoff frequency of approximately 67 Hz.

Figure 5. SAR ADC reference buffer and RC filter.

During conversions, current spikes as high as 2.5 mA can occur on the AD7981 reference input. A high value reservoir capacitor is placed as close as possible to the reference input to supply that current and keep the reference input noise

low. Typically, a low ESR— $10~\mu F$  or more—ceramic capacitor is used, but for high temperature applications this is problematic due to the lack of availability of high value, high temperature ceramic capacitors. For this reason, a low ESR 47  $\mu F$  tantalum capacitor was chosen that has minimal impact to the performance of the circuit.

#### Digital Interface

The AD7981 offers a flexible serial digital interface compatible with SPI, QSPI, and other digital hosts. The interface can be configured for a simple 3-wire mode for the lowest I/O count, or 4-wire mode that allows options for the daisy-chained readback and busy indication. The 4-wire mode also allows independent readback timing from the CNV (convert input), which enables simultaneous sampling with multiple converters.

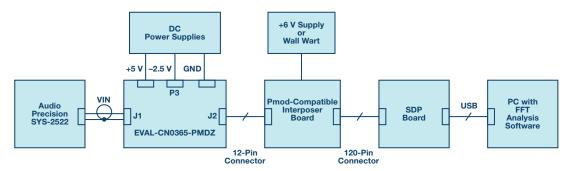

The Pmod-compatible interface utilized on this reference design implements the simple 3-wire mode with SDI tied high to VIO. The VIO voltage is supplied externally from the SDP-PMOD interposer board. The interposer board connects the reference design board to the Analog Devices System Development Platform (SDP) board and allows connection to a PC through USB in order to run software to evaluate performance.

#### **Power Supplies**

This reference design requires external low noise power supplies for the +5 V and -2.5 V rails. Because the AD7981 is low power, it can be supplied directly from the reference buffer. This eliminates the need for an additional power supply rail—saving power and board space. The proper configuration to power the ADC from the reference buffer is shown in Figure 6. VIO can also be supplied if logic levels are compatible. For the reference design board VIO is supplied externally through the Pmod-compatible interface for maximum flexibility.

Figure 6. Supplying ADC from reference buffer.

The typical total power consumption for an entire data acquisition solution at 175°C can be calculated as follows:

ADR225:  $30 \mu A \times 5 V = 0.15 \text{ mW}$

AD8634:  $(1 \text{ mA} \times 2 \text{ amplifiers}) \times 7.5 \text{ V} = 15 \text{ mW}$

AD7981: 4.65 mW @ 600 kSPS

Total power consumption = 19.8 mW

#### IC Packaging and Reliability

Devices in the Analog Devices high temperature portfolio go through a special process flow that includes design, characterization, reliability qualification, and a production test. Part of this process includes special packaging designed specifically for extreme temperatures. A special material set is used for the 175°C plastic packages in this circuit.

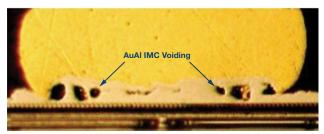

One of the major failure mechanisms in high temperature packaging is the bond wire-to-bond pad interface, particularly when gold (Au) and aluminum (Al) metals are mixed, as is typical in plastic packages. Elevated temperature accelerates the growth of AuAl intermetallic compounds. It is these intermetallics that are associated with bond failures, such as brittle bonds and voiding, which can occur in a few hundred hours as shown in Figure 7.

Figure 7. Au ball bond on Al pad, post 500 hours at 195°C.

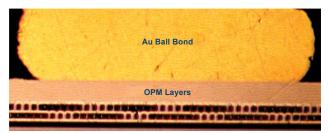

In order to avoid these failures, Analog Devices uses an over pad metallization (OPM) process to create a gold bond pad surface for the gold bond wire to attach. This monometallic system will not form intermetallics and has been proven reliable in qualification testing with over 6000 hours soak at 195°C, as shown in Figure 8.

Figure 8. Au ball bond on OPM pad, post 6000 hours at 195°C.

Although Analog Devices has shown reliable bonding at 195°C, the plastic package is rated for operation only to 175°C due to the glass transition temperature of the molding compound. In addition to the 175°C rated products used on this circuit, 210°C rated models are also available in a ceramic flatpack package. Known good die (KGD) are also available for systems that require custom packaging.

Analog Devices has a comprehensive reliability qualification program for high temperature (HT) products that includes high temperature operating life (HTOL), with the parts biased at the maximum operating temperature. HT products are data sheet specified for a minimum of 1000 hours at the maximum rated temperature. Full production testing is the last step required to guarantee performance for each device that is manufactured. Each device in Analog Devices' high temperature portfolio is production tested at elevated temperature to ensure performance is met.

#### Passive Components

Passive components chosen should be rated for high temperatures. For this design, >175°C thin film, low TCR resistors were used. COG/NPO capacitors were used for low value filter and decoupling applications and have a very flat coefficient over temperature. High temperature rated tantalum capacitors are available in larger values than ceramic and are commonly used for power supply filtering. The SMA connector used on this board is rated for 165°C, so it should be removed for long duration testing at elevated temperatures. Similarly, the insulation material on the 0.1" header connectors (J2 and P3) is only rated for short durations at high temperature but should also be removed for prolonged high temperature testing. For

production assemblies, there are a number of options for HT rated connectors from multiple vendors, such as Micro-D style connectors.

#### **PCB Layout and Assembly**

The PCB for this circuit is designed so that the analog signals and digital interface are on separate sides of the ADC, with no switching signals running under the ADC IC or near analog signal paths. This design minimizes the amount of noise that is coupled into the ADC die and supporting analog signal chain. The pin out of the AD7981, with all its analog signals on the left side and all its digital signals on the right side, eases this task. The voltage reference input, REF, has a dynamic input impedance and should be decoupled with minimal parasitic inductances, which is achieved by placing the reference decoupling capacitor as close as possible to the REF and GND pin and making the connection to the pin with a wide, low impedance trace. The layout of this board was purposely designed with components only on the top side of the board in order to facilitate testing over temperature where heat would be applied from the bottom of the board. A photo of the complete assembly is shown in Figure 9. For further layout recommendations, see the AD7981 data sheet.

Figure 9. Reference design circuit assembly.

For high temperature circuits, special circuit materials and assembly techniques should be used to ensure reliability. FR4 is a common material used for PCB laminates, but commercial grade FR4 has a typical glass transition temperature around 140°C. Above 140°C, the PCB will begin to break down, delaminate, and cause stress on components. A widely used alternative for high temperature assemblies is polyimide, which typically has a glass transition temperature of greater than 240°C. A four layer polyimide PCB was used in this design.

The PCB surface is also a concern, especially when used with solders containing tin because of the tendency to form bronze intermetallics with copper traces. A nickel-gold surface finish is commonly used, where the nickel provides a barrier, and the gold provides a good surface for the solder joint bonding. High melting point solder should also be used with a good margin between the melting point and maximum operating temperature of the system. SAC305 lead free solder was chosen for this assembly. With a melting point of 217°C, there is a margin of 42°C from the highest operational temperature of 175°C.

#### Performance Expectations

The AD7981 is specified for typical SNR of 91 dB with a 1 kHz input tone and a 5 V reference. However, when using low reference voltages such as 2.5 V, as is common in low power/low voltage systems, some degradation in SNR is expected. We can calculate the theoretical SNR based on the specifications of the components used in the circuit. From the AD8634 amplifier data sheet, its input voltage noise density is 4.2 nV/ $\sqrt{\rm Hz}$  and current noise density is 0.6 pA/ $\sqrt{\rm Hz}$ . Since the noise gain of AD8634 in buffer configuration is 1, and assuming negligible series input resistance for the current noise calculation, the equivalent output noise contribution from the AD8634 would be:

$$\sqrt{(4.2e-9)^2 + 0 \times (0.6e-12)^2} = 4.2 \text{ nV}/\sqrt{\text{Hz}}$$

Figure 10. Characterization test setup.

The total integrated noise at the ADC input

(after RC filter

$$\left(\frac{1}{2\pi(85)(2.7e-9)}\right)$$

) would be:

$$4.2 \text{ nV/}\sqrt{\text{Hz}} \times \sqrt{(693.48e3 \times \frac{\pi}{2})} = 4.38 \text{ }\mu\text{V rms}$$

The rms noise of AD7981 can be calculated from its data sheet typical SNR of 86 dB for a 2.5 V reference.

$$e_{\text{AD7981}} = 10^{\left(-\frac{\text{SNR}}{20}\right)} \times V_{\text{signal-rms}} =$$

$$10^{\left(\!-\frac{86}{20}\!\right)}\!\times 0.884~V = 44.3~\mu V~rms$$

The total rms noise of the complete data acquisition system can be calculated by using root-sum-square (RSS) of AD8634 and AD7981 noise sources:

$$V_{\text{noise-rms}} = \sqrt{(4.38e - 6)^2 + (44.3e - 6)^2}$$

$$= 44.51 \text{ µV rms}$$

So, the theoretical SNR of the data acquisition system at room temp (25°C) can be estimated as shown below:

$$SNR = 20 \times \log \left( \frac{V_{signal - rms}}{V_{noise - rms}} \right)$$

$$= 20 \times \log \left( \frac{0.884 \text{ V}}{44.51 \text{ µV rms}} \right) = ~86 \text{ dB}$$

#### **Test Results**

The ac performance of the circuit was evaluated over temperature from 25°C to 185°C. It is critical to use a low distortion signal generator to characterize performance. For this test, the Audio Precision SYS-2522 was used. In order to facilitate testing in an oven, extension harnesses were assembled so that only the reference design circuit was exposed to an elevated temperature. The block diagram of the test setup is shown below in Figure 10.

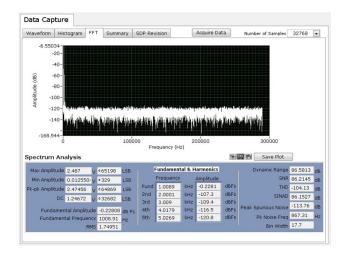

From our calculations in the previous setup, we expect to achieve approximately 86 dB SNR at room temperature. This compares well to our measured value of 86.2 dB SNR at room temperature as shown in the FFT summary in Figure 11.

Figure 11. AC performance with 1 kHz input tone, 580 kSPS, 25°C.

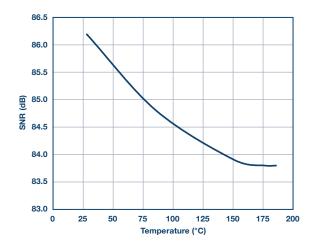

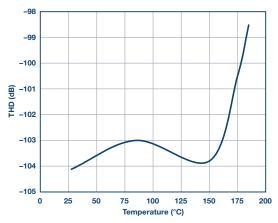

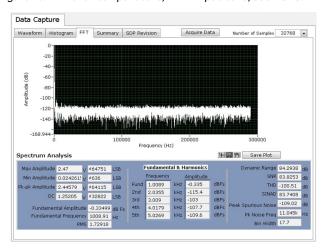

When this circuit is evaluated over temperature, SNR performance only degrades to approximately 84 dB at 175°C as shown in Figure 12. THD remains better than –100 dB, as shown in Figure 13. The FFT summary for the circuit at 175°C is shown in Figure 14.

Figure 12. SNR over temperature, 1 kHz input tone, 580 kSPS.

Figure 13. THD over temperature, 1 kHz input tone, 580 kSPS.

Figure 14. AC performance with 1 kHz input tone, 580 kSPS, 175°C.

#### Summary

In this article we presented a new reference design for high temperature data acquisition, characterized from room temperature to 175°C. This circuit is a complete low power (<20 mW) data acquisition circuit building block that will take an analog sensor input, condition it, and digitize it to an SPI serial data stream. This reference design is available off the shelf to facilitate testing by designers and includes all schematics, bill of materials, PCB artwork, test software, and documentation.

For more information on this reference design, please visit analog.com/CN0365. For more information on ADI's high temperature portfolio, please visit analog.com/hightemp.

#### References

Arkin, Michael, Jeff Watson, Michael Siu, and Michael Cusack. "Precision Analog Signal Conditioning Semicondcutors for Operation in Very High Temperature Environments." Proceeding from the High Temperature Electronics Network, 2013.

AD7981.

Digilent Pmod Interface Specification.

Harman, George. Wire Bonding in Microelectronics. McGraw Hill, Feb 2010.

Phillips, Reggie, et al. "High Temperature Ceramic Capacitors for Deep Well Applications." CARTS International 2013 Proceedings. March 2013.

Siewert, Thomas, Juan Carlos Madeni, and Stephen Liu. "Formation and Growth of Intermetallics at the Interface Between Lead-Free Solders and Copper Substrates." Proceedings of the APEX Conference on Electronics Manufacturing. Anaheim, California. April 2003.

Walsh, Alan. "Front-End Amplifier and RC Filter Design for a Precision SAR Analog-to-Digital Converter." *Analog Dialogue*, Volume 46, Number 4, 2012.

Walsh, Alan. "Voltage Reference Design for Precision Successive-Approximation ADCs." *Analog Dialogue*, Volume 47, Number 2, 2013.

Watson, Jeff and Gustavo Castro. "High Temperature Electronics Pose Design and Reliability Challenges." *Analog Dialogue*, Volume 46, Number 2, 2012.

Zedníček, Tomas, Zdeněk Sita, and Slavomir Pala. "Tantalum Capacitor Technology for Extended Operating Temperature Range."

Jeff Watson [jeffrey.watson@analog.com] is a systems applications engineer in the Instrumentation, Aerospace and Defense business unit at Analog Devices, focusing on high temperature applications. Prior to joining ADI, he was a design engineer in the downhole oil and gas instrumentation industry and off-highway automotive instrumentation/controls industry. Jeff received his bachelor's and master's degrees in electrical engineering from Penn State University.

Maithil Pachchigar [maithil.pachchigar@analog.com] is an applications engineer in in the Instrumentation, Aerospace and Defense business unit at Analog Devices in Wilmington, MA. He joined ADI in 2010 and focuses on the precision ADC product portfolio and customers in the instrumentation, industrial, healthcare, and energy segments. Having worked in the semiconductor industry since 2005, he has published numerous technical articles. He received an M.S.E.E. degree from San Jose State University in 2006 and an M.B.A. degree from Silicon Valley University in 2010.

#### **Jeff Watson**

Also by this Author:

High Temperature Electronics Pose Design and Reliability Challenges Volume 46, Number 2

#### Maithil Pachchigar

Also by this Author:

RF-to-Bits Solution Offers Precise Phase and Magnitude Data for Material Analysis Volume 48, Number 4

# Analyzing, Optimizing, and Eliminating Integer Boundary Spurs in Phase-Locked Loops with VCOs at up to 13.6 GHz

#### By Robert Brennan

A phase-locked loop (PLL) and voltage controlled oscillator (VCO) outputs an RF signal at a certain frequency, and ideally this signal would be the only signal present at the output. In reality, there are unwanted spurious signals and phase noise at the output. This article discusses the simulation and elimination of one of the more troublesome spurious signals—integer boundary spurs.

PLL and VCO combinations (PLL/VCOs) that are only capable of operating at integer multiples of the phase frequency detector reference frequency are known as integer-N PLLs. PLL/VCOs capable of much finer frequency steps are known as fractional-N PLLs. Fractional-N PLL/VCOs offer much more flexibility and are more widely used. Fractional-N PLLs achieve this feat by modulating the feedback path in the PLL at the reference rate. While capable of much finer frequency steps than the phase detector reference frequency, fractional-N PLL/VCOs have spurious outputs called integer boundary spurs (IBS). Integer boundary spurs occur at integer (1, 2, 3 ... 20, 21 ...) multiples of the PLL's phase frequency detector's reference (or comparison) frequency ( $f_{PFD}$ ). For example, if  $f_{PFD} = 100$  MHz, there will be integer boundary spurs at 100 MHz, 200 MHz, 300 MHz ... 2000 MHz, 2100 MHz. In a system where the desired VCO output signal is 2001 MHz, then there will be an IBS at 2000 MHz—this will appear at a 1 MHz offset from the desired signal. Due to effective sampling in the PLL system, this 1 MHz offset IBS is aliased to both sides of the desired signal. Therefore, when the desired output is 2001 MHz, spurious signals will be present at 2000 MHz and 2002 MHz.

Integer boundary spurs are undesirable for two main reasons:

- If they are at low frequency offsets from the carrier (the desired signal), then the IBS power contributes to integrated phase noise.

- If they are at large frequency offsets from the carrier, then

the IBS will modulate/demodulate adjacent channels to the

desired channel and result in distortion in system.

In some systems, high integer boundary spurs render some output channels unusable. If a system has 1000 channels in a certain spectrum bandwidth, and 10% of the channels have spurious signals above a certain power level, those 100 channels may be unusable. In protocols where spectrum bandwidth costs a lot of money, it is wasteful if 10% of the available channels cannot be used.

Integer boundary spurs are strongest when the integer boundary falls within the PLL bandwidth from the desired output frequency. That is, if the output frequency is 2000.01 MHz and the loop bandwidth is 50 kHz, the IBS will be strongest. As the output frequency moves away from the integer boundary, the power of the IBS reduces in a calculable and repeatable manner. Analog Devices' new, free simulator—ADIsimFrequencyPlanner™—uses this predictable behavior to accurately simulate integer boundary spur power (and much more).

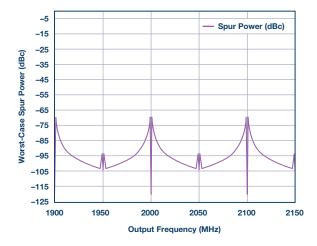

Figure 1 shows the worst-case integer boundary spur power at each output frequency from 1900 MHz to 2150 MHz (1 MHz steps). It can be seen that, at 2001 MHz, the worst-case IBS power is –70 dBc (70 dB below the carrier power). At 2000 MHz, there is no IBS because the output frequency falls on an integer boundary. The IBS power reduces as the carrier moves away from the integer boundary until the carrier starts getting close to the next integer boundary.

The spurious signals seen halfway between the integer boundaries (2049 MHz and 2051 MHz in Figure 1) are second-order integer boundary spurs. Second-order integer boundary spurs occur halfway between integer boundaries. Typically, second-order IBS are 10 dB to 20 dB lower than first-order IBS. ADIsimFrequencyPlanner simulates first-, second-, third-, fourth-, and fifth-order integer boundary spurs.

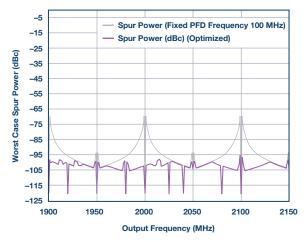

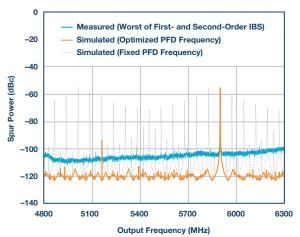

Figure 1. Worst-case integer boundary spur power at each output frequency from 1900 MHz to 2150 MHz (1 MHz steps; 100 kHz loop bandwidth; HMC830).

Suppose a certain modulation scheme states that channels with integer boundary spur power above -80 dBc are unusable; then about 10% of the channels in Figure 1 are no longer available. To overcome this problem, ADIsimFrequencyPlanner can optimize the PLL/VCO configuration to reduce and, in most cases, eliminate integer boundary spurs. Recall that the integer boundary spurs occur at integer multiples of the PFD frequency, and that they are strongest when near the carrier frequency. If the PFD frequency can be changed so that the integer multiple of the PFD frequency falls at a large enough offset from the carrier frequency, then the IBS power will be reduced to a nonproblematic level. This is what the algorithm in ADIsimFrequencyPlanner does—while taking into account the relative powers of the first-through fifth-order integer boundary spurs, ADIsimFrequencyPlanner finds the optimum solution that results in the lowest possible integer boundary spurs at the VCO output.

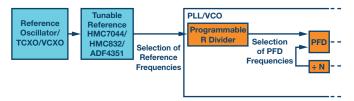

How can the PFD frequency be changed? Traditionally, in a PLL/VCO system, the PFD frequency is kept fixed. However,

by making the most of a programmable clock distribution source, the PLL reference input divider, and the PLL fractional-N modulator architecture, it is now easy to change the PFD frequency for each output channel.

In the recommended solution, the new HMC7044 clock generation and distribution chip is used. The HMC7044 has 14 ultralow noise outputs; each of the 14 outputs has a programmable divider. By connecting one of these outputs to the PLL reference input, and then programming the output divider as needed, an array of reference frequencies becomes available to the PLL.

The HMC7044 is a clock distribution system applicable to applications that use numerous synchronized clocks for ADCs, DACs, and other system components. Simpler applications that don't require as many outputs can use a simpler alternative, such as the HMC832 or ADF4351—both are integrated PLL and VCO chips.

Then, at the PLL reference input, the reference input divider (R divider) can be programmed as needed to divide the array of available reference frequencies to a larger array of PFD frequencies (the PFD frequency is the frequency at the output of the R divider). Thanks to the high order fractional-N modulator in the PLL, a change to the PFD frequency does not cause a problem in achieving the desired output frequency. Also, the programmable charge pump current of the PLL can be used to compensate for any change in the PFD frequency and therefore maintain a constant-loop bandwidth.

Figure 2. Block diagram showing a selection of PFD frequencies.

#### Example:

| f <sub>PFD</sub> (MHz) | N     | I <sub>CP</sub> | $f_{PFD} \times N = RF_{OUT} (MHz)$ | Comments          |

|------------------------|-------|-----------------|-------------------------------------|-------------------|

| 100                    | 20.01 | 2.08            | 2001                                | IBS at<br>±1 MHz  |

| 75                     | 26.68 | 1.88            | 2001                                | IBS at<br>±24 MHz |

#### where:

$I_{CP}$  = programmable charge pump current

$f_{PFD}$  = PLL PFD frequency;

N = PLL fractional-N value;

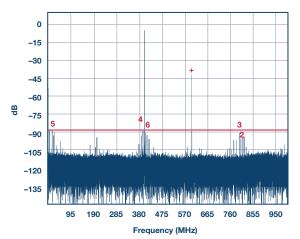

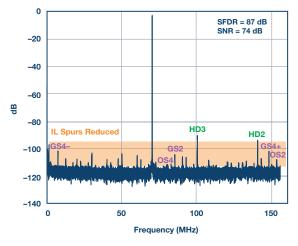

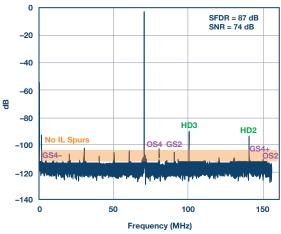

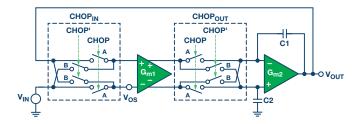

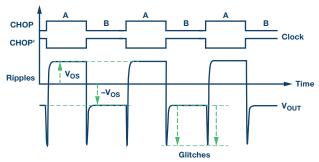

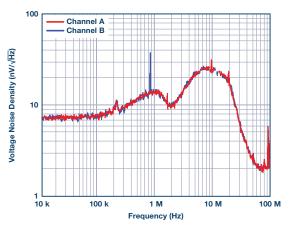

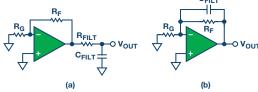

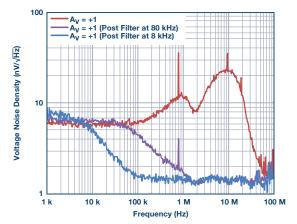

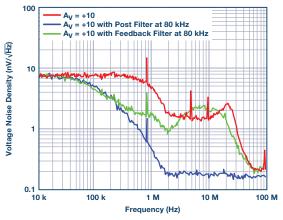

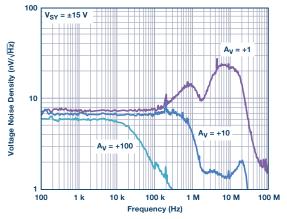

RF<sub>OUT</sub> = VCO output frequency/carrier frequency/desired signal