# (11) EP 3 026 442 A1

(12)

# **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

01.06.2016 Bulletin 2016/22

(51) Int Cl.:

G01R 1/36 (2006.01)

H02H 9/04 (2006.01)

(21) Application number: 15195715.6

(22) Date of filing: 20.11.2015

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Designated Extension States:

**BA ME**

**Designated Validation States:**

MA MD

(30) Priority: 21.11.2014 US 201462082841 P

10.12.2014 US 201414566534

(71) Applicant: Keithley Instruments, Inc. Cleveland OH 44139 (US)

(72) Inventor: GOEKE, Wayne Hudson, Ohio 44236 (US)

(74) Representative: Clarke, Jeffrey David

HGF Limited Fountain Precinct Balm Green

Sheffield S1 2JA (GB)

# (54) **VOLTAGE CLAMP**

(57) A voltage clamp circuit (200) which operates using a voltage controlled current source (I0) where the change of the polarity of the voltage controlled current source controls whether it is clamping or not. While clamping, the stability of the control loop uses the capacitance of the output (C1) to create and single pole roll-off

of the loop gain and while not clamping, uses the capacitance (C2) of the circuit which sets the clamping voltage to produce the roll-off. The circuit operates in a linear fashion both while clamping and not clamping, which allows for a faster response when clamping is needed.

FIG. 2

EP 3 026 442 A1

15

20

40

45

#### Description

#### **Technical Field**

**[0001]** This disclosure relates generally to voltage clamps and, more particularly, to voltage clamps designed for dry circuit ohms clamping.

1

### **Brief Description of the Drawings**

## [0002]

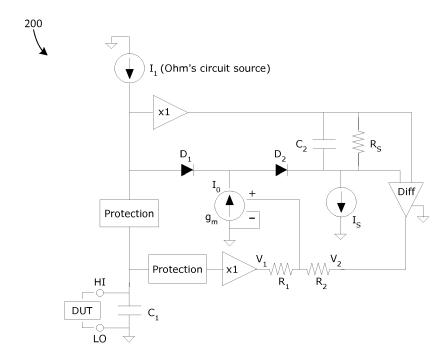

FIGURE 1 illustrates an example of a loop concept circuit on which certain voltage clamp design embodiments in accordance with the disclosed technology are based.

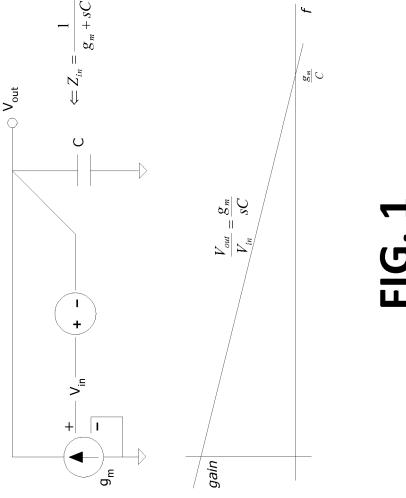

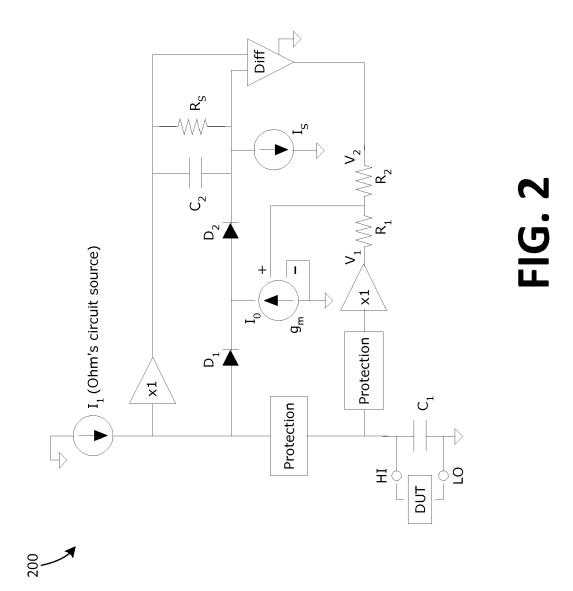

FIGURE 2 is a block diagram illustrating an example of a voltage clamp circuit coupled with a device under test (DUT) in accordance with certain embodiments of the disclosed technology.

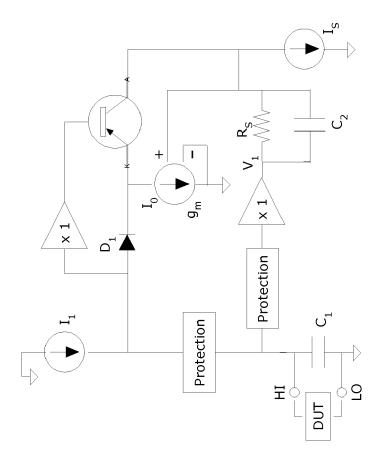

FIGURE 3 is a block diagram illustrating an alternative example of a voltage clamp circuit coupled with a DUT in accordance with certain embodiments of the disclosed technology.

#### **Detailed Description**

**[0003]** Dry circuit resistance generally requires a sourcing circuit that limits the maximum applied voltage across the device under test (DUT) to less than a few tens of millivolts (e.g., 20mV to 30mV). This is typically needed to prevent the breaking down of a thin oxide that can form on electrical contacts within the DUT, such as a relay contact or a contact within a connector pair.

**[0004]** Embodiments of the disclosed technology are generally directed to a circuit having a maximum voltage limit and a maximum current limit. The circuit may include a first current source configured to drive the output of the circuit (i.e., by setting the maximum current) and a second current source having a polarity that is opposite the polarity of the first current source, and is coupled with a resistance.

**[0005]** A voltage-controlled current source may be configured to, when its current has a polarity opposite that of the first current source, remove current from the output and, when its current has a polarity that is opposite that of the second current source, remove current from the node common to the second current source and the resistance, thus reducing the current through the resistance.

**[0006]** The circuit may include a component configured to compare the output voltage to the voltage across the resistance and drive the voltage controlled current source's input such that there is a negative feedback.

[0007] The circuit may include a first capacitance added to the output of the circuit to provide a single pole roll off of the output voltage from the input to the voltage controlled current source. The circuit may also include a

second capacitance added across the resistance to provide a single pole roll off of the voltage across the resistance from the input to the voltage controlled current source.

**[0008]** FIGURE 1 illustrates an example of a loop concept circuit 100 on which certain voltage clamp design embodiments in accordance with the disclosed technology are based. In the example 100, a capacitor C causes

a 20dB/dec roll-off where  $\frac{g_m}{c}$  represents the gain-bandwidth of the circuit. The current source  $\mathbf{g}_{\mathrm{m}}$  should have

a constant gain for frequencies less than or equal to  $\frac{g_m}{c}$ .

**[0009]** FIGURE 2 is a block diagram illustrating an example of a voltage clamp circuit 200 coupled with a DUT in accordance with certain embodiments of the disclosed technology. In the example, a current source  $I_0$  is steered by the two diodes  $D_1$  and  $D_2$  to regulate the voltage on one of two capacitors  $C_1$  or  $C_2$ . When the  $I_0$  current is negative, the Ohm's current source  $I_1$  is diverted through the first diode  $D_1$ , thus reducing the current flowing to the HI connection.

**[0010]** When the  $I_0$  current is positive, however, the  $I_S$  current source is supplied through the second diode  $D_2$ , thus reducing the current flowing through a source resistor  $R_S$ . The loop circuit 200 generally either regulates

$\frac{V_1}{R_1}$  to be equal to  $\frac{-V_2}{R_2}$  (i.e., with the first diode D<sub>1</sub>

conducting) or regulates  $\frac{V_2}{R_2}$  to be equal to  $\frac{-V_1}{R_1}$  (i.e.,

with the second diode  $D_2$  conducting).

[0011] In the example 200, a voltage  $V_1$  may be

clamped to  $\frac{R_1}{R_2}$   $R_SI_S$ . Thus,  $\frac{R_1}{R_2}$   $R_SI_S$  generally needs to be set between 20mV and 30mV to meet the

needs for dry circuit testing. The loop bandwidth is  $\frac{g_m}{c_1}$

when  ${\rm D_1}$  is conducting and switches to  $\,\frac{g_m}{c_2}\,$  when  ${\rm D_2}$  is conducting.

**[0012]** The ohm's current source protection will generally drop voltage when current is flowing through it. Therefore, the capacitor  $C_2$  and source resistor Rs may be bootstrapped to follow the ohm's current source's voltage. This advantageously prevents both of the diodes  $D_1$  and  $D_2$  from turning on at the same time. A differential stage, Diff, may be used to translate the voltage across the source resistor Rs to ground to be mixed against the voltage  $V_1$ .

**[0013]** In the example 200, the first capacitor  $C_1$  is used to limit the rate that the voltage  $V_1$  rises when a conduction path (e.g., the DUT) between the HI and LO connections is suddenly removed, e.g., to minimize the over-

shoot. Using the capacitance- $g_m$  interaction to control stability generally avoids problems that the capacitance may present in situations where a normal voltage source loop is used.

**[0014]** FIGURE 3 is a block diagram illustrating an alternative example of a voltage clamp circuit 300 coupled with a DUT in accordance with certain embodiments of the disclosed technology. In the example 300, the clamp voltage for V<sub>1</sub> is  $I_S * R_S$ .

**[0015]** Examples provide a voltage clamp circuit, comprising a first current source configured to drive an output of the circuit, the first current source having a polarity, a second current source coupled with a resistance, the second current source having a polarity that is opposite the polarity of the first current source, a voltage-controlled current source having a polarity and configured to, when its polarity is opposite that of the first current source, remove current from the output and, when its polarity is opposite that of the second current source, remove current from a node common to the second current source and the resistance, a first capacitance coupled with the resistance

**[0016]** Some examples further comprise a component configured to compare the output voltage to the voltage across the resistance.

**[0017]** In some examples the component is further configured to drive an input of the voltage-controlled current source such than there is a negative feedback.

**[0018]** In some examples the first current source is configured to drive the output of the circuit by setting a maximum current.

**[0019]** In some examples the first capacitance is configured to provide a single pole roll off of the output voltage from the input to the voltage-controlled current source.

**[0020]** In some examples the second capacitance is configured to provide a single pole roll off of the voltage across the resistance from input to the voltage controlled current source.

**[0021]** Having described and illustrated the principles of the invention with reference to illustrated embodiments, it will be recognized that the illustrated embodiments may be modified in arrangement and detail without departing from such principles, and may be combined in any desired manner. And although the foregoing discussion has focused on particular embodiments, other configurations are contemplated.

[0022] In particular, even though expressions such as "according to an embodiment of the invention" or the like are used herein, these phrases are meant to generally reference embodiment possibilities, and are not intended to limit the invention to particular embodiment configurations. As used herein, these terms may reference the same or different embodiments that are combinable into other embodiments.

#### Claims

1. A voltage clamp circuit, comprising:

a first current source configured to drive an output of the circuit, the first current source having a polarity;

a second current source coupled with a resistance, the second current source having a polarity that is opposite the polarity of the first current source:

a voltage-controlled current source having a polarity and configured to:

when its polarity is opposite that of the first current source, remove current from the output; and

when its polarity is opposite that of the second current source, remove current from a node common to the second current source and the resistance:

a first capacitance coupled with the output; and a second capacitance coupled across the resistance.

- The circuit of claim 1, further comprising a component configured to compare the output voltage to the voltage across the resistance.

- The circuit of claim 2, wherein the component is further configured to drive an input of the voltage-controlled current source such than there is a negative feedback.

- 4. The circuit of any previous claim, wherein the first current source is configured to drive the output of the circuit by setting a maximum current.

- 40 5. The circuit of any previous claim, wherein the first capacitance is configured to provide a single pole roll off of the output voltage from the input to the voltage-controlled current source.

- 45 **6.** The circuit of any of claims 1 to 4, wherein the second capacitance is configured to provide a single pole roll off of the voltage across the resistance from input to the voltage controlled current source.

55

50

30

35

# FIG. 3

#### **EUROPEAN SEARCH REPORT**

**Application Number** EP 15 19 5715

5

**DOCUMENTS CONSIDERED TO BE RELEVANT** CLASSIFICATION OF THE APPLICATION (IPC) Citation of document with indication, where appropriate, Relevant Category of relevant passages to claim 10 US 5 337 205 A (HAUN ANDY A [US] ET AL) 9 August 1994 (1994-08-09) Χ 1-6 INV. G01R1/36 column 4, line 48 - line 55 \* figure 1 \* ADD. \* figure 2 \* H02H9/04 \* column 3, line 53 - line 55 \* \* figure 3 \* 15 \* column 4, line 10 - line 13 \* \* column 4, line 56 - line 65 \* US 6 717 450 B1 (LINDER LLOYD F [US]) 1 Α 20 6 April 2004 (2004-04-06) \* figure 1 \* US 5 384 532 A (UHLING THOMAS F [US]) 5,6 Α 24 January 1995 (1995-01-24) \* column 9, line 55 - line 58 \* 25 US 2007/216391 A1 (BLANKEN PIETER G [NL]) 20 September 2007 (2007-09-20) Α 4 \* the whole document \* TECHNICAL FIELDS SEARCHED (IPC) 30 Α EP 1 832 888 A1 (TERADYNE INC [US]) 1 G01R 12 September 2007 (2007-09-12) H01L \* the whole document \* H<sub>0</sub>2H US 2009/086395 A1 (SKRENES LAWRENCE [US] ET AL) 2 April 2009 (2009-04-02) Α 1 35 the whole document \* 40 45 The present search report has been drawn up for all claims 3 Place of search Date of completion of the search Examiner 50 15 April 2016 Meliani, Chafik Munich T: theory or principle underlying the invention E: earlier patent document, but published on, or after the filling date D: document cited in the application CATEGORY OF CITED DOCUMENTS 03.82 ( X : particularly relevant if taken alone

Y : particularly relevant if combined with another

document of the same category

A : technological background 1503 L : document cited for other reasons 55 & : member of the same patent family, corresponding non-written disclosure

P: intermediate document

# EP 3 026 442 A1

# ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 15 19 5715

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

15-04-2016

| c          | Patent document ited in search report |    | Publication<br>date |                                                    | Patent family<br>member(s)                                                                                    |                                     | Publication<br>date                                                                                                        |

|------------|---------------------------------------|----|---------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| U:         | S 5337205                             | A  | 09-08-1994          | CA<br>DE<br>DE<br>EP<br>JP<br>JP<br>US<br>WO       | 2122259<br>69308534<br>69308534<br>0611495<br>2801404<br>H07501200<br>5337205<br>9406190                      | D1<br>T2<br>A1<br>B2<br>A<br>A      | 17-03-1994<br>10-04-1997<br>11-09-1997<br>24-08-1994<br>21-09-1998<br>02-02-1995<br>09-08-1994<br>17-03-1994               |

| U:         | S 6717450                             | B1 | 06-04-2004          | AU<br>TW<br>US<br>WO                               | 2003269419<br>200402541<br>6717450<br>03098231                                                                | A<br>B1                             | 02-12-2003<br>16-02-2004<br>06-04-2004<br>27-11-2003                                                                       |

| Ü:         | S 5384532                             | Α  | 24-01-1995          | NON                                                | E                                                                                                             |                                     |                                                                                                                            |

| U:         | S 2007216391                          | A1 | 20-09-2007          | AT<br>CN<br>EP<br>ES<br>JP<br>JP<br>KR<br>US<br>WO | 544225<br>101027621<br>1797492<br>2381482<br>4734511<br>2008515077<br>20070059201<br>2007216391<br>2006035394 | A<br>A1<br>T3<br>B2<br>A<br>A<br>A1 | 15-02-2012<br>29-08-2007<br>20-06-2007<br>28-05-2012<br>27-07-2011<br>08-05-2008<br>11-06-2007<br>20-09-2007<br>06-04-2006 |

| E          | P 1832888                             | A1 | 12-09-2007          | AT<br>EP<br>TW<br>US<br>WO                         | 434189<br>1832888<br>200817706<br>2007210810<br>2007102856                                                    | A1<br>A<br>A1                       | 15-07-2009<br>12-09-2007<br>16-04-2008<br>13-09-2007<br>13-09-2007                                                         |

| U:         | S 2009086395                          | A1 | 02-04-2009          | US<br>WO                                           | 2009086395<br>2009046013                                                                                      |                                     | 02-04-2009<br>09-04-2009                                                                                                   |

| FORM P0459 |                                       |    |                     |                                                    |                                                                                                               |                                     |                                                                                                                            |

© Lorentz Control Cont