#### **Document information**

| Information | Content                                                                                                                              |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | MOSFET, maximum peak drain current                                                                                                   |

| Abstract    | This application note provides an explanation of the derivation of the maximum drain current as a function of pulse duration rating. |

#### Understanding the MOSFET peak drain current rating

### 1. Introduction

$I_{DM}$  is the maximum rated peak drain current for a power MOSFET. It can be defined as a function of the time duration of a rectangular current pulse.  $I_{DM}$  is referred to in the Nexperia application note *AN11158* [1] and IEC60747-8 [2].

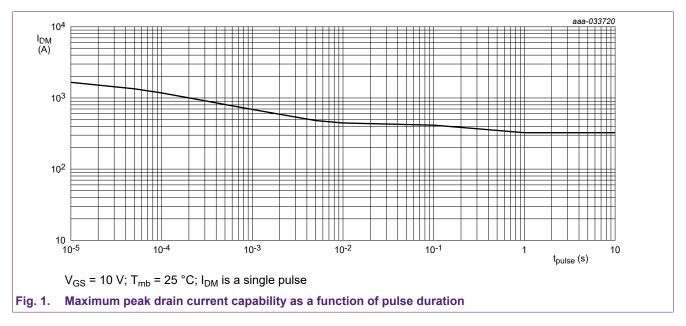

Recently, in some Nexperia MOSFET data sheets, a graph is included which shows the maximum device peak drain current capability ( $I_{DM}$ ) expressed as a function of pulse duration. An example from the BUK7S1R0-40H data sheet <sup>[3]</sup> is shown below in Fig. 1.

In Fig. 1 time is shown logarithmically from 10  $\mu$ s to 10 s. The maximum allowed peak drain current  $I_{DM}$  is also expressed logarithmically.

Historically the  $I_{DM}$  capability is shown in the limiting values section of the data sheet for  $t_p \le 10~\mu s$ .  $I_D$  at DC (continuous) is also shown.  $I_{DM}$  is traditionally specified as four times the theoretical value of  $I_D$  at DC, see Fig. 2. The  $I_{DM}$  rating here is more than four times the  $I_D$  as the  $I_D$  specified is limited by the package, rather than the silicon itself.

### Table 5. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter               | Conditions                                                      |     | Min | Max  | Unit |

|------------------|-------------------------|-----------------------------------------------------------------|-----|-----|------|------|

| V <sub>DS</sub>  | drain-source voltage    | 25 °C ≤ T <sub>j</sub> ≤ 175 °C                                 |     | -   | 40   | V    |

| $V_{GS}$         | gate-source voltage     | DC; T <sub>j</sub> ≤ 175 °C                                     |     | -10 | 20   | V    |

| P <sub>tot</sub> | total power dissipation | T <sub>mb</sub> = 25 °C; Fig. 1                                 |     | -   | 375  | W    |

| I <sub>D</sub>   | drain current           | V <sub>GS</sub> = 10 V; T <sub>mb</sub> = 25 °C; Fig. 2         | [1] | -   | 325  | Α    |

| I <sub>DM</sub>  | peak drain current      | pulsed; $t_p \le 10 \mu s$ ; T $_{mb} = 25 \text{ °C}$ ; Fig. 3 |     | -   | 1659 | Α    |

### Fig. 2. BUK7S1R0-40H data sheet limiting values

It is difficult for the user to know what the capability would be at other time durations. Some information can be gleaned from the Safe Operating Area (SOA) graph, however it is still hard to assess the actual capability for different time intervals.

The aim of this new  $I_{DM}$  graph is to provide information regarding the current handling capability of the MOSFET for any time duration in the range provided. It should be noted that only the current carrying capability due to conduction losses is considered. Additional losses incurred due to

AN50014

### **Understanding the MOSFET peak drain current rating**

switching events (linear mode and avalanche) may take the device junction temperature beyond the 175 °C limit and cause damage to the device.

### 2. I<sub>DM</sub> theoretical curve calculation

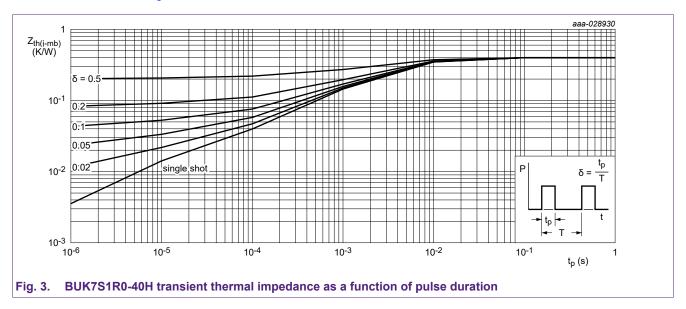

The power handling capability of the MOSFET can be derived using the transient thermal impedance characteristic ( $Z_{th}$ ) curve. An example from BUK7S1R0-40H data sheet is shown in Fig. 3 below:

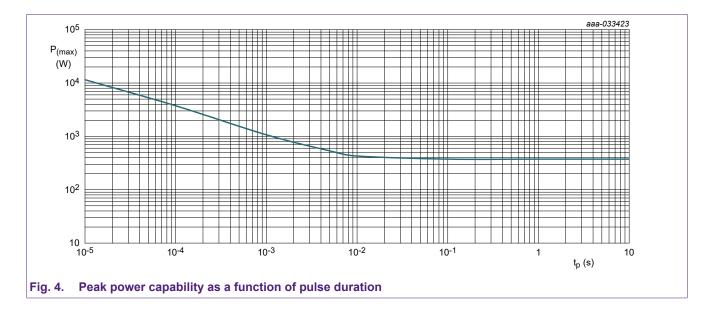

The transient power capability characteristic as a function of time can be determined, assuming that the MOSFET junction temperature would be raised by 150 K, from 25  $^{\circ}$ C to 175  $^{\circ}$ C. See Eq. 1 and Fig. 4.

$$P_{max}(t) = \frac{150}{Z_{th}(t)} \tag{1}$$

AN50014

### **Understanding the MOSFET peak drain current rating**

To relate power capability to theoretical maximum current, the following relationship is used:

$$I_{DM}(t) = \sqrt{\frac{P_{max}(t)}{R_{DSon}}}$$

(2)

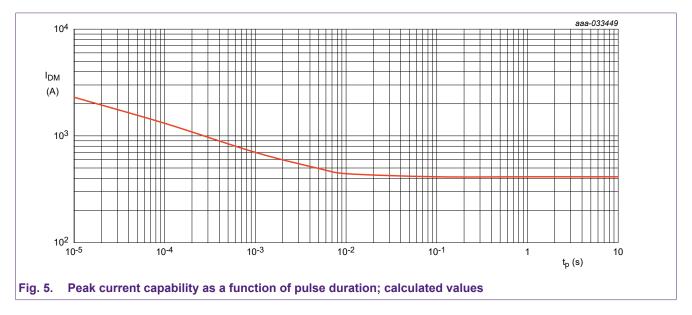

$R_{DSon}$  in <u>Eq. 2</u> is the maximum value specified at 175 °C. Using the data sheet value of 2.2 m $\Omega$ , a theoretical characteristic based on this formula is shown in <u>Fig. 5</u>.

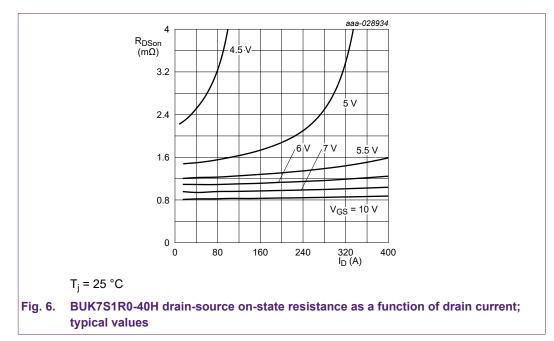

The maximum theoretical device current for a 10  $\mu$ s pulse is 2.3 kA, see <u>Fig. 5</u>. However, the R<sub>DSon</sub> changes with I<sub>D</sub> and this is not taken into account with this approach. R<sub>DSon</sub> value increases with I<sub>D</sub>. See the example graph from BUK7S1R0-40H data sheet in <u>Fig. 6</u> below:

The data provided in Fig. 6 is for 25 °C and is only for  $I_D$  up to 400 A. Therefore, it cannot be used for  $I_{DM}$  estimation. As  $R_{DSon}$  dependence on  $I_D$  is not taken into account, the data on Fig. 5 is an over estimate. Actual measurement of the device capability is a better way to determine with confidence the current handling capability at various time intervals.

AN50014

### Understanding the MOSFET peak drain current rating

### 3. Device test method

Devices at Nexperia are measured for  $I_{DM}$  from 10 µs pulses up to DC. The devices, depending on their size, are expected to achieve several thousand of Amperes of  $I_{DM}$  at 10 µs and few hundred Amperes at DC. For this reason different test gear is used for pulsed and DC measurements.

For pulsed conditions, an in-house designed pulse current tester is used, capable of 5 kA for pulse lengths up to 100  $\mu$ s. The longest pulse tested is 10 ms. The device is mounted to a specially designed test PCB which ensures low inductance and current. This is important because the pulsed current will have very steep turn-on and turn-off slopes. The thermal capability of the PCB is not critical since at such short pulse intervals no significant heat is transferred to the PCB.

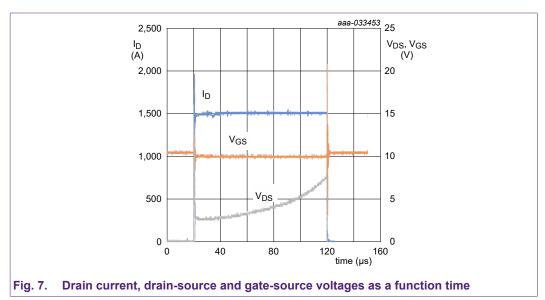

Waveforms showing typical behaviour are shown in Fig. 7 below:

In this example a 1,500 A, 100  $\mu$ s pulse is applied to a device which is already switched on. Initially the voltage drop across the device is around 2.7 V, therefore  $R_{DSon}$  is around 1.8  $m\Omega$

(2.7 V/1,500 A). At this, initial instance the junction can be considered to be close to 25 °C ambient temperature. According to the device data sheet, at 25 °C the maximum value of  $R_{DSon}$  is 1 m $\Omega$  at a 25 A test current and the typical value is 0.88 m $\Omega$ . As it can be seen in this example, the measured  $R_{DSon}$  is roughly double the data sheet value, because of the big difference in the applied current.

As the device heats up, the  $V_{DS}$  increases to around 7.5 V.  $R_{DSon}$  is therefore around 5 m $\Omega$  (7.5 V/1,500 A). This waveform is recorded just before device failure, so it is likely that the junction temperature was higher than 175 °C. It may happen that the capability of the device exceeds the tester capability, so the device cannot be tested until destruction, and the true  $I_{DM}$  cannot be obtained.

A different tester is used to test DC capability, because the device has to be cooled. The mounting base temperature is kept as close to 25 °C as it is practically possible, whilst the junction temperature achieves 175 °C. The device must be mounted on a special high thermal conductivity board, in order to ensure that heat is removed from the package as effectively as possible. The device and PCB are then immersed in cooling fluid. Note that these measures to cool the device are required to demonstrate the MOSFET capability and are impractical for most real applications.

Several devices are tested at each time point (from 10 µs to DC). This allows statistical analysis to be performed and suitable derating applied to take into consideration device variability.

### Understanding the MOSFET peak drain current rating

### 4. Measurement results

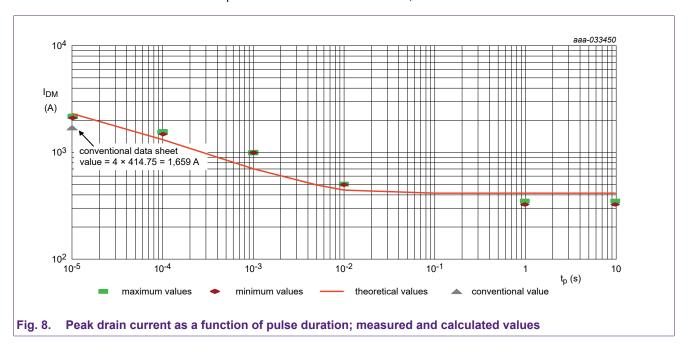

For this device (BUK7S1R0-40H) the theoretical  $I_{D(dc)}$  is 414.75 A. Therefore  $I_{DM}$  at 10  $\mu s$  is determined as per the convention:  $4 \times 414.75 = 1,659$  A.

Considering a small sample of measured devices,  $I_{DM}$  at 10  $\mu$ s achieves around 2.1 kA. As previously suggested, this is less than the value derived on Fig. 5 of 2.3 kA. Fig. 8 demonstrates the relationship between the theoretical and measured values for  $I_{DM}$ . The grey triangle denotes the value obtained by convention.

#### **Derating**

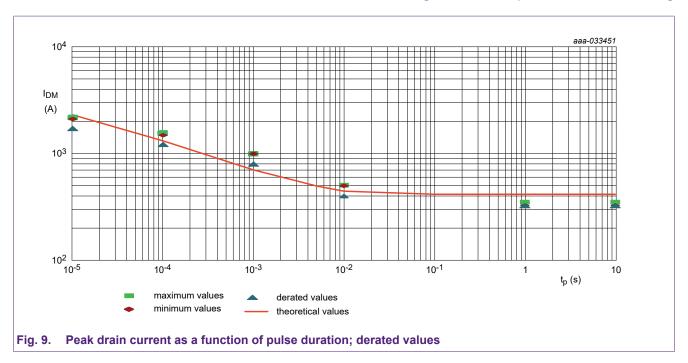

To guarantee a safe capability curve the measured values are derated by 20%, to consider the fact that  $T_j$  will be > 175 °C in the measurements and that there will be some batch to batch variation in device performance. The derated peak current at 10  $\mu$ s is, therefore, reduced to 1,680 A, which is close to the conventionally obtained value. At the DC end of the curve, devices can be measured for 10 s or longer durations, however there is still an untested gap between 10 ms and 10 s. To fill this gap interpolation is used, with the value obtained for 10 s used for the 1 s value.

### **Understanding the MOSFET peak drain current rating**

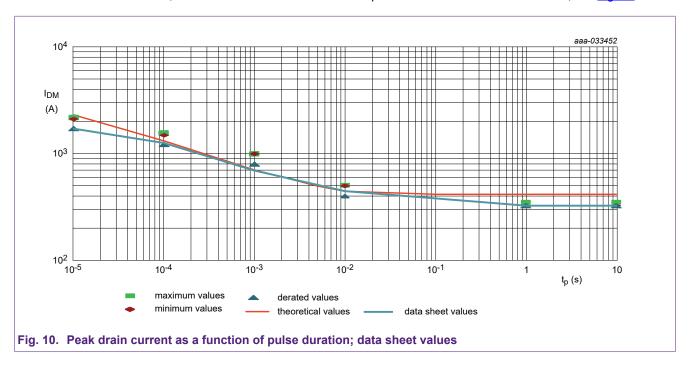

Consequently, the characteristic curve is a theoretical line which is supported by test results. If the derated minimum measured values are above the theoretical line then the theoretical line is the limit, otherwise the derated measurement point will determine the characteristic; see Fig. 10

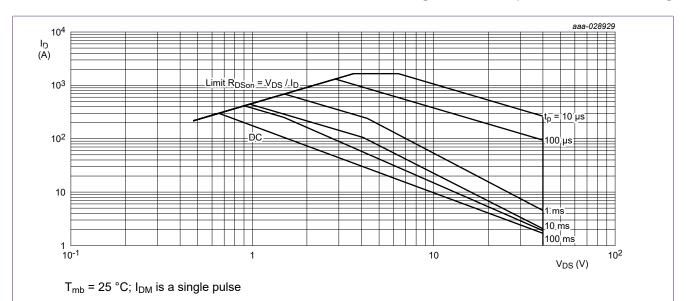

Having determined the capability at different pulse durations, this is aligned with other data sheet characteristics such as the Safe Operating Area, example in Fig. 11 below:

### **Understanding the MOSFET peak drain current rating**

Fig. 11. BUK7S1R0-40H Safe operating area; continuous and peak drain currents as a function of drain-source voltage

### 5. Example of the final IDM curve

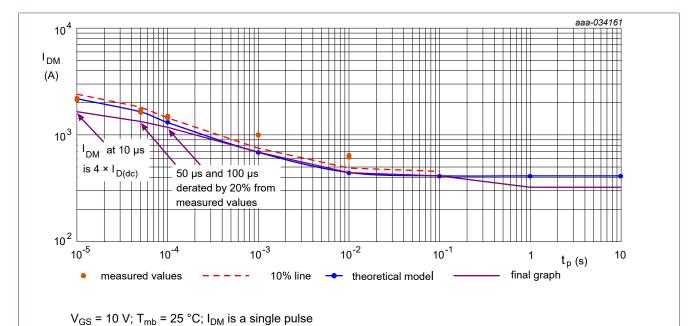

The graph shown in Fig. 12 shows the capability of the BUK7S1R0-40H, taking into account the theoretical capability and de-rated measured capability. Fig. 12 also shows a 10% safety line from the measured data points, that is also taken into account when producing the final graph that appears in the data sheets. Due to the combination of the methods for obtaining the data sheet values, Nexperia has a high degree of confidence that this is the practical limit for current handling capability as a function of time.

Fig. 12. BUK7S1R0-40H peak drain current capability; measured values, theoretical model, 10% line and final graph

### **Understanding the MOSFET peak drain current rating**

### 6. References

- 1. Nexperia application note AN11158

- **2.** <u>IEC</u> IEC 60747-8: 2010

- 3. Nexperia data sheet BUK7S1R0-40H

# 7. Revision history

### Table 1. Revision history

| Revision number | Date       | Description      |

|-----------------|------------|------------------|

| 1.0             | 2022-03-28 | Initial version. |

### Understanding the MOSFET peak drain current rating

### 8. Legal information

#### **Definitions**

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

Right to make changes — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Nexperia does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### **Trademarks**

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

Understanding the MOSFET peak drain current rating

| - |     | _   | _  |   |     |

|---|-----|-----|----|---|-----|

|   | ist | O.F | To | ы |     |

|   |     |     | 17 |   | 160 |

|   |     |     |    |   |     |

Table 1. Revision history.....9

### **Understanding the MOSFET peak drain current rating**

# **List of Figures**

| Fig. 1. Maximum peak drain current capability as a function of pulse duration                                       | 2 |

|---------------------------------------------------------------------------------------------------------------------|---|

| Fig. 2. BUK7S1R0-40H data sheet limiting values                                                                     | 2 |

| Fig. 3. BUK7S1R0-40H transient thermal impedance as a function of pulse duration                                    | 3 |

| Fig. 4. Peak power capability as a function of pulse duration                                                       | 3 |

| Fig. 5. Peak current capability as a function of pulse duration; calculated values                                  | 4 |

| Fig. 6. BUK7S1R0-40H drain-source on-state resistance as a function of drain current; typical values                | 4 |

| Fig. 7. Drain current, drain-source and gate-source voltages as a function time                                     | 5 |

| Fig. 8. Peak drain current as a function of pulse duration; measured and calculated values                          | 6 |

| Fig. 9. Peak drain current as a function of pulse duration; derated values                                          | 7 |

| Fig. 10. Peak drain current as a function of pulse duration; data sheet values                                      | 7 |

| Fig. 11. BUK7S1R0-40H Safe operating area; continuous and peak drain currents as a function of drain-source voltage | 8 |

| Fig. 12. BUK7S1R0-40H peak drain current capability; measured values, theoretical model, 10% line and               | 0 |

| final graph                                                                                                         | o |

### **Understanding the MOSFET peak drain current rating**

# **Contents**

| 1  | Introduction                                  | -  |

|----|-----------------------------------------------|----|

|    |                                               |    |

| 2. | I <sub>DM</sub> theoretical curve calculation | 3  |

| 3. | Device test method                            | 5  |

| 4. | Measurement results                           | е  |

| 5. | Example of the final IDM curve                | 8  |

| 6. | References                                    | 9  |

| 7. | Revision history                              | 9  |

| 8. | Legal information                             | 10 |

|    |                                               |    |

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com Date of release: 28 March 2022

<sup>©</sup> Nexperia B.V. 2022. All rights reserved