# MOTOROLA

# Advance Information **Dual PLL Frequency** Synthesizers with **DACs and Voltage Multiplier**

The MC145225 and MC145230 are dual frequency synthesizers containing very-low supply voltage circuitry. These devices support two independent loops with a single input reference and operate down to 1.8 V. Phase noise reduction circuitry is incorporated into each device.

The MC145225 is capable of direct usage up to 1.2 GHz on the main loop and up to 550 MHz on the secondary loop. The MC145230 is capable of direct usage up to 2.2 GHz on the main loop and up to 550 MHz on the secondary loop. Each device has a 32/33 prescaler for the main loop and an 8/9 prescaler for the secondary loop. Lock detection circuitry for each loop is multiplexed to a single output.

Two 8-bit DACs are powered through a dedicated pin. The DAC supply range is 1.8 to 3.6 V; this voltage may differ from the main supply.

An on-chip voltage multiplier supplies power to the phase/frequency detectors. Thus, in a 2 V application, the detectors are supplied with 4 V power. In 2.6 to 3.6 V applications, the multiplied voltage is regulated at approximately 5 V. The current source/sink phase/frequency detector for the main loop is designed to achieve faster lock times than a conventional detector. Both high and low current outputs are available along with a timer, double buffers, and a MOSFET switch to adjust the external low-pass filter response.

There are several levels of standby which are controllable with a 1-byte transfer through the serial port. Either of the PLLs and/or the reference oscillator may be independently placed in the low-power standby state. In addition, any of the phase/frequency detector outputs may be placed in the floating state to facilitate modulation of the external VCOs. Either DAC may be placed in standby via a 4-byte transfer.

- Operating Frequency MC145225 — Main Loop: 100 to 1200 MHz Secondary Loop: 50 to 550 MHz MC145230 — Main Loop: 500 to 2200 MHz Secondary Loop: 50 to 550 MHz

- Operating Supply Voltage: 1.8 to 3.6 V

emiconductor,

esca

- Nominal Supply Current, Both Loops Active MC145225: 4 mA MC145230: 5 mA

- Maximum Standby Current, All Systems Shut Down: 10 μA

- Nominal Phase Detector Output Current: 1.8 V Supply - PDout-Hi: 2.8 mA, PDout-Lo: 0.7 mA ≥2.5 V Supply - PDout-Hi: 4.4 mA, PDout-Lo: 1.1 mA

- Two Independent 8–Bit DACs with Separate Supply Pin (Up to 3.6 V)

- Lock Detect Output with Adjustable Lock Indication Window

- Independent R Counters Allow Independent Step Sizes for Each Loop

- Main Loop Divider Range: 992 to 262,143

- Secondary Loop Divider Range: 152 to 65,535

- Fractional Reference Counters Divider Range: 20 to 32,767.5

- Auxiliary Reference Divider with Small–Signal Differential Output - Ratios: 8, 10, 12.5

- Three General–Purpose Outputs

- Direct Interface to Motorola SPI Data Port Up to 10 Mbps

BitGrabber is a trademark of Motorola, Inc.

MC145225 MC145230

# **BICMOS COMPONENT** FOR 2 OR 3 VOLT SYSTEMS

SEMICONDUCTOR **TECHNICAL DATA**

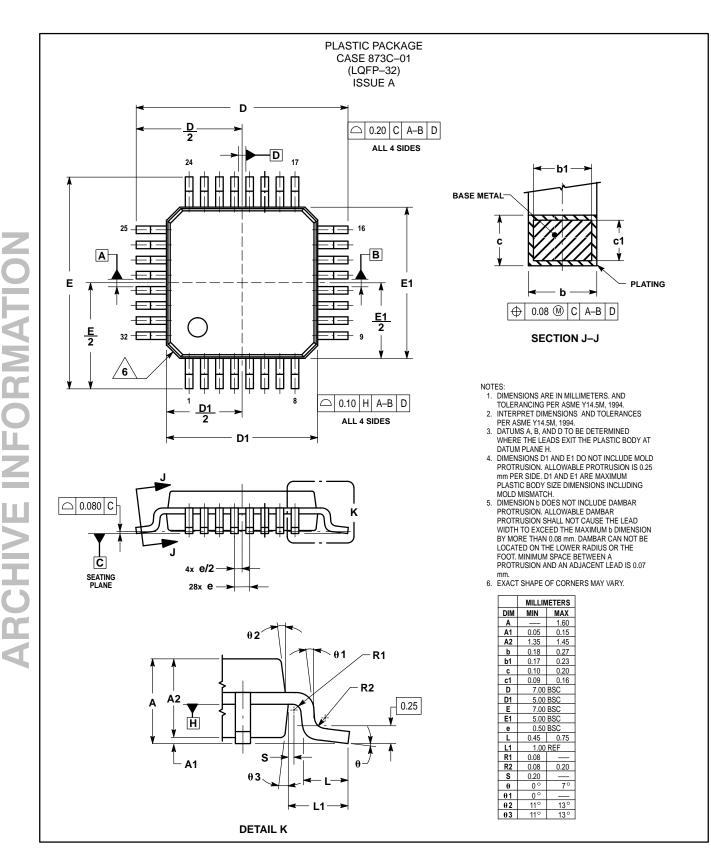

PLASTIC PACKAGE CASE 873C (LQFP-32, Tape & Reel Only) VERY-SMALL 5 x 5 mm BODY

# **DEVELOPMENT SYSTEM**

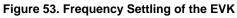

The MC145230EVK, which contains hardware and software, is strongly recommended for system development. (The user must provide the VCOs for evaluating the MC145181.) The software supports all features and modes of operation of the device. Up to four boards or devices can be controlled and the user is alerted to error conditions. The control program may be used with any board based on the MC145181, MC145225, or MC145230.

# **ORDERING INFORMATION**

| Device        | Main/Secondary<br>Loop<br>Maximum<br>Frequency | Package |

|---------------|------------------------------------------------|---------|

| MC145225FTAR2 | 1200/550 MHz                                   | LQFP-32 |

| MC145230FTAR2 | 2200/550 MHz                                   |         |

This document contains information on a new product. Specifications and information herein are subject to change without notice.

For More Information On This Product, Go to: www.freescale.com

**Freescale Semiconductor, Inc.**

**B**N

**O**

Z

Ĩ

4

# Freescale Seminonductor, Inc.

# CONTENTS

| 1.  | BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2.  | PIN CONNECTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4                    |

| 3.  | PARAMETER TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                    |

|     | <ul> <li>3A. Maximum Ratings</li> <li>3B. DC Electrical Characteristics</li> <li>3C. PD<sub>out</sub>–Hi and PD<sub>out</sub>–Lo Phase/Frequency Detector Characteristics</li> <li>3D. PD<sub>out</sub>' Phase/Frequency Detector Characteristics</li> <li>3E. DAC Characteristics</li> <li>3F. Voltage Multiplier and Keep–alive Oscillator Characteristics</li> <li>3G. Dynamic Characteristics of Digital Pins</li> <li>3H. Dynamic Characteristics of Loop and f<sub>out</sub> Pins</li> </ul> |                      |

| 4.  | DEVICE OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                    |

|     | <ul> <li>4A. Serial Interface and Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10<br>10             |

| 5.  | PIN DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                   |

|     | <ul> <li>5A. Digital Pins</li> <li>5B. Reference Pins</li> <li>5C. Loop Pins</li> <li>5D. Analog Outputs</li> <li>5E. External Components</li> <li>5F. Supply Pins</li> </ul>                                                                                                                                                                                                                                                                                                                      | 13<br>13<br>14<br>15 |

| 6.  | DETAILED REGISTER DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 16                   |

|     | 6A.       C Register         6B.       Hr Register         6C.       N Register         6D.       R' Register         6E.       Hn' Register         6F.       D Register                                                                                                                                                                                                                                                                                                                          | 19<br>20<br>22<br>25 |

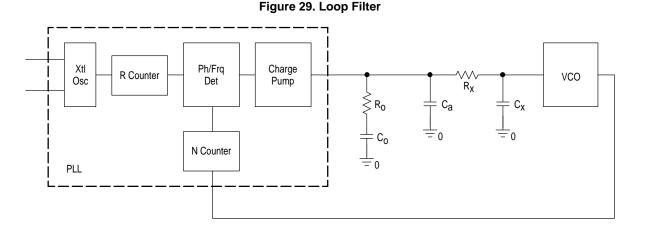

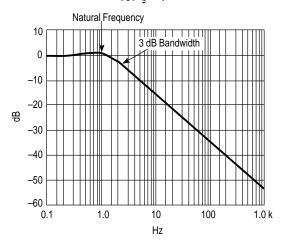

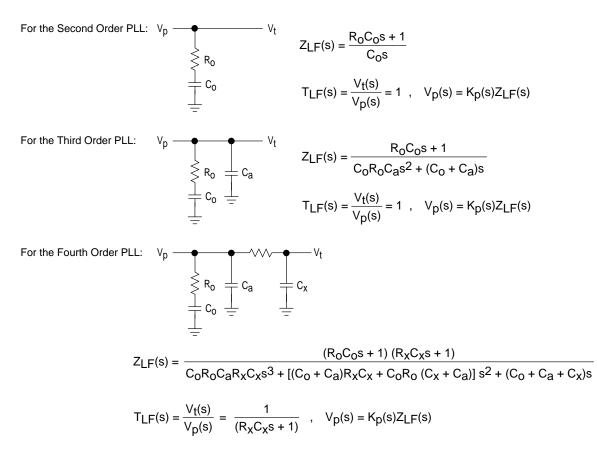

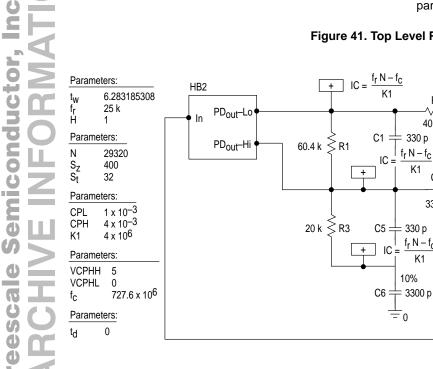

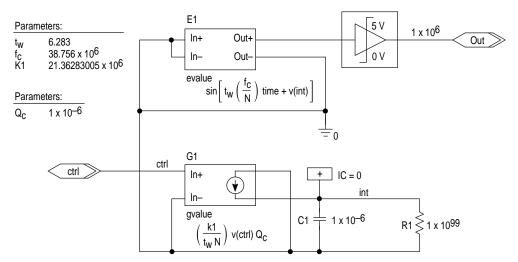

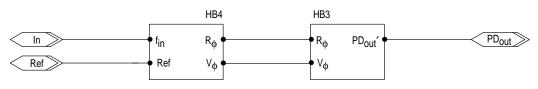

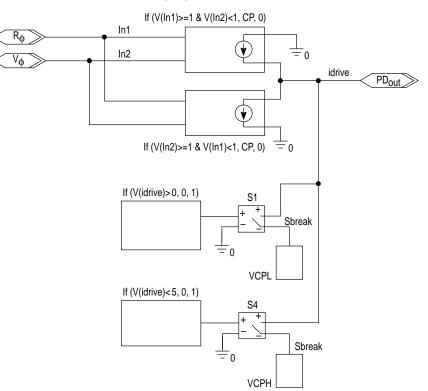

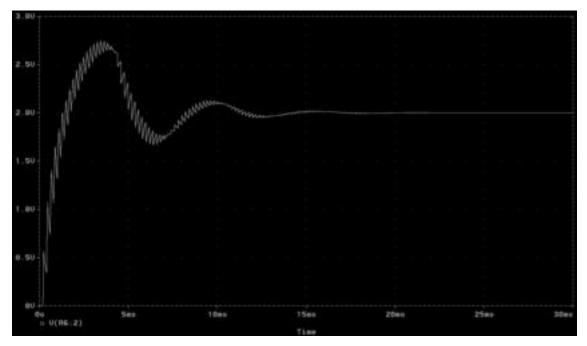

| 7.  | APPLICATIONS INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29                   |

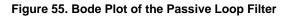

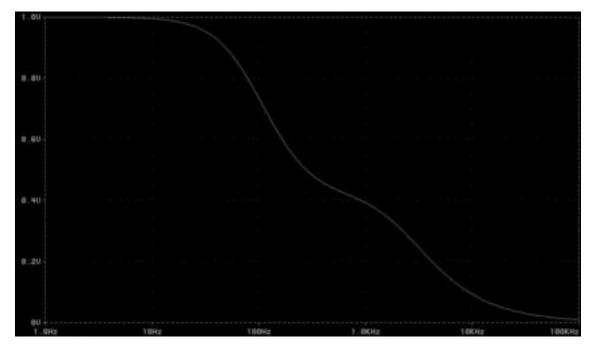

|     | <ul> <li>7A. Crystal Oscillator Considerations</li> <li>7B. Main Loop Filter Design — Conventional</li> <li>7C. Main Loop Filter Design — Adapt</li> <li>7D. Secondary Loop Filter Design</li> <li>7E. Voltage Multiplier Stall Avoidance</li> </ul>                                                                                                                                                                                                                                               | 34<br>41<br>50       |

| 8.  | PROGRAMMER'S GUIDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58                   |

|     | <ul> <li>8A. Quick Reference</li> <li>8B. Initializing the Device</li> <li>8C. Programming Without Adapt</li> <li>8D. Programming Utilizing Horseshoe With Adapt</li> <li>8E. Controlling the DACs</li> </ul>                                                                                                                                                                                                                                                                                      | 66                   |

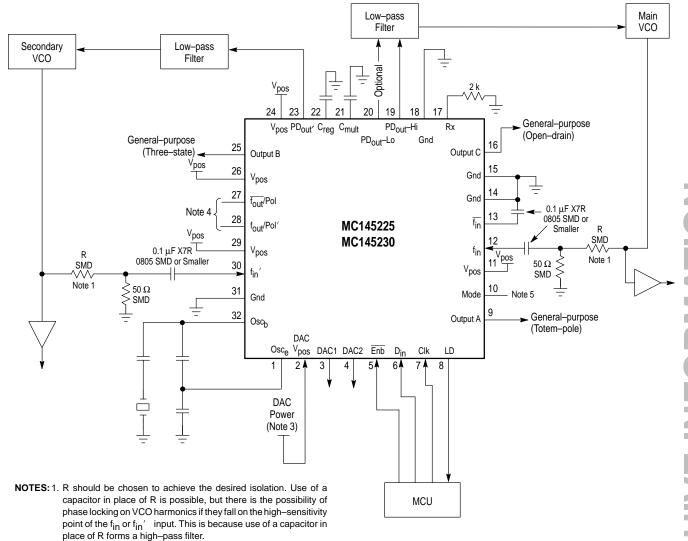

| 9.  | APPLICATION CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 69                   |

| 10. | OUTLINE DIMENSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 70                   |

Semiconductor, Inc. /E INFORMATIC

reescale

1. BLOCK DIAGRAM

Freescale Seminonductor, Inc.

16 ► Output C Ē Out C 25 ► Output B Out B/Ref PLL Stby Out A C Register 8 Bits PLL Stby fR Output A 9 ► Output A Mux  $f_{R}'$ - PLL' Stby Ph Det Pulse PD Float ► PD' Float Osc Stby Function Timer N Register 3 High-24 Bits 19 ► PD<sub>out</sub>-Hi current Charge 18 Pump  $\frac{f_{\text{in}}}{f_{\text{in}}} \frac{12}{13}$ Phase/ fy <u>17</u> Rx Frequency N Counter 18 Stages Detector, Amp Timer, Lowand Control fR 20 ► PD<sub>out</sub>-Lo current R Counter Charge 16 Stages Lo-I Gain Pump 16 Polarity R Register Osc-16 Bits 21 C<sub>mult</sub> Voltage V-Mult Window 22 Creg Multiplier Control 16/ and Regulator ⊌ Hr Register Lock 16 Bits Detector Osc<sub>e</sub> Osc<sub>b</sub> <sup>8</sup>→ LD 2 Oscillator 3 Supply Current R' Register Minimization Lock Circuit 24 Bits Detector' 16 Test  $f_{R}'$ R' Counter 16 Stages Ratio Phase/ 23 ► PD<sub>out</sub>' Mode 10 Frequency Detector' fv′ f<sub>in</sub>' <u>30</u> N' Counter 16 Stages Amp 16 Polarity N' Register 16 Bits 28 fout/Pol 16 J Auxiliary 27 - fout/Pol Divider 3 Stages Hn' Register 16 Bits DAC <sup>3</sup> ► DAC1 8 D Register 8 Bits 8 16 Bits \_\_\_\_ DAC V<sub>pos</sub> 5 Enb -DAC <sup>4</sup> ► DAC2 Power Connections: 8 Bits Shift Register and 6 Din Pin 2 = DAC V<sub>pos</sub> Address Generator Pins 11, 24, 26, and 29 = V<sub>pos</sub> 7 Clk Pins 14, 15, 18, and 31 = Gnd

Semiconductor, Inc

eescale

Ĭ

Z

ш

# Freescale Seminonductor, Inc.

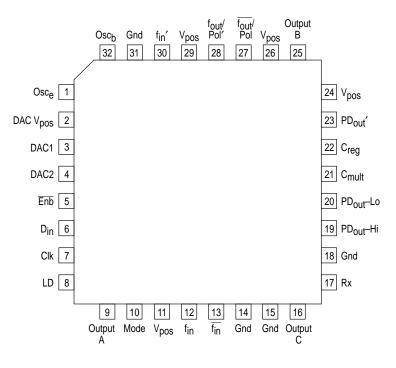

# 2. PIN CONNECTIONS

This device contains 15,260 active transistors.

# 3. PARAMETER TABLES

| Parameter                                                                                                                                                     | Symbol                                     | Value                          | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------|------|

| DC Supply Voltages                                                                                                                                            | V <sub>pos</sub> ,<br>DAC V <sub>pos</sub> | -0.5 to 3.6                    | V    |

| DC Input Voltage — Osc <sub>e</sub> , f <sub>in</sub> , f <sub>in</sub> ', Mode,<br>D <sub>in</sub> , Clk, Enb, f <sub>out</sub> /Pol', f <sub>out</sub> /Pol | V <sub>in</sub>                            | –0.5 to V <sub>pos</sub> + 0.5 | V    |

| DC Output Voltage                                                                                                                                             | Vout                                       | –0.5 to V <sub>pos</sub> + 0.5 | V    |

| DC Input Current, per Pin                                                                                                                                     | l <sub>in</sub>                            | ±10                            | mA   |

| DC Output Current, per Pin                                                                                                                                    | l <sub>out</sub>                           | ±20                            | mA   |

| DC Supply Current, $V_{pos}$ and Gnd Pins                                                                                                                     | I                                          | 25                             | mA   |

| Power Dissipation, per Package                                                                                                                                | PD                                         | 100                            | mW   |

| Storage Temperature                                                                                                                                           | T <sub>stg</sub>                           | -65 to 150                     | °C   |

| Lead Temperature, 1 mm from Case for 10 Seconds                                                                                                               | т∟                                         | 260                            | °C   |

3A. MAXIMUM RATINGS (Voltages Referenced to Gnd, unless otherwise stated)

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit.

NOTES: 1. Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the limits in the Electrical Characteristics tables or Pin Descriptions section.

ESD (electrostatic discharge) immunity meets Human Body Model (HBM) up to 2000 V. Additional ESD data available upon request.

eescale Semiconductor, Inc DCHIV/F INFORMATIC

# Freescale Seminonductor, Inc.

# **3B. DC ELECTRICAL CHARACTERISTICS**

V<sub>DOS</sub> = 1.8 to 3.6 V, Voltages Referenced to Gnd, T<sub>A</sub> = -40 to 85°C, unless otherwise statedt

| Parameter                                                                                                             | Condition                                                                                                                                                                           | Symbol           | Guaranteed<br>Limit    | Unit |

|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------|------|

| Maximum Low–Level Input Voltage<br>(D <sub>in</sub> , Clk, Enb, Mode, f <sub>out</sub> /Pol′, f <sub>out</sub> /Pol)  | $f_{out}/Pol'$ and $\overline{f_{out}}/Pol$ Configured as Inputs                                                                                                                    | VIL              | 0.3 x V <sub>pos</sub> | V    |

| Minimum High–Level Input Voltage<br>(D <sub>in</sub> , Clk, Enb, Mode, f <sub>out</sub> /Pol′, f <sub>out</sub> /Pol) | $f_{out}/Pol'$ and $\overline{f_{out}}/Pol$ Configured as Inputs                                                                                                                    | VIH              | 0.7 x V <sub>pos</sub> | V    |

| Minimum Hysteresis Voltage (Clk)                                                                                      |                                                                                                                                                                                     | V <sub>Hys</sub> | 100                    | mV   |

| Maximum Low–Level Output Voltage<br>(LD, Output A, Output B)                                                          | I <sub>out</sub> = 20 μA                                                                                                                                                            | VOL              | 0.1                    | V    |

| Minimum High–Level Output Voltage<br>(LD, Output A, Output B)                                                         | I <sub>out</sub> = -20 μA                                                                                                                                                           | VOH              | V <sub>pos</sub> – 0.1 | V    |

| Minimum Low–Level Output Current<br>(LD, Output A, Output B)                                                          | V <sub>out</sub> = 0.3 V                                                                                                                                                            | IOL              | 0.7                    | mA   |

| Minimum High–Level Output Current<br>(LD, Output A, Output B)                                                         | $V_{out} = V_{pos} - 0.3 V$                                                                                                                                                         | ЮН               | -0.7                   | mA   |

| Minimum Low–Level Output Current (Output C)                                                                           | $V_{out} = 0.2 V$                                                                                                                                                                   | IOL              | 2.8                    | mA   |

| Maximum Input Leakage Current<br>(D <sub>in</sub> , Clk, Enb, Mode, f <sub>out</sub> /Pol′, f <sub>out</sub> /Pol)    | $V_{in} = V_{pos}$ or Gnd; $f_{out}$ /Pol' and $\overline{f_{out}}$ /Pol Configured as Inputs                                                                                       | l <sub>in</sub>  | ±1.0                   | μA   |

| Maximum Output Leakage Current<br>(Output B, Output C)                                                                | V <sub>out</sub> = V <sub>pos</sub> or Gnd; Output in High–Impedance<br>State                                                                                                       | loz              | ±1                     | μA   |

| Maximum ON Resistance (Output C)                                                                                      | $\begin{array}{l} 1.8 \ V \leq V_{pos} < 2.5 \ V \ Supply \\ 2.5 \ V \leq V_{pos} \leq 3.6 \ V \ Supply \end{array}$                                                                | R <sub>on</sub>  | 75<br>50               | Ω    |

| Maximum Standby Supply Current $$(V_{\mbox{pos}}$ and DAC V_{\mbox{pos}}$ Tied Together)$}$                           | $V_{in} = V_{pos}$ or Gnd; Outputs Open; Both PLLs in<br>Standby Mode; Oscillator in Standby Mode;<br>DAC1 and DAC2 Output = Zero; Keep–alive<br>Oscillator Off (Notes 1, 2, and 3) | ISTBY            | 10                     | μA   |

NOTES: 1. The total supply current drain for the keep-alive oscillator, voltage multiplier, and regulator is approximately 250 µA.

2. When the Mode pin is tied high, bit C6 must be programmed to a 0 for minimum supply current drain. Otherwise, if C6 = 1, the current drain is approximately 8 μA for a 1.8 V supply and approximately 40 μA for a 3.6 V supply. This restriction on bit C6 does not apply when the Mode pin is tied low.

To ensure minimum standby supply current drain, the voltage potential at the C<sub>mult</sub> pin must not be allowed to fall below the potential at the V<sub>pos</sub> pins. See discussion in Section 5E under C<sub>mult</sub>.

# 3C. PDout-Hi AND PDout-Lo PHASE/FREQUENCY DETECTOR CHARACTERISTICS

Nominal Output Current, Vpos = 1.8 V: PDout-Hi = 2.8 mA, PDout-Lo = 0.7 or 0.35 mA

Nominal Output Current, V<sub>pos</sub> ≥ 2.5 V: PD<sub>out</sub>-Hi = 4.4 mA, PD<sub>out</sub>-Lo = 1.1 or 0.55 mA

$Rx = 2.0 \text{ k}\Omega$ , Voltages Referenced to Gnd, Voltage Multiplier ON,  $T_A = -40 \text{ to } 85^{\circ}\text{C}$

| Parameter                                     |            | Condition                                   | Guaranteed<br>Limit               | Unit |

|-----------------------------------------------|------------|---------------------------------------------|-----------------------------------|------|

| Maximum Source Current Variation Part-to-Part | (See Note) | V <sub>out</sub> = 0.5 x V <sub>Cmult</sub> | ±14                               | %    |

| Maximum Sink-versus-Source Mismatch           | (See Note) | V <sub>out</sub> = 0.5 x V <sub>Cmult</sub> | 20                                | %    |

| Output Voltage Range                          | (See Note) | $I_{out}$ Variation $\leq 27\%$             | 0.6 to V <sub>Cmult</sub> – 0.6 V | V    |

| Maximum Three–State Leakage Current           |            | V <sub>out</sub> = 0 or V <sub>Cmult</sub>  | ±50                               | nA   |

NOTE: Percentages calculated using the following formula: (Maximum Value – Minimum Value)/Maximum Value.

# 3D. PDout' PHASE/FREQUENCY DETECTOR CHARACTERISTICS

$V_{pos}$  = 1.8 to 3.6 V, Voltages Referenced to Gnd, Voltage Multiplier ON,  $T_A$  = -40 to 85°C

| Parameter                           | Condition                                     | Guaranteed<br>Limit | Unit |

|-------------------------------------|-----------------------------------------------|---------------------|------|

| Minimum Low-Level Output Current    | V <sub>out</sub> = 0.3 V                      | 0.3                 | mA   |

| Minimum High-Level Output Current   | V <sub>out</sub> = V <sub>Cmult</sub> – 0.3 V | -0.3                | mA   |

| Maximum Three–State Leakage Current | V <sub>out</sub> = 0 or V <sub>Cmult</sub>    | ±50                 | nA   |

Treescale Semiconductor, Inc ARCHIVE INFORMATIC

# Freescale Seminondugtor, Inc.

# **3E. DAC CHARACTERISTICS**

$V_{pos}$  = 1.8 to 3.6 V, DAC  $V_{pos}$  = 1.8 to 3.6 V; T<sub>A</sub> = -40 to 85°C

| Parameter                                                 | Condition                                                                       | Guaranteed<br>Limit                   | Unit |

|-----------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------|------|

| Resolution                                                |                                                                                 | 8                                     | Bits |

| Maximum Integral Nonlinearity                             |                                                                                 | ±1                                    | LSB  |

| Maximum Offset Voltage from Gnd                           | No External Load                                                                | 1                                     | LSB  |

| Maximum Offset Voltage from DAC Vpos                      | No External Load                                                                | 2                                     | LSB  |

| Maximum Output Impedance                                  | Over Entire Output Range, Including Zero<br>Output (which is Low–power Standby) | 130                                   | kΩ   |

| Maximum Standby Current                                   | Zero Output, No External Load                                                   | (See I <sub>STBY</sub> in Section 3B) |      |

| Maximum Supply Current per DAC @ DAC $V_{\mbox{pos}}$ pin | Except with Zero Output, No External Load                                       | (DAC V <sub>pos</sub> ) / 36          | mA   |

# 3F. VOLTAGE MULTIPLIER AND KEEP-ALIVE OSCILLATOR CHARACTERISTICS

Voltages Referenced to Gnd, T<sub>A</sub> = -40 to 85°C

| Parameter                         | Condition                                                                                                                                         | Guaranteed<br>Limit          | Unit |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|

| Voltage Multiplier Output Voltage | 5 MHz Refresh Rate, 100 $\mu$ A Continuous<br>Sourcing, Measured at C <sub>mult</sub> pin<br>V <sub>pos</sub> = 1.8 V<br>V <sub>pos</sub> = 3.6 V | 3.32 to 3.78<br>4.75 to 5.35 | v    |

| Keep-alive Refresh Frequency      | V <sub>pos</sub> = 1.8 to 3.6 V                                                                                                                   | 300 to 700                   | kHz  |

# **3G. DYNAMIC CHARACTERISTICS OF DIGITAL PINS**

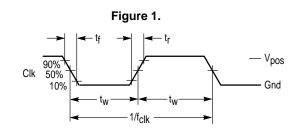

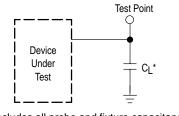

$V_{\text{DOS}}$  = 1.8 to 3.6 V,  $T_{\text{A}}$  = –40 to 85°C, Input  $t_{\text{f}}$  =  $t_{\text{f}}$  = 10 ns,  $C_{\text{L}}$  = 25 pF

| Parameter                                                                          | Figure<br>No. | Symbol                                                                                                                          | Guaranteed<br>Limit | Unit   |

|------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------|--------|

| Serial Data Clk Frequency<br>NOTE: Refer to Clk t <sub>w</sub> Below               | 1             | <sup>f</sup> clk                                                                                                                | dc to 10            | MHz    |

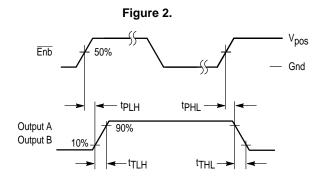

| Maximum Propagation Delay, Enb to Output A (Selected as General–Purpose Output)    | 2, 7          | <sup>t</sup> PLH <sup>, t</sup> PHL                                                                                             | 200                 | ns     |

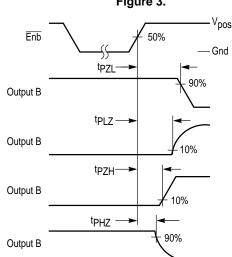

| Maximum Propagation Delay, Enb to Output B                                         | 2, 3, 7, 8    | <sup>t</sup> PLH <sup>, t</sup> PHL <sup>,</sup><br>tPZL <sup>, t</sup> PLZ <sup>,</sup><br><sup>t</sup> PZH <sup>, t</sup> PHZ | 200                 | ns     |

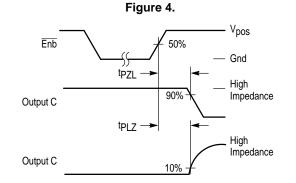

| Maximum Propagation Delay, Enb to Output C                                         | 4, 8          | tPZL, tPLZ                                                                                                                      | 200                 | ns     |

| Maximum Output Transition Time, Output A; Output B with Active Pullup and Pulldown | 2, 7          | ttlh, tthl                                                                                                                      | 75                  | ns     |

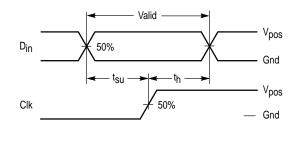

| Minimum Setup and Hold Times, Din versus Clk                                       | 5             | t <sub>su</sub> , t <sub>h</sub>                                                                                                | 30                  | ns     |

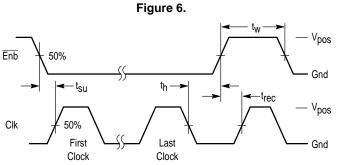

| Minimum Setup, Hold, and Recovery Times, Enb versus Clk                            | 6             | t <sub>su</sub> , t <sub>h</sub> , t <sub>rec</sub>                                                                             | 100                 | ns     |

| Minimum Pulse Width, Inactive (High) Time, Enb                                     | 6             | t <sub>W</sub>                                                                                                                  | *                   | cycles |

| Minimum Pulse Width, Clk                                                           | 1             | t <sub>W</sub>                                                                                                                  | 50                  | ns     |

| Maximum Input Capacitance — Din, CLK, Enb                                          |               | C <sub>in</sub>                                                                                                                 | 10                  | pF     |

\*For Hr register access, the minimum limit is 20 Osce cycles.

For Hn' register access, the minimum limit is 27  $f_{\mbox{in}\,}{}^\prime$  cycles.

For N register access, the minimum limit is 20  $\mbox{Osc}_{e}$  cycles + 99  $\mbox{f}_{in}$  cycles.

When the timer is used for adapt, the minimum limit after the second N register access and before the next register access is the time-out interval + 99 fin cycles.

Freescale Seminonductor, Inc.

\* Includes all probe and fixture capacitance.

Figure 8. Source current and limit voltage to Vpos for tpLz and tpzL. Sink current and limit voltage to Gnd Test Point for tPHZ and tPZH. Ø 250 µA Device Under  $C_{L^{*}}$ Test

\* Includes all probe and fixture capacitance.

Semiconductor, Inc

Freescale

# Freescale Serinondrytor, Inc.

# 3H. DYNAMIC CHARACTERISTICS OF LOOP AND fout PINS

$V_{DOS} = 1.8$  to 3.6 V,  $T_A = -40$  to  $85^{\circ}C$

| Symbol            | Parameter                                                                                                                           | Condition                                                                                                                                                                                                                                                                        | Figure<br>No. | Min                      | Max                      | Unit |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------|--------------------------|------|

| vin               | Input Voltage Range, f <sub>in</sub>                                                                                                | $\begin{array}{l} \mbox{MC145225:} \\ 100\ \mbox{MHz} \leq f_{in} < 400\ \mbox{MHz} \\ 400\ \mbox{MHz} \leq f_{in} \leq 1.2\ \mbox{GHz} \\ \mbox{MC145230:} \\ 500\ \mbox{MHz} \leq f_{in} < 800\ \mbox{MHz} \\ 800\ \mbox{MHz} \leq f_{in} \leq 2.2\ \mbox{GHz} \\ \end{array}$ | 9             | 300<br>100<br>200<br>100 | 600<br>500<br>600<br>500 | mVpp |

| vin′              | Input Voltage Range, f <sub>in</sub> '                                                                                              | 50 MHz ≤ f <sub>in</sub> < 150 MHz<br>150 MHz ≤ f <sub>in</sub> ≤ 550 MHz                                                                                                                                                                                                        | 10            | 400<br>175               | 600<br>600               | mVpp |

| fOsce             | Input Frequency Range, Osc <sub>e</sub>                                                                                             | v <sub>in</sub> = 350 to 600 mVpp,<br>Device in External Reference Mode                                                                                                                                                                                                          | 11            | 9                        | 80                       | MHz  |

| <sup>f</sup> Xtal | Crystal Frequency, Osc <sub>b</sub> and Osc <sub>e</sub>                                                                            | Device in Crystal Mode                                                                                                                                                                                                                                                           | *             | 9                        | 80                       | MHz  |

| C <sub>in</sub>   | Input Capacitance of Pins Osc <sub>b</sub> and Osc <sub>e</sub>                                                                     |                                                                                                                                                                                                                                                                                  |               | _                        | _                        | pF   |

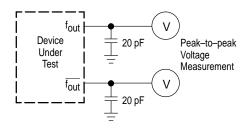

| fout              | Output Frequency Range, $f_{out}$ and $\overline{f_{out}}$                                                                          | Output Signal Swing > 300 mVpp per<br>pin (600 mVpp differential)                                                                                                                                                                                                                | 12            | 1                        | 6.2                      | MHz  |

| $f_{\varphi}$     | Operating Frequency Range of the<br>Phase/Frequency Detectors, PD <sub>out</sub> –Hi,<br>PD <sub>out</sub> –Lo, PD <sub>out</sub> ′ |                                                                                                                                                                                                                                                                                  |               | dc                       | 600                      | kHz  |

\* Refer to the Crystal Oscillator Considerations section.

Figure 9.

Figure 10.

Figure 12.

# Freescale Seminonductor, Inc.

# 4. DEVICE OVERVIEW

Refer to the Block Diagram in Section 1.

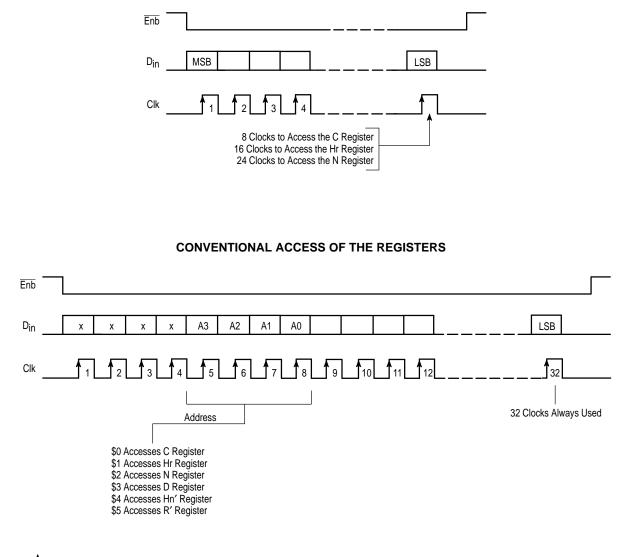

# 4A. SERIAL INTERFACE AND REGISTERS

The serial interface is comprised of a Clock pin (Clk), a Data In pin ( $D_{in}$ ), and an Enable pin (Enb). Information on the data input pin is shifted into a shift register on the low-to-high transition of the serial clock. The data format is most significant bit (MSB) first. Both Clk and Enb are Schmitt-triggered inputs.

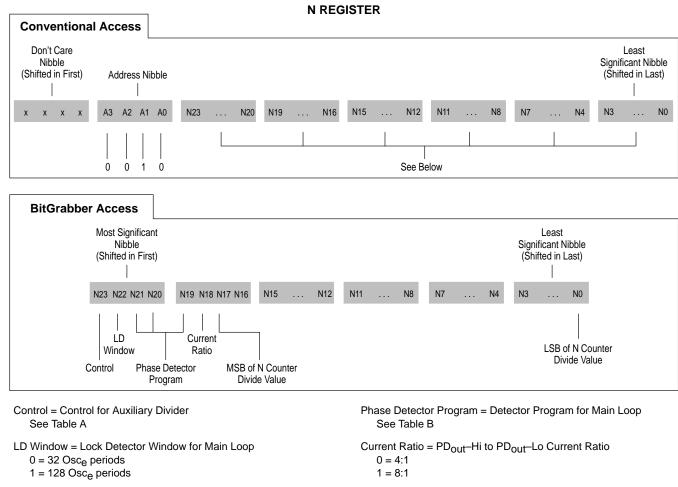

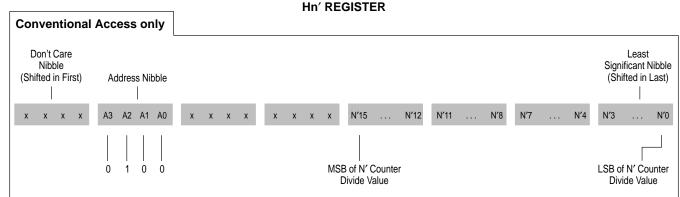

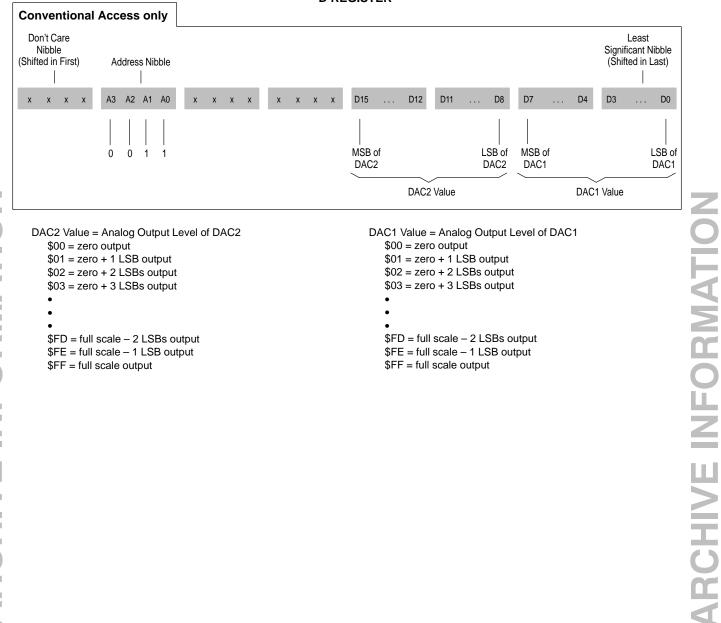

The R and N registers contain counter divide ratios for the main loop, PLL. The R' and N' registers contain counter divide ratios for the secondary loop, PLL'. Additional contol bits are located in the R', N, and C registers. The D register controls the digital–to–analog converters (DACs). Random access is allowed to the N, R', Hr, Hn', D, and C registers.

Two 16-bit holding registers, Hr and Hn', feed registers R and N', respectively. The R and N' registers determine the divide ratios of the R and N' counters, respectively. Thus, the information presented to the R and N' counters is double-buffered. Using the proper programming sequence, new divide ratios may be presented to the N, R, and N' counters; simultaneously.

Enb is used to activate the data port and allow transfer of data. To ensure that data is accepted by the device, the Enb signal line must initially be a high voltage (not asserted), then make a transition to a low voltage (asserted) prior to the occurrence of a serial clock, and must remain asserted until after the last serial clock of the burst. Serial data may be transferred in an SPI format (while Enb remains asserted). Data is transferred to the appropriate register on the rising edge of Enb (see Table 1). "Short shifting", depicted as BitGrabber™ in the table, allows access to certain registers without requiring address bits. When Enb is inactive (high), Clk is inhibited from shifting the shift register.

The serial input pins may NOT be driven above the supply voltage applied to the  $V_{\text{DOS}}$  pins.

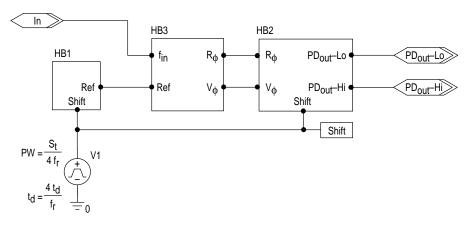

## 4B. REFERENCE INPUT AND COUNTERS CIRCUITS

## **Reference (Oscillator) Circuit**

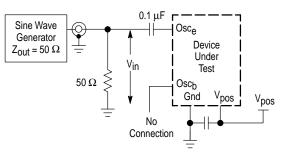

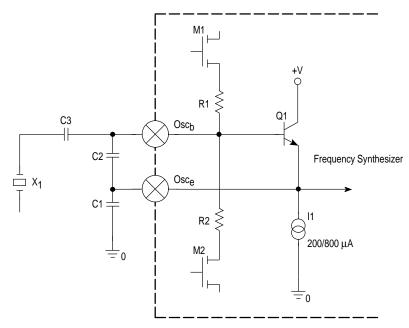

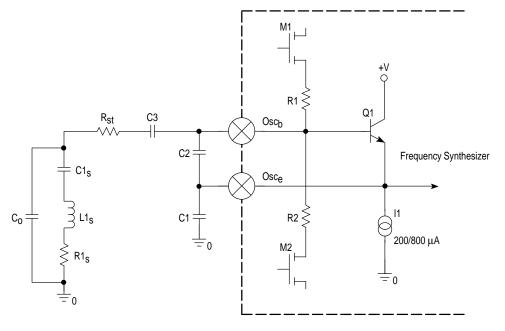

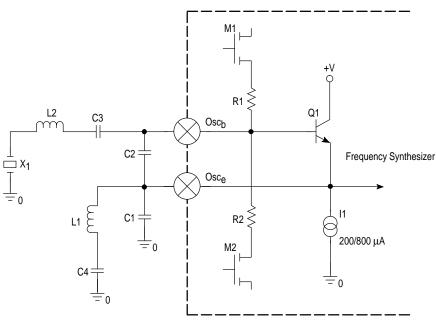

For the Colpitts reference oscillator, one pin ties to the base (Osc<sub>b</sub>, pin 32) and the other ties to the emitter (Osc<sub>e</sub>, pin 1), of an on-chip NPN transistor. In addition, the reference circuit may be operated in the external reference (XRef) mode as selectable via bit C6 when the Mode pin is high.

The  $Osc_b$  and  $Osc_e$  pins support an external fundamental or overtone crystal. The output of the oscillator is routed to both the reference counter for the main loop (R counter) and the reference counter for the secondary loop (R' counter).

In a second mode, determined by bit C6 being 1 and the Mode pin being high,  $Osc_e$  is an input which accepts an ac-coupled signal from a TCXO or other source.  $Osc_b$  must be floated. If the Mode pin is low, this "XRef mode" is not allowed.

## **Reference Counter for Main Loop**

Main reference counter R divides down the frequency at Osce and feeds the phase/frequency detector for the main

loop. The detector feeds the two charge pumps with outputs  $PD_{out}$ -Hi and  $PD_{out}$ -Lo. The division ratio of the R counter is determined by bits in the R register.

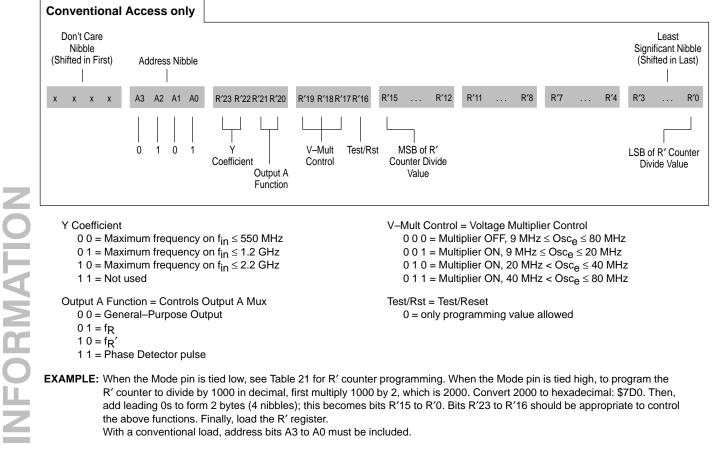

## **Reference Counter for Secondary Loop**

Secondary reference counter R' divides down the frequency at  $Osc_e$  and feeds the phase/frequency detector for the secondary loop. The detector output is  $PD_{out}$ '. The division ratio of the R' counter is determined by the 16 LSBs of the R' register.

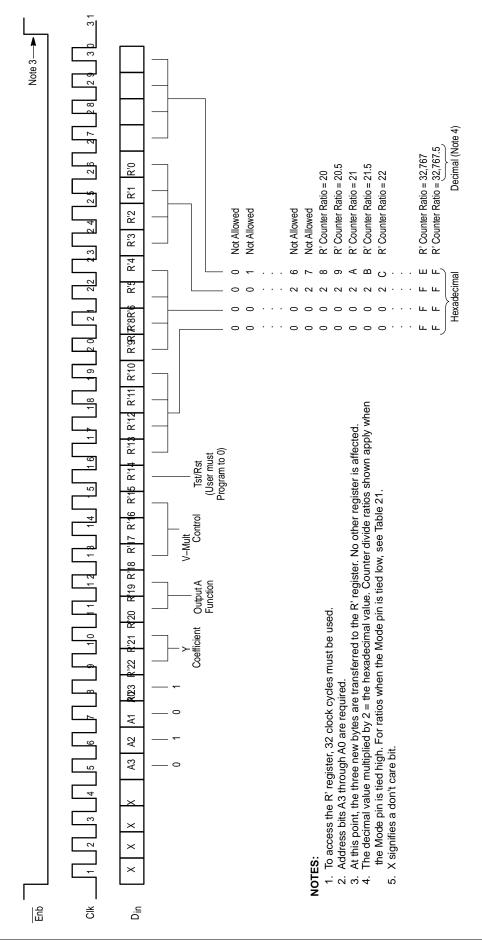

The R' counter has a special mode to provide a frequency output at pins  $f_{out}$  and  $\overline{f_{out}}$  (differential outputs). These are low–jitter ECL–type outputs. With the Mode pin low, software control allows the Osc<sub>e</sub> frequency to be divided–by–8, –10, or –12.5 and routed to the  $f_{out}$  pins. This output is derived by tapping off of a front–end stage of the R' counter and feeding the auxiliary counter which provides the divided–down frequency. The chip must have the Mode pin low, which activates the  $f_{out}$  pins. The actual R' divide ratio must be divisible by 2 or 2.5 when the  $f_{out}$  pins are activated. There is no such restriction when the Mode pin is high. See Section 6D, **R' Register.**

## 4C. LOOP DIVIDER INPUTS AND COUNTER CIRCUITS

#### fin Inputs and Counter Circuit

$f_{in}$  and  $\overline{f_{in}}$  are high–frequency inputs to the amplifier which feeds the N counter. A small signal can feed these inputs either differentially or single–ended.

The N counter divides down the external VCO frequency for the main loop. (The divide ratio of the N counter is also known as the loop multiplying factor.) The divide ratio of this counter is determined by the 18 LSBs of the N register. The output of the N counter feeds the phase/frequency detector for the main loop.

## fin' Input and Counter Circuit

$f_{in}$ ' is the high-frequency input to the amplifier which feeds the N' counter. A small signal can feed this input single-ended.

The N' counter divides down the external VCO frequency for the secondary loop. (The divide ratio of the N' counter is also known as the loop multiplying factor.) The divide ratio of this counter is determined by bits in the N' register. The output of the N' counter feeds the phase/frequency detector for the secondary loop.

## 4D. VOLTAGE MULTIPLIER AND KEEP-ALIVE CIRCUITS

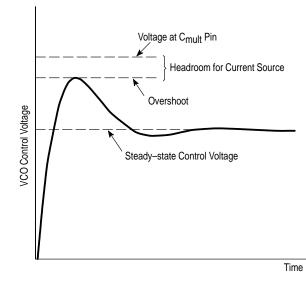

The voltage multiplier produces approximately two times the voltage present at the V<sub>pos</sub> pins over a supply range of 1.8 V to about 2.5 V. With a supply range of approximately 2.5 V to 3.6 V, the elevated voltage is regulated/limited to approximately 5 V. The elevated voltage, present at the C<sub>mult</sub> pin, is applied to both phase detectors. An external capacitor to Gnd is required on the C<sub>mult</sub> pin. The other capacitors required for the multiplier are on–chip.

A capacitor to Gnd is also required on the  $C_{reg}$  pin. The voltage on this pin is equal to the voltage on the  $V_{pos}$  pins over a supply range of 1.8 V to about 2.5 V. The voltage on

emiconductor, I

eescale

# Freescale Seminondyntor, Inc.

$C_{\text{reg}}$  is limited to approximately 2.5 V maximum when the  $V_{\text{pos}}$  pins exceed 2.5 V.

The refresh rate determines the repetition rate that the capacitors for the voltage multiplier are charged. Refresh is normally derived off of the signal present at the  $Osc_e$  pin, through a divider which is part of the voltage multiplier and regulator circuitry. The refresh rate is controlled via bits in the R' register.

When the reference oscillator circuit is placed in standby, an on-chip keep-alive oscillator assists in maintaining the elevated voltage on the phase detectors. The keep-alive refresh rate is per the spec table in Section 3F.

If desired, the keep–alive oscillator can be inhibited from turning on, by placing the multiplier in the inactive state via R' register bits. This causes the phase/frequency detector voltage to bleed off while in standby, but has the advantage of achieving the lowest supply current if all other sections of the chip are shut down.

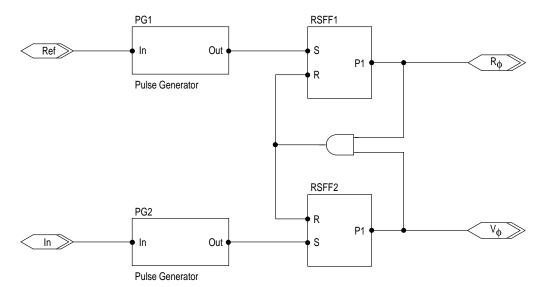

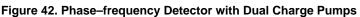

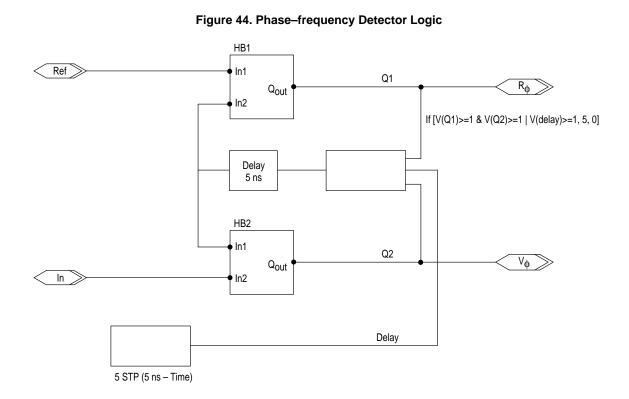

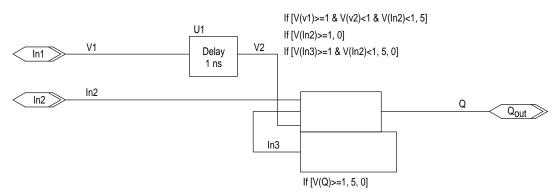

# 4E. PHASE/FREQUENCY DETECTORS

#### **Detector for Main Loop**

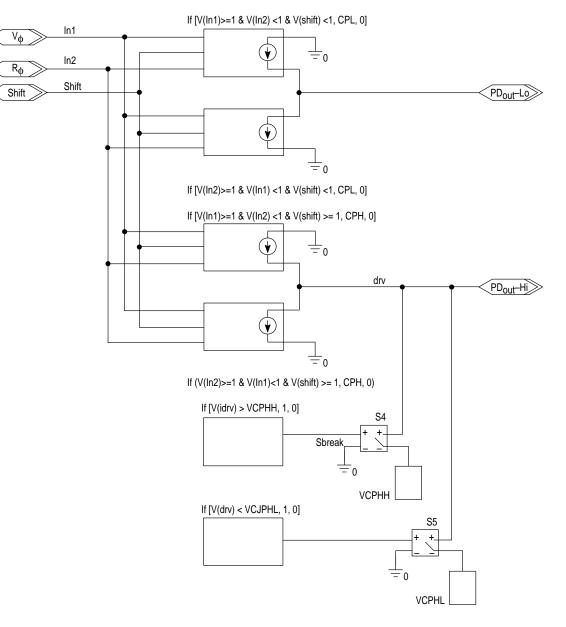

The detector for the main loop senses the phase and frequency difference between the outputs of the R and N counters. The detector feeds both a high–current charge pump with output  $PD_{out}$ –Hi and a low–current charge pump with output  $PD_{out}$ –Lo.

The charge pumps can be operated in three conventional manners as controlled by bits in the N register.  $PD_{out}$ -Lo can be enabled with  $PD_{out}$ -Hi inhibited. Conversely,  $PD_{out}$ -Hi can be enabled with  $PD_{out}$ -Lo inhibited. Both outputs can be enabled and tied together externally for maximum charge pump current. Finally, both outputs can be inhibited. In this last case, they float. The outputs can also be forced to the floating state by a bit in the C register. This facilitates introduction of modulation into the VCO input.

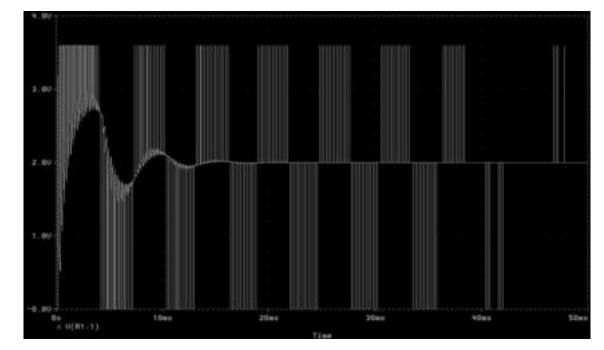

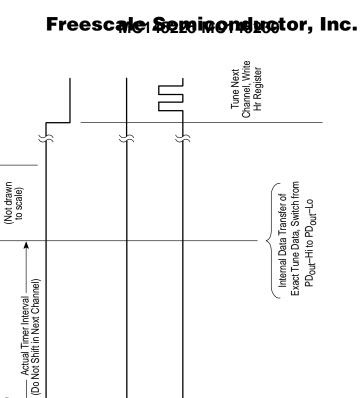

The charge pumps can be operated in an adapt mode as controlled by bits in the N register. The bits essentially program a timer which determines how long  $PD_{out}$ -Hi is active. After the time-out,  $PD_{out}$ -Hi floats and  $PD_{out}$ -Lo becomes active. In addition, a second set of R and N counter values can be engaged after the time-out. For more information, see Table 16 and Section 8, **Programmer's Guide**.

## **Detector for Secondary Loop**

The detector for the secondary loop senses the phase and frequency difference between the outputs of the R' and N'  $\,$

counters. Detector output PD<sub>out</sub>' is a voltage-type output with a three-state push-pull driver.

The output can be forced to the floating state by a bit in the C register. This facilitates introduction of modulation into the VCO input.

## 4F. LOCK DETECTORS

Window counters in each of the lock detector circuits determine the lock detector phase threshold for PLL and PLL'. The window counter divide ratio for the main loop's lock detector is controlled via a bit in the N register. The window counter divide ratio for the secondary loop is not controllable by the user.

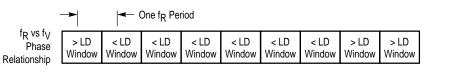

The lock detector window determines a minimum phase difference which must occur before the Lock Detect pin goes high. Note that the lock detect signals for each loop drive an AND gate, which then feeds the LD pin. The LD pin indicates the condition of both loops, or the one active loop if the other is in standby. If both loops are in standby, LD is low indicating unlocked.

## 4G. DACs

The two independent 8-bit DACs facilitate crystal oscillator trimming and PA output power control. They are also suitable for any general-purpose use.

Each DAC utilizes an R–2R ladder architecture. The output pins, DAC1 and DAC2, are directly connected to the ladder; that is, there is no on–chip buffer.

The DAC outputs are determined by the contents of the D register. When a DAC output is zero scale, it is also in a low-power mode. The power-on reset (POR) circuit initializes the DACs in the low-power mode upon power up.

## 4H. GENERAL-PURPOSE OUTPUTS

There are three outputs which may be used as port expanders for a microcontroller unit (MCU).

Output A is actually a multi-purpose output with a push-pull output driver. See Table 2 for details.

Output B is a three–state output. The state of Output B depends on two bits; one of these bits also controls whether the main PLL is in standby or not. See Table 5 for details.

Output C is an open–drain output. The state of this output is controlled by one bit per Table 4. Output C is specified with a guaranteed ON resistance, and thus, may be used in an analog fashion.

# Freescale Seminondyntor, Inc.

# 5. PIN DESCRIPTIONS

## 5A. DIGITAL PINS

# Enb, D<sub>in</sub>, and Clk

# Pins 5, 6, and 7 — Serial Data Port Inputs

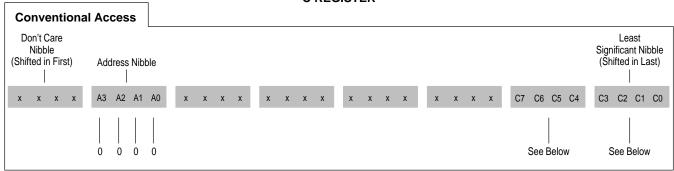

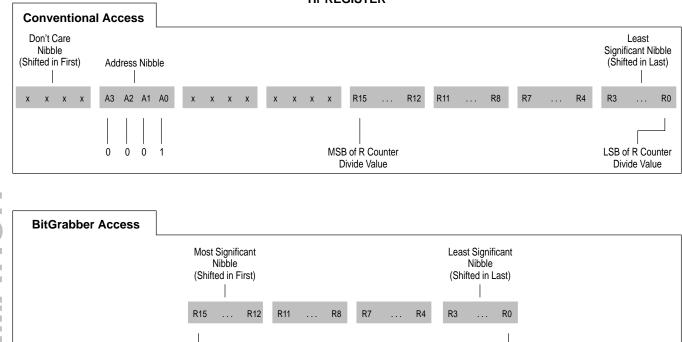

The Enb input is used to activate the serial interface to allow the transfer of data to the device. To transfer data to the device, the Enb pin must be low during the interval that the data is being clocked in. When Enb is taken back high (inactive), data is transferred to the appropriate register depending either on the data stream length or address bits. The C, Hr, and N registers can be accessed using either a unique data stream length (BitGrabber) or by using address bits (Conventional). The D, Hn', and R' registers can only be accessed using address bits. See Table 1.

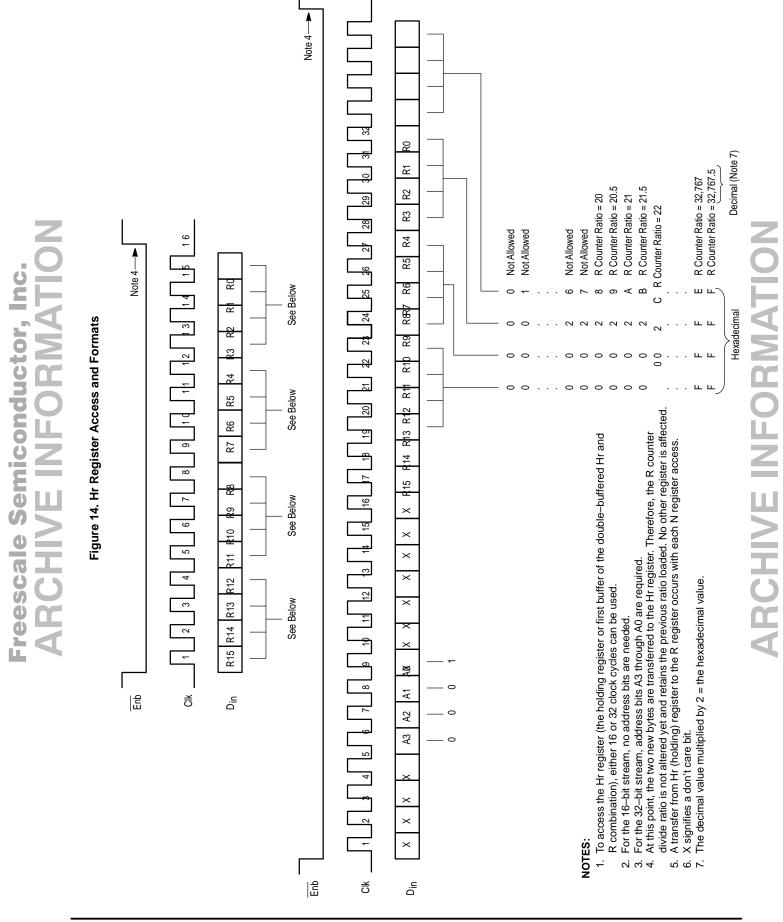

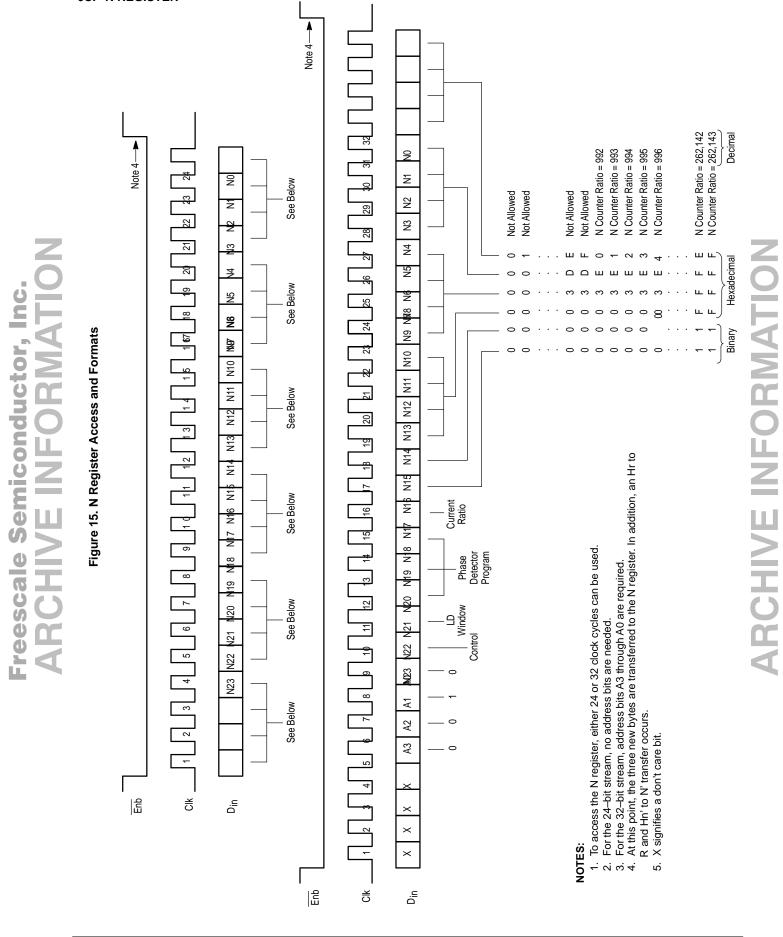

The bit stream begins with the MSB and is shifted in on the low-to-high transition of Clk. The bit pattern is 1 byte (8 bits) long to access the C register, 2 bytes (16 bits) to access the Hr register, or 3 bytes (24 bits) to access the N register. A bit pattern of 4 bytes (32 bits) is used to access the registers when using address bits. The device has double buffers for storage of the N' and R counter divide ratios. One double buffer is composed of the Hr register which feeds the R register. An Hr to R register transfer occurs whenever the N register is written. The other double buffer is the Hn' register which feeds the N' register. An Hr to N' register. An Hr' to N' register transfer occurs whenever the N register is written. The N register is written. Thus, new divide ratios may be presented to the R, N', and N counters simultaneously.

Transitions on  $\overline{\text{Enb}}$  must not be attempted while Clk is high. This puts the device out of synchronization with the microcontroller. Resynchronization occurs whenever  $\overline{\text{Enb}}$  is high (inactive) and Clk is low.

Data is retained in the registers over a supply range of 1.8 to 3.6 V. The bit-stream formats are shown in Figures 13 through 18.

# LD

# Pin 8 — Lock Detectors Output

This signal is the logical AND of the lock detect signals from both PLL and PLL'. For the main PLL, the phase window that defines "lock" is programmable via bit N22. The phase window for the secondary PLL' is not programmable.

If either PLL or PLL' is in standby, LD indicates the lock condition of the active loop only. If both loops are in standby, the LD output is a static low level.

Each PLL's lock detector is in the high state when the respective loop is locked (the inputs to the phase detector being the same phase and frequency). The lock detect signal is in the low state when a loop is out of lock. See Figure 19.

Upon power up, the LD pin indicates a *not locked* condition. The LD pin is a push-pull CMOS output. If unused, LD should be left open.

# Output A

## Pin 9 — Multiple–Purpose Digital Output

Depending on control bits R'21 and R'20, Output A is selectable by the user as a general–purpose output (either high or low level),  $f_R$  (output of main reference counter),  $f_R'$  (output of secondary reference counter), or a phase detector pulse indicator for both loops. When selected as general–purpose output, bit C7 determines whether the output is a high or low level per Table 2. When configured as  $f_R$ ,  $f_R'$ , or phase detector pulse, Output A appears as a normally low signal and pulses high.

Output A is a slew-rate limited CMOS totem-pole output. If unused, Output A should be left open.

| Access<br>Type | Accessed<br>Register | Address<br>Nibble | Number<br>of<br>Clocks | Register Bit<br>Nomenclature | Figure<br>No. |

|----------------|----------------------|-------------------|------------------------|------------------------------|---------------|

| BitGrabber     | С                    | _                 | 8                      | C7, C6, C5,, C0              | 13            |

| BitGrabber     | Hr                   | _                 | 16                     | R15, R14, R13,, R0           | 14            |

| BitGrabber     | N                    | _                 | 24                     | N23, N22, N21,, N0           | 15            |

| Conventional   | С                    | \$0               | 32                     | C7, C6, C5,, C0              | 13            |

| Conventional   | Hr                   | \$1               | 32                     | R15, R14, R13,, R0           | 14            |

| Conventional   | N                    | \$2               | 32                     | N23, N22, N21,, N0           | 15            |

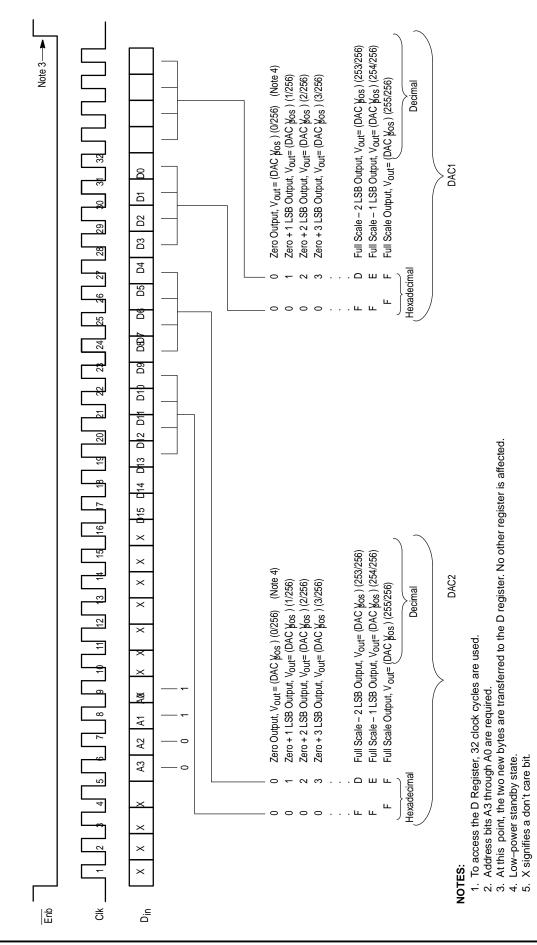

| Conventional   | D                    | \$3               | 32                     | D15, D14, D13,, D0           | 18            |

| Conventional   | R′                   | \$5               | 32                     | R'23, R'22, R'21,, R'0       | 16            |

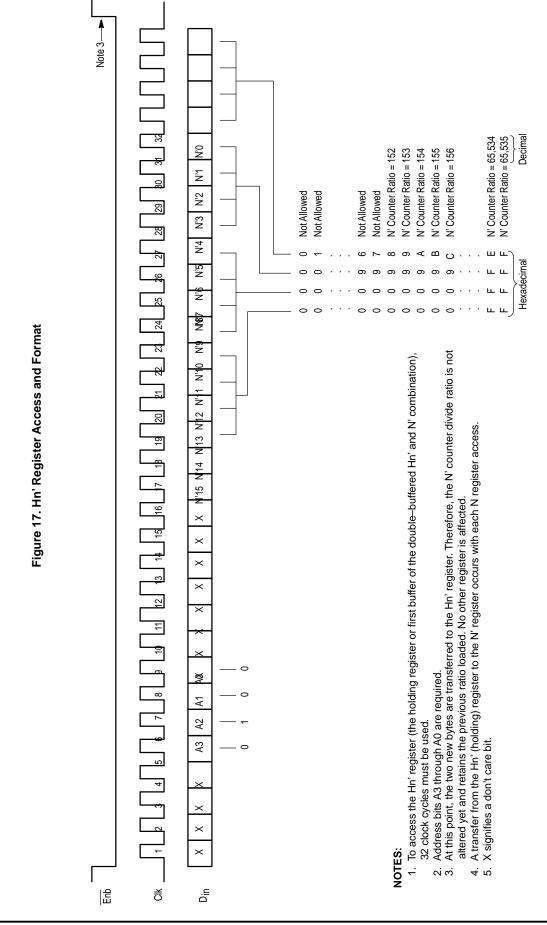

| Conventional   | Hn′                  | \$4               | 32                     | N'15, N'14, N'13,, N'0       | 17            |

Table 1. Register Access (LSBs are C0, R0, N0, D0, R'0, and N'0)

NOTE: \$0 denotes hexadecimal zero, \$1 denotes hexadecimal one, etc.

# Freescale Seminondugtor, Inc.

| Table 2. Output A Configuration |             |           |                                       |  |  |  |

|---------------------------------|-------------|-----------|---------------------------------------|--|--|--|

| Bit<br>R′21                     | Bit<br>R′20 | Bit<br>C7 | Function of Output A                  |  |  |  |

| 0                               | 0           | 0         | General–Purpose Output,<br>Low Level  |  |  |  |

| 0                               | 0           | 1         | General–Purpose Output,<br>High Level |  |  |  |

| 0                               | 1           | х         | fR                                    |  |  |  |

| 1                               | 0           | х         | fR'                                   |  |  |  |

| 1                               | 1           | х         | Phase Detector Pulse<br>Indicator     |  |  |  |

#### Table 2. Output A Configuration

# Mode

emiconductor, In

eescale S

## Pin 10 — Mode Input

When the Mode pin is tied low (approximately Gnd), the pair of pins named  $f_{out}$ /Pol' and  $\overline{f_{out}}$ /Pol become outputs  $f_{out}$  and  $\overline{f_{out}}$ . As such, these pins are the divided down reference frequency. The division ratio is controlled by bits per Table 6. In addition, when Mode is low, the R' counter is preceded by a fixed–divide prescaler. Also, only a crystal may be used at pins Osc<sub>b</sub> and Osc<sub>e</sub>; an external reference, such as a TCXO, should not be used to drive either pin. The default on the phase detector polarity is positive. See the summary in Table 3.

When the Mode pin is tied high (approximately  $V_{pOS}$ ), the pair of pins named  $f_{Out}$ /Pol' and  $\overline{f_{Out}}$ /Pol become inputs Pol' and Pol. As such, these pins control the polarity of the phase/frequency detectors for PLL' and PLL, respectively. In addition, when Mode is high, the R' counter is preceded by a dual-modulus prescaler. Therefore, the R' counter is completely programmable per Figure 16. Also, either a crystal or TCXO may be used with the device. See the summary in Table 3.

Table 3. Mode Pin Summary

| Attribute                  | Mode Pin = Low Level                                                             | Mode Pin = High Level                                                          |

|----------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| f <sub>out</sub> /Pol′ pin | Pin is f <sub>out</sub> output;<br>polarity of phase<br>detector' is positive    | Pin is Pol' input and<br>controls polarity of<br>phase detector'               |

| f <sub>out</sub> /Pol pin  | Pin is $\overline{f_{Out}}$ output;<br>polarity of phase<br>detector is positive | Pin is Pol input and<br>controls polarity of<br>phase detector                 |

| Oscillator<br>circuit      | Supports a crystal only                                                          | Supports crystal or<br>accommodates TCXO                                       |

| R' counter                 | Programmable in increments of 2 or 2.5                                           | Programmable in increments of 0.5                                              |

| Output B<br>pin            | State of pin controlled by Bit C6                                                | Pin not used, Bit C6<br>controls whether<br>crystal or TCXO is<br>accommodated |

# **Output C**

# Pin 16 — General–Purpose Digital Output

This pin is controllable by bit C5 as either low level or high impedance per Table 4.

The output driver is an open–drain N–channel MOSFET connected to Gnd. The ESD (electrostatic discharge) protection circuit for this pin is tied to Gnd and V<sub>DOS</sub>. Thus,

voltages above  $V_{\text{POS}}$  are clipped at approximately 0.7 V above  $V_{\text{POS}}$ . If unused, Output C should be left open.

| Table 4  | Output ( | - Drogram | mina |

|----------|----------|-----------|------|

| Table 4. | Output   | C Program | mmg  |

| Bit C5 | State of Output C Pin                                |

|--------|------------------------------------------------------|

| 0      | Low level<br>(ON resistance per<br>Electrical Table) |

| 1      | High impedance<br>(leakage per Electrical Table)     |

# Output B

# Pin 25 — General-Purpose Digital Output

This pin is controllable by bits C6 and C1 as either low level, high level, or high impedance per Table 5. Note that whenever the main PLL is placed in standby by bit C1, Output B is forced to high impedance. The three–state MOSFET output is slew–rate limited. If unused, Output B should be left open.

## Table 5. Output B Programming

| Bit C6 | Bit C1 | State of<br>Output B Pin | Condition of<br>Main PLL |

|--------|--------|--------------------------|--------------------------|

| 0      | 0      | Low level                | Active                   |

| 0      | 1      | High impedance*          | Standby*                 |

| 1      | 0      | High level               | Active                   |

| 1      | 1      | High impedance           | Standby                  |

|        |        |                          |                          |

\*Power–up default.

Tables 7 and 8.

## f<sub>out</sub>/Pol′ and f<sub>out</sub>/Pol Pins 28 and 27 — Dual–purpose Outputs/Inputs

# These pins are outputs when the Mode pin is low and

inputs when the Mode pin is high. When the Mode pin is low, these pins are small–signal differential outputs  $f_{OUt}$  and  $\overline{f_{OUt}}$  with a frequency derived from the signal present at the Osc<sub>e</sub> pin. The frequency of the output signal is per Table 6. If this function is not needed, the Mode pin should be tied high, which minimizes supply current. In this case, these inputs must be tied high or low per

## Table 6. $f_{out}$ and $\overline{f_{out}}$ Frequency (Mode Pin = Low)

| Bit N23 | Bit R'1 | Bit R'0 | Output Frequency                 |

|---------|---------|---------|----------------------------------|

| 0       | 0       | 0       | Osc <sub>e</sub> divided by 10   |

| 0       | 0       | 1       | Osce divided by 12.5             |

| 0       | 1       | 0       | Osce divided by 12.5             |

| 0       | 1       | 1       | Osc <sub>e</sub> divided by 12.5 |

| 1       | 0       | 0       | Osc <sub>e</sub> divided by 8    |

| 1       | 0       | 1       | Osc <sub>e</sub> divided by 10   |

| 1       | 1       | 0       | Osc <sub>e</sub> divided by 10   |

| 1       | 1       | 1       | Osc <sub>e</sub> divided by 10   |

RMATI

emiconductor, Ind

0

Ŭ

When the Mode pin is high, these pins are digital inputs Pol' and Pol which control the polarity of the phase/frequency detectors. See Tables 7 and 8. Positive polarity is used when an increase in an external VCO control voltage input causes an increase in VCO output frequency. Negative polarity is used when a decrease in an external VCO control voltage input causes an increase an increase in XCO output frequency.

| Table 7. I | Main Phase/Frequer | ncy Detector Polarity |

|------------|--------------------|-----------------------|

|            | (Mode Pin =        | High)                 |

| (        |         |                                                                             |  |

|----------|---------|-----------------------------------------------------------------------------|--|

| Mode Pin | Pol Pin | Main Detector Polarity<br>(PD <sub>out</sub> –Lo and PD <sub>out</sub> –Hi) |  |

| High     | Low     | Positive                                                                    |  |

| High     | High    | Negative                                                                    |  |

| Low      | *       | Positive                                                                    |  |

\*Pin configured as an output; should not be driven.

| Table 8. Secondary Phase/Frequency |  |  |

|------------------------------------|--|--|

| Detector Polarity                  |  |  |

| (Mode Pin = High)                  |  |  |

| Mode Pin | Pol′ Pin | Secondary Detector<br>Polarity<br>(PD <sub>out</sub> ') |

|----------|----------|---------------------------------------------------------|

| High     | Low      | Positive                                                |

| High     | High     | Negative                                                |

| Low      | *        | Positive                                                |

\*Pin configured as an output; should not be driven.

# 5B. REFERENCE PINS

Osce and Oscb

#### Pins 1 and 32 — Reference Oscillator Transistor Emitter and Base

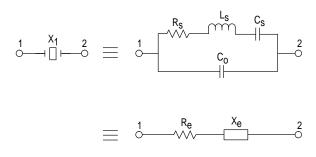

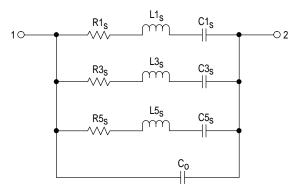

These pins can be configured to support an external crystal in a Colpitts oscillator configuration. The required connections for the crystal circuit are shown in the **Crystal Oscillator Considerations** section.

Additionally, the pins can be configured to accept an external reference frequency source, such as a TCXO. In this case, the reference signal is ac coupled into  $Osc_e$  and the  $Osc_b$  pin is left floating. See Figure 11.

Bit C6 and the Mode input pin control the configuration of these pins per Table 9.

|   | Table S | . Reference | Conti | guration |

|---|---------|-------------|-------|----------|

| 1 |         |             |       |          |

| Mode<br>Input<br>Pin | Bit C6 | Reference<br>Configuration     | Comment                         |

|----------------------|--------|--------------------------------|---------------------------------|

| Low                  | х      | Supports Crystal<br>(default)  | C6 used to control<br>Output B* |

| High                 | 0      | Supports Crystal               | Output B not useful             |

| High                 | 1      | Requires External<br>Reference | Output B not useful             |

\*See Table 5.

5C. LOOP PINS

fin and fin

## Pins 12 and 13 — Frequency Input for Main Loop (PLL)

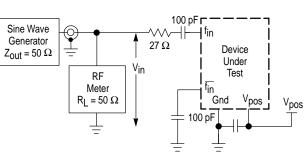

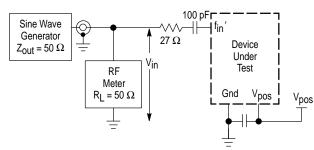

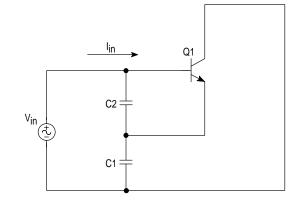

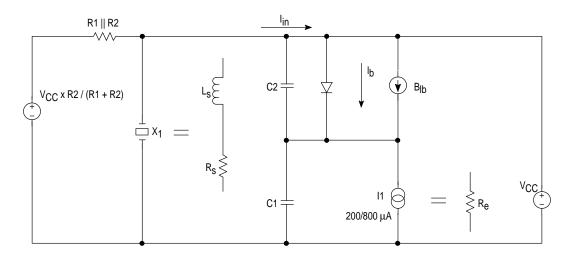

These pins feed the on-chip RF amplifier which drives the high-speed N counter. This input may be fed differentially. However, it is usually used in a single-ended configuration with  $f_{in}$  driven while  $\overline{f_{in}}$  is tied to a good RF ground (via a capacitor). The signal source driving this input must be ac coupled and originates from an external VCO.

The sensitivity of the RF amplifier is dependent on frequency as shown in the Loop Specifications table. Sensitivity of the f<sub>in</sub> input is specified as a level across a 50  $\Omega$  load driven by a 50  $\Omega$  source. A VCO that can drive a load within the data sheet limits can also drive f<sub>in</sub>. Usually, to avoid load pull and resultant frequency modulation of the VCO, f<sub>in</sub> is lightly coupled by a small value capacitor and/or a resistor. See the applications circuit of Figure 65.

# $f_{in}$

## Pin 30 — Frequency Input for Secondary Loop (PLL')

This pin feeds the on–chip RF amplifier which drives the high–speed N' counter. This input is used in a single–ended configuration. The signal source driving this input must be ac coupled and originates from an external VCO.

The sensitivity of the RF amplifier is dependent on frequency as shown in the Loop Specifications table. Sensitivity of the  $f_{in}$ ' input is specified as a level across a 50  $\Omega$  load driven by a 50  $\Omega$  source. A VCO that can drive a load within the data sheet limits can also drive  $f_{in}$ '. Usually, to avoid load pull and resultant frequency modulation of the VCO,  $f_{in}$ ' is lightly coupled by a small value capacitor and/or a resistor. See the applications circuit of Figure 65.

If the secondary loop is not used, PLL' should be placed in standby and  $f_{in}$ ' should be left open.

# PDout-Hi and PDout-Lo

# Pins 19 and 20 — Phase/Frequency Detector Outputs for Main Loop (PLL)

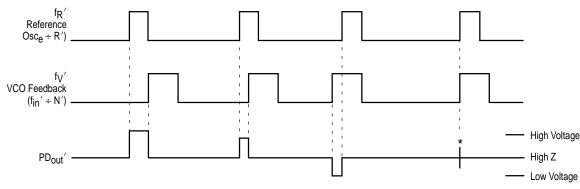

Each pin is a three-state current source/sink/float output for use as a loop error signal when combined with an external low-pass loop filter. Under bit control,  $PD_{out}$ -Lo has either one-quarter or one-eighth the output current of  $PD_{out}$ -Hi per Table 10. The detector is characterized by a linear transfer function (no dead zone). The polarity of the detector is controllable. The operation of the detector is described below and shown in Figure 20.

> Table 10. Current Ratio of PD<sub>out</sub>-Hi and PD<sub>out</sub>-Lo

| Bit<br>N18 | Output Current Ratio<br>PD <sub>out</sub> -Hi:PD <sub>out</sub> -Lo<br>(Gain Ratio) |  |

|------------|-------------------------------------------------------------------------------------|--|

| 0          | 4 : 1                                                                               |  |

| 1          | 8:1                                                                                 |  |

When the Mode pin is high, positive polarity occurs when the Pol pin is low. Also, when the Mode pin is low, polarity

eescale Semiconductor, Inc RCHIVE INFORMAT

# Freescale Seminonderstor, Inc.

defaults to positive. Positive polarity is described below. fV is the output of the main loop's VCO divider (N counter). fR is the output of the main loop's reference divider (R counter).

- (a) Frequency of  $f_V > f_R$  or phase of  $f_V$  leading  $f_R$ : current–sinking pulses from a floating state.

- (b) Frequency of  $f_V < f_R$  or phase of  $f_V$  lagging  $f_R$ : current–sourcing pulses from a floating state.

- (c) Frequency and phase of f<sub>V</sub> = f<sub>R</sub>: essentially a floating state, voltage at pin determined by loop filter.

When the Mode pin is high, negative polarity occurs when the Pol pin is high. Negative polarity is described below. fV is the output of the main loop's VCO divider (N counter). fR is the output of the main loop's reference divider (R counter).

- (a) Frequency of f<sub>V</sub> > f<sub>R</sub> or phase of f<sub>V</sub> leading f<sub>R</sub>: current–sourcing pulses from a floating state.

- (b) Frequency of f<sub>V</sub> < f<sub>R</sub> or phase of f<sub>V</sub> lagging f<sub>R</sub>: current–sinking pulses from a floating state.

- (c) Frequency and phase of  $f_V = f_R$ : essentially a floating state, voltage at pin determined by loop filter.

These outputs can be enabled and disabled by bits in the C and N registers. Placing the main PLL in standby (bit C1 = 1) forces the detector outputs to a floating state. In addition, setting the PD Float bit (bit C4 = 1) forces the detector outputs to a floating state while allowing the counters to run for the main PLL. For selection of the outputs, see Table 11.

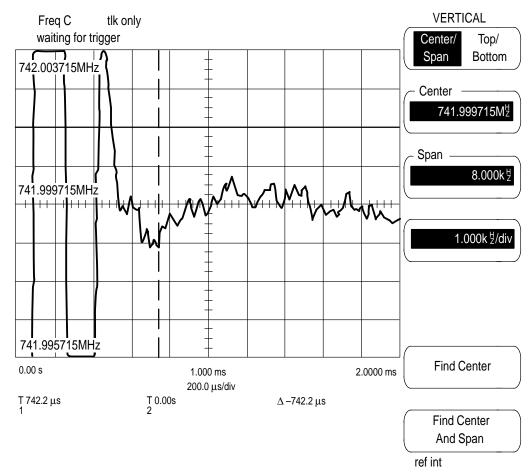

The phase detector gain (in amps per radian) =  $PD_{out}$  current (in amps) divided by  $2\pi$ .

If a detector output is not used, that pin should be left open.

**Table 11. Selection of Main Detector Outputs**

| Bit<br>N21 | Bit<br>N20 | Bit<br>N19 | Result                                                                                                     |  |

|------------|------------|------------|------------------------------------------------------------------------------------------------------------|--|

| 0          | 0          | 0          | Both outputs not enabled                                                                                   |  |

| 0          | 0          | 1          | PD <sub>out</sub> -Lo enabled                                                                              |  |

| 0          | 1          | 0          | PD <sub>out</sub> –Hi enabled                                                                              |  |

| 0          | 1          | 1          | Both PD <sub>out</sub> –Lo and PD <sub>out</sub> –Hi<br>enabled                                            |  |

| 1          | 0          | 0          | PD <sub>out</sub> –Hi enabled for 16 f <sub>R</sub> cycles<br>only, then PD <sub>out</sub> –Lo enabled     |  |

| 1          | 0          | 1          | PD <sub>out</sub> –Hi enabled for 32 f <sub>R</sub> cycles<br>only, then PD <sub>out</sub> –Lo enabled     |  |

| 1          | 1          | 0          | PD <sub>out</sub> –Hi enabled for 64 f <sub>R</sub> cycles<br>only, then PD <sub>out</sub> –Lo enabled     |  |

| 1          | 1          | 1          | PD <sub>out</sub> -Hi enabled for 128 f <sub>R</sub><br>cycles only, then PD <sub>out</sub> -Lo<br>enabled |  |

NOTES: 1. When a detector output is not enabled, it is floating.

2. Setting bit N21 = 1 places the IC in an adapt mode and engages a timer.

PD<sub>out</sub>'

# Pin 23 — Phase/Frequency Detector Output for Secondary Loop (PLL')

This pin is a three-state voltage output for use as a loop error signal when combined with an external low-pass loop filter. The detector is characterized by a linear transfer function (no dead zone). The polarity of the detector is controllable. The operation of the detector is described below and shown in Figure 21.

When the Mode pin is high, positive polarity occurs when the Pol' pin is low. Also, when the Mode pin is low, polarity defaults to positive. Positive polarity is described below. fy' is the output of the secondary loop's VCO divider (N' counter). f<sub>R</sub>' is the output of the secondary loop's reference divider (R' counter.)

- (a) Frequency of  $f_V' > f_R'$  or phase of  $f_V'$  leading  $f_R'$ : negative pulses from high impedance.

- (b) Frequency of  $f_V < f_R'$  or phase of  $f_V'$  lagging  $f_R'$ : positive pulses from high impedance.

- (c) Frequency and phase of f<sub>V</sub> ' = f<sub>R</sub> ': essentially a high–impedance state, voltage at pin determined by loop filter.

When the Mode pin is high, negative polarity occurs when the Pol' pin is high. Negative polarity is described below. fv' is the output of the secondary loop's VCO divider (N' counter). fR' is the output of the secondary loop's reference counter (R' counter.)

- (a) Frequency of fV' > fR' or phase of fV' leading fR': positive pulses from high impedance.

- (b) Frequency of  $f_V' < f_R'$  or phase of  $f_V'$  lagging  $f_R'$ : negative pulses from high impedance.

- (c) Frequency and phase of f<sub>V</sub> ' = f<sub>R</sub> ': essentially a high–impedance state, voltage at pin determined by loop filter.

This output can be enabled and disabled by bits in the C register. Placing the secondary PLL' in standby (bit C0 = 1) forces the detector output to a high–impedance state. In addition, setting the PD' Float bit (bit C3 = 1) forces the detector output to a high–impedance state while allowing the counters to run for PLL'.

The phase detector gain (in volts per radian) =  $C_{mult}$  voltage (in volts) divided by  $4\pi$ .

If the secondary loop is not used, PLL' should be placed in standby and  $PD_{out}$ ' should be left open.

# **5D. ANALOG OUTPUTS**

## DAC1 and DAC2

## Pins 3 and 4 — Digital-to-Analog Converter Outputs

These are independent outputs of the two 8-bit D/A converters. The output voltage is determined by bits in the D register. Each output is a static level with an output impedance of approximately 100 k $\Omega$ .

The DACs may be used for crystal oscillator trimming, PA (power amplifier) output power control, or other general-purpose use.

If a DAC output is not used, the pin should be left open.

# Freescale Seriegondretor, Inc.

## 5E. EXTERNAL COMPONENTS

#### Rx

#### Pin 17 — Current–Setting Resistor

An external resistor to Gnd at this pin sets a reference current that is used to determine the current at the phase/frequency detector outputs  $PD_{out}$ -Hi and  $PD_{out}$ -Lo. A value of 2 k $\Omega$  is required.

## C<sub>mult</sub>

## Pin 21 — Voltage–Multiplier Capacitor

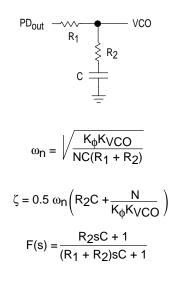

An external capacitor to Gnd at this pin is used for the on-chip voltage multiplier circuit. The value of this capacitor must be greater than 20 times the value of the largest loop filter capacitor. For example, if the largest loop filter capacitor on either the main loop or the secondary loop is 0.01  $\mu$ F, then a 0.22  $\mu$ F capacitor could be used on the C<sub>mult</sub> pin.

To ensure minimum standby supply current drain, the voltage potential at the C<sub>mult</sub> pin must not be allowed to fall below the potential at the V<sub>pos</sub> pins. Therefore, if the keep–alive oscillator is shut off, the user should tie a large value resistor (> 10 MΩ) between the C<sub>mult</sub> pin and V<sub>pos</sub>. This resistor should be sized to overcome leakage from C<sub>mult</sub> to Gnd due to the printed circuit board and the external capacitor. The consequence of not using the resistor is higher supply current drain in standby. If standby is not used, the resistor can be omitted.

# Creg

eescale Semiconductor, I

## Pin 22 — Regulator Capacitor

An external capacitor to Gnd at this pin is required for the on–chip voltage regulator. A value of 1  $\mu$ F is recommended.

5F. SUPPLY PINS

# DAC V<sub>pos</sub>

## Pin 2 — Positive Supply Potential for DACs

This pin supplies power to both DACs and determines the full–scale output of the DACs. The full–scale output is approximately equal to the voltage at DAC V<sub>pos</sub>. The voltage applied to this pin may be more, less, or equal to the potential applied to the V<sub>pos</sub> pins. The voltage range for DAC V<sub>pos</sub> is 1.8 to 3.6 V with respect to the Gnd pins.

If both DACs are not used, DAC  $V_{\mbox{pos}}$  should be tied to the same potential as  $V_{\mbox{pos}}.$

## Vpos

## Pins 11, 24, 26, and 29 — Principal Positive Supply Potential

These pins supply power to the main portion of the chip. All V<sub>pos</sub> pins must be at the same voltage potential. The voltage range for V<sub>pos</sub> is 1.8 to 3.6 V with respect to the Gnd pins.

For optimum performance, all V<sub>pos</sub> pins should be tied together and bypassed to a ground plane using a low-inductance capacitor mounted very close to the device. Lead lengths and printed circuit board traces between the capacitor and the IC package should be minimized. (The very-fast switching speed of the device can cause excessive current spikes on the power leads if they are improperly bypassed.)

## Gnd

## Pins 14, 15, 18, and 31 — Ground

Common ground for the device. All Gnd pins must be at the same potential and should be tied to a ground plane.

# Freescale Seminond motor, Inc.

6. DETAILED REGISTER DESCRIPTIONS

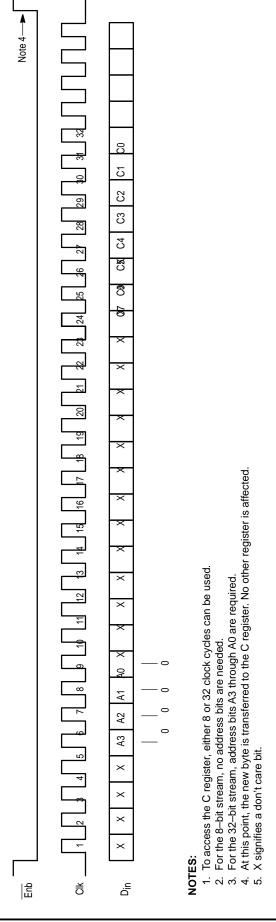

Figure 13. C Register Access and Formats

6A. C REGISTER

Note 4---

**ARCHIVE INFORMATION**

# Freescale Seminonductor, Inc.

# **C REGISTER BITS**

See Figure 13 for C register access and serial data formats.

# Out A (C7)

When the Output A pin is selected as a General–Purpose Output (via bits R'21 = R'20 = 0), bit C7 determines the state of the pin. When C7 is 1, Output A is forced to a high level. When C0 is 0 Output A is forced low.

When Output A is not selected as a General–Purpose Output, bit C7 has no function; i.e., C7 is a "don't care" bit.

# Out B/XRef (C6)

Bit C6 is a dual-purpose bit.

When the Mode pin is tied low, C6 and C1 (PLL Stby), can be used to control Output B. See Table 12. (The reference circuit defaults to crystal configuration.)

When the Mode pin is tied high, additional control of the reference circuit is allowed. See Table 13.

| Bit C6 | Bit C1 | State of<br>Output B Pin | Condition of<br>Main PLL |

|--------|--------|--------------------------|--------------------------|

| 0      | 0      | Low level                | Active                   |

| 0*     | 1*     | High impedance*          | Standby*                 |

| 1      | 0      | High level               | Active                   |

| 1      | 1      | High impedance           | Standby                  |

#### Table 12. Out B/XRef Bit with Mode Pin = Low

\*Power up default.

## Table 13. Out B/XRef Bit with Mode Pin = High