### Freescale Semiconductor

Order this document by MC68CK331EC16/D

# MC68CK331 MC68CK331PU

# Technical Supplement

# 16.78 MHz Electrical Characteristics

Devices in the 68300 Modular Microcontroller Family are built up from a selection of standard functional modules. The MC68CK331 incorporates a central processing unit (CPU32), a system integration module (SIM), a general-purpose timer (GPT), and a queued serial module (QSM).

This publication contains new electrical characteristics for the MC68CK331/MC68CK331PU to be used in conjunction with the *MC68331 User's Manual* (MC68331UM/AD).

New features on the MC68CK331 include:

- V<sub>DD</sub> operating range from 2.7 volts to 3.6 volts

- PLL operation at 16.78 MHz

- 5V tolerant, TTL compatible I/O

An additional feature on the MC68CK331PU includes:

• Reduced pin count (100 pin package)

# **PRELIMINARY**

# **Freescale Semiconductor, Inc.**LIST OF FIGURES

| Figure |                                                       | Page |

|--------|-------------------------------------------------------|------|

| 1      | CLKOUT Output Timing Diagram                          | 12   |

| 2      | External Clock Input Timing Diagram                   | 12   |

| 3      | ECLK Output Timing Diagram                            | 12   |

| 4      | Read Cycle Timing Diagram                             | 13   |

| 5      | Write Cycle Timing Diagram                            | 14   |

| 6      | Fast Termination Read Cycle Timing Diagram            | 15   |

| 7      | Fast Termination Write Cycle Timing Diagram           | 16   |

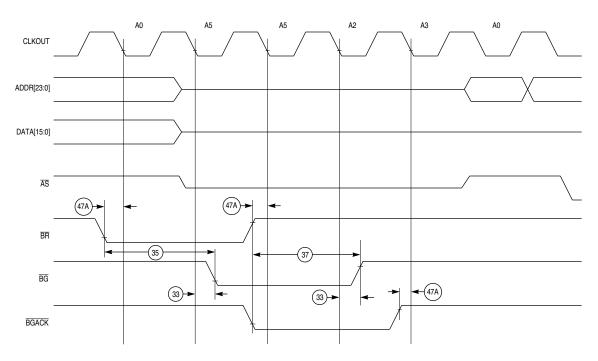

| 8      | Bus Arbitration Timing Diagram — Active Bus Case      | 17   |

| 9      | Bus Arbitration Timing Diagram — Idle Bus Case        | 18   |

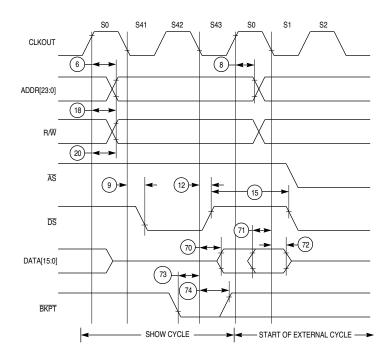

| 10     | Show Cycle Timing Diagram                             |      |

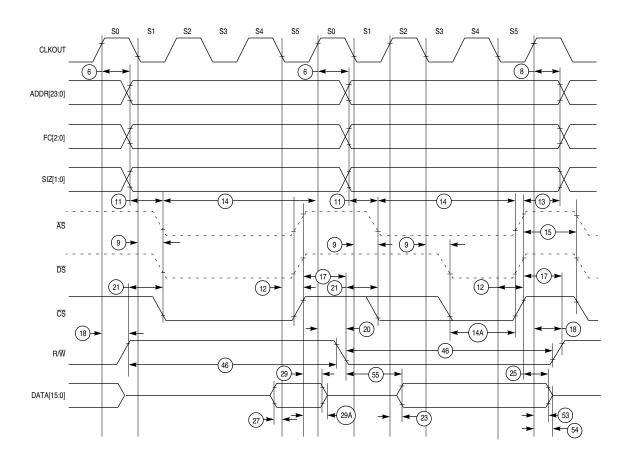

| 11     | Chip-Select Timing Diagram                            |      |

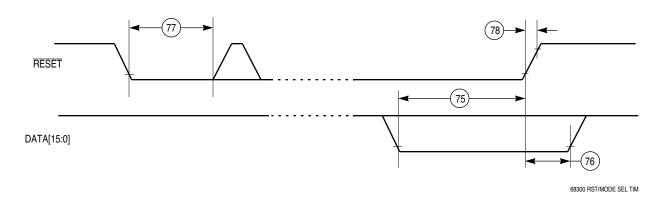

| 12     | Reset and Mode Select Timing Diagram                  |      |

| 13     | BDM Serial Communication Timing Diagram               |      |

| 14     | BDM Freeze Assertion Timing Diagram                   |      |

| 15     | ECLK Timing Diagram                                   |      |

| 16     | QSPI Timing — Master, CPHA = 0                        |      |

| 17     | QSPI Timing — Master, CPHA = 1                        |      |

| 18     | QSPI Timing — Slave, CPHA = 0                         |      |

| 19     | QSPI Timing — Slave, CPHA = 1                         |      |

| 20     | Input Signal Conditioner Timing                       |      |

| 21     | Pulse Accumulator —Event Counting Mode (Leading Edge) |      |

| 22     | Pulse Accumulator —Gated Mode (Count While Pin High)  |      |

| 23     | Pulse Accumulator —Using TOF as Gated Mode Clock      |      |

| 24     | PWMx (PWMx Register = 01, Fast Mode)                  |      |

| 25     | Output Compare (Toggle Pin State)                     |      |

| 26     | Input Capture (Capture on Rising Edge                 |      |

| 27     | General-Purpose Input                                 |      |

| 28     | General-Purpose Output (Causes Input Capture)         |      |

| 29     | Force Compare (CLEAR)                                 |      |

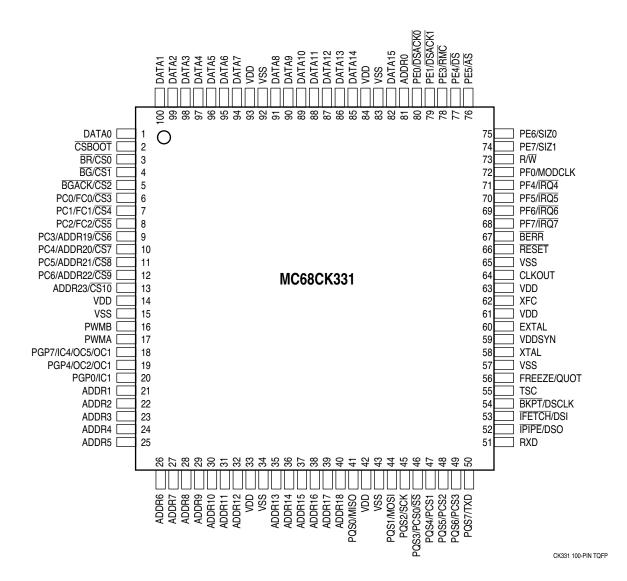

| 30     | MC68CK331 Pin Assignments for 100-Pin Package         |      |

| 31     | MC68CK331 Pin Assignments for 132-Pin Package         |      |

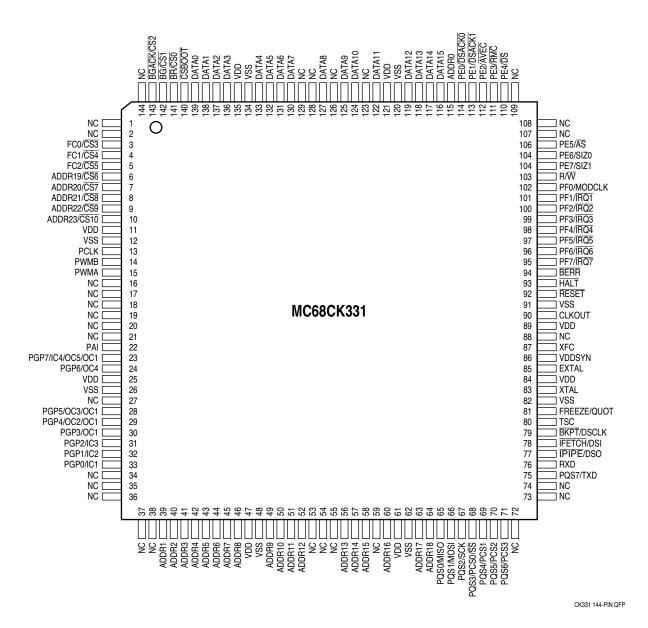

| 32     | MC68CK331 Pin Assignments for 144-Pin Package         | 38   |

### **LIST OF TABLES**

| Table |                                          | Page |

|-------|------------------------------------------|------|

| 1     | Maximum Ratings                          |      |

| 2     | MC68CK331 Typical Ratings                |      |

| 3     | Thermal Characteristics                  |      |

| 4     | Clock Control Timing                     | 6    |

| 5     | 16.78 MHz DC Characteristics             |      |

| 6     | 16.78 MHz AC Timing                      |      |

| 7     | Background Debugging Mode Timing         |      |

| 8     | ECLK Bus Timing                          | 22   |

| 9     | QSPI Timing                              | 24   |

| 10    | General-Purpose Timer AC Characteristics |      |

| 11    | MC68CK331PU 100-Pin TQFP Pin Assignments |      |

| 12    | MC68CK331PU Deleted Function Pin List    |      |

#### **Table 1 Maximum Ratings**

| Num | Rating                                                                                                                                       | Symbol           | Value                                         | Unit |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------|------|

| 1   | Supply Voltage <sup>1, 2, 7</sup>                                                                                                            | V <sub>DD</sub>  | -0.3 to + 5.5                                 | V    |

| 2   | Input Voltage <sup>1, 2, 3, 5, 7</sup><br>TSC                                                                                                | V <sub>in</sub>  | -0.3 to + 5.5<br>-0.3 to + 6.0                | V    |

| 3   | Instantaneous Maximum Current Single pin limit (applies to all pins) <sup>1, 5, 6, 7</sup>                                                   | I <sub>D</sub>   | 25                                            | mA   |

| 4   | Operating Maximum Current  Digital Input Disruptive Current $^{4, 5, 6, 7, 8}$ $V_{NEGCLMAP} \cong -0.3 V$ $V_{POSCLAMP} \cong V_{DD} + 0.3$ | I <sub>ID</sub>  | -500 to 500                                   | μА   |

| 5   | Operating Temperature Range                                                                                                                  | T <sub>A</sub>   | T <sub>L</sub> to T <sub>H</sub><br>-40 to 85 | °C   |

| 6   | Storage Temperature Range                                                                                                                    | T <sub>stg</sub> | -55 to 150                                    | °C   |

#### NOTES:

- Permanent damage can occur if maximum ratings are exceeded. Exposure to voltages or currents in excess

of recommended values affects device reliability. Device modules may not operate normally while being exposed to electrical extremes.

- 2. Although sections of the device contain circuitry to protect against damage from high static voltages or electrical fields, take normal precautions to avoid exposure to voltages higher than maximum-rated voltages.

- 3. All pins except TSC.

- 4. All functional non-supply pins are internally clamped to  $V_{SS}$ . All functional pins except EXTAL, TSC, and XFC are internally clamped to  $V_{DD}$ .

- Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

- 6. Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions.

- 7. This parameter is periodically sampled rather than 100% tested.

- 8. Total input current for all digital input-only and all digital input/output pins must not exceed 10 mA. Exceeding this limit can cause disruption of normal operation.

### Table 2 MC68CK331 Typical Ratings

| Num | Rating                                                                                                                                          | Symbol             | Value           | Unit           |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|----------------|

| 1   | Supply Voltage                                                                                                                                  | $V_{DD}$           | 3.0             | V              |

| 2   | Operating Temperature                                                                                                                           | T <sub>A</sub>     | 25              | °C             |

| 3   | V <sub>DD</sub> Supply Current RUN LPSTOP, External clock, maximum f <sub>sys</sub> LPSTOP, VCO off                                             | I <sub>DD</sub>    | 35<br>1.0<br>70 | mA<br>mA<br>μA |

| 4   | Clock Synthesizer Operating Voltage                                                                                                             | V <sub>DDSYN</sub> | 3.0             | V              |

| 5   | V <sub>DDSYN</sub> Supply Current<br>External clock, maximum f <sub>sys</sub><br>32.768 kHz Crystal Reference, VCO on, maximum f <sub>sys</sub> | I <sub>DDSYN</sub> | 1.5<br>1        | mA<br>mA       |

| 6   | Power Dissipation                                                                                                                               | P <sub>D</sub>     | 108             | mW             |

#### **Table 3 Thermal Characteristics**

| Num | Rating                        | Symbol        | Value | Unit |

|-----|-------------------------------|---------------|-------|------|

|     | Thermal Resistance            |               | 49    |      |

| 1   | Plastic 144-Pin Surface Mount | $\Theta_{JA}$ | 60    | °C/W |

|     | Plastic 100-Pin Surface Mount |               | 00    |      |

The average chip-junction temperature (TJ) in C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \Theta_{JA}) \quad (1)$$

where:

T<sub>A</sub> = Ambient Temperature, °C

$\Theta_{JA}$  = Package Thermal Resistance, Junction-to-Ambient, °C/W

$P_D = P_{INT} + P_{I/O}$

$P_{INT}$  =  $I_{DD} \times V_{DD}$ , Watts — Chip Internal Power

P<sub>I/O</sub> = Power Dissipation on Input and Output Pins — User Determined

For most applications  $P_{I/O} < P_{INT}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_D = K \div (T_J + 273^{\circ}C)$$

(2)

Solving equations 1 and 2 for K gives:

$$K = P_D + (T_A + 273^{\circ}C) + \Theta_{JA} \times P_{D^2}$$

(3)

where K is a constant pertaining to the particular part. K can be determined from equation (3) by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving equations (1) and (2) iteratively for any value of  $T_A$ .

#### **Table 4 Clock Control Timing**

$(V_{DD} \text{ and } V_{DDSYN} = 2.7 \text{ Vdc to } 3.6 \text{ Vdc}, V_{SS} = 0 \text{ Vdc}, T_{A} = T_{L} \text{ to } T_{H}, 32.768 \text{ kHz reference})$

| Num | Characteristic                                                                             | Symbol            | Min                        | Max                                             | Unit |

|-----|--------------------------------------------------------------------------------------------|-------------------|----------------------------|-------------------------------------------------|------|

| 1   | PLL Reference Frequency Range                                                              | f <sub>ref</sub>  | 25                         | 50                                              | kHz  |

| 2   | System Frequency <sup>1</sup> On-Chip PLL System Frequency External Clock Operation        | f <sub>sys</sub>  | 4(f <sub>ref</sub> )<br>dc | 16.78<br>16.78                                  | MHz  |

| 3   | PLL Lock Time <sup>2,3,4,5</sup>                                                           | t <sub>lpll</sub> | _                          | 50                                              | ms   |

| 4   | VCO Frequency <sup>6</sup>                                                                 | f <sub>VCO</sub>  | _                          | 2 (f <sub>sys</sub> max)                        | MHz  |

| 5   | Limp Mode Clock Frequency SYNCR X bit = 0 SYNCR X bit = 1                                  | f <sub>limp</sub> | _                          | f <sub>sys</sub> max /2<br>f <sub>sys</sub> max | MHz  |

| 6   | CLKOUT Jitter <sup>2, 3, 4, 7</sup> Short term (5 μs interval) Long term (500 μs interval) | J <sub>clk</sub>  | -0.5<br>-0.05              | 0.5<br>0.05                                     | %    |

#### NOTES:

- 1. All internal registers retain data at 0 Hz.

- 2. This parameter is periodically sampled rather than 100% tested.

- 3. Assumes that a low-leakage external filter network is used to condition clock synthesizer input voltage. Total external resistance from the XFC pin due to external leakage must be greater than 15  $M\Omega$  to guarantee this specification. Filter network geometry can vary depending upon operating environment.

- 4. Proper layout procedures must be followed to achieve specifications.

- 5. Assumes that stable V<sub>DDSYN</sub> is applied, and that the crystal oscillator is stable. Lock time is measured from the time V<sub>DD</sub> and V<sub>DDSYN</sub> are valid until RESET is released. This specification also applies to the period required for PLL lock after changing the W and Y frequency control bits in the synthesizer control register (SYNCR) while the PLL is running, and to the period required for the clock to lock after LPSTOP.

- 6. Internal VCO frequency ( $f_{VCO}$ ) is determined by SYNCR W and Y bit values. The SYNCR X bit controls a divide-by-two circuit that is not in the synthesizer feedback loop. When X = 0, the divider is enabled, and  $f_{sys} = f_{VCO} \div 4$ . When X = 1, the divider is disabled, and  $f_{sys} = f_{VCO} \div 2$ . X must equal one when operating at maximum specified  $f_{sys}$ .

- 7. Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>sys</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via V<sub>DDSYN</sub> and V<sub>SS</sub> and variation in crystal oscillator frequency increase the J<sub>clk</sub> percentage for a given interval. When jitter is a critical constraint on control system operation, this parameter should be measured during functional testing of the final system.

### **Table 5 16.78 MHz DC Characteristics**

(V<sub>DD</sub> and V<sub>DDSYN</sub> = 2.7 to 3.6 Vdc, V<sub>SS</sub> = 0 Vdc,  $T_A = T_L$  to  $T_H$ )

| Num | Characteristic                                                                                                                                                                                                                                                  | Symbol             | Min                   | Max                   | Unit                 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|-----------------------|----------------------|

| 1   | Input High Voltage                                                                                                                                                                                                                                              | V <sub>IH</sub>    | 2.0                   | 5.5                   | V                    |

| 2   | Input Low Voltage                                                                                                                                                                                                                                               | V <sub>IL</sub>    | V <sub>SS</sub> - 0.3 | 0.8                   | V                    |

| 3   | Input Hysteresis <sup>1</sup>                                                                                                                                                                                                                                   | V <sub>HYS</sub>   | 0.5                   | _                     | V                    |

| 4   | Input Leakage Current $^2$ $V_{in} = V_{DD}$ or $V_{SS}$ Input-only pins $V_{in} = 5.5 \text{ V}$                                                                                                                                                               | l <sub>in</sub>    | -2.5<br>-2.5          | 2.5<br>2.5            | μА                   |

| 5   | High Impedance (Off-State) Leakage Current <sup>2</sup> $V_{in} = V_{DD}$ or $V_{SS}$ All input/output and output pins $V_{in} = 5.5 \text{ V}$                                                                                                                 | I <sub>OZ</sub>    | -2.5<br>-2.5          | 2.5<br>2.5            | μΑ                   |

| 6   | CMOS Output High Voltage <sup>2, 3</sup> $I_{OH} = -10.0 \mu\text{A}$ Group 1, 2, 4 input/output and output pins                                                                                                                                                | V <sub>OH</sub>    | V <sub>DD</sub> -0.2  | _                     | V                    |

| 7   | CMOS Output Low Voltage <sup>2</sup> I <sub>OL</sub> = 10.0 μA Group 1, 2, 4 input/output and output pins                                                                                                                                                       | V <sub>OL</sub>    | _                     | 0.2                   | V                    |

| 8   | TTL Compatible Output High Voltage <sup>2, 3</sup> I <sub>OH</sub> = -0.4 mA Group 1, 2, 4 input/output and output pins                                                                                                                                         | V <sub>OH</sub>    | 2.4                   | _                     | V                    |

| 9   | TTL Compatible Output Low Voltage <sup>2</sup> $I_{OL} = 0.8 \text{ mA Group 1 I/O pins, CLKOUT, FREEZE/QUOT, } \overline{IPIPE}$ $I_{OL} = 2.6 \text{ mA Group 2 and Group 4 I/O pins, } \overline{CSBOOT, } \overline{BG/CS}$ $I_{OL} = 6 \text{ mA Group 3}$ | V <sub>OL</sub>    | _<br>_<br>_           | 0.4<br>0.4<br>0.4     | V                    |

| 10  | Three State Control Input High Voltage                                                                                                                                                                                                                          | V <sub>IHTSC</sub> | $1.65 \times V_{DD}$  | 6.0                   | V                    |

| 11  | Data Bus Mode Select Pull-up Current $^4$ $V_{in} = V_{IL}$ $V_{in} = V_{IH}$                                                                                                                                                                                   | I <sub>MSP</sub>   | _<br>-8               | –95<br><i>–</i> -     | μА                   |

| 12  | V <sub>DD</sub> Supply Current <sup>5</sup> Run LPSTOP, external clock input frequency = max f <sub>sys</sub> LPSTOP, VCO off                                                                                                                                   | I <sub>DD</sub>    | _<br>_<br>_           | 45<br>2<br>260        | mA<br>mA<br>μA       |

| 13  | Clock Synthesizer Operating Voltage                                                                                                                                                                                                                             | V <sub>DDSYN</sub> | 2.7                   | 3.6                   | V                    |

| 14  | V <sub>DDSYN</sub> Supply Current External clock, maximum f <sub>sys</sub> 32.768 kHz Crystal Reference, VCO on, maximum f <sub>sys</sub> LPSTOP, 32.768 kHz Crystal Reference, VCO off 32.768 kHz, V <sub>DD</sub> Powered down                                | I <sub>DDSYN</sub> | =                     | 3<br>655<br>150<br>70 | mA<br>μA<br>μA<br>μA |

| 15  | Power Dissipation <sup>6</sup>                                                                                                                                                                                                                                  | P <sub>D</sub>     | _                     | 173                   | mW                   |

|     | 1                                                                                                                                                                                                                                                               | 1                  |                       |                       | 1                    |

### Table 5 16.78 MHz DC Characteristics (Continued)

$(V_{DD} \text{ and } V_{DDSYN} = 2.7 \text{ to } 3.6 \text{ Vdc}, V_{SS} = 0 \text{ Vdc}, T_A = T_I \text{ to } T_H)$

| Num | Characteristic                                                                                                                                  | Symbol          | Min              | Max                  | Unit |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|----------------------|------|

| 16  | Input Capacitance <sup>2, 7</sup> All input-only pins All input/output pins                                                                     | C <sub>in</sub> | _                | 10<br>20             | pF   |

| 17  | Load Capacitance <sup>2</sup> Group 1 I/O Pins, CLKOUT, FREEZE/QUOT, IPIPE Group 2 I/O Pins and CSBOOT, BG/CS Group 3 I/O Pins Group 4 I/O Pins | C <sub>L</sub>  | _<br>_<br>_<br>_ | 80<br>80<br>80<br>80 | pF   |

#### NOTES:

1. Applies to:

QSM pins

IRQ[7:1], RESET, EXTAL, TSC, RMC, BKPT/DSCLK, IFETCH/DSI

2. Input-Only Pins: TSC, BKPT/DSCLK, RXD

Output-Only Pins: CSBOOT, BG/CS, CLKOUT, FREEZE/QUOT, IPIPE/DSO

Input/Output Pins:

Group 1: DATA[15:0], IFETCH/DSI

Group 2: ADDR[23:19]/CS[10:6], FC[2:0]/CS[5:3], DSACK[1:0], AVEC, RMC, DS, AS, SIZ[1:0]

IRQ[7:1], MODCLK, ADDR[18:0], R/W, BERR, BR/CSO, BGACK/CS2, PCS[3:1], PCSO/SS, TXD

Group 3: HALT, RESET Group 4: MISO, MOSI, SCK

- 3. Does not apply to HALT and RESET because they are open drain pins. Does not apply to Port QS[7:0] (TXD, PCS[3:1], PCS0/SS, SCK, MOSI, MISO) in wired-OR mode.

- 4. Current measured at maximum system clock frequency.

- 5. Total operating current is the sum of the appropriate  $V_{DD}$  supply and  $V_{DDSYN}$  supply current.

- 6. Power dissipation measured at specified system clock frequency, all modules active. Power dissipation can be calculated using the expression:

$$P_D = 3.6V (I_{DDSYN} + I_{DD})$$

$I_{DD}$  includes supply currents for all device modules powered by  $V_{DDE}$  and  $V_{DDI}$  pins.

7. Input capacitance is periodically sampled rather than 100% tested.

### Table 6 16.78 MHz AC Timing

$(V_{DD} \text{ and } V_{DDSYN} = 2.7 \text{ to } 3.6 \text{ Vdc}, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H)^1$

| Num    | Characteristic                                             | Symbol             | Min  | Max   | Unit |

|--------|------------------------------------------------------------|--------------------|------|-------|------|

| F1     | Frequency of Operation                                     | f                  | DC   | 16.78 | MHz  |

| 1      | Clock Period                                               | t <sub>cyc</sub>   | 59.6 | _     | ns   |

| 1A     | ECLK Period                                                | t <sub>Ecyc</sub>  | 476  | _     | ns   |

| 1B     | External Clock Input Period <sup>2</sup>                   | t <sub>Xcyc</sub>  | 59.6 | _     | ns   |

| 2, 3   | Clock Pulse Width                                          | t <sub>CW</sub>    | 24   | _     | ns   |

| 2A, 3A | ECLK Pulse Width                                           | t <sub>ECW</sub>   | 236  | _     | ns   |

| 2B, 3B | External Clock Input High/Low Time <sup>2</sup>            | t <sub>XCHL</sub>  | 29.8 | _     | ns   |

| 4, 5   | CLKOUT Rise and Fall Time                                  | t <sub>Crf</sub>   | _    | 5     | ns   |

| 4A, 5A | Rise and Fall Time (All outputs except CLKOUT)             | t <sub>rf</sub>    | _    | 8     | ns   |

| 4B, 5B | External Clock Input Rise and Fall Time                    | t <sub>XCrf</sub>  | _    | 5     | ns   |

| 6      | Clock High to ADDR, FC, RMC, SIZ Valid                     | t <sub>CHAV</sub>  | 0    | 29    | ns   |

| 7      | Clock High to ADDR, Data, FC, RMC,SIZ High Impedance       | t <sub>CHAZx</sub> | 0    | 59    | ns   |

| 8      | Clock High to ADDR, FC, RMC, SIZ Invalid                   | t <sub>CHAZn</sub> | 0    | _     | ns   |

| 9      | Clock Low to AS, DS, CS Asserted                           | t <sub>CLSA</sub>  | 2    | 25    | ns   |

| 9A     | AS to DS or CS Asserted (Read) <sup>3</sup>                | t <sub>STSA</sub>  | -15  | 15    | ns   |

| 9C     | Clock Low to IFETCH, IPIPE Asserted                        | t <sub>CLIA</sub>  | 2    | 22    | ns   |

| 11     | ADDR, FC, RMC, SIZ Valid to AS, CS, (and DS Read) Asserted | t <sub>AVSA</sub>  | 15   | _     | ns   |

| 12     | Clock Low to AS, DS, CS Negated                            | t <sub>CLSN</sub>  | 2    | 29    | ns   |

| 12A    | Clock Low to IFETCH, IPIPE Negated                         | t <sub>CLIN</sub>  | 2    | 22    | ns   |

| 13     | AS, DS, CS Negated to ADDR, FC, SIZ Invalid (Address Hold) | t <sub>SNAI</sub>  | 15   | _     | ns   |

| 14     | AS, CS (and DS Read) Width Asserted                        | t <sub>SWA</sub>   | 100  | _     | ns   |

| 14A    | DS, CS Width Asserted (Write)                              | t <sub>SWAW</sub>  | 45   | _     | ns   |

| 14B    | AS, CS (and DS Read) Width Asserted (Fast Cycle)           | t <sub>SWDW</sub>  | 40   | _     | ns   |

| 15     | AS, DS, CS Width Negated <sup>4</sup>                      | t <sub>SN</sub>    | 40   | _     | ns   |

| 16     | Clock High to AS, DS, R/W High Impedance                   | t <sub>CHSZ</sub>  | _    | 59    | ns   |

| 17     | AS, DS, CS Negated to R/W High                             | t <sub>SNRN</sub>  | 15   | _     | ns   |

| 18     | Clock High to R/W High                                     | t <sub>CHRH</sub>  | 0    | 29    | ns   |

| 20     | Clock High to R/W Low                                      | t <sub>CHRL</sub>  | 0    | 29    | ns   |

| 21     | R/W High to AS, CS Asserted                                | t <sub>RAAA</sub>  | 15   | _     | ns   |

| 22     | R/W Low to DS, CS Asserted (Write)                         | t <sub>RASA</sub>  | 70   | _     | ns   |

| 23     | Clock High to Data Out Valid                               | t <sub>CHDO</sub>  | _    | 29    | ns   |

|        |                                                            |                    |      |       |      |

### Table 6 16.78 MHz AC Timing (Continued)

$(V_{DD} \text{ and } V_{DDSYN} = 2.7 \text{ to } 3.6 \text{ Vdc}, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H)^1$

| Num | Characteristic                                                        | Symbol             | Min | Max      | Unit             |

|-----|-----------------------------------------------------------------------|--------------------|-----|----------|------------------|

| 24  | Data Out Valid to Negating Edge of AS, CS (Fast Write Cycle)          | t <sub>DVASN</sub> | 15  | <b> </b> | ns               |

| 25  | DS, CS Negated to Data Out Invalid (Data Out Hold)                    | t <sub>SNDOI</sub> | 15  | T —      | ns               |

| 26  | Data Out Valid to DS, CS Asserted (Write)                             | t <sub>DVSA</sub>  | 15  | T —      | ns               |

| 27  | Data In Valid to Clock Low (Data Setup)                               | t <sub>DICL</sub>  | 5   | 1 –      | ns               |

| 27A | Late BERR, HALT Asserted to Clock Low (Setup Time)                    | t <sub>BELCL</sub> | 20  | T —      | ns               |

| 28  | AS, DS Negated to DSACK[1:0], BERR, HALT, AVEC Negated                | t <sub>SNDN</sub>  | 0   | 80       | ns               |

| 29  | DS, CS Negated to Data In Invalid (Data In Hold) <sup>5</sup>         | t <sub>SNDI</sub>  | 0   | _        | ns               |

| 29A | DS, CS Negated to Data In High Impedance <sup>5, 6</sup>              | t <sub>SHDI</sub>  | _   | 55       | ns               |

| 30  | CLKOUT Low to Data In Invalid (Fast Cycle Hold) <sup>5</sup>          | t <sub>CLDI</sub>  | 15  |          | ns               |

| 30A | CLKOUT Low to Data In High Impedance <sup>5</sup>                     | t <sub>CLDH</sub>  | _   | 90       | ns               |

| 31  | DSACK[1:0] Asserted to Data In Valid <sup>7</sup>                     | t <sub>DADI</sub>  | _   | 50       | ns               |

| 33  | Clock Low to BG Asserted/Negated                                      | t <sub>CLBAN</sub> | _   | 29       | ns               |

| 35  | BR Asserted to BG Asserted (RMC not Asserted) <sup>8</sup>            | t <sub>BRAGA</sub> | 1   |          | t <sub>cyc</sub> |

| 37  | BGACK Asserted to BG Negated                                          | t <sub>GAGN</sub>  | 1   | 2        | t <sub>cyc</sub> |

| 39  | BG Width Negated                                                      | t <sub>GH</sub>    | 2   |          | t <sub>cyc</sub> |

| 39A | BG Width Asserted                                                     | t <sub>GA</sub>    | 1   |          | t <sub>cyc</sub> |

| 46  | R/W Width Asserted (Write or Read)                                    | t <sub>RWA</sub>   | 150 |          | ns               |

| 46A | R/W Width Asserted (Fast Write or Read Cycle)                         | t <sub>RWAS</sub>  | 90  |          | ns               |

| 47A | Asynchronous Input Setup Time BR, BGACK, DSACK[1:0], BERR, AVEC, HALT | t <sub>AIST</sub>  | 5   | _        | ns               |

| 47B | Asynchronous Input Hold Time                                          | t <sub>AIHT</sub>  | 15  |          | ns               |

| 48  | DSACK[1:0] Asserted to BERR, HALT Asserted <sup>9</sup>               | t <sub>DABA</sub>  | _   | 30       | ns               |

| 53  | Data Out Hold from Clock High                                         | t <sub>DOCH</sub>  | 0   |          | ns               |

| 54  | Clock High to Data Out High Impedance                                 | t <sub>CHDH</sub>  | _   | 28       | ns               |

| 55  | R/W Asserted to Data Bus Impedance Change                             | t <sub>RADC</sub>  | 40  |          | ns               |

| 56  | RESET Pulse Width (Reset Instruction)                                 | t <sub>HRPW</sub>  | 512 |          | t <sub>cyc</sub> |

| 57  | BERR Negated to HALT Negated (Rerun)                                  | t <sub>BNHN</sub>  | 0   | _        | ns               |

| 70  | Clock Low to Data Bus Driven (Show Cycle)                             | t <sub>SCLDD</sub> | 0   | 29       | ns               |

| 71  | Data Setup Time to Clock Low (Show Cycle)                             | t <sub>SCLDS</sub> | 15  | _        | ns               |

| 72  | Data Hold from Clock Low (Show Cycle)                                 | t <sub>SCLDH</sub> | 10  |          | ns               |

| 73  | BKPT Input Setup Time                                                 | t <sub>BKST</sub>  | 15  | _        | ns               |

### Table 6 16.78 MHz AC Timing (Continued)

$(V_{DD} \text{ and } V_{DDSYN} = 2.7 \text{ to } 3.6 \text{ Vdc}, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H)^1$

| Num | Characteristic                     | Symbol            | Min | Max | Unit             |

|-----|------------------------------------|-------------------|-----|-----|------------------|

| 74  | BKPT Input Hold Time               | t <sub>BKHT</sub> | 10  | _   | ns               |

| 75  | Mode Select Setup Time             | t <sub>MSS</sub>  | 20  | _   | t <sub>cyc</sub> |

| 76  | Mode Select Hold Time              | t <sub>MSH</sub>  | 0   | _   | ns               |

| 77  | RESET Assertion Time <sup>10</sup> | t <sub>RSTA</sub> | 4   | _   | t <sub>cyc</sub> |

| 78  | RESET Rise Time <sup>11, 12</sup>  | t <sub>RSTR</sub> | _   | 10  | t <sub>cyc</sub> |

#### NOTES:

- 1. All AC timing is shown with respect to 2.0 V and 0.8 V levels unless otherwise noted.

- 2. When an external clock is used, minimum high and low times are based on a 50% duty cycle. The minimum allowable t<sub>Xcyc</sub> period is reduced when the duty cycle of the external clock varies. The relationship between external clock input duty cycle and minimum t<sub>Xcyc</sub> is expressed:

Minimum  $t_{XCVC}$  period = minimum  $t_{XCHL}$  / (50% – external clock input duty cycle tolerance).

- 3. Specification 9A is the worst-case skew between  $\overline{AS}$  and  $\overline{DS}$  or  $\overline{CS}$ . The amount of skew depends on the relative loading of these signals. When loads are kept within specified limits, skew will not cause  $\overline{AS}$  and  $\overline{DS}$  to fall outside the limits shown in specification 9.

- 4. If multiple chip-selects are used,  $\overline{CS}$  width negated (specification 15) applies to the time from the negation of a heavily loaded chip-select to the assertion of a lightly loaded chip select. The  $\overline{CS}$  width negated specification between multiple chip-selects does not apply to chip selects being used for synchronous ECLK cycles.

- 5. Hold times are specified with respect to  $\overline{DS}$  or  $\overline{CS}$  on asynchronous reads and with respect to CLKOUT on fast cycle reads. The user is free to use either hold time.

- Maximum value is equal to (t<sub>cvc</sub> / 2) + 25 ns.

- 7. If the asynchronous setup time (specification 47A) requirements are satisfied, the DSACK[1:0] low to data setup time (specification 31) and DSACK[1:0] low to BERR low setup time (specification 48) can be ignored. The data must only satisfy the data-in to clock low setup time (specification 27) for the following clock cycle. BERR must satisfy only the late BERR low to clock low setup time (specification 27A) for the following clock cycle.

- 8. To ensure coherency during every operand transfer,  $\overline{BG}$  is not asserted in response to  $\overline{BR}$  until after all cycles of the current operand transfer are complete.

- 9. In the absence of DSACK[1:0], BERR is an asynchronous input using the asynchronous setup time (specification 47A).

- After external RESET negation is detected, a short transition period (approximately 2) t<sub>cyc</sub> elapses, then the SIM drives RESET low for 512 t<sub>cyc</sub>.

- 11. External assertion of the RESET input can overlap internally-generated resets. To insure that an external reset is recognized in all cases, RESET must be asserted for at least 590 CLKOUT cycles.

- 12. External logic must pull RESET high during this period in order for normal MCU operation to begin.

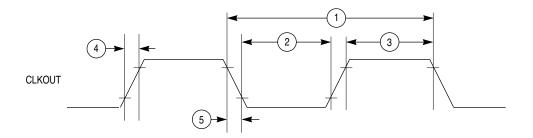

68300 CLKOUT TIM

Figure 1 CLKOUT Output Timing Diagram

PULSE WIDTH SHOWN WITH RESPECT TO 50%  $V_{DD}$ .

68300 EXT CLK INPUT TIM

Figure 2 External Clock Input Timing Diagram

68300 ECLK OUTPUT TIM

Figure 3 ECLK Output Timing Diagram

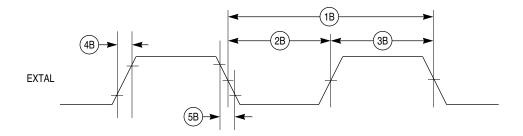

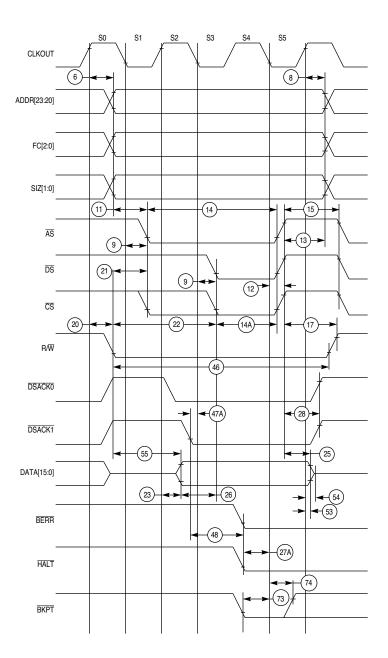

68300 RD CYC TIM

**Figure 4 Read Cycle Timing Diagram**

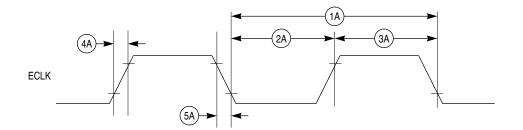

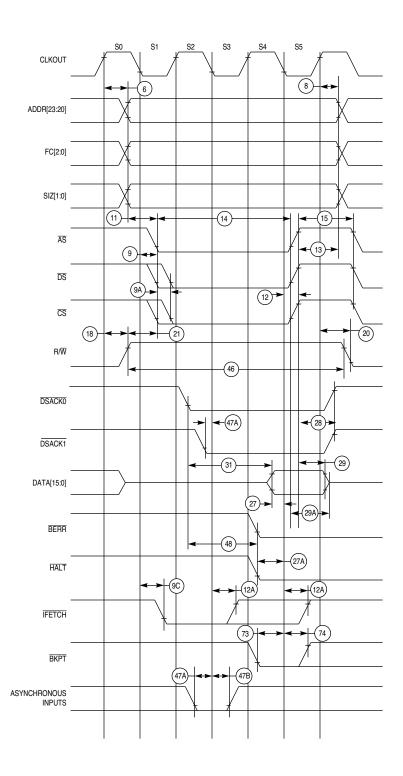

68300 WR CYC TIM

**Figure 5 Write Cycle Timing Diagram**

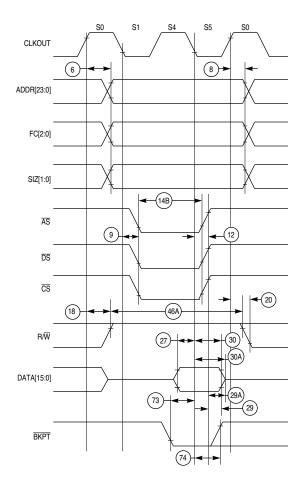

68300 FAST RD CYC TIM

**Figure 6 Fast Termination Read Cycle Timing Diagram**

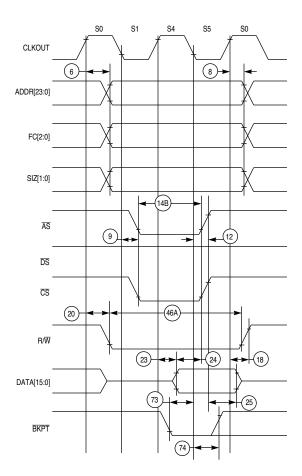

68300 FAST WR CYC TIM

**Figure 7 Fast Termination Write Cycle Timing Diagram**

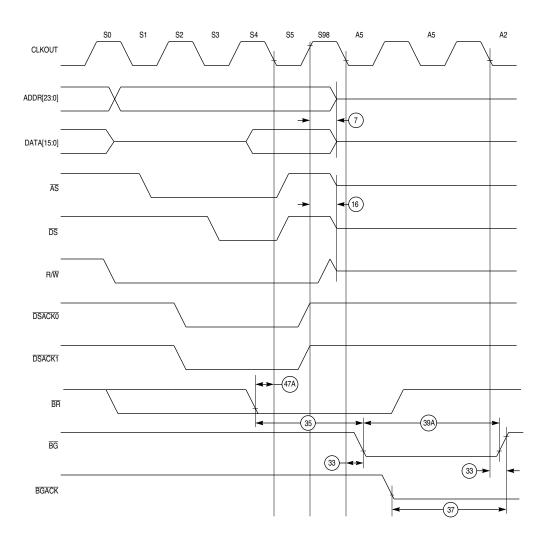

68300 BUS ARB TIM

Figure 8 Bus Arbitration Timing Diagram — Active Bus Case

68300 BUS ARB TIM IDLE

Figure 9 Bus Arbitration Timing Diagram — Idle Bus Case

### NOTE:

Show cycles can stretch during clock phase S42 when bus accesses take longer than two cycles due to IMB module wait-state insertion.

68300 SHW CYC TIM

**Figure 10 Show Cycle Timing Diagram**

68300 CHIP SEL TIM

**Figure 11 Chip-Select Timing Diagram**

Figure 12 Reset and Mode Select Timing Diagram

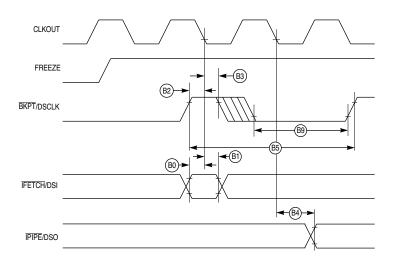

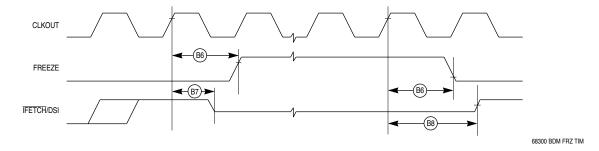

### **Table 7 Background Debugging Mode Timing**

$(V_{DD} \text{ and } V_{DDSYN} = 2.7 \text{ to } 3.6 \text{ Vdc}, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H)^1$

| Num | Characteristic                        | Symbol              | Min | Max | Unit             |

|-----|---------------------------------------|---------------------|-----|-----|------------------|

| В0  | DSI Input Setup Time                  | t <sub>DSISU</sub>  | 15  | _   | ns               |

| B1  | DSI Input Hold Time                   | t <sub>DSIH</sub>   | 10  | _   | ns               |

| B2  | DSCLK Setup Time                      | t <sub>DSCSU</sub>  | 15  | _   | ns               |

| В3  | DSCLK Hold Time                       | t <sub>DSCH</sub>   | 10  | _   | ns               |

| B4  | DSO Delay Time                        | t <sub>DSOD</sub>   |     | 25  | ns               |

| B5  | DSCLK Cycle Time                      | t <sub>DSCCYC</sub> | 2   | _   | t <sub>cyc</sub> |

| В6  | CLKOUT Low to FREEZE Asserted/Negated | t <sub>FRZAN</sub>  |     | 50  | ns               |

| В7  | CLKOUT High to IFETCH High Impedance  | t <sub>IPZ</sub>    |     | 50  | ns               |

| B8  | CLKOUT High to IFETCH Valid           | t <sub>IP</sub>     | _   | 50  | ns               |

| В9  | DSCLK Low Time                        | t <sub>DSCLO</sub>  | 1   | _   | t <sub>cyc</sub> |

### NOTES:

1. All AC timing is shown with respect to 20%  $\rm V_{DD}$  and 70%  $\rm V_{DD}$  levels unless otherwise noted.

68300 BKGD DBM SER COM TIM

Figure 13 BDM Serial Communication Timing Diagram

Figure 14 BDM Freeze Assertion Timing Diagram

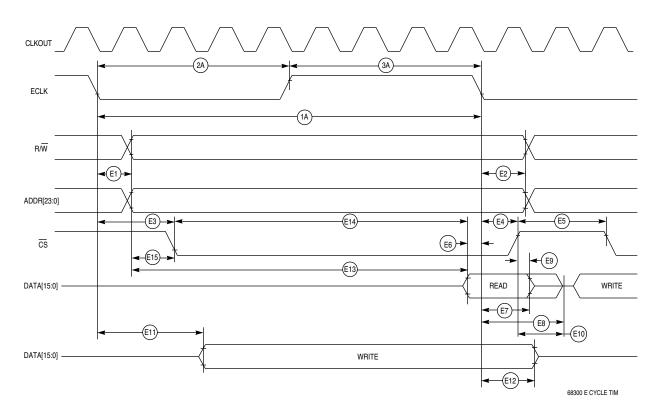

### **Table 8 ECLK Bus Timing**

$(V_{DD} \text{ and } V_{DDSYN} = 2.7 \text{ to } 3.6 \text{ Vdc}, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H)^1$

| Num | Characteristic                              | Symbol            | Min | Max | Unit             |

|-----|---------------------------------------------|-------------------|-----|-----|------------------|

| E1  | ECLK Low to Address Valid <sup>2</sup>      | t <sub>EAD</sub>  | _   | 60  | ns               |

| E2  | ECLK Low to Address Hold                    | t <sub>EAH</sub>  | 15  | _   | ns               |

| E3  | ECLK Low to CS Valid (CS Delay)             | t <sub>ECSD</sub> | _   | 150 | ns               |

| E4  | ECLK Low to CS Hold                         | t <sub>ECSH</sub> | 15  | _   | ns               |

| E5  | CS Negated Width                            | t <sub>ECSN</sub> | 30  | _   | ns               |

| E6  | Read Data Setup Time                        | t <sub>EDSR</sub> | 30  | _   | ns               |

| E7  | Read Data Hold Time                         | t <sub>EDHR</sub> | 5   | _   | ns               |

| E8  | ECLK Low to Data High Impedance             | t <sub>EDHZ</sub> | _   | 60  | ns               |

| E9  | CS Negated to Data Hold (Read)              | t <sub>ECDH</sub> | 0   | _   | ns               |

| E10 | CS Negated to Data High Impedance           | t <sub>ECDZ</sub> | _   | 1   | t <sub>cyc</sub> |

| E11 | ECLK Low to Data Valid (Write)              | t <sub>EDDW</sub> | _   | 2   | t <sub>cyc</sub> |

| E12 | ECLK Low to Data Hold (Write)               | t <sub>EDHW</sub> | 15  | _   | ns               |

| E13 | Address Access Time (Read) <sup>3</sup>     | t <sub>EACC</sub> | 386 | _   | ns               |

| E14 | Chip-Select Access Time (Read) <sup>4</sup> | t <sub>EACS</sub> | 296 | _   | ns               |

| E15 | Address Setup Time                          | t <sub>EAS</sub>  | 1/2 | _   | t <sub>cyc</sub> |

### NOTES:

- 1. All AC timing is shown with respect to 20%  $\rm V_{DD}$  and 70%  $\rm V_{DD}$  levels unless otherwise noted.

- 2. When previous bus cycle is not an ECLK cycle, the address may be valid before ECLK goes low.

- 3. Address access time =  $t_{Ecyc} t_{EAD} t_{EDSR}$ .

- 4. Chip select access time =  $t_{Ecyc} t_{ECSD} t_{EDSR}$ .

**Figure 15 ECLK Timing Diagram**

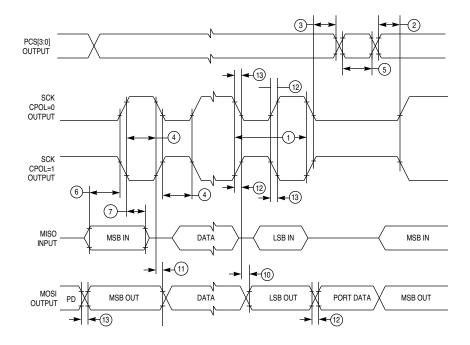

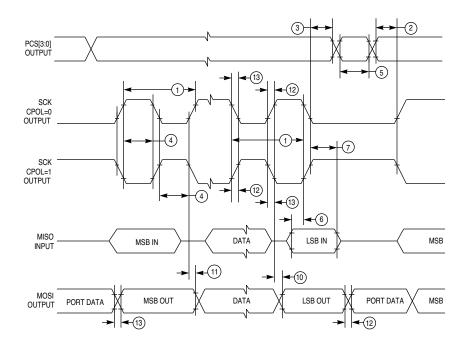

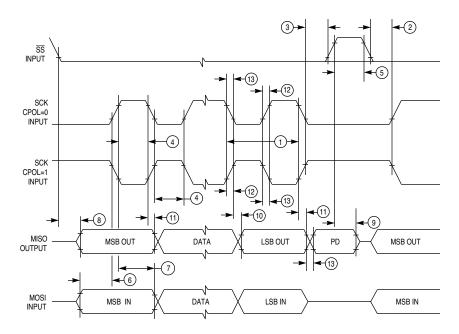

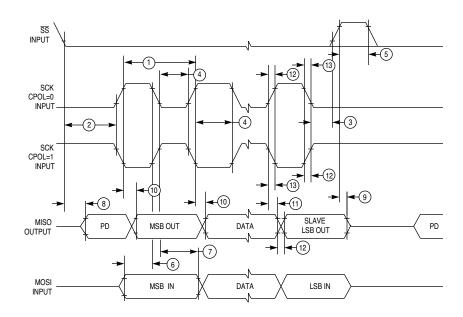

### **Table 9 QSPI Timing**

$(V_{DD} \text{ and } V_{DDSYN} = 2.7 \text{ to } 3.6 \text{ Vdc}, V_{SS} = 0 \text{ Vdc}, T_A = T_L \text{ to } T_H$  , 80 pF load on all QSPI pins)<sup>1</sup>

| Num | Function                                                                 | Symbol                             | Min                                               | Max                  | Unit                                 |

|-----|--------------------------------------------------------------------------|------------------------------------|---------------------------------------------------|----------------------|--------------------------------------|

| 1   | Operating Frequency<br>Master<br>Slave                                   | f <sub>op</sub>                    | DC<br>DC                                          | 1/4<br>1/4           | f <sub>sys</sub><br>f <sub>sys</sub> |

| 2   | Cycle Time<br>Master<br>Slave                                            | t <sub>qcyc</sub>                  | 4<br>4                                            | 510<br>—             | t <sub>cyc</sub><br>t <sub>cyc</sub> |

| 3   | Enable Lead Time<br>Master<br>Slave                                      | t <sub>lead</sub>                  | 2<br>2                                            | 128<br>—             | t <sub>cyc</sub><br>t <sub>cyc</sub> |

| 4   | Enable Lag Time<br>Master<br>Slave                                       | t <sub>lag</sub>                   |                                                   | 1/2<br>—             | SCK<br>t <sub>cyc</sub>              |

| 5   | Clock (SCK) High or Low Time<br>Master<br>Slave <sup>2</sup>             | t <sub>sw</sub>                    | 2 t <sub>cyc</sub> – 60<br>2 t <sub>cyc</sub> – n | 255 t <sub>cyc</sub> | ns<br>ns                             |

| 6   | Sequential Transfer Delay<br>Master<br>Slave (Does Not Require Deselect) | t <sub>td</sub>                    | 17<br>13                                          | 8192<br>—            | t <sub>cyc</sub><br>t <sub>cyc</sub> |

| 7   | Data Setup Time (Inputs) Master Slave                                    | t <sub>su</sub>                    | 30<br>20                                          | _                    | ns<br>ns                             |

| 8   | Data Hold Time (Inputs)<br>Master<br>Slave                               | t <sub>hi</sub>                    | 0<br>20                                           | _                    | ns<br>ns                             |

| 9   | Slave Access Time                                                        | t <sub>a</sub>                     | _                                                 | 1                    | t <sub>cyc</sub>                     |

| 10  | Slave MISO Disable Time                                                  | t <sub>dis</sub>                   | _                                                 | 2                    | t <sub>cyc</sub>                     |

| 11  | Data Valid (after SCK Edge)<br>Master<br>Slave                           | t <sub>v</sub>                     |                                                   | 50<br>50             | ns<br>ns                             |

| 12  | Data Hold Time (Outputs)  Master Slave                                   | t <sub>ho</sub>                    | 0<br>0                                            |                      | ns<br>ns                             |

| 13  | Rise Time<br>Input<br>Output                                             | t <sub>ri</sub><br>t <sub>ro</sub> | _                                                 | 2<br>30              | μs<br>ns                             |

| 14  | Fall Time<br>Input<br>Output                                             | t <sub>fi</sub><br>t <sub>fo</sub> |                                                   | 2<br>30              | μs<br>ns                             |

#### NOTES

- 1. All AC timing is shown with respect to 20%  $\rm V_{DD}$  and 70%  $\rm V_{DD}$  levels unless otherwise noted.

- 2. For high time, n = external SCK rise time; for low time, n = external SCK fall time.

68300 QSPI MAST CPHA0

Figure 16 QSPI Timing — Master, CPHA = 0

68300 QSPI MAST CPHA1

Figure 17 QSPI Timing — Master, CPHA = 1

68300 QSPI SLV CPHA0

Figure 18 QSPI Timing — Slave, CPHA = 0

68300 QSPI SLV CPHA1

Figure 19 QSPI Timing — Slave, CPHA = 1

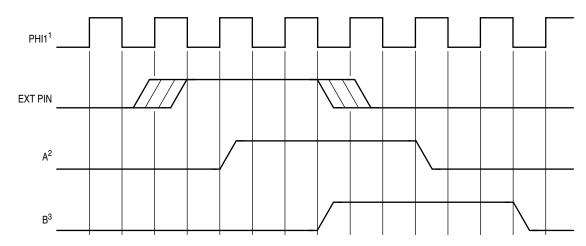

**Table 10 General-Purpose Timer AC Characteristics**

| Num | Parameter                 | Symbol | Min      | Max        | Unit |

|-----|---------------------------|--------|----------|------------|------|

| 1   | Operating Frequency       | Fclock | 0        | 16.78      | MHz  |

| 2   | PCLK Frequency            | Fpclk  | 0        | 1/4 Fclock | MHz  |

| 3   | Pulse Width Input Capture | PWtim  | 2/Fclock | _          | _    |

| 4   | PWM Resolution            | _      | 2/Fclock | _          | _    |

| 5   | IC/OC Resolution          | _      | 4/Fclock | _          | _    |

| 6   | PCLK Width (PWM)          | _      | 4/Fclock | _          | _    |

| 7   | PCLK Width (IC/OC)        | _      | 4/Fclock | _          | _    |

| 8   | PAI Pulse Width           | _      | 2/Fclock | _          | _    |

#### NOTES:

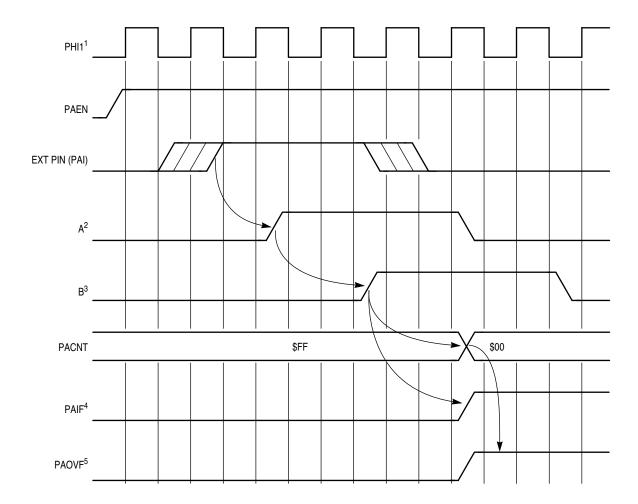

- 1. PHI1 IS THE SAME FREQUENCY AS THE SYSTEM CLOCK; HOWEVER, IT DOES NOT HAVE THE SAME TIMING. 2. A = INPUT SIGNAL AFTER THE SYNCHRONIZER.

- 3. B = "A" AFTER THE DIGITAL FILTER.

INPUT SIG CONDITIONER TIM

**Figure 20 Input Signal Conditioner Timing**

#### NOTES:

- 1. PHI1 IS THE SAME FREQUENCY AS THE SYSTEM CLOCK; HOWEVER, IT DOES NOT HAVE THE SAME TIMING.

- 2. A = PAI SIGNAL AFTER THE SYNCHRONIZER.

- 3. B = "A" AFTER THE DIGITAL FILTER.

- 4. THE EXTERNAL LEADING EDGE CAUSES THE PULSE ACCUMULATOR TO INCREMENT AND THE PAIF FLAG TO BE SET.

- 5. THE COUNTER TRANSITION FROM \$FF TO \$00 CAUSES THE PAOVF FLAG TO BE SET.

PULSE ACCUM ECM LEAD EDGE

Figure 21 Pulse Accumulator —Event Counting Mode (Leading Edge)

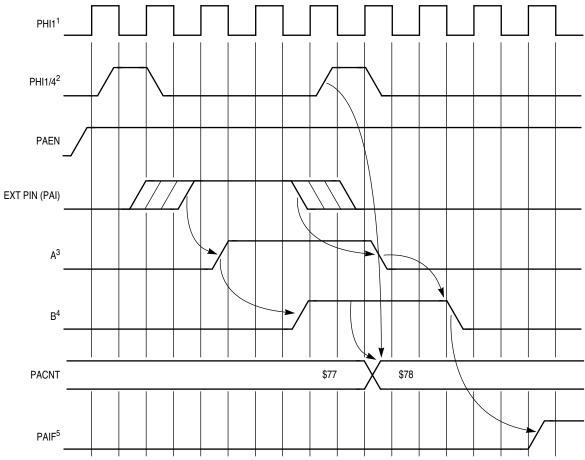

### NOTES:

- 1. PHI1 HAS THE SAME FREQUENCY AS THE SYSTEM CLOCK; HOWEVER, IT DOES NOT HAVE THE SAME TIMING.

- 2. PHI1/4 CLOCKS PACNT WHEN GT-PAIF IS ASSERTED.

3. A = PAI SIGNAL AFTER THE SYNCHRONIZER.

- 4. B = "A" AFTER THE DIGITAL FILTER.

- 5. PAIF IS ASSERTED WHEN PAI IS NEGATED.

PULSE ACCUM GATED MODE

Figure 22 Pulse Accumulator —Gated Mode (Count While Pin High)

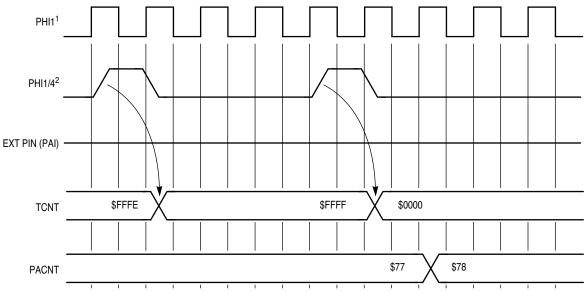

#### NOTES:

- 1. PHI1 HAS THE SAME FREQUENCY AS THE SYSTEM CLOCK; HOWEVER, IT DOES NOT HAVE THE SAME TIMING.

- 2. TCNT COUNTS AS A RESULT OF PHI1/4; PACNT COUNTS WHEN TCNT OVERFLOWS FROM \$FFFF TO \$0000 AND THE CONDITIONED PAI SIGNAL IS ASSERTED.

PULSE ACCUM TOF GATED MODE

Figure 23 Pulse Accumulator —Using TOF as Gated Mode Clock

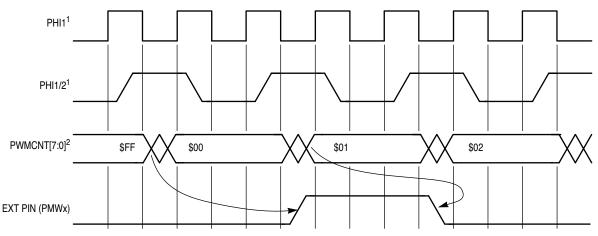

#### NOTES:

- 1. PHI1 IS THE SAME FREQUENCY AS THE SYSTEM CLOCK; HOWEVER, IT DOES NOT HAVE THE SAME TIMING.

- WHEN THE COUNTER ROLLS OVER FROM \$FF TO \$00, THE PWM PIN IS SET TO LOGIC LEVEL ONE.

WHEN THE COUNTER EQUALS THE PWM REGISTER, THE PWM PIN IS CLEARED TO A LOGIC LEVEL ZERO.

PWMx FAST MODE

Figure 24 PWMx (PWMx Register = 01, Fast Mode)

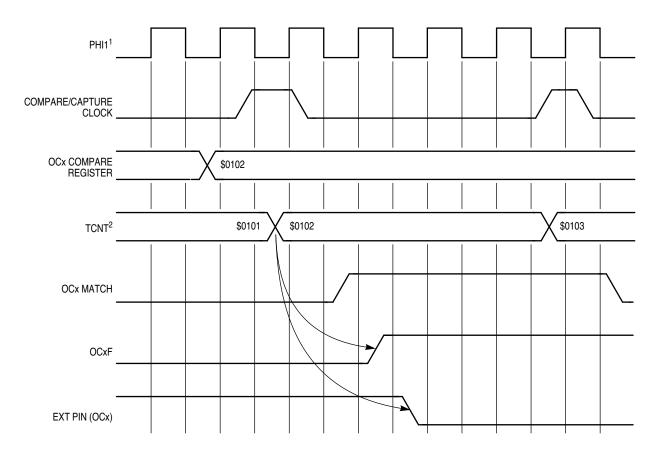

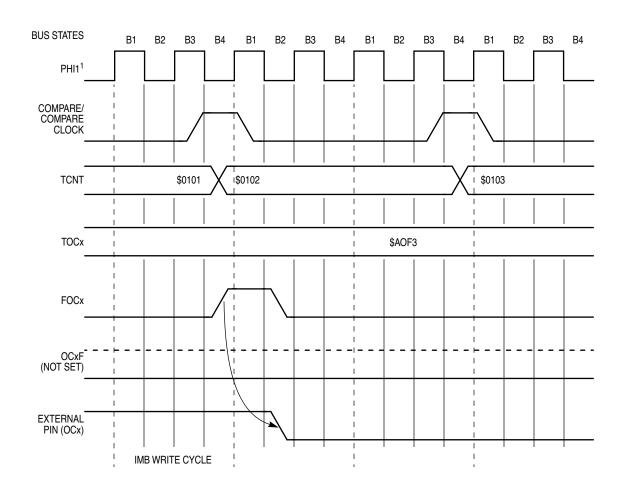

#### NOTES:

- 1. PHI1 IS THE SAME FREQUENCY AS THE SYSTEM CLOCK; HOWEVER, IT DOES NOT HAVE THE SAME TIMING.

2. WHEN THE TCNT MATCHES THE OCX COMPARE REGISTER, THE OCX FLAG IS SET FOLLOWED BY THE OCX PIN CHANGING STATE.

OUTPUT COMPARE

Figure 25 Output Compare (Toggle Pin State)

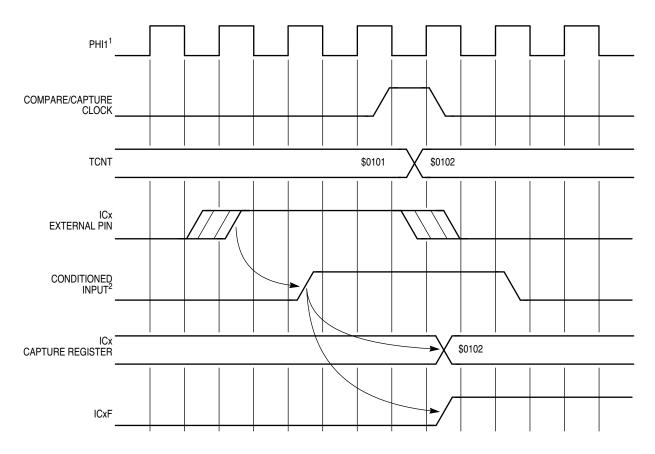

#### NOTES:

- 1. PHI1 IS THE SAME FREQUENCY AS THE SYSTEM CLOCK; HOWEVER, IT DOES NOT HAVE THE SAME TIMING.

- 2. THE CONDITIONED INPUT SIGNAL CAUSES THE CURRENT VALUE OF THE TONT TO BE LATCHED BY THE ICX CAPTURE REGISTER. THE ICXF FLAG IS SET AT THE SAME TIME.

INPUT CAPTURE

Figure 26 Input Capture (Capture on Rising Edge

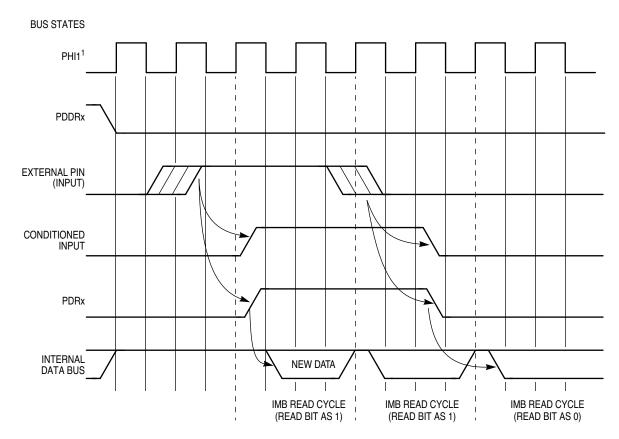

NOTES:

1. PHI1 IS THE SAME FREQUENCY AS THE SYSTEM CLOCK; HOWEVER, IT DOES NOT HAVE THE SAME TIMING.

GENERAL PURPOSE INPUT

Figure 27 General-Purpose Input

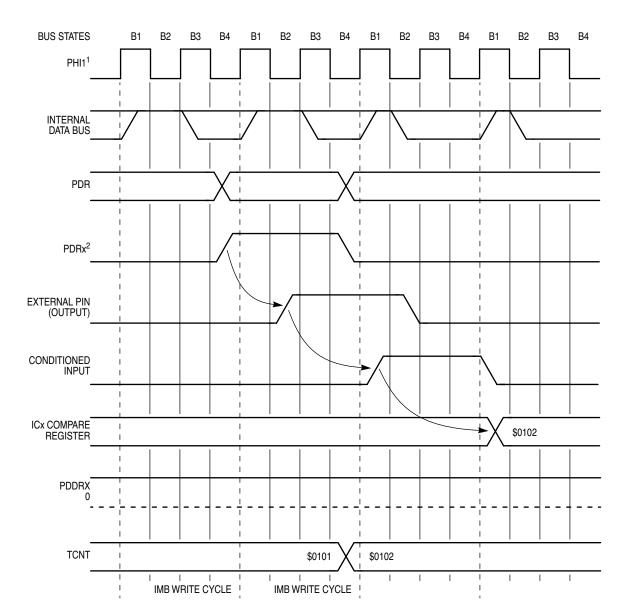

#### NOTES:

PHI1 IS THE SAME FREQUENCY AS THE SYSTEM CLOCK; HOWEVER, IT DOES NOT HAVE THE SAME TIMING.

WHEN THE BIT VALUE IS DRIVEN ON THE PIN, THE INPUT CIRCUIT SEES THE SIGNAL. AFTER IT IS CONDITIONED, IT CAUSES THE CONTENTS OF THE TCNT TO BE LATCHED INTO THE ICX COMPARE REGISTER.

GENERAL PURPOSE OUTPUT

Figure 28 General-Purpose Output (Causes Input Capture)

NOTES:

1. PHI1 IS THE SAME FREQUENCY AS THE SYSTEM CLOCK; HOWEVER, IT DOES NOT HAVE THE SAME TIMING.

FORCE COMPARE

Figure 29 Force Compare (CLEAR)

Figure 30 MC68CK331 Pin Assignments for 100-Pin Package

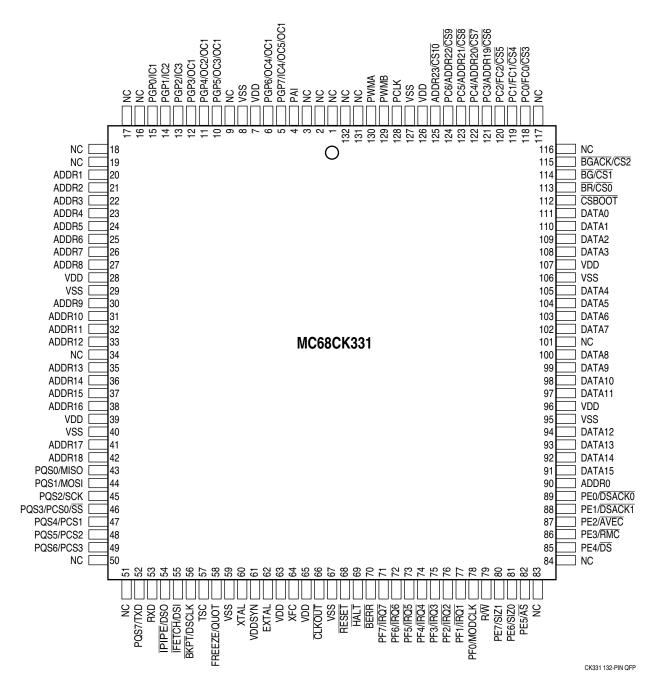

Figure 31 MC68CK331 Pin Assignments for 132-Pin Package

Figure 32 MC68CK331 Pin Assignments for 144-Pin Package

Table 11 MC68CK331PU 100-Pin TQFP Pin Assignments

| Pin | Description      | Pin | Description     | Pin | Description        | Pin | Description     |

|-----|------------------|-----|-----------------|-----|--------------------|-----|-----------------|

| 1   | DATA0            | 26  | ADDR6           | 51  | RXD                | 76  | PE5/AS          |

| 2   | CSBOOT           | 27  | ADDR7           | 52  | ĪPIPĒ/DSO          | 77  | PE4/DS          |

| 3   | BR/CS0           | 28  | ADDR8           | 53  | ĪFETCH/DSI         | 78  | PE3/RMC         |

| 4   | BG/CS0           | 29  | ADDR9           | 54  | BKPT/DSCLK         | 79  | PE1/DSACK1      |

| 5   | BGACK/CS2        | 30  | ADDR10          | 55  | TSC                | 80  | PE0/DSACK0      |

| 6   | PC0/FC0/CS3      | 31  | ADDR11          | 56  | FREEZE/QUOT        | 81  | ADDR0           |

| 7   | PC1/FC1/CS4      | 32  | ADDR12          | 57  | V <sub>SS</sub>    | 82  | DATA15          |

| 8   | PC2/FC2/CS5      | 33  | $V_{DD}$        | 58  | $V_{DD}$           | 83  | V <sub>SS</sub> |

| 9   | PC3/ADDR19/CS6   | 34  | V <sub>SS</sub> | 59  | V <sub>DDSYN</sub> | 84  | V <sub>DD</sub> |

| 10  | PC4/ADDR20/CS7   | 35  | ADDR13          | 60  | EXTAL              | 85  | DATA14          |

| 11  | PC5/ADDR21/CS8   | 36  | ADDR14          | 61  | $V_{DD}$           | 86  | DATA13          |

| 12  | PC6/ADDR22/CS9   | 37  | ADDR15          | 62  | XFC                | 87  | DATA12          |

| 13  | ADDR23/CS10      | 38  | ADDR16          | 63  | $V_{DD}$           | 88  | DATA11          |

| 14  | $V_{DD}$         | 39  | ADDR17          | 64  | CLKOUT             | 89  | DATA10          |

| 15  | V <sub>SS</sub>  | 40  | ADDR18          | 65  | V <sub>SS</sub>    | 90  | DATA9           |

| 16  | PWMB             | 41  | PQS0/MISO       | 66  | RESET              | 91  | DATA8           |

| 17  | PWMA             | 42  | VDD             | 67  | BERR               | 92  | V <sub>SS</sub> |

| 18  | PGP7/IC4/OC5/OC1 | 43  | VSS             | 68  | PF7/IRQ7           | 93  | V <sub>DD</sub> |

| 19  | PGP4/OC2/OC1     | 44  | PQS1/MOSI       | 69  | PF6/IRQ6           | 94  | DATA7           |

| 20  | PGP0/IC1         | 45  | PQS2/SCK        | 70  | PF5/IRQ5           | 95  | DATA6           |

| 21  | ADDR1            | 46  | PQS3/PCS0/SS    | 71  | PF4/IRQ4           | 96  | DATA5           |

| 22  | ADDR2            | 47  | PQS4/PCS1       | 72  | PF0/MODCLK         | 97  | DATA4           |

| 23  | ADDR3            | 48  | PQS5/PCS2       | 73  | R/W                | 98  | DATA3           |

| 24  | ADDR4            | 49  | PQS6/PCS3       | 74  | PE7/SIZ1           | 99  | DATA2           |

| 25  | ADDR5            | 50  | PQS7/TXD        | 75  | PE6/SIZ0           | 100 | DATA1           |

Table 12 MC68CK331PU Deleted Function Pin List

| Module | Description | Tied | Lost Function                       |

|--------|-------------|------|-------------------------------------|

| SIM    | HALT        | High | Single-step, double bus fault       |

|        | PE2/AVEC    | High | Must use chip-select for AVEC       |

|        | PF3/IRQ3    | High | Level 3 interrupt request, port pin |

|        | PF2/IRQ2    | High | Level 2 interrupt request, port pin |

|        | PF1/IRQ1    | High | Level 1 interrupt request, port pin |

| GPT    | PGP1/IC2    | High | Input capture pin                   |

|        | PGP2/IC3    | High | Input capture pin                   |

|        | PGP3/OC1    | High | Output compare pin                  |

|        | PGP5/OC3    | High | Output compare pin                  |

|        | PGP6/OC4    | High | Output compare pin                  |

|        | PAI         | High | Pulse accumulator input             |

|        | PCLK        | High | External GPT clock reference        |

Home Page: www.freescale.com

support@freescale.com

USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German)

+33 1 69 35 48 48 (French) support@freescale.com

Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate,

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150

**LDCForFreescaleSemiconductor**

@hibbertgroup.com

RoHS-compliant and/or Pb- free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb- free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale.s Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.