### MC68HC05P4

# Addendum to MC68HC05P4 HCMOS Microcontroller Unit Technical Data

This addendum supplements *MC68HC05P4 Technical Data* (Motorola document number MC68HC05P4/D) with the following additional information:

- DC Electrical Characteristics

- MC68HCL05P4 data APPENDIX A contains data for the MC68HCL05P4, a low-power version of the MC68HC05P4

- MC68HSC05P4 data APPENDIX B contains data for the MC68HSC05P4, a high-speed version

of the MC68HC05P4

#### 9.4 DC ELECTRICAL CHARACTERISTICS

The following table replaces Table 9-3 in MC68HC05P4 Technical Data.

Table 9-3. DC Electrical Characteristics ( $V_{DD}$  = 5.0 Vdc  $\pm$  10%)

| Characteristic                                                                                        | Symbol                              | Min                       | Typ <sup>(1)</sup> | Max                     | Unit                 |

|-------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------|--------------------|-------------------------|----------------------|

| Output Voltage<br>I <sub>LOAD</sub> = 10.0 μA<br>I <sub>LOAD</sub> = -10.0 μA                         | V <sub>OL</sub><br>V <sub>OH</sub>  | <br>V <sub>DD</sub> - 0.1 |                    | 0.1<br>—                | V<br>V               |

| Output High Voltage (I <sub>LOAD</sub> = -0.8 mA) PA7-PA0, PB7-PB5, PC7-PC0, PD5, TCMP                | V <sub>OH</sub>                     | V <sub>DD</sub> - 0.8     | _                  |                         | V                    |

| Output Low Voltage (I <sub>LOAD</sub> = 1.6 mA)<br>PA7-PA0, PB7-PB5, PC7-PC0, PD5,<br>TCMP            | VaL                                 | _                         | -                  | 0.4                     | ٧                    |

| Input High Voltage PA7-PA0, PB7-PB5, PC7-PC0, PD5, PD7/TCAP, IRQ, RESET, OSC1                         | V <sub>IH</sub>                     | 0.7 × V <sub>DD</sub>     |                    | V <sub>DD</sub>         | V                    |

| Input Low Voltage PA7-PA0, PB7-PB5, PC7-PC0, PD5, PD7/TCAP, IRQ, RESET, OSC1                          | V <sub>IL</sub>                     | V <sub>ss</sub>           | _                  | 0.2 × V <sub>DD</sub>   | v                    |

| Data-Retention Mode Supply Voltage                                                                    | V <sub>RM</sub>                     | 2                         | _                  |                         | V                    |

| Supply Current Run <sup>(2)</sup> WAIT <sup>(3)</sup> STOP <sup>(4)</sup> 25 °C 0 to 70 °C (Standard) | I <sub>DD</sub>                     | _<br>_<br>_               | 3.1<br>1.1<br>2.25 | 7.0<br>4.0<br>50<br>140 | mA<br>mA<br>μA<br>μA |

| I/O Ports High-Z Leakage Current<br>PA7-PA0, PB7-PB5, PC7-PC0, PD5                                    | I <sub>IL</sub>                     | _                         | _                  | ±10                     | μΑ                   |

| Input Current<br>RESET, IRQ, OSC1, PD7/TCAP                                                           | I <sub>IN</sub>                     |                           | _                  | ±1                      | μΑ                   |

| Capacitance Ports (Input or Output) RESET, IRQ, PD5, PD7/TCAP                                         | C <sub>OUT</sub><br>C <sub>IN</sub> |                           |                    | 12<br>8                 | pF<br>pF             |

<sup>1.</sup> Typical values at midpoint of voltage range, 25 °C only.

<sup>2.</sup> Run (operating)  $I_{DD}$  measured using external square wave clock source ( $f_{OSC} = 4.2$  MHz). All inputs 0.2 V from rail. No dc loads. Less than 50 pF on all outputs.  $C_L = 20$  pF on OSC2.

<sup>3.</sup> WAIT  $I_{DD}$  measured using external square wave clock source ( $f_{OSC}$  = 4.2 MHz). All inputs 0.2 V from rail. No dc loads. Less than 50 pF on all outputs. CL = 20 pF on OSC2. All ports configured as inputs.  $V_{IL}$  = 0.2 V.  $V_{IH} = V_{DD}$  - 0.2 V. OSC2 capacitance linearly affects WAIT  $I_{DD}$ . 4. STOP  $I_{DD}$  measured with OSC1 =  $V_{SS}$ . All ports configured as inputs.  $V_{IL} = 0.2$  V.  $V_{IH} = V_{DD}$  - 0.2 V.

The following table replaces Table 9-4 in MC68HC05P4 Technical Data.

Table 9-4. DC Electrical Characteristics ( $V_{DD} = 3.3 \text{ Vdc} \pm 10\%$ )

| Characteristic                                                                                        | Symbol                              | Min                       | Typ <sup>(1)</sup>      | Max                    | Unit                 |

|-------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------|-------------------------|------------------------|----------------------|

| Output Voltage<br>I <sub>LOAD</sub> = 10.0 μA<br>I <sub>LOAD</sub> = -10.0 μA                         | V <sub>OL</sub><br>V <sub>OH</sub>  | <br>V <sub>DD</sub> - 0.1 | <u>-</u>                | 0.1<br>—               | v<br>v               |

| Output High Voltage (I <sub>LOAD</sub> = -0.2 mA)<br>PA7-PA0, PB7-PB5, PC7-PC0, PD5,<br>TCMP          | V <sub>OH</sub>                     | V <sub>DD</sub> - 0.3     | _                       | _                      | V                    |

| Output Low Voltage (I <sub>LOAD</sub> = 0.4 mA)<br>PA7-PA0, PB7-PB5, PC7-PC0, PD5,<br>TCMP            | V <sub>OL</sub>                     | _                         | -                       | 0.3                    | V                    |

| Input High Voltage PA7-PA0, PB7-PB5, PC7-PC0, PD5, PD7/TCAP, IRQ, RESET, OSC1                         | V <sub>IH</sub>                     | 0.7 × V <sub>DD</sub>     | _                       | V <sub>DD</sub>        | V                    |

| Input Low Voltage PA7-PA0, PB7-PB5, PC7-PC0, PD5, PD7/TCAP, IRQ, RESET, OSC1                          | V <sub>IL</sub>                     | V <sub>ss</sub>           | -                       | 0.2 × V <sub>DD</sub>  | V                    |

| Supply Current Run <sup>(2)</sup> WAIT <sup>(3)</sup> STOP <sup>(4)</sup> 25 °C 0 to 70 °C (Standard) | I <sub>DD</sub>                     | _<br>_<br>_               | 0.8<br>0.35<br>0.6<br>— | 2.5<br>1.4<br>30<br>80 | mA<br>mA<br>μA<br>μA |

| I/O Ports High-Z Leakage Current<br>PA7-PA0, PB7-PB5, PC7-PC0, PD5                                    | I <sub>IL</sub>                     |                           |                         | ±10                    | μА                   |

| Input Current<br>RESET, IRQ, OSC1, PD7/TCAP                                                           | I <sub>IN</sub>                     |                           |                         | ±1                     | μА                   |

| Capacitance Ports (Input or Output) RESET, IRQ, PD5, PD7/TCAP                                         | C <sub>OUT</sub><br>C <sub>IN</sub> | _                         | _                       | 12<br>8                | pF<br>pF             |

<sup>1.</sup> Typical values at midpoint of voltage range, 25 °C only.

4. STOP  $I_{DD}$  measured with OSC1 =  $V_{SS}$ . All ports configured as inputs.  $V_{IL}$  = 0.2 V.  $V_{IH}$  =  $V_{DD}$  - 0.2 V.

REV. 1

<sup>2.</sup> Run (operating)  $I_{DD}$  measured using external square wave clock source ( $f_{OSC} = 2.1$  MHz). All inputs 0.2 V from rail. No dc loads. Less than 50 pF on all outputs.  $C_L = 20$  pF on OSC2.

<sup>3.</sup> WAIT  $I_{DD}$  measured using external square wave clock source ( $f_{OSC}$  = 2.1 MHz). All inputs 0.2 V from rail. No dc loads. Less than 50 pF on all outputs.  $C_L$  = 20 pF on OSC2. All ports configured as inputs.  $V_{IL}$  = 0.2 V.  $V_{IH}$  =  $V_{DD}$  - 0.2 V. OSC2 capacitance linearly affects WAIT  $I_{DD}$ .

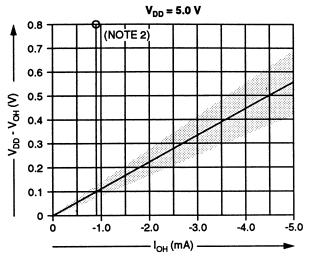

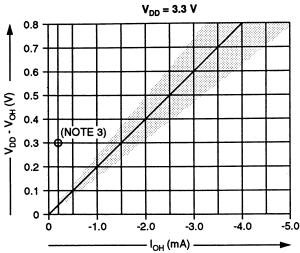

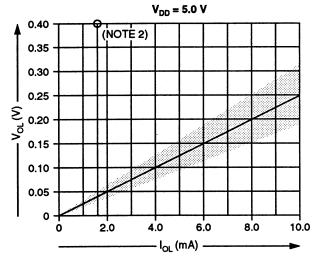

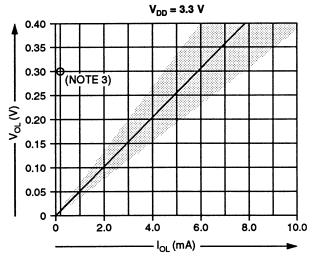

The following figures replace Figure 9-2 and Figure 9-3 of MC68HC05P4 Technical Data.

#### NOTES:

- 1. Shaded area indicates variation in driver characteristics due to changes in temperature and for normal processing tolerances. Within the limited range of values shown, V vs I curves are approximately straight lines.

- 2. At  $V_{DD}$  = 5.0 V, devices are specified and tested for  $V_{OH} \ge V_{DD}$  800 mV @  $I_{OH}$  = -0.8 mA.

- 3. At  $V_{DD}$  = 3.3 V, devices are specified and tested for  $V_{OH} \ge V_{DD}$  300 mV @  $I_{OH}$  = -0.2 mA.

Figure 9-2. Typical High-Side Driver Characteristics

#### NOTES:

- 1. Shaded area indicates variation in driver characteristics due to changes in temperature and for normal processing tolerances. Within the limited range of values shown, V vs I curves are approximately straight lines.

- 2. At  $V_{DD}$  = 5.0 V, devices are specified and tested for  $V_{OL} \le 400$  mV @  $I_{OL}$  = 1.6 mA.

- 3. At  $V_{DD}$  = 3.3 V, devices are specified and tested for  $V_{OL} \le$  300 mV @  $I_{OL}$  = 0.4 mA.

Figure 9-3. Typical Low-Side Driver Characteristics

# NP

## Freescale Semiconductor, Inc.

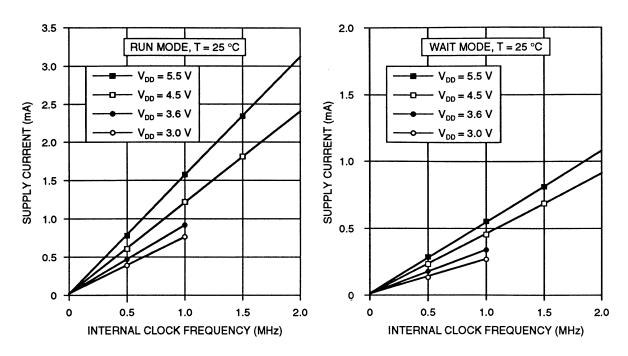

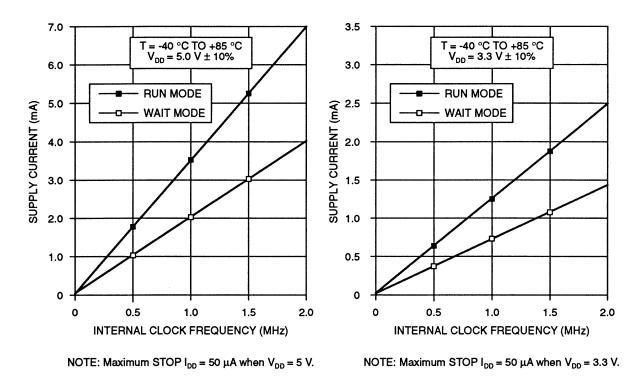

The following figures replace Figure 9-4 and Figure 9-5 in MC68HC04P4 Technical Data.

Figure 9-4. Typical Supply Current vs Internal Clock Frequency

Figure 9-5. Maximum Supply Current vs Internal Clock Frequency

# APPENDIX A MC68HCL05P4

This appendix introduces the MC68HCL05P4, a low-power version of the MC68HC05P4. All of the information in *MC68HC05P4 Technical Data* applies to the MC68HCL05P4 with the exceptions given in this appendix.

#### A.1 DC ELECTRICAL CHARACTERISTICS

The data given in Table 9-3 and Table 9-4 of MC68HC05P4 Technical Data applies to the MC68HCL05P4 with the exceptions given in Table A-1, Table A-2, and Table A-3.

Table A-1. Low-Power Output Voltage ( $V_{DD} = 1.8-2.4 \text{ Vdc}$ )

| Characteristic                                                                            | Symbol          | Min                   | Тур | Max | Unit     |

|-------------------------------------------------------------------------------------------|-----------------|-----------------------|-----|-----|----------|

| Output High Voltage (I <sub>LOAD</sub> = -0.1 mA)<br>PA7-PA0, PB7-PB5, PC7-PC0, PD5, TCMP | V <sub>OH</sub> | V <sub>DD</sub> - 0.3 |     | _   | <b>v</b> |

| Output Low Voltage (I <sub>LOAD</sub> = 0.2 mA)<br>PA7–PA0, PB7–PB5, PC7–PC0, PD5, TCMP   | V <sub>OL</sub> | _                     |     | 0.3 | ٧        |

Table A-2. Low-Power Output Voltage ( $V_{DD} = 2.5-3.6 \text{ Vdc}$ )

| Characteristic                                                                            | Symbol          | Min                   | Тур | Max | Unit |

|-------------------------------------------------------------------------------------------|-----------------|-----------------------|-----|-----|------|

| Output High Voltage (I <sub>LOAD</sub> = -0.2 mA)<br>PA7-PA0, PB7-PB5, PC5-PC0, PD5, TCMP | V <sub>OH</sub> | V <sub>DD</sub> - 0.3 |     | _   | V    |

| Output Low Voltage (I <sub>LOAD</sub> = 0.4 mA)<br>PA7-PA0, PB7-PB5, PC5-PC0, PD5, TCMP   | V <sub>OL</sub> |                       |     | 0.3 | V    |

**Table A-3. Low-Power Supply Current**

| Characteristic                                                                                                                                                      | Symbol          | Min           | Typ <sup>(1)</sup> | Max                       | Unit                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|--------------------|---------------------------|----------------------|

| Supply Current (V <sub>DD</sub> = 4.5–5.5 Vdc, f <sub>OP</sub> = 2.1 MHz) Run <sup>(2)</sup> WAIT <sup>(3)</sup> STOP <sup>(4)</sup> 25 °C                          | I <sub>DD</sub> | <u>-</u><br>- | 3.1<br>1.1<br>2.0  | 4.25<br>2.25<br>15        | mA<br>mA<br>μA       |

| 0 °C to 70 °C (Standard)                                                                                                                                            |                 |               | _                  | 25                        | μA                   |

| Supply Current (V <sub>DD</sub> = 2.5–3.6 Vdc, f <sub>OP</sub> = 1.0 MHz) Run <sup>(2)</sup> WAIT <sup>(3)</sup> STOP <sup>(4)</sup> 25 °C 0 °C to 70 °C (Standard) | I <sub>DD</sub> | _<br>_<br>_   | 0.8<br>0.35<br>0.6 | 1.6<br>1.0<br>5.0<br>10.0 | mA<br>mA<br>μA<br>μA |

| Supply Current (V <sub>DD</sub> = 2.5–3.6 Vdc, f <sub>OP</sub> = 500 kHz) Run <sup>(2)</sup> WAIT <sup>(3)</sup> STOP <sup>(4)</sup> 25 °C 0 °C to 70 °C (Standard) | I <sub>DD</sub> | -             | 400<br>200<br>0.6  | 800<br>500<br>5.0<br>10.0 | μΑ<br>μΑ<br>μΑ<br>μΑ |

| Supply Current (V <sub>DD</sub> = 1.8–2.4 Vdc, f <sub>OP</sub> = 500 kHz) Run <sup>(2)</sup> WAIT <sup>(3)</sup> STOP <sup>(4)</sup> 25 °C 0 °C to 70 °C (Standard) | I <sub>DD</sub> | <u>-</u><br>  | 300<br>200<br>0.3  | 600<br>400<br>2.0<br>5.0  | μΑ<br>μΑ<br>μΑ<br>μΑ |

- 1. Typical values reflect average measurements at midpoint of voltage range at 25 °C.

- 2. Run (operating)  $I_{DD}$  measured using external square wave clock source with all inputs 0.2 V from rail. No dc loads. Less than 50 pF on all outputs.  $C_L = 20$  pF on OSC2.

- 3. WAIT  $I_{DD}$  measured using external square wave clock source with all inputs 0.2 V from rail. No dc loads. Less than 50 pF on all outputs.  $C_L = 20$  pF on OSC2. All ports configured as inputs.  $V_{IL} = 0.2$  V,  $V_{IH} = V_{DD}$  0.2 V. OSC2 capacitance linearly affects WAIT  $I_{DD}$ .

- 4. STOP  $I_{DD}$  measured with OSC1 =  $V_{DD}$ . All ports configured as inputs.  $V_{IL}$  = 0.2 V,  $V_{IH}$  =  $V_{DD}$  0.2 V.

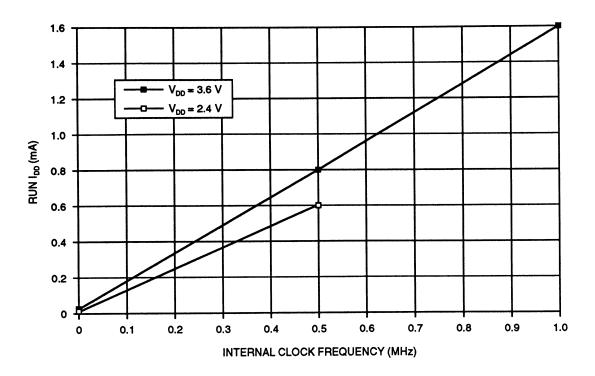

Figure A-1. Maximum Run Mode I<sub>DD</sub> vs Frequency

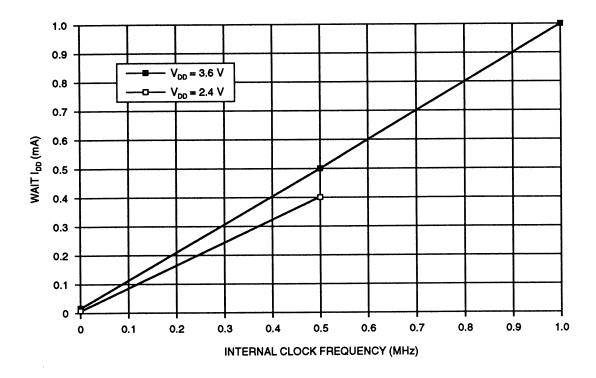

Figure A-2. Maximum WAIT Mode  $I_{\rm DD}$  vs Frequency

#### A.2 MC Ordering Information

Table A-4 provides information for available package types.

**Table A-4. MC Order Numbers**

| Package Type                                   | Temperature    | MC Order Number |

|------------------------------------------------|----------------|-----------------|

| 28-Pin Plastic Dual In-Line Package (DIP)      | 0° C to +70° C | MC68HCL05P4P    |

| 28-Pin Small Outline Integrated Circuit (SOIC) | 0° C to +70° C | MC68HCL05P4DW   |

# APPENDIX B MC68HSC05P4

This appendix introduces the MC68HSC05P4, a high-speed version of the MC68HC05P4. All of the information in *MC68HC05P4 Technical Data* applies to the MC68HSC05P4 with the exceptions given in this appendix.

#### **B.1 DC ELECTRICAL CHARACTERISTICS**

The data in Table 9-3 and Table 9-4 of MC68HC05P4 Technical Data applies to the MC68HSC05P4 with the exceptions given in Table B-1.

Table B-1. High-Speed Supply Current

| Characteristic                                                                                                                                             | Symbol          | Min         | Typ <sup>(1)</sup>     | Max                     | Unit                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|------------------------|-------------------------|----------------------|

| Supply Current ( $V_{DD}$ = 4.5–5.5 Vdc, $f_{OP}$ = 4.0 MHz)<br>Run <sup>(2)</sup><br>WAIT <sup>(3)</sup><br>STOP <sup>(4)</sup><br>25 °C<br>-40 to +85 °C | I <sub>DD</sub> | . 1 1 1 1   | 7.0<br>2.0<br>2.0<br>— | 9.0<br>5.0<br>15<br>28  | mA<br>mA<br>μA<br>μA |

| Supply Current ( $V_{DD}$ = 3.0–3.6 Vdc, $f_{OP}$ = 2.1 MHz)<br>Run <sup>(2)</sup><br>WAIT <sup>(3)</sup><br>STOP <sup>(4)</sup><br>25 °C<br>-40 to +85 °C | I <sub>DD</sub> | _<br>_<br>_ | 1.8<br>0.8<br>0.6      | 5.0<br>2.5<br>5.0<br>12 | mA<br>mA<br>μΑ<br>μΑ |

- 1. Typical values at midpoint of voltage range, 25 °C only.

- 2. Run (operating)  $I_{DD}$  measured using external square wave clock source with all inputs 0.2 V from rail. No dc loads. Less than 50 pF on all outputs.  $C_L = 20$  pF on OSC2.

- 3. WAIT  $I_{DD}$  measured using external square wave clock source with all inputs 0.2 V from rail. No dc loads. Less than 50 pF on all outputs.  $C_L = 20$  pF on OSC2. All ports configured as inputs;  $V_{IL} = 0.2$  V,  $V_{IH} = V_{DD}$  0.2 V. OSC2 capacitance linearly affects WAIT  $I_{DD}$ .

- 4. STOP  $I_{DD}$  measured with OSC1 =  $V_{DD}$ . All ports configured as inputs.  $V_{IL}$  = 0.2 V,  $V_{IH}$  =  $V_{DD}$  0.2 V.

#### **B.2 CONTROL TIMING**

The data given in Table 9-5 and Table 9-6 of MC68HC05P4 Technical Data applies to the MC68HSC05P4 with the exceptions given in Table B-2 and Table B-3.

Table B-2. High-Speed Control Timing ( $V_{DD}$  = 5.0 V  $\pm$  10%)

| Characteristic                                                                               | Symbol                            | Min | Max        | Unit       |

|----------------------------------------------------------------------------------------------|-----------------------------------|-----|------------|------------|

| Oscillator Frequency Crystal Oscillator External Clock                                       | fosc                              | dc  | 8.0<br>8.0 | MHz<br>MHz |

| Internal Operating Frequency (f <sub>OSC</sub> + 2) Crystal Oscillator External Clock Option | f <sub>OP</sub>                   | dc  | 4.0<br>4.0 | MHz<br>MHz |

| Internal Clock Cycle Time                                                                    | t <sub>cyc</sub>                  | 250 |            | ns         |

| Capture/Compare Timer<br>Input Capture Pulse Width                                           | t <sub>TH</sub> , t <sub>TL</sub> | 63  | ·          | ns         |

| Interrupt Pulse Width Low (Edge-Triggered)                                                   | t <sub>ILIL</sub>                 | 63  |            | ns         |

| OSC1 Pulse Width                                                                             | t <sub>OH</sub> , t <sub>OL</sub> | 45  |            | ns         |

Table B-3. High-Speed Control Timing ( $V_{DD}$  = 3.3 V  $\pm$  10%)

| Characteristic                                                                                     | Symbol                            | Min | Max        | Unit       |

|----------------------------------------------------------------------------------------------------|-----------------------------------|-----|------------|------------|

| Oscillator Frequency<br>Crystal Oscillator<br>External Clock                                       | f <sub>osc</sub>                  | dc  | 4.2<br>4.2 | MHz<br>MHz |

| Internal Operating Frequency (f <sub>OSC</sub> + 2)<br>Crystal Oscillator<br>External Clock Option | f <sub>OP</sub>                   | dc  | 2.1<br>2.1 | MHz<br>MHz |

| Internal Clock Cycle Time                                                                          | t <sub>cyc</sub>                  | 480 |            | ns         |

| Capture/Compare Timer<br>Input Capture Pulse Width                                                 | t <sub>TH</sub> , t <sub>TL</sub> | 125 |            | ns         |

| Interrupt Pulse Width Low (Edge-Triggered)                                                         | t <sub>ILIL</sub>                 | 125 |            | ns         |

| OSC1 Pulse Width                                                                                   | t <sub>OH</sub> , t <sub>OL</sub> | 90  |            | ns         |

#### **B.3 SIOP TIMING**

The data given in Table 9-7 and Table 9-8 of MC68HC05P4 Technical Data applies to the MC68HSC05P4 with the exceptions given in Table B-4 and Table B-5.

Table B-4. SIOP Timing ( $V_{DD}$  = 5.0 V  $\pm$  10%)

| Characteristic                                   | Symbol            | Min | Max | Unit |

|--------------------------------------------------|-------------------|-----|-----|------|

| Clock (SCK) Low Time (f <sub>OP</sub> = 4.2 MHz) | t <sub>sckl</sub> | 466 | _   | ns   |

| SDO Data Valid Time                              | t <sub>V</sub>    |     | 100 | ns   |

| SDO Hold Time                                    | t <sub>HO</sub>   | 0   | . — | ns   |

| SDI Setup Time                                   | ts                | 50  | _   | ns   |

| SDI Hold Time                                    | t <sub>H</sub>    | 50  |     | ns   |

Table B-5. SIOP Timing ( $V_{DD}$  = 3.3 V  $\pm$  10%)

| Characteristic                                   | Symbol            | Min | Max | Unit |

|--------------------------------------------------|-------------------|-----|-----|------|

| Clock (SCK) Low Time (f <sub>OP</sub> = 2.1 MHz) | t <sub>SCKL</sub> | 990 |     | ns   |

| SDO Data Valid Time                              | t <sub>V</sub>    |     | 200 | ns   |

| SDO Hold Time                                    | t <sub>HO</sub>   | 0   | -   | ns   |

| SDI Setup Time                                   | t <sub>s</sub>    | 100 |     | ns   |

| SDI Hold Time                                    | t <sub>H</sub>    | 100 |     | ns   |

#### **B.4 MC ORDERING INFORMATION**

Table B-6 provides information for available package types.

**Table B-6. MC Order Numbers**

| Package Type                                   | Temperature                        | MC Order Number                 |

|------------------------------------------------|------------------------------------|---------------------------------|

| 28-Pin Plastic Dual In-Line Package (DIP)      | 0° C to +70° C<br>-40° C to +85° C | MC68HSC05P4P<br>MC68HSC05P4CP   |

| 28-Pin Small Outline Integrated Circuit (SOIC) | 0° C to +70° C<br>-40° C to +85° C | MC68HSC05P4DW<br>MC68HSC05P4CDW |

Go to: www.freescale.com

Home Page:

www.freescale.com

email:

support@freescale.com

**USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler. Arizona 85224

(800) 521-6274

480-768-2130 support@freescale.com

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

support@freescale.com

Japan:

Freescale Semiconductor Japan Ltd.

Headquarters

ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku

Tokyo 153-0064, Japan

0120 191014

+81 2666 8080

support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

**Technical Information Center**

2 Dai King Street

Tai Po Industrial Estate, Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

(800) 441-2447

303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor

@hibbertgroup.com

RoHS-compliant and/or Pb- free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb- free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale.s Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.