ADC12QJ1600-SP SBASAI8 - JUNE 2022

# ADC12QJ1600-SP Quad Channel 1.6-GSPS, 12-Bit, Analog-to-Digital Converter (ADC) with JESD204C Interface

#### 1 Features

- Radiation Performance:

- Total Ionizing Dose (TID): 300 krad (Si)

- Single Event Latchup (SEL): 120 MeV-cm2/mg

- Single Event Upset (SEU) immune registers

- ADC Core:

- Resolution: 12 Bit

- Maximum sampling rate: 1.6 GSPS

- Non-interleaved architecture

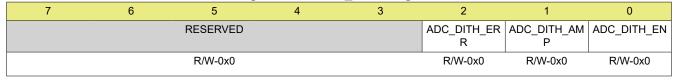

- Internal dither reduces high-order harmonics

- Performance specifications (-1 dBFS):

- SNR (100 MHz): 57.4 dBFS

- ENOB (100 MHz): 9.1 Bits

- SFDR (100 MHz): 64 dBc

- Noise floor (–20 dBFS): –147 dBFS

- Full-scale input voltage: 800 mV<sub>PP-DIFF</sub>

- Full-power input bandwidth: 6 GHz

- JESD204C Serial data interface:

- Support for 2 to 8 total SerDes lanes

- Maximum baud-rate: 17.16 Gbps

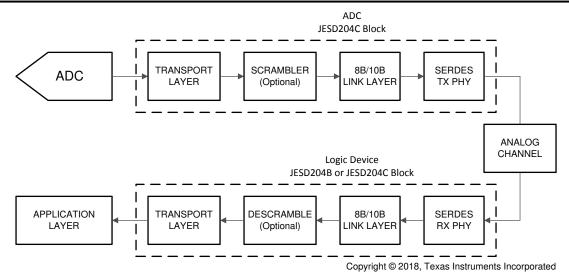

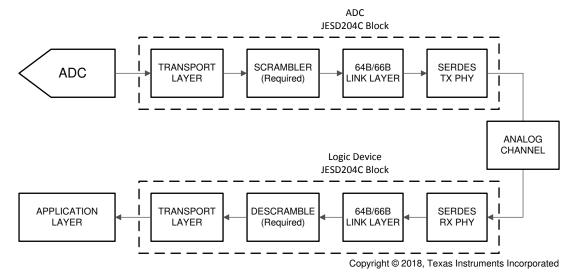

- 64B/66B and 8B/10B encoding modes

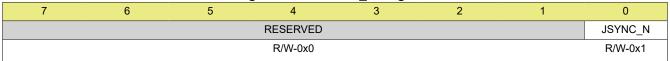

- Subclass-1 support for deterministic latency

- Compatible with JESD204B receivers

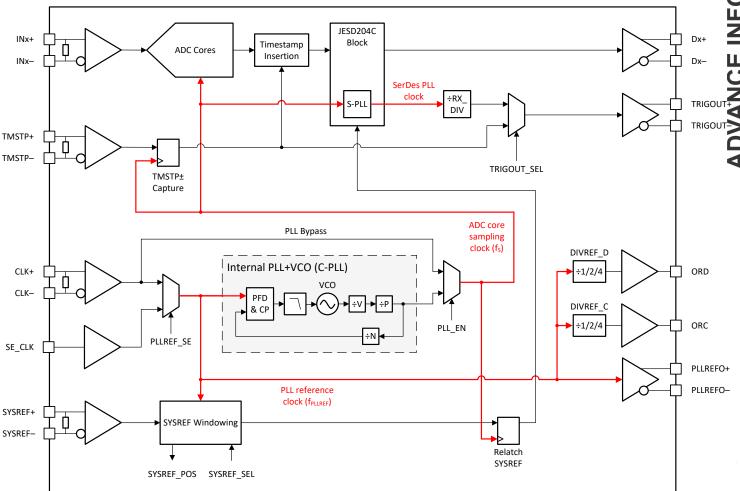

- Optional internal sampling clock generation

- Internal PLL and VCO (7.2–8.2 GHz)

- SYSREF Windowing eases synchronization

- Four clock outputs simplify system clocking

- Reference clocks for FPGA or adjacent ADC

- Reference clock for SerDes transceivers

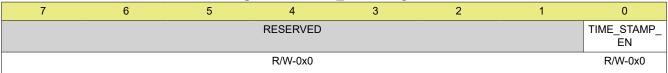

- Timestamp input and output for pulsed systems

- Power consumption (1 GSPS): 1.9W

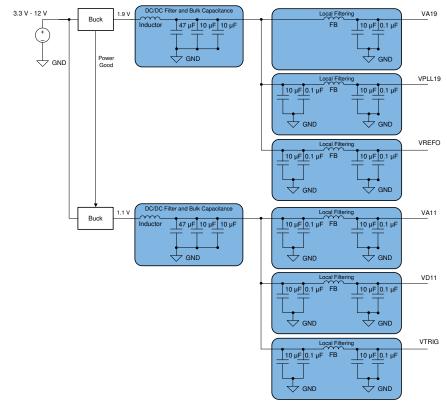

- Power supplies: 1.1 V, 1.9 V

# 2 Applications

- Electronic warfare (SIGINT, ELINT)

- Satellite communications (SATCOM)

# 3 Description

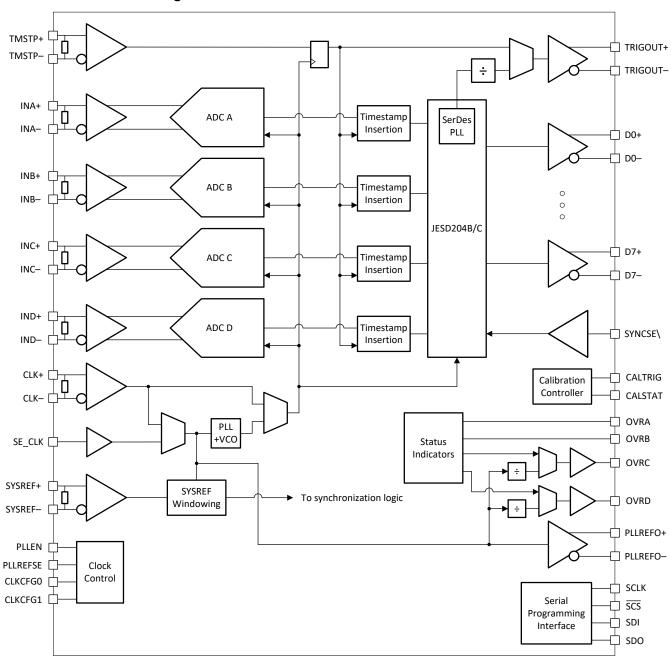

ADC12QJ1600-SP is a quad channel, 12-bit, 1.6 GSPS analog-to-digital converters (ADC). Low power consumption, high sampling rate and 12-bit resolution makes the device suited for a variety of multi-channel communications systems.

Full-power input bandwidth (-3 dB) of 6 GHz enables direct RF sampling of of L-band and S-band.

#### **Package Information**

| PART NUMBER    | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |

|----------------|------------------------|-------------------|

| ADC12QJ1600-SP | FCBGA (144)            | 10.0 mm × 10.0 mm |

For all available packages, see the package option addendum at the end of the data sheet.

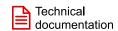

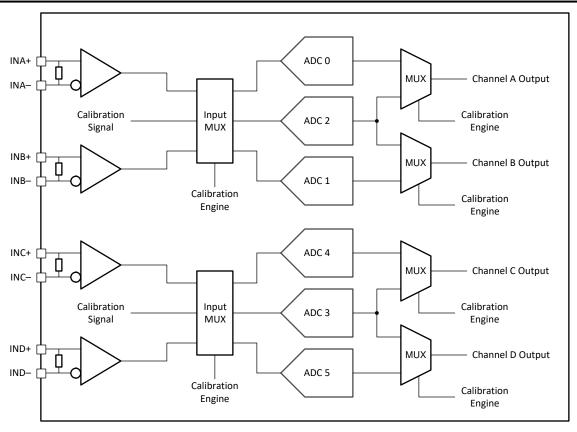

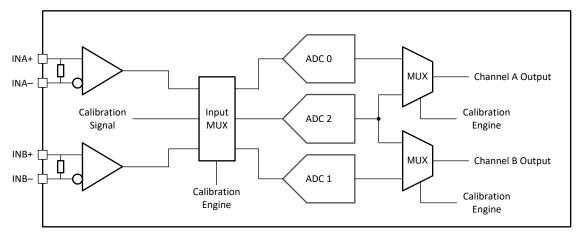

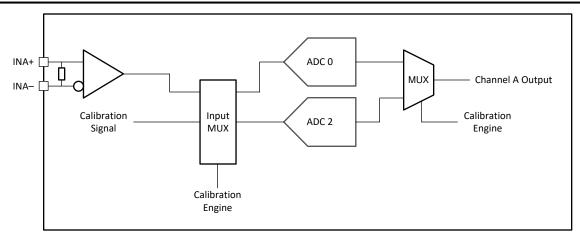

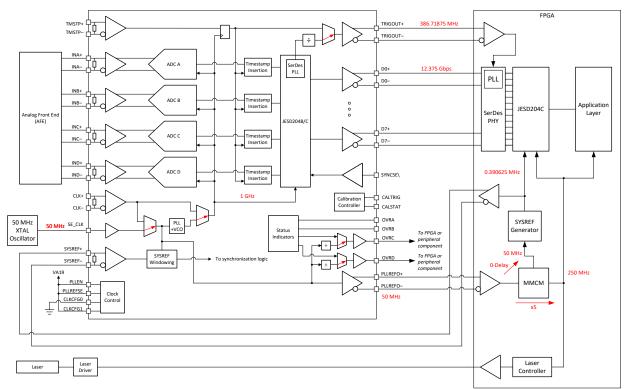

**Quad Channel Block Diagram**

#### **Table of Contents**

| 1 Features                                           | 8.3 Feature Description                             | 48                   |

|------------------------------------------------------|-----------------------------------------------------|----------------------|

| 2 Applications                                       | 8.4 Device Functional Modes                         |                      |

| 3 Description                                        | 8.5 Programming                                     | 88                   |

| 4 Description (continued)2                           | 9 Application and Implementation                    | 128                  |

| 5 Revision History2                                  | 9.1 Application Information                         | 128                  |

| 6 Pin Configuration and Functions3                   | 9.2 Typical Applications                            |                      |

| 7 Specifications8                                    | 9.3 Initialization Set Up                           |                      |

| 7.1 Absolute Maximum Ratings8                        | 9.4 Power Supply Recommendations                    | 134                  |

| 7.2 ESD Ratings8                                     | 9.5 Layout                                          | 136                  |

| 7.3 Recommended Operating Conditions9                | 10 Device and Documentation Support                 | 141                  |

| Thermal Information9                                 | 10.1 Device Support                                 | <mark>14</mark> 1    |

| 7.4 Electrical Characteristics: DC Specifications 10 | 10.2 Receiving Notification of Documentation Update | es <mark>14</mark> 1 |

| 7.5 Electrical Characteristics: Power Consumption 12 | 10.3 Support Resources                              | 141                  |

| 7.6 Electrical Characteristics: AC Specifications 14 | 10.4 Trademarks                                     | 141                  |

| 7.7 Switching Characteristics19                      | 10.5 Electrostatic Discharge Caution                | 141                  |

| 7.8 Timing Requirements21                            | 10.6 Glossary                                       | 141                  |

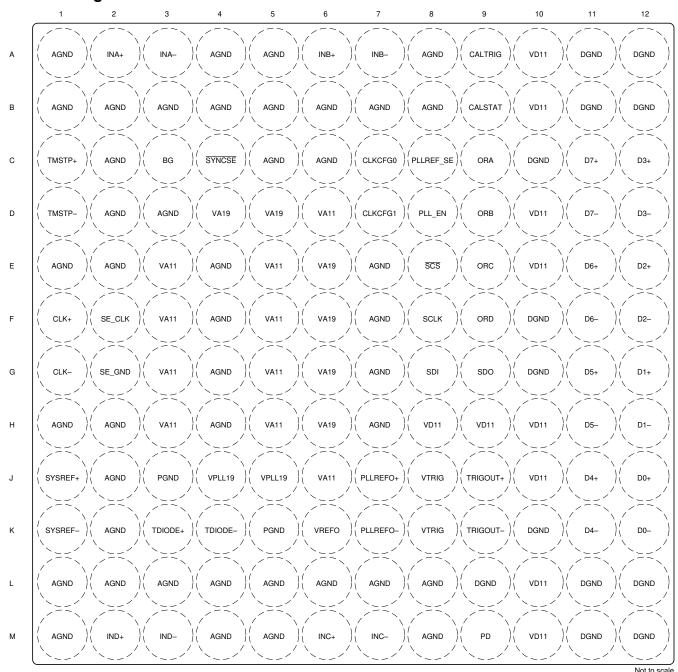

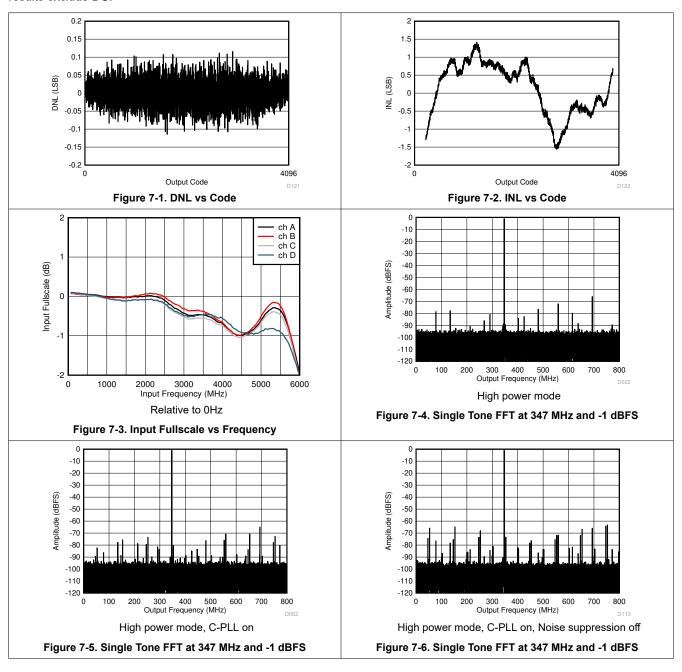

| 7.9 Typical Characteristics22                        | 11 Mechanical, Packaging, and Orderable             |                      |

| 8 Detailed Description46                             | Information                                         | 141                  |

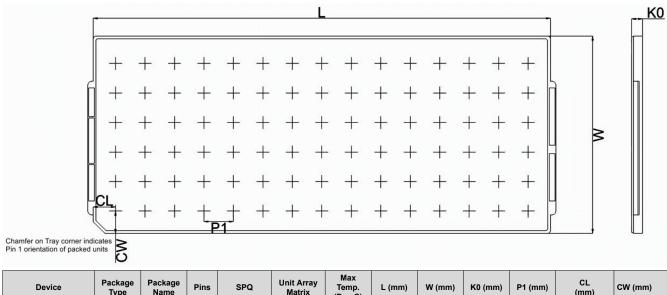

| 8.1 Overview46                                       | 11.1 Tray Information                               |                      |

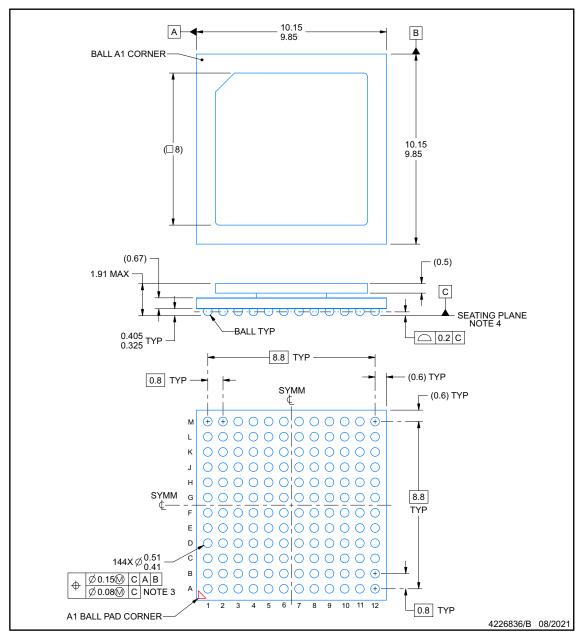

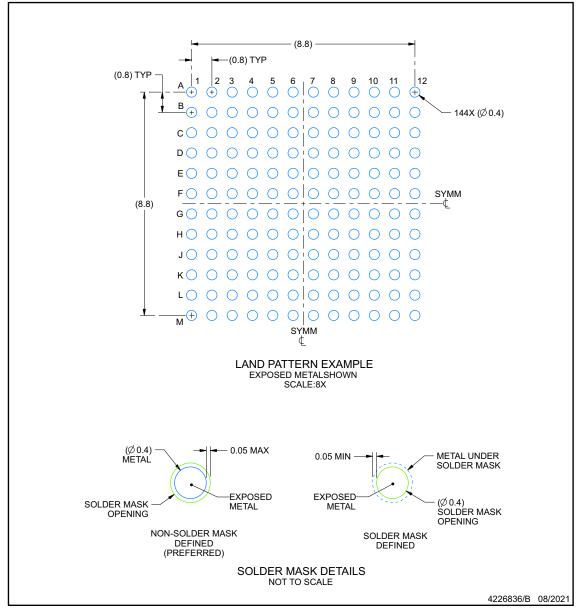

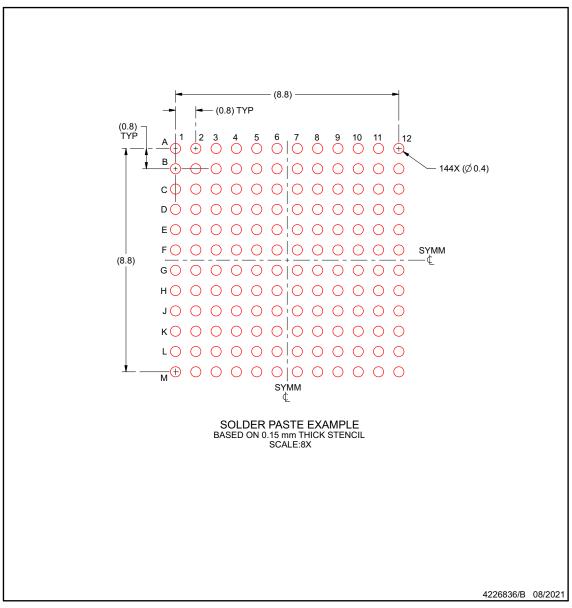

| 8.2 Functional Block Diagram47                       | 11.2 Mechanical Data                                | 143                  |

|                                                      |                                                     |                      |

# 4 Description (continued)

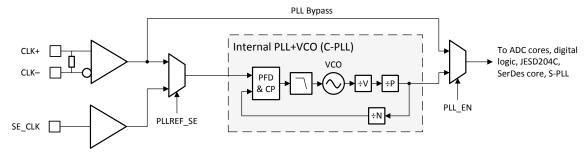

A number of clocking features are included to relax system hardware requirements, such as an internal phase-locked loop (PLL) with integrated voltage-controlled oscillator (VCO) to generate the sampling clock. Four clock outputs are provided to clock the logic and SerDes of the FPGA or ASIC. A timestamp input and output is provided for pulsed systems.

JESD204C serialized interface decreases system size by reducing the amount of printed circuit board (PCB) routing. Interface modes support from 2 to 8 lanes (dual and quad channel devices) or 1 to 4 lanes (for the single channel device), with SerDes baud-rates up to 17.16 Gbps, to allow the optimal configuration for each application.

#### 5 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE      | REVISION | NOTES            |

|-----------|----------|------------------|

| June 2022 | *        | Initial release. |

# **6 Pin Configuration and Functions**

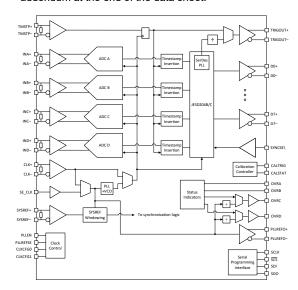

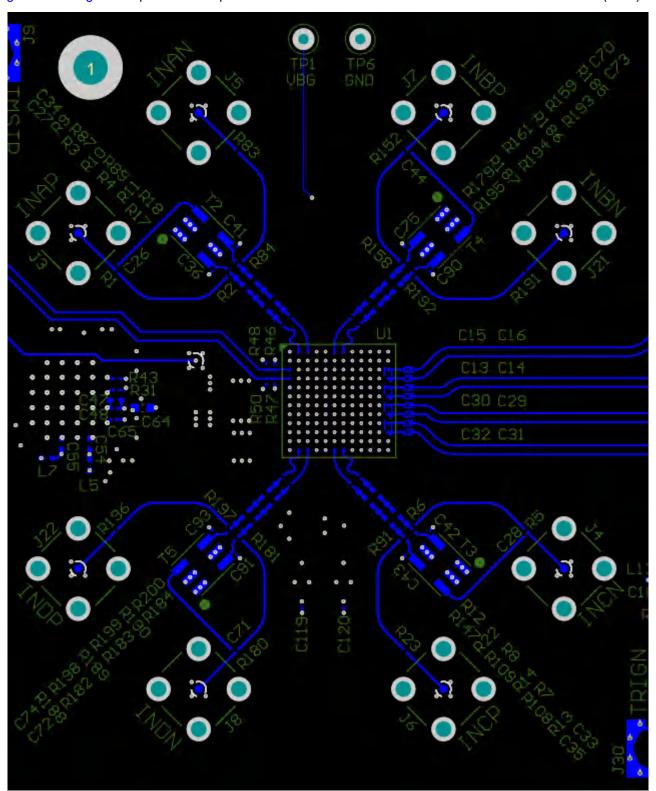

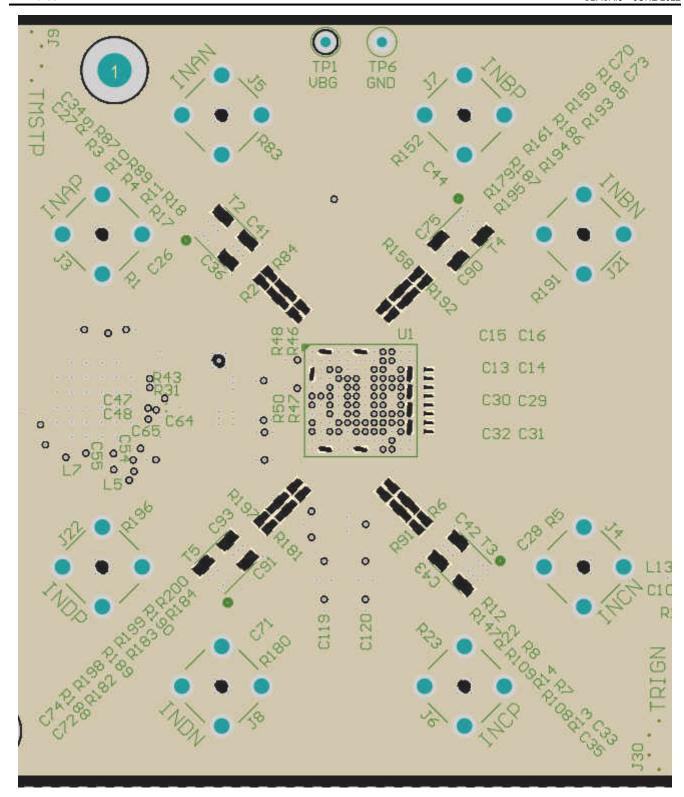

Figure 6-1. Quad Channel ALR Package, 144-Ball Flip Chip BGA (Top View)

#### Table 6-1. Pin Functions

| PI                                                                                                                                                                                                       | IN      |      | Table 6-1. Pin Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.                                                                                                                                                                                                      | NAME    | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| A1, A4, A5, A8,<br>B1, B2, B3, B4,<br>B5, B6, B7, B8,<br>C2, C5, C6, D2,<br>D3, E1, E2, E4,<br>E7, F4, F7, G4,<br>G7, H1, H2, H4,<br>H7, J2, K2, L1,<br>L2, L3, L4, L5,<br>L6, L7, L8, M1,<br>M4, M5, M8 | AGND    | -    | Analog supply ground. Tie AGND, PGND, SE_GND and DGND to a common ground plane (GND) on the circuit board.                                                                                                                                                                                                                                                                                                                                                                  |  |

| C3                                                                                                                                                                                                       | BG      | 0    | Band-gap voltage output. This pin is capable of sourcing only small currents and driving limited capacitive loads, as specified in the Recommended Operating Conditions table. This pin can be left disconnected if not used.                                                                                                                                                                                                                                               |  |

| В9                                                                                                                                                                                                       | CALSTAT | 0    | Foreground calibration status output or device alarm output. Functionality is programmed through CAL_STATUS_SEL. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                             |  |

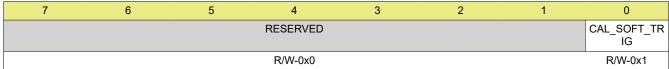

| A9                                                                                                                                                                                                       | CALTRIG | I    | Foreground calibration trigger input. This pin is only used if hardware calibration triggering is selected in CAL_TRIG_EN, otherwise software triggering is performed using CAL_SOFT_TRIG. Tie this pin to GND if not used.                                                                                                                                                                                                                                                 |  |

| G1                                                                                                                                                                                                       | CLK-    | ı    | Device (sampling) clock negative input or differential PLL reference clock negative input. TI strongly recommends using AC-coupling for best performance. This pin can be left disconnected if SE_CLK is used to apply the reference clock.                                                                                                                                                                                                                                 |  |

| F1                                                                                                                                                                                                       | CLK+    | ı    | Device (sampling) clock positive input or differential PLL reference clock negative input. The clock signal is strongly recommended to be AC-coupled to this input for best performance. This differential input has an internal 100-Ω differential termination and is self-biased to the optimal input common-mode voltage as long as DEVCLK_LVPECL_EN is set to 0. This pin can be left disconnected if SE_CLK is used to apply the reference clock when the PLL is used. |  |

| C7                                                                                                                                                                                                       | CLKCFG0 | ı    | CLKCFG0 and CLKCFG1 can be used enable additional clock outputs on ORC and ORD when the C-PLL is used (PLL_EN is set high). Tie this pin to ground if not used.                                                                                                                                                                                                                                                                                                             |  |

| D7                                                                                                                                                                                                       | CLKCFG1 | ı    | CLKCFG0 and CLKCFG1 can be used enable additional clock outputs on ORC and ORD when the C-PLL is used (PLL_EN is set high). Tie this pin to ground if not used.                                                                                                                                                                                                                                                                                                             |  |

| K12                                                                                                                                                                                                      | D0-     | 0    | High-speed serialized data output for lane 0, negative connection. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                                                           |  |

| J12                                                                                                                                                                                                      | D0+     | 0    | High-speed serialized data output for lane 0, negative connection. This pin can be left disconnected if n High-speed serialized data output for lane 0, positive connection. This differential output must be AC-cc and must always be terminated with a $100-\Omega$ differential termination at the receiver. This pin can be left disconnected if not used.                                                                                                              |  |

| H12                                                                                                                                                                                                      | D1–     | 0    | High-speed serialized data output for lane 1, negative connection. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                                                           |  |

| G12                                                                                                                                                                                                      | D1+     | 0    | High-speed serialized data output for lane 1, positive connection. This differential output must be AC-coupled and must always be terminated with a $100-\Omega$ differential termination at the receiver. This pin can be left disconnected if not used.                                                                                                                                                                                                                   |  |

| F12                                                                                                                                                                                                      | D2-     | 0    | High-speed serialized data output for lane 2, negative connection. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                                                           |  |

| E12                                                                                                                                                                                                      | D2+     | 0    | High-speed serialized data output for lane 2, positive connection. This differential output must be AC-coupled and must always be terminated with a $100-\Omega$ differential termination at the receiver. This pin can be left disconnected if not used.                                                                                                                                                                                                                   |  |

| D12                                                                                                                                                                                                      | D3-     | 0    | High-speed serialized data output for lane 3, negative connection. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                                                           |  |

| C12                                                                                                                                                                                                      | D3+     | 0    | High-speed serialized data output for lane 3, positive connection. This differential output must be AC-coupled and must always be terminated with a $100-\Omega$ differential termination at the receiver. This pin can be left disconnected if not used.                                                                                                                                                                                                                   |  |

| K11                                                                                                                                                                                                      | D4-     | 0    | High-speed serialized data output for lane 4, negative connection. Not used for single channel devices. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                      |  |

| J11                                                                                                                                                                                                      | D4+     | 0    | High-speed serialized data output for lane 4, positive connection. Not used for single channel devices. This differential output must be AC-coupled and must always be terminated with a 100-Ω differential termination at the receiver. This pin can be left disconnected if not used.                                                                                                                                                                                     |  |

| H11                                                                                                                                                                                                      | D5-     | 0    | High-speed serialized data output for lane 5, negative connection. Not used for single channel devices. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                      |  |

| G11                                                                                                                                                                                                      | D5+     | 0    | High-speed serialized data output for lane 5, positive connection. Not used for single channel devices. This differential output must be AC-coupled and must always be terminated with a 100-Ω differential termination at the receiver. This pin can be left disconnected if not used.                                                                                                                                                                                     |  |

| F11                                                                                                                                                                                                      | D6-     | 0    | High-speed serialized data output for lane 6, negative connection. Not used for single channel devices. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                      |  |

| E11                                                                                                                                                                                                      | D6+     | 0    | High-speed serialized data output for lane 6, positive connection. Not used for single channel devices. This differential output must be AC-coupled and must always be terminated with a 100-Ω differential termination at the receiver. This pin can be left disconnected if not used.                                                                                                                                                                                     |  |

#### **Table 6-1. Pin Functions (continued)**

| P                                                                          | IN   |      | Table 6-1. Pin Functions (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.                                                                        | NAME | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| D11                                                                        | D7-  | 0    | High-speed serialized data output for lane 7, negative connection. Not used for single channel devices. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| C11                                                                        | D7+  | 0    | High-speed serialized data output for lane 7, positive connection. Not used for single channel devices. This differential output must be AC-coupled and must always be terminated with a 100-Ω differential termination at the receiver. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A11, A12, B11,<br>B12, C10, F10,<br>G10, K10, L9,<br>L11, L12, M11,<br>M12 | DGND | _    | Digital supply ground. Tie AGND, PGND, SE_GND and DGND to a common ground plane (GND) on the circuit board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

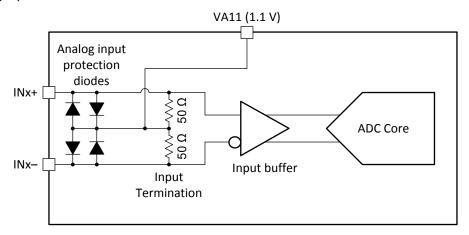

| A3                                                                         | INA- | ı    | Channel A analog input negative connection for quad, dual and single channel devices. See INA+ for detailed description. This input is terminated to VA11 through a 50-Ω termination resistor. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A2                                                                         | INA+ | ı    | Channel A analog input positive connection for quad, dual and single channel devices. The differential full-scale input voltage is determined by the FS_RANGE register (see the <i>Full-Scale Voltage (VFS) Adjustment</i> section). This input is terminated to VA11 through a 50-Ω termination resistor. The input common-mode voltage is internally self-biased to VA11 (1.1 V nominally) and must follow the recommendations in the Recommended Operating Conditions table. This input can be AC coupled to the source if DC signals are not required. If DC signals are required then a DC-coupled fully differential driving amplifier must be used with its output common-mode voltage set to the VA11 supply voltage. This pin can be left disconnected if not used.                            |

| A7                                                                         | INB- | I    | Channel B analog input negative connection for quad and dual channel devices. Do not connect for single channel device. See INB+ for detailed description. This input is terminated to VA11 through a 50-Ω termination resistor. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A6                                                                         | INB+ | ı    | Channel B analog input positive connection for quad and dual channel devices. Do not connect for single channel device. The differential full-scale input voltage is determined by the FS_RANGE register (see the Full-Scale Voltage (VFS) Adjustment section). This input is terminated to VA11 through a 50-Ω termination resistor. The input common-mode voltage is internally self-biased to VA11 (1.1 V nominally) and must follow the recommendations in the Recommended Operating Conditions table. This input can be AC coupled to the source if DC signals are not required. If DC signals are required then a DC-coupled fully differential driving amplifier must be used with its output common-mode voltage set to the VA11 supply voltage. This pin can be left disconnected if not used. |

| M7                                                                         | INC- | ı    | Channel C analog input negative connection for quad channel device. Do not connect for single and dual channel devices. See INC+ for detailed description. This input is terminated to VA11 through a 50-Ω termination resistor. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| M6                                                                         | INC+ | ı    | Channel C analog input positive connection for quad channel device. Do not connect for single and dual channel devices. The differential full-scale input voltage is determined by the FS_RANGE register (see the Full-Scale Voltage (VFS) Adjustment section). This input is terminated to VA11 through a 50-Ω termination resistor. The input common-mode voltage is internally self-biased to VA11 (1.1 V nominally) and must follow the recommendations in the Recommended Operating Conditions table. This input can be AC coupled to the source if DC signals are not required. If DC signals are required then a DC-coupled fully differential driving amplifier must be used with its output common-mode voltage set to the VA11 supply voltage. This pin can be left disconnected if not used. |

| M3                                                                         | IND- | ı    | Channel D analog input negative connection for quad channel device. Do not connect for single and dual channel devices. See IND+ for detailed description. This input is terminated to VA11 through a 50-Ω termination resistor. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| M2                                                                         | IND+ | ı    | Channel D analog input positive connection for quad channel device. Do not connect for single and dual channel devices. The differential full-scale input voltage is determined by the FS_RANGE register (see the Full-Scale Voltage (VFS) Adjustment section). This input is terminated to VA11 through a 50-Ω termination resistor. The input common-mode voltage is internally self-biased to VA11 (1.1 V nominally) and must follow the recommendations in the Recommended Operating Conditions table. This input can be AC coupled to the source if DC signals are not required. If DC signals are required then a DC-coupled fully differential driving amplifier must be used with its output common-mode voltage set to the VA11 supply voltage. This pin can be left disconnected if not used. |

| C9                                                                         | ORA  | 0    | Fast over-range detection status output for channel A. When the analog input for channel A exceeds the threshold programmed into OVR_T, this status indicator goes high. The minimum pulse duration is set by OVR_N. See the <i>ADC Overrange Detection</i> section for more information. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D9                                                                         | ORB  | 0    | Fast over-range detection status output for channel B. Only used for quad and dual channel devices. Do not connect for single channel device. When the analog input for channel B exceeds the threshold programmed into OVR_T, this status indicator goes high. The minimum pulse duration is set by OVR_N. See the <i>ADC Overrange Detection</i> section for more information. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                                                                         |

#### **Table 6-1. Pin Functions (continued)**

|        | PIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.    | NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ITPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| E9     | ORC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0    | Fast over-range detection status output for channel C or additional clock output. The fast over-range detection function is only available for quad channel device. When the analog input for channel C exceeds the threshold programmed into OVR_T, this status indicator goes high. The minimum pulse duration is set by OVR_N. See the <i>ADC Overrange Detection</i> section for more information. This pin can alternatively be used as an additional clock output (DIVREF_C) when enabled by CLKCFG[1:0] or through the SPI register configuration and when PLL_EN is high. When CLKCFG0 and CLKCFG1:0] the oth set low (or disabled through SPI) the ORC output is used to output the over-range signal for ADC channel C.ORC can be programmed as a copy of PLLREFO (CLKCFG[1:0] = 0x1) or as a divide-by-2 (CLKCFG[1:0] = 0x2) or divide-by-4 (CLKCFG[1:0] = 0x3) copy of PLLREFO. The clock at ORC is available at device power up if PLL_EN is set high, PD is set low and CLKCFG[1:0] are configured appropriately. This pin can be left disconnected if not used.                                                                                       |

| F9     | ORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0    | Fast over-range detection status output for channel D or additional clock output. The fast over-range detection function is only available for quad channel device. When the analog input for channel D exceeds the threshold programmed into OVR_T, this status indicator goes high. The minimum pulse duration is set by OVR_N. See the ADC Overrange Detection section for more information. This pin can alternatively be used as an additional clock output (DIVREF_D) when enabled by CLKCFG[1:0] or through the SPI register configuration and when PLL_EN is high. When CLKCFG0 and CLKCFG1 are both set low (or disabled through SPI) the ORD output is used to output the over-range signal for ADC channel D.ORD can be programmed as a copy of PLLREFO when any or both of CLKCFG[1:0] are set which will be available at startup if PLL_EN is set high and PD is held low. ORD can be set as a divide-by-2 or divide-by-4 copy of PLLREFO when overridden through the SPI register. A clock out of ORD is only available if a clock is also output from ORC. If only one clock is required then use ORC. This pin can be left disconnected if not used. |

| M9     | PD I CMOS input to power down the device for power savings or temperature diode calibration. Setting PD has disables PLLREFO and the ORC and ORD clock outputs and therefore this pin should not be used if the clocks are critical for system operation. Tie this pin to GND if not used.  PLL supply ground. Tie AGND, PGND, SE_GND and DGND to a common ground plane (GND) on the common ground plane (GN |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| J3, K5 | PGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _    | PLL supply ground. Tie AGND, PGND, SE_GND and DGND to a common ground plane (GND) on the circuit board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| D8     | PLL_EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ı    | CMOS input to enable the internal PLL for sampling clock generation if set high or to disable and bypass the PLL if set low. Tie this pin to GND if PLL is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C8     | PLLREF_SE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ı    | CMOS input to select the single-ended PLL reference clock input (SE_CLK) if set high or the differential clock input (CLK±) if set low. Only CLK± can be used for the sampling clock if the PLL is disabled. Tie this pin to GND if the PLL is not used or if CLK± is used as the reference clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| K7     | PLLREFO-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0    | Negative LVDS PLL reference clock output. The clock is repeated from the selected PLL reference clock input (CLK± or SE_CLK). It is available at device power up to clock other devices when PLL_EN is set high and PD is held low. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| J7     | PLLREFO+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0    | Positive LVDS PLL reference clock output. The clock is repeated from the selected PLL reference clock input (CLK± or SE_CLK). It is available at device power up to clock other devices when PLL_EN is set high and PD is held low. This pin can be left disconnected if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

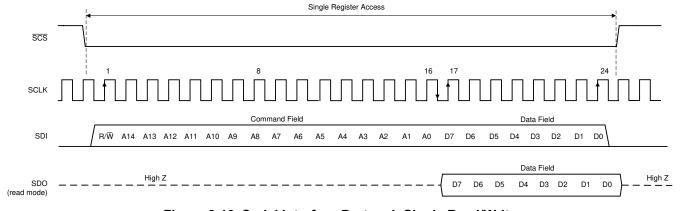

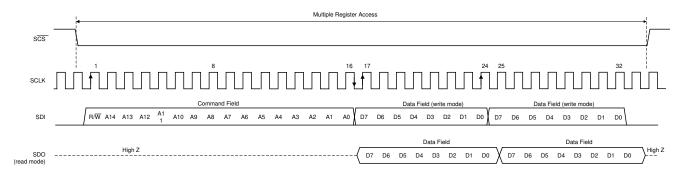

| F8     | SCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ı    | Serial interface clock. This pin functions as the serial-interface clock input that clocks the serial programming data in and out. The <i>Using the Serial Interface</i> section describes the serial interface in more detail. Supports 1.1-V to 1.9-V CMOS levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

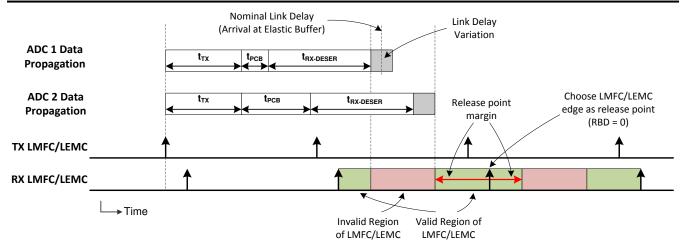

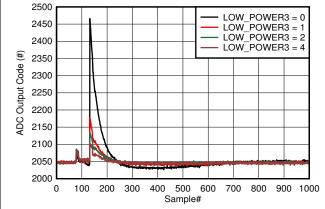

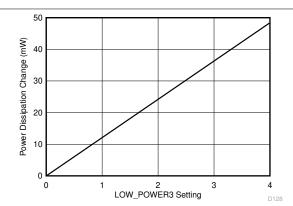

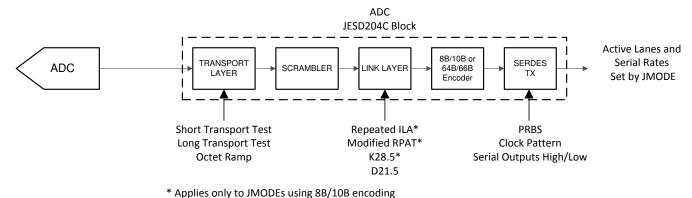

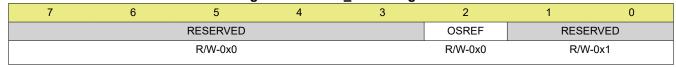

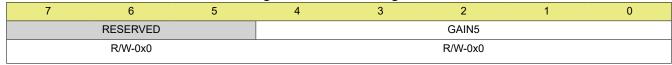

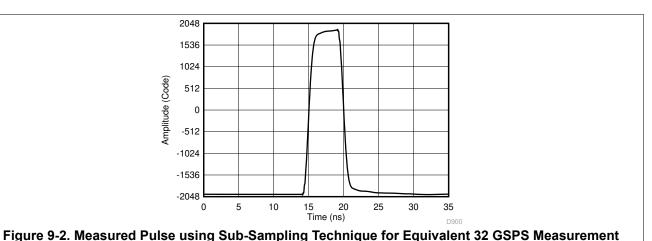

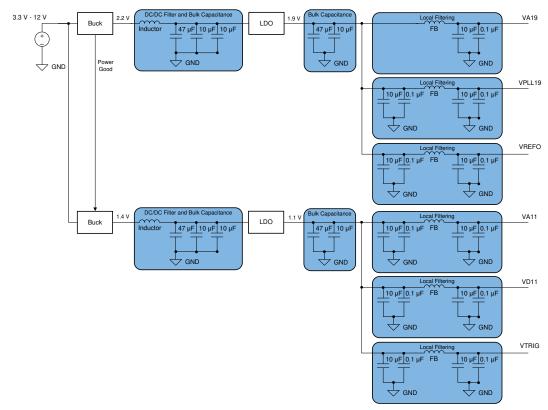

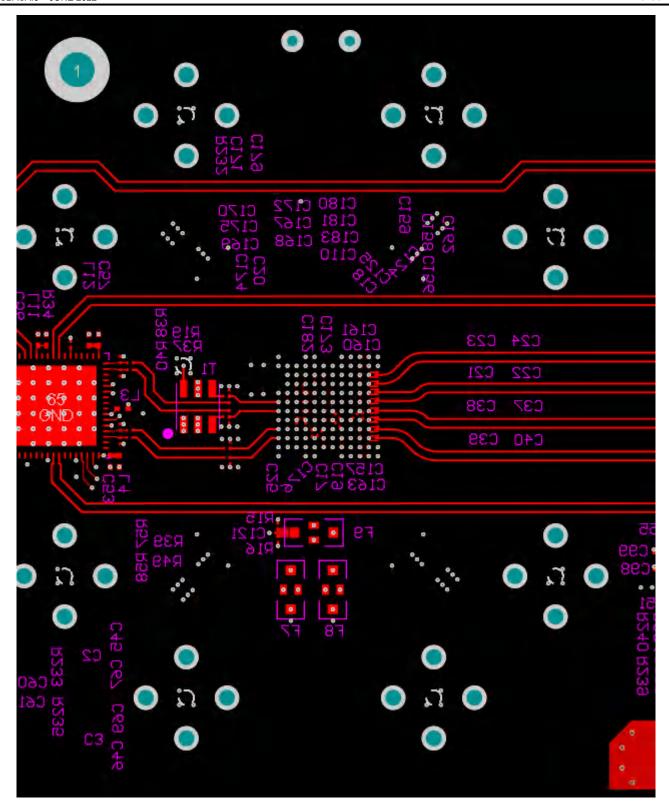

| E8     | SCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ı    | Serial interface chip select active low input. The <i>Using the Serial Interface</i> section describes the serial interface in more detail. Supports 1.1-V to 1.9-V CMOS levels. This pin has a 82-kΩ pull-up resistor to VD11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |