# Application Note

# Sitara™ Processor Power Distribution Networks: Implementation and Analysis

Dave King

#### **ABSTRACT**

The purpose of a power distribution network (PDN) is primarily to provide clean and reliable power to the active devices on the system. The printed circuit board (PCB) is a critical component of the system-level PDN delivery network. As such, optimal design of the PCB power distribution network is of utmost importance for high performance microprocessors. This application report provides implementation guidelines and recommendations for designing printed circuit board (PCB) power delivery networks (PDN) for the Texas Instruments Sitara<sup>™</sup> family of microprocessors.

# **Table of Contents**

| 1 Introduction                                                                                                                                           | 2  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 Acronyms Used in This Document                                                                                                                       | 2  |

| 2 Guidelines for PCB Stack-Up                                                                                                                            | 3  |

| 3 Physical Layout Optimization of the PDN                                                                                                                |    |

| 4 Static PDN Analysis (IR Drop Optimization)                                                                                                             | 8  |

| 5 Dynamic Analysis of PCB PDN                                                                                                                            |    |

| 5.1 Selecting Decoupling Capacitors to Meet Z <sub>TARGET</sub>                                                                                          |    |

| 6 Checklist for PDN                                                                                                                                      |    |

| 7 Implementation Examples and PDN Targets                                                                                                                | 14 |

| 7.1 AM570x                                                                                                                                               | 14 |

| 7.2 AM571x                                                                                                                                               | 16 |

| 7.3 AM572x                                                                                                                                               | 19 |

| 7.4 AM574x                                                                                                                                               | 22 |

| 7.5 AM65xx/DRA80xM                                                                                                                                       | 25 |

| 7.6 AM62xx                                                                                                                                               | 28 |

| 8 Revision History                                                                                                                                       | 29 |

| List of Figures  Figure 2-1. Minimize Loop Inductance by Optimizing Layer Assignments in the PCB                                                         | 3  |

| Figure 2-1. Minimize Loop inductance by Optimizing Layer Assignments in the POB<br>Figure 2-2. Example Stack-Up Utilizing High-Density Interconnect Vias |    |

| Figure 2-3. Example Stack-Up Utilizing Plated-Through-Hole (PTH) Vias                                                                                    |    |

| Figure 3-1. Characteristics of a "Real" Capacitor With ESL and ESR                                                                                       |    |

| Figure 3-2. Typical Impedance Profile of a Capacitor                                                                                                     |    |

| Figure 3-3. Example of "Co-Planar' Shielding of Power Net Using Ground Guard-Band                                                                        |    |

| Figure 3-4. Capacitor Mounting Geometries                                                                                                                |    |

| Figure 4-1. Depiction of Sheet Resistivity and Resistance                                                                                                |    |

| Figure 4-2. PCB IR Drop Budget                                                                                                                           |    |

| Figure 4-3. Sense Line Placement.                                                                                                                        |    |

| Figure 4-4. Allowable Power Input Voltage Difference                                                                                                     |    |

| Figure 5-1. Components of a Typical Power Distribution Network (PDN)                                                                                     |    |

| Figure 5-2. Decoupling Frequency Range of PCB Components                                                                                                 |    |

| Figure 5-3. Example Capacitor Placement                                                                                                                  |    |

| List of Tables                                                                                                                                           |    |

| Table 1-1. Acronyms                                                                                                                                      |    |

| Table 7-1. AM570x PDN Targets and Decoupling Example                                                                                                     |    |

|                                                                                                                                                          |    |

Trademarks w

| Table 7-2. AM571x PDN Targets and Decoupling Example         | . 18 |

|--------------------------------------------------------------|------|

| Table 7-3. AM572x PDN Targets and Decoupling Example         |      |

| Table 7-4. AM574x PDN Targets and Decoupling Example         |      |

| Table 7-5. AM65xx/DRA80xM PDN Targets and Decoupling Example |      |

| Table 7-6 AM62xx PDN Targets and Decoupling Example          |      |

#### **Trademarks**

Sitara<sup>™</sup> is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

#### 1 Introduction

This application report provides implementation guidelines and recommendations for designing printed circuit board (PCB) power delivery networks (PDN) for the Texas Instruments Sitara family of microprocessors. This application report will:

- Discuss PCB PDN design methodology

- Provide general PCB PDN design recommendations and requirements

- · Discuss the rationale behind these design requirements

- Provide suggestions and methods that PCB designers can implement to ensure that the PDN requirements for a specific processor are met.

- Provide PDN targets for Sitara-class microprocessors

# 1.1 Acronyms Used in This Document

Table 1-1. Acronyms

| Acronym    | Description                                               |

|------------|-----------------------------------------------------------|

| AC         | Alternating current                                       |

| BGA        | Ball grid array                                           |

| DC         | Direct current (static)                                   |

| Df         | Loss tangent                                              |

| Dk         | Dielectric constant                                       |

| EDA        | Electronic design automation                              |

| EM         | Electromigration                                          |

| ESL        | Effective series inductance                               |

| ESR        | Effective series resistance                               |

| FDTIM      | Frequency domain target impedance method                  |

| HDI        | High density interconnect (for example, buried/blind via) |

| IR         | Product of current (I) x resistance (R)                   |

| РСВ        | Printed circuit board                                     |

| PDN        | Power distribution network                                |

| PM-IC/PMIC | Power management integrated circuit                       |

| PTH        | Plated through hole                                       |

| RLC        | Resistance, inductance, and capacitance                   |

| SMPS       | Switch mode power supply                                  |

| SMT        | Surface mount technology                                  |

| SRF        | Self resonant frequency                                   |

| VIP        | Via in pad                                                |

| VRM        | Voltage regulator module                                  |

### Note

Notwithstanding any provision to the contrary, TI makes no warranty expressed, implied, or statutory, including any implied warranty of merchantability of fitness for a specific purpose, for customer boards. The data described in this document are intended as guidelines only.

# 2 Guidelines for PCB Stack-Up

The PCB stack-up (or layer assignment) is an important factor in ensuring optimal performance of a power distribution scheme. An optimized PCB stack-up for improved power integrity performance can be achieved by following these recommendations:

- Power and ground plane pairs/"islands" should be closely coupled together. The capacitance formed between the planes can be used to decouple the power supply. Whenever possible the power and ground planes should be solid to provide a continuous return path for return current.

- Use a thin dielectric between the power and ground plane pair. Capacitance is inversely proportional to the separation of the plane pair so minimizing the separation distance (the dielectric thickness) will help to maximize the capacitance.

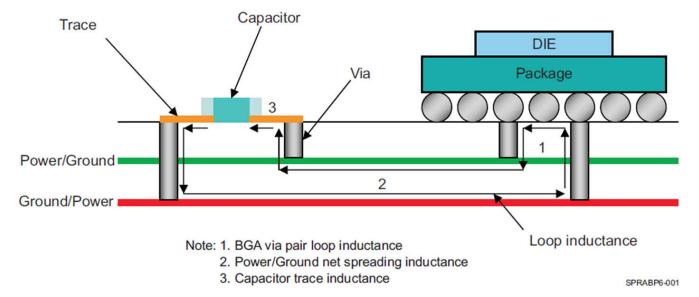

- Keep the power and ground plane pair as close to the PCB top and bottom surfaces as possible (see Figure 2-1). This will help to minimize the associated loop inductance of the decoupling capacitors, vias, and the power/ground plane pair spreading loop inductance.

Figure 2-1. Minimize Loop Inductance by Optimizing Layer Assignments in the PCB

Guidelines for PCB Stack-Up www.ti.com

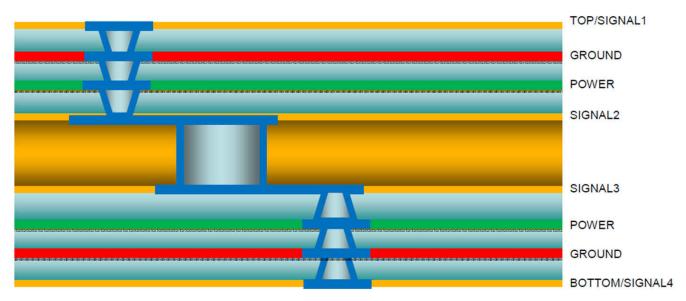

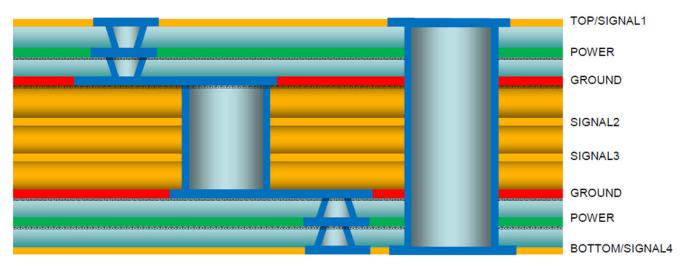

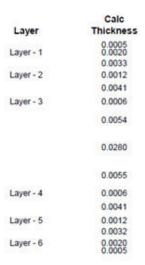

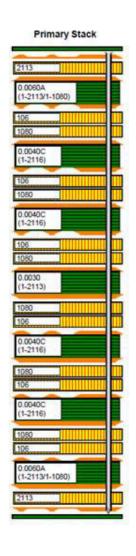

The placement of power and ground planes in the PCB stack-up (determined by layer assignment) has a significant impact on the parasitic inductance of the power current path as shown above. For this reason, it is recommended to consider layer order in the early stages of the PCB PDN design cycle, putting high priority supplies in the top half of the stack-up and low-priority supplies in the bottom half of the stack-up as shown in the examples below. Figure 2-2 and Figure 2-3 show examples of typical PCB stack-ups designed with power distribution performance in mind. Device-specific stack-up examples can be found in Section 8.

Figure 2-2. Example Stack-Up Utilizing High-Density Interconnect Vias

Figure 2-3. Example Stack-Up Utilizing Plated-Through-Hole (PTH) Vias

# 3 Physical Layout Optimization of the PDN

The following are important requirements that need to be implemented in the PCB PDN design:

- External power trace routing between components should be as wide as possible as wider traces result in reduced DC resistance and consequently a lower static IR drop. They also provide for lower loop inductance and higher capacitance.

- Whenever possible, attempt to achieve a ratio of 1:1 (or better) for component pins and associated vias. Do not share vias among multiple capacitors.

- · Placement of decoupling capacitors and associated vias should be as close to the processor ball as possible.

- The maximum current-carrying capacity of each transitional via should be evaluated through simulation to

determine the appropriate number of vias required to connect components. This ensures that the currentcarrying ability of a via interconnect network is sufficient for the needs of each particular component. When

a via interconnect, or a network of same, is unable to supply sufficient current, this is referred to as "via

starvation".

- TI highly recommends that both static and dynamic IR drop analysis (discussed in Section 4 and Section 5) be performed on any new PCB design prior to fabrication. These analyses should be used to assess the appropriate number of vias and geometrical trace width dimensions required to meet the IR drop requirements of system components.

- Whenever possible for the internal layers (both signal routing and power plane), wide traces and copper area

fills are recommended for PDN layout. As discussed in previous sections of this document, routing power

nets in planes provides for more inter-plane capacitance and improves high frequency performance of the

PDN.

- Decoupling capacitors should be mounted with minimum impact to inductance. A capacitor has

characteristics not only of capacitance but also inductance and resistance. Figure 3-1 shows the parasitic

model of a real capacitor. A real capacitor should be treated as an RLC circuit with effective series resistance

(ESR) and effective series inductance (ESL).

Figure 3-1. Characteristics of a "Real" Capacitor With ESL and ESR

The magnitude of the impedance of this series model is given in Equation 1.

$$\begin{split} \left|Z\right| &= \sqrt{\text{ESR}^2 + \left(w\text{ESL} - \frac{1}{wC}\right)^2} \\ \text{where} \\ w &= 2\pi f \end{split} \tag{1}$$

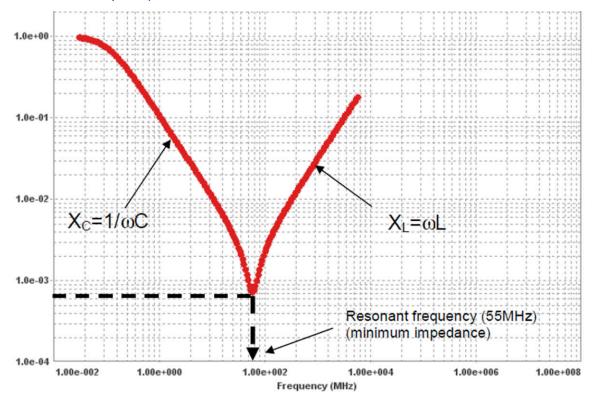

Figure 3-2 shows the resonant frequency response of a typical capacitor with self-resonant frequency of 55 MHz. The impedance of the capacitor is a combination of its series resistance and reactive capacitance and inductance as shown per Equation 1.

Figure 3-2. Typical Impedance Profile of a Capacitor

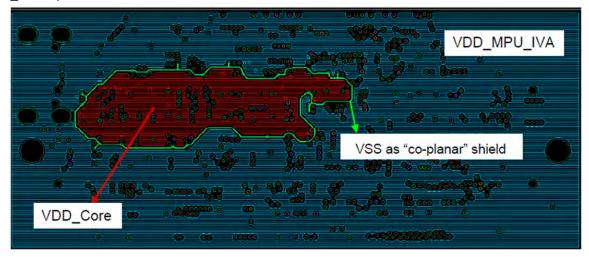

Try to avoid different power nets coupling on the PCB by using "co-planar" shielding whenever appropriate.

Figure 3-3 depicts an example of co-planar shielding for two different power nets (VDD\_MPU\_IVA and VDD\_CORE).

Figure 3-3. Example of "Co-Planar' Shielding of Power Net Using Ground Guard-Band

As the capacitors have both series inductance and resistance that will impact their effectiveness, it is critical that the following recommendations are adopted in placing them on the power distribution network. Whenever possible make sure to mount the capacitor with the geometry that will minimize the mounting inductance and resistance. The capacitor mounting inductance and resistance includes the inductance and resistance of the pads, the trace, and the associated vias.

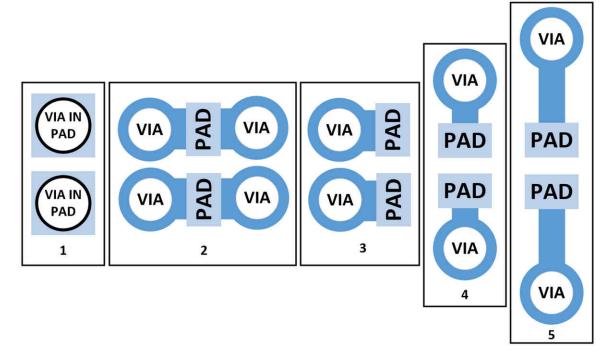

The length of a trace used to connect a capacitor has a significant impact on the parasitic inductance and resistance of the mounting. This trace should be as short and wide as possible. Wherever possible, minimize the trace by locating vias near the solder pad landing. Further improvements can be made to the mounting by placing vias to the side of capacitor lands or by doubling the number of vias. If the PCB manufacturing process allows, and if cost-effective, via-in-pad (VIP) geometries are strongly recommended.

The most common via placement geometries are proved below, in order of preference for reducing parasitic impact:

- 1. Via-In-Pad (VIP)

- 2. Dual Offset Via

- 3. Single Offset Via

- 4. Pad to Via Trace (short)

- 5. Pad to Via Trace (long)

Figure 3-4. Capacitor Mounting Geometries

In addition to mounting inductance and resistance associated with placing a capacitor on the PCB, the effectiveness of a decoupling capacitor also depends on the spreading inductance and resistance that the capacitor sees with respect to the load. The spreading inductance and resistance is strongly dependent on the layer assignment in the PCB stack-up (see Figure 2-1).

# 4 Static PDN Analysis (IR Drop Optimization)

Delivering reliable power to circuits is always of critical importance as IR drops can occur at every level in a chip, package, and board system. Components that are distant from their associated power source are particularly susceptible to IR drop, and designs that rely on battery power must further minimize voltage drop to avoid unacceptable power loss. Early DC assessments made through simulation help to determine power distribution basics such as the best available entry point for power, layer stack-up choices, and estimates for the amount of copper needed to carry the required current.

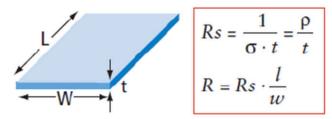

The resistance Rs of a plane conductor for a unit length and unit width is called the surface resistivity (ohms per square).

Figure 4-1. Depiction of Sheet Resistivity and Resistance

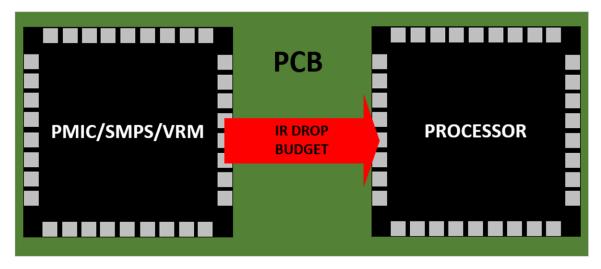

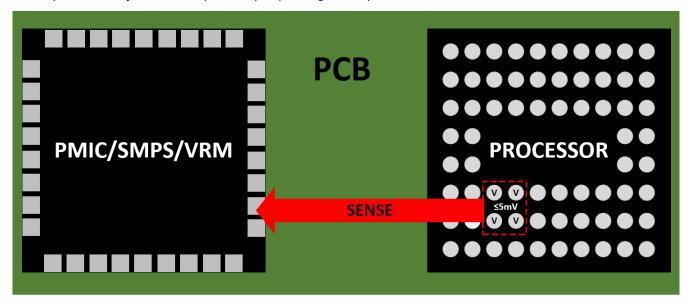

Ohm's Law (V=IR) relates conduction current to voltage drop, and at DC, the relation coefficient is a constant representing the resistance of the conductor. Conductors also dissipate power due to their resistance. Both voltage drop and power dissipation are proportional to the resistance of the conductor. Static IR or DC analysis/design methodology consists of designing the power distribution network such that the voltage drop (under DC operating conditions) across the power and ground pads of the application processor device is within a specified value of the nominal voltage to ensure proper functionality of the device. The PCB-level static IR drop budget is defined between the *pins/pads* of the power management device (PMIC/VRM/SMPS) and the *BGA balls* on the application processor device to which the power management device is supplying power (see Figure 4-2).

Figure 4-2. PCB IR Drop Budget

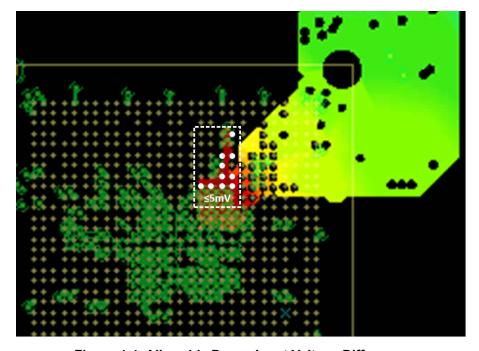

Given the total system-level margin allowed for proper device functionality, allowable voltage variation at the BGA of the device is typically specified at 2.5% of the nominal voltage. <sup>1</sup> For devices implementing remotesense functionality, it is a requirement that the power management device feedback/sense line(s) be placed as close to the relevant processor power balls as physically possible (see Figure 4-3) and that a supply input voltage difference of ≤5 mV under maximum current loading is maintained across all balls connected to a common power rail. This 5 mV maximum represents any voltage difference that may exist between a remote sense point and any associated power input (see Figure 4-4).

Figure 4-3. Sense Line Placement

Figure 4-4. Allowable Power Input Voltage Difference

<sup>1</sup> This is a generic recommendation and may not apply to your specific processor. For processor requirements, see the device-specific data sheet.

# **5 Dynamic Analysis of PCB PDN**

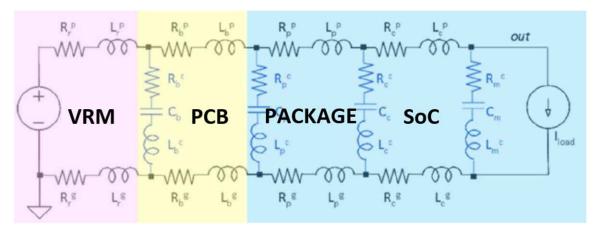

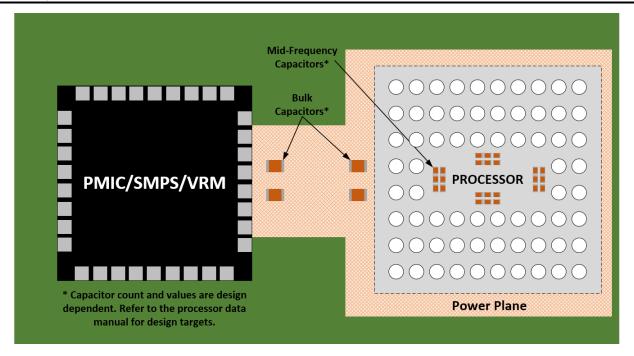

The typical elements of the PDN are shown in Figure 5-1; which includes the chip-level power distribution with thin-oxide decoupling capacitors. The package-level power distribution with planes and mid-frequency decoupling capacitors; and the board-level (for example, PCB) power distribution with planes, low-frequency ceramic and bulk decoupling capacitors, and the voltage regulator module (VRM).

Figure 5-1. Components of a Typical Power Distribution Network (PDN)

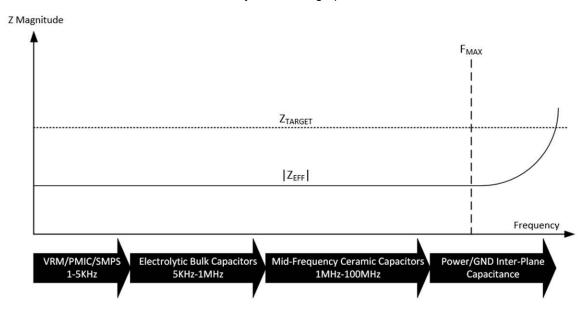

The frequency ranges covered by these elements are shown in Figure 5-2. As the primary focus is on optimizing the PCB PDN for high performance, the methodology is developed around the areas over which the PCB designer has control over and can influence early in the design phase.

Figure 5-2. Decoupling Frequency Range of PCB Components

The VRM/PMIC/SMPS (or simply voltage regulator device) is the first major component of the PDN. It observes its output voltage and adjusts the amount of current being supplied to keep the voltage constant. Most common voltage regulators make this adjustment on the order of milliseconds to microseconds. They are effective at maintaining output voltage for events at all frequencies from DC to a few kilohertz (depending on the regulator dynamic response time). For all transient events that occur at frequencies above this range, there is a time delay before the voltage regulator can respond to the new level of demand. During this time delay the rail suffers from voltage droop. A power delivery network has an impedance ( $Z_{PDN}$ ) associated with the path from the voltage regulator module to the processor. The magnitude of noise (voltage ripple) seen on a given power rail is proportional to the impedance ( $Z_{PDN}$ ) and the transient current ( $I_{TRANSIENT}$ ) draw associated with that rail.

Based on Ohm's Law,

$$V_{RIPPLE} = I_{TRANSIENT} \times Z_{PDN}$$

(2)

Typically the transient current is application-specific and is determined by a particular switching scenario. As a board designer, you have the ability to minimize the voltage ripple by reducing  $Z_{PDN}$  either by reducing the inductance, or by maximizing the capacitance. To ensure that the voltage ripple noise is within the processor's specification, the  $Z_{PDN}$  must be designed to meet a certain impedance, referred to as the target impedance ( $Z_{TARGET}$ ). Using frequency domain target impedance method (FDTIM) to describe the behavior of a power delivery system has been widely accepted.

The key concept of the FDTIM is the determination of the target impedance  $Z_{TARGET}$  (see Equation 3) for the power rail under consideration. For reliable operation of a power delivery system, its impedance spectrum needs to be maintained below the target value at the frequencies from DC to FMAX (see Figure 5-2). FMAX is the point in frequency after which adding a reasonable number of decoupling capacitors does not bring the power rail impedance |ZEFF| below the target impedance ( $Z_{TARGET}$ ) due to the dominance of the parasitic planar spreading inductance and package inductances.

$$Z_{TARGET} = \frac{Voltage \ Rail \times \%Ripple}{0.5 \times IMax}$$

(3)

# 5.1 Selecting Decoupling Capacitors to Meet Z<sub>TARGET</sub>

To maintain power integrity throughout the entire frequency range of interest, the power distribution network relies on the voltage regulator module (VRM/SMPS), the on-board discrete bulk electrolytic and ceramic decoupling capacitors, and the inter-plane capacitances (capacitance from the power-ground sandwich in the board stack-up). For a first-order analysis, the VRM of the power management integrated circuit (PMIC) can be modeled as a series-connected resistor and inductor. A PMIC, at low frequencies (up to 500 KHz-1 MHz), typically has low impedance and is capable of responding to the instantaneous requirements of the processor. The ESR and ESL values for the VRM are therefore very low. Beyond lower frequencies, the VRM impedance is primarily inductive, making it incapable of meeting the transient current requirement of the device. The bulk and ceramic discrete decoupling capacitors must provide the required low impedance from the point at which the VRM becomes inductive. The effectiveness of the bulk and mid-frequency decoupling capacitors (1 MHz-70 MHz, depending on the capacitor's ESL and ESR) is limited by its placement (due to loop inductance), value, and type. Refer to Figure 5-3 for a capacitor placement example. Note that in order to minimize the loop inductance, the mid-frequency capacitors have been placed directly underneath the processor (on the bottom side of the PCB).

Figure 5-3. Example Capacitor Placement

The bulk capacitors should be located near the point of entry of the supply entrance to the board. The decoupling capacitors maintain the PDN impedance at the required value beyond the VRM frequency and until the frequency at which mid-frequency capacitors become useful. The mid-frequency SMT capacitors are useful in the 10 to 150 MHz range and higher. These capacitors are primarily ceramic capacitors that come in several dielectric types (NPO, X7R, X5R, and Y5V) and several sizes (1206, 0805, 0603, 0402, and so forth). The mid-frequency capacitors are much smaller than the bulk capacitors and can be placed closer to the transistor circuit. Since the ceramic capacitors are smaller, they have lower ESR and ESL and lower capacitance than bulk capacitors, leading to a higher resonance frequency with smaller impedance at resonance. Therefore, ceramic capacitors can be used at higher frequencies. Typical mid-frequency capacitors have capacitance in the range of 1 nF -100 nF, ESR in the range of 10-100 m $\Omega$ , and ESL in the range of 0.5 nH -1 nH.

The concept of "loop inductance" is a useful metric for quantifying the effectiveness of the decoupling capacitors of a power distribution network. To calculate the "loop inductance" associated with decoupling capacitor placement, Equation 4 can be used:

$$L_{eff} = \frac{Imaginary \left(Z \left(Power, GND \text{ pads of decap}\right)\right)}{2 \times \pi \times Frequency} \tag{4}$$

Where  $L_{eff}$  is the effective loop inductance, Z (power, GND pads of decap) represents the Z-parameters of the port defined across the power and ground pads of the corresponding decap. The frequency should be chosen in the "flat" region of the Z-parameter response, typically in the 50 MHz – 70 MHz range.

www.ti.com Checklist for PDN

#### 6 Checklist for PDN

Although this list is not inclusive of every parameter and variable that must be considered when designing a PCB, a PDN-optimized PCB design will implement these guidelines:

- Power and ground plane pairs (or "islands") should be closely coupled together. The capacitance formed between the planes can be used to decouple the power supply at high frequencies.

- Whenever possible, the power and ground planes should be solid as this provides a continuous return path for return current.

- Use a thin dielectric thickness between the power and ground plane pair. Capacitance is inversely proportional to the separation of the plane pair so minimizing the separation distance (such as, the dielectric thickness) will maximize the resulting capacitance.

- The placement of power and ground planes in the PCB stack-up (determined by layer assignment) has a significant impact on the parasitic inductances of power current path. For this reason, it is recommended to consider layer order in the early stages of the PCB PDN design cycle, placing high priority supplies in the upper-half of the stack-up and low priority supplies in the lower half of the stack-up. This helps to minimize the loop inductance caused by decoupling capacitors and their associated vias.

- External power trace routing between components should be as wide as possible as wider traces result in reduced DC resistance and consequently a lower static IR drop.

- Whenever possible, attempt to achieve a ratio of 1:1 (or better) for component pins and associated vias. Do not share vias among multiple capacitors.

- Placement of decoupling capacitors and their associated vias should be as close to the processor ball as possible. Reserve the space directly underneath the processor for this purpose.

- Use of short and wide surface traces to connect capacitor pads to the vias connected to the planes below is preferred.

- Use of large diameter vias is preferred for reduced inductance/resistance.

- 1 oz 2 oz Cu weight for power / ground plane is preferred to enable better PCB heat spreading, which helps to reduce processor junction temperatures. In addition, it is preferable to have the power / ground planes be located adjacent to the PCB surface on which the processor is mounted.

- Place the VRM as close as possible to the processor and on the same side of the PCB. In cases where a

power management IC (PMIC) is implemented as the VRM, it should be aligned to minimize distance for the

highest current rail.

# 7 Implementation Examples and PDN Targets

This section provides device-specific PDN targets and implementation examples that meet these targets.

#### Note

The decoupling capacitor counts and/or capacitor values presented in this document are PCB designspecific and should not be used in lieu of PCB simulations. It is the responsibility of the PCB designer to ensure that any design meets the provided PDN targets.

## 7.1 AM570x

Materials: Isola 370H High-Tg FR4

| Requirement              | Req. Thickness | Tol +  | Tol -  | Calc Thick |  |

|--------------------------|----------------|--------|--------|------------|--|

| Incl. Plating & Mask     | 0.0620         | 0.0062 | 0.0062 | 0.0622     |  |

| Incl. Mask over Laminate | 0.0580         | 0.0058 | 0.0058 | 0.0582     |  |

| Incl. Plating            | 0.0610         | 0.0061 | 0.0061 | 0.0612     |  |

| After Lamination         | 0.0576         | 0.0029 | 0.0029 | 0.0578     |  |

| Over Laminate            | 0.0570         | 0.0057 | 0.0057 | 0.0572     |  |

| Impedance Type                          | Layer | Design  | Actual | Pitch  | Plane | Target | Tol<br>(ohms) | Predict |       |  |

|-----------------------------------------|-------|---------|--------|--------|-------|--------|---------------|---------|-------|--|

| Surface MS                              | L1    | 0.0050  | 0.0050 | _ 💯    |       |        |               | 49.89   |       |  |

| 0.0000000000000000000000000000000000000 |       | -       |        | *      | L2    | 50     | 5             | 49.89   |       |  |

| 2 EC Microstrip                         | L1    | 0.00480 | 0.0046 | 0.0110 |       | 8225   |               | 50.00   |       |  |

|                                         | -     | 0.00480 | 0.0046 | -      | L2    | 90     | 9             | 90.71   |       |  |

| 3 EC Microstrip                         | L1    | 0.00440 | 0.0042 | 0.0140 |       | 100    |               |         |       |  |

| ·                                       | -     | 0.00440 | 0.0042 |        | L2    |        | 10            | 100.04  |       |  |

| 4 Stripline                             | L3    | 0.00525 | 0.0054 | - S    | L2    | TOWAY! | 50            | 5       | 50.01 |  |

|                                         | -     | -       |        |        | L5    | 50     |               | 50,01   |       |  |

| 5 EC Stripline                          | L3    | 0.00450 | 0.0045 | 0.0140 | L2    |        | 14.0          |         |       |  |

|                                         |       | 0.00450 | 0.0045 |        | L5    | 100    | 10            | 100.18  |       |  |

| EC Stripline                            | L3    | 0.0050  | 0.0050 | 0.0110 | L2    |        |               |         |       |  |

|                                         | 2     | 0.0050  | 0.0050 |        | L5    | 90     | 9.0           | 89.67   |       |  |

Plane Pitch Target Predict Impedance Type Layer Design Actual L4 0.00525 0.0054 Stripline 1.2 50 5 50.03 . . -. L5 EC Stripline L4 0.00450 0.0045 0.0140 L2 100 10 100.22 0.00450 0.0045 L5 0.0110 EC Stripline L4 0.0050 0.0050 12 90 9 89.71 0.0050 0.0050 L5 **EC Microstrip** L6 0.00440 0.0041 0.0140 L5 100 10 99.6 0.00440 0.0041 . 0.0110 **EC Microstrip** L6 0.00480 0.0046 L5 90 9 89.44 0.00480 0.0046 L6 0.0050 0.0048 L5 Surface MS 49.88

Table 7-1. AM570x PDN Targets and Decoupling Example

|                                | Static<br>PDN<br>Target                  | Dynamic PDN Targets                          |                          |                                   |           | Number of Decoupling Capacitors Per Supply (1) (2) (3) (4) (5) (6) (9) |           |         |           |           |          |          |

|--------------------------------|------------------------------------------|----------------------------------------------|--------------------------|-----------------------------------|-----------|------------------------------------------------------------------------|-----------|---------|-----------|-----------|----------|----------|

| Supply<br>Name <sup>(10)</sup> | Max R <sub>eff</sub> (mΩ) <sup>(7)</sup> | Dec Cap<br>Max LL<br>(nH) <sup>(6) (8)</sup> | Max<br>Impedance<br>(mΩ) | Frequency<br>of Interest<br>(MHz) | 100<br>nF | 220<br>nF                                                              | 470<br>nF | 1<br>µF | 2.2<br>μF | 4.7<br>μF | 10<br>μF | 22<br>µF |

| VDD_CORE                       | 18                                       | 2                                            | 57                       | ≤20                               |           |                                                                        | 5         | 4       |           |           | 1        |          |

| VDD_DSP                        | 22                                       | 2.5                                          | 54                       | ≤20                               |           |                                                                        | 6         | 5       |           |           | 2        |          |

| VDDS_DDR1                      | 10                                       | 2.5                                          | 200                      | ≤100                              |           |                                                                        | 12        | 1       |           |           | 1        |          |

| CAP_VBBLDO_DSP                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |                                                                        |           | 1       |           |           |          |          |

| CAP_VBBLDO_GPU                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |                                                                        |           | 1       |           |           |          |          |

| CAP_VBBDLO_IVA                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |                                                                        |           | 1       |           |           |          |          |

| CAP_VBBLD0_MPU                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |                                                                        |           | 1       |           |           |          |          |

| CAP_VDDRAM_CORE1               | N/A                                      | 6                                            | N/A                      | N/A                               |           |                                                                        |           | 1       |           |           |          |          |

| CAP_VDDRAM_CORE2               | N/A                                      | 6                                            | N/A                      | N/A                               |           |                                                                        |           | 1       |           |           |          |          |

| CAP_VDDRAM_CORE3               | N/A                                      | 6                                            | N/A                      | N/A                               |           |                                                                        |           | 1       |           |           |          |          |

| CAP_VDDRAM_CORE4               | N/A                                      | 6                                            | N/A                      | N/A                               |           |                                                                        |           | 1       |           |           |          |          |

| CAP_VDDRAM_DSP                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |                                                                        |           | 1       |           |           |          |          |

| CAP_VDDRAM_GPU                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |                                                                        |           | 1       |           |           |          |          |

| CAP_VDDRAM_IVA                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |                                                                        |           | 1       |           |           |          |          |

| CAP_VDDRAM_MPU                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |                                                                        |           | 1       |           |           |          |          |

- (1) For more information on peak-to-peak noise values, see the *Recommended Operating Conditions* table in the device-specific data manual.

- (2) ESL must be as low as possible and not exceed 0.5 nH.

- (3) The power delivery network (PDN) impedance characteristics are defined versus the device activity (that runs at different frequency) based on the *Recommended Operating Conditions* table in the *Specifications* chapter of the device-specific data manual.

- (4) The static drop requirement drives the maximum acceptable PCB resistance between the PMIC or the external SMPS and the processor power balls.

- (5) Assuming that the external SMPS (power IC) feedback sense is taken close to processor power balls.

- (6) High-frequency (30 MHz 70 MHz) PCB decoupling capacitors.

- (7) Maximum R<sub>eff</sub> from VRM/SMPS/PMIC to processor.

- (8) Maximum loop inductance for decoupling capacitor.

- (9) Decoupling capacitor counts and values are provided as a baseline recommendation only. TI recommends that all PCB designs be simulated prior fabrication to ensure that the processor PDN requirements are met.

- (10) Ganged rails must meet all requirements of each member rail.

#### 7.2 AM571x

| Layer      | Calc<br>Thickness |

|------------|-------------------|

| Layer - 1  | 0.0005            |

| Layer      | 0.0037            |

| Layer - 2  | 0.0012            |

|            | 0.0060            |

| Layer - 3  | 0.0006            |

|            | 0.0048            |

| Layer - 4  | 0.0006            |

|            | 0.0041            |

| Layer - 5  | 0.0006            |

|            | 0.0048            |

| Layer - 6  | 0.0006            |

|            | 0.0041            |

| Layer - 7  | 0.0006            |

|            | 0.0048            |

| Layer - 8  | 0.0006            |

|            | 0.0030            |

| Layer - 9  | 0.0006            |

|            | 0.0048            |

| Layer - 10 | 0.0006            |

|            | 0.0041            |

| Layer - 11 | 0.0006            |

|            | 0.0048            |

| Layer - 12 | 0.0006            |

|            | 0.0041            |

| Layer - 13 | 0.0006            |

|            | 0.0048            |

| Layer - 14 | 0.0006            |

|            | 0.0060            |

| Layer - 15 | 0.0012            |

| 1 40       | 0.0037            |

| Layer - 16 | 0.0017<br>0.0005  |

| Description                          | Dk / Df       |

|--------------------------------------|---------------|

| Taiyo 4000-BN<br>1/4oz Mix (Std Plt) | 4.71 / 0.0330 |

| 370H                                 | 4.34 / 0.0210 |

| 1oz P/G                              |               |

| 370H                                 | 4.33 / 0.0210 |

| 1/2oz Mix                            |               |

| 370H                                 | 4.06 / 0.0210 |

| 1/20z P/G                            |               |

| 370H                                 | 4.54 / 0.0190 |

| 1/2oz Mix                            |               |

| 370H                                 | 4.06 / 0.0210 |

| 1/2oz P/G                            |               |

| 370H                                 | 4.54 / 0.0190 |

| 1/2oz Mix                            |               |

| 370H                                 | 4.06 / 0.0210 |

| 1/20z P/G                            |               |

| 370H                                 | 4.57 / 0.0190 |

| 1/20z P/G                            |               |

| 370H                                 | 4.06 / 0.0210 |

| 1/2oz Mix                            |               |

| 370H                                 | 4.54 / 0.0190 |

| 1/20Z P/G                            |               |

| 370H                                 | 4.06 / 0.0210 |

| 1/2oz Mix                            |               |

| 370H                                 | 4.54 / 0.0190 |

| 1/20z P/G                            |               |

| 370H                                 | 4.06 / 0.0210 |

| 1/2oz Mix                            |               |

| 370H                                 | 4.33 / 0.0210 |

| 1oz P/G                              |               |

| 370H                                 | 4.34 / 0.0210 |

| 1/4oz Mix (Std Plt)<br>Taiyo 4000-BN | 4.71 / 0.0330 |

|                                      |               |

Materials: Isola 370H High-Tg FR4

| Requirement              | Req. Thickness | Tol+   | Tol -  | Calc Thick |  |  |

|--------------------------|----------------|--------|--------|------------|--|--|

| Incl. Plating & Mask     | 0.0800         | 0.0080 | 0.0080 | 0.0816     |  |  |

| Incl. Mask over Laminate | 0.0766         | 0.0077 | 0.0077 | 0.0782     |  |  |

| Incl. Plating            | 0.0790         | 0.0079 | 0.0079 | 0.0806     |  |  |

| Requirement      | Req. Thickness | Tol+   | Tol -  | Calc Thick |  |

|------------------|----------------|--------|--------|------------|--|

| After Lamination | 0.0762         | 0.0038 | 0.0038 | 0.0778     |  |

| Over Laminate    | 0.0756         | 0.0076 | 0.0076 | 0.0772     |  |

#### Job Comment Sim to pn 516581 Rev F and 517391A

| Impedance Type             | Layer | Design  | Actual | Pitch  | Plane | Target        | Tol<br>(ohms) | Predict    |      |       |

|----------------------------|-------|---------|--------|--------|-------|---------------|---------------|------------|------|-------|

| Surface MS                 | L1    | 0.00550 | 0.0055 | 123    | 23    | 50            | -             | 40.00      |      |       |

| Description of the Control |       |         | -      | F0     | L2    | 50            | 5             | 49.83      |      |       |

| EC Microstrip              | L1    | 0.00470 | 0.0047 | 0.0100 |       | 658           | 9             | 522284     |      |       |

|                            | 1 05  | 0.00470 | 0.0047 |        | L2    | 90            | 9             | 89.73      |      |       |

| EC Microstrip              | L1    | 0.0040  | 0.0040 | 0.0105 |       | COMMUNICATION |               |            |      |       |

|                            | 1.8   | 0.0040  | 0.0040 | 80     | L2    | 100           | 10            | 99.29      |      |       |

| Stripline                  | L3    | 0.00450 | 0.0045 | . 8    | L2    | 17220         | - 2           |            |      |       |

|                            | 134   |         |        |        | L4    | 50            | 5             | 50.71      |      |       |

| EC Stripline               | L3    | 0.0050  | 0.0050 | 0.0120 | L2    |               |               |            |      |       |

|                            | 15    | 0.0050  | 0.0050 |        | L4    | 90            | 9.0           | 90.96      |      |       |

| EC Stripline               | L3    | 0.00370 | 0.0037 | 0.0090 | L2    | 1 2120237     | 00000         | 17-12-3-15 |      |       |

|                            | -     | 0.00370 | 0.0037 | -      | L4    | 100           | 10            | 100.20     |      |       |

| Stripline                  | L5    | 0.00370 | 0.0037 | -      | L4    | 2200          | 1 00          | russear    |      |       |

|                            | -     | -       |        |        | L6    | 50            | 5             | 49.84      |      |       |

| EC Stripline               | L5    | 0.00360 | 0.0036 | 0.0120 | L4    | i comen       |               |            |      |       |

|                            | ( B   | 0.00360 | 0.0036 |        | L6    | 100           | 100           | 100        | 10.0 | 98.59 |

| Stripline                  | L7    | 0.00370 | 0.0037 |        | L6    | 17200         | 12            | 100000     |      |       |

|                            | 134   |         |        | - 2    | L8    | 50            | 5             | 49.84      |      |       |

| EC Stripline               | L7    | 0.00360 | 0.0036 | 0.0120 | L6    |               |               |            |      |       |

|                            | j 15  | 0.00360 | 0.0036 |        | L8    | 100           | 10.0          | 98.59      |      |       |

| 1 Stripline                | L10   | 0.00370 | 0.0037 | - 43   | L9    | TO BEAUTI     | 120           | 778787     |      |       |

|                            |       |         | )(*)   | •      | L11   | 50            | 5             | 49.84      |      |       |

| 2 EC Stripline             | L10   | 0.00360 | 0.0036 | 0.0120 | L9    | 7983          | 000000        | 2000       |      |       |

|                            | -     | 0.00360 | 0.0036 | -      | L11   | 100           | 10.0          | 98.59      |      |       |

| 3 Stripline                | L12   | 0.00370 | 0.0037 |        | L11   |               |               |            |      |       |

|                            | 100   | 17.0    |        | 15     | L13   | 50            | 5             | 49.84      |      |       |

| EC Stripline               | L12   | 0.00360 | 0.0036 | 0.0120 | L11   | 100           | 40.0          | 00.55      |      |       |

|                            | 12    | 0.00360 | 0.0036 | -      | L13   |               | 10.0          | 98.59      |      |       |

| 5 Stripline                | L14   | 0.00450 | 0.0045 | - 8    | L13   | 22.1          |               |            |      |       |

|                            | 0.5   |         |        | - 3    | L15   | 50            | 5             | 50.71      |      |       |

| Impedance Type                 | Layer | Design  | Actual | Pitch  | Plane | Target | Tol<br>(ohms) | Predict   |    |  |

|--------------------------------|-------|---------|--------|--------|-------|--------|---------------|-----------|----|--|

| EC Stripline                   | L14   | 0.00370 | 0.0037 | 0.0090 | L13   |        |               |           |    |  |

|                                | 2     | 0.00370 | 0.0037 |        | L15   | 100    | 10            | 100.20    |    |  |

| 7 Surface MS                   | L16   | 0.00550 | 0.0055 | -      | L15   |        | - 52          |           |    |  |

|                                |       |         | -      | - 0    | 2     | 50     | 5             | 49.84     |    |  |

| 8 EC Microstrip                | L16   | 0.00470 | 0.0047 | 0.0100 | L15   |        |               |           |    |  |

| 4                              | 100   | 0.00470 | 0.0047 | 51     | 2     | 90     | 9             | 89.73     |    |  |

| 9 EC Microstrip                | L16   | 0.0040  | 0.0040 | 0.0105 | L15   | 100    | 400           | 400       | 10 |  |

| and a version of the second of | -     | 0.0040  | 0.0040 | -      | -     |        | 10            | 99.29     |    |  |

| EC Microstrip                  | L1    | 0.00350 | 0.0035 | 0.0120 |       | 10,000 | 1<br>P2/2027  | Manager 1 |    |  |

|                                | 95    | 0.00350 | 0.0035 |        | L2    | 110    | 11.0          | 109.02    |    |  |

| 21 EC Microstrip               | L1    | 0.00560 | 0.0056 | 0.0120 |       | 87     |               |           |    |  |

|                                | 100   | 0.00560 | 0.0056 |        | L2    |        | 8.7           | 86.46     |    |  |

| 22 EC Microstrip               | L16   | 0.00560 | 0.0056 | 0.0120 | L15   | 227    | 8.7           | 20.00     |    |  |

|                                | S-    | 0.00560 | 0.0056 |        |       | 87     | 8.7           | 86.46     |    |  |

Table 7-2. AM571x PDN Targets and Decoupling Example

|                                |                                          |                                              |                          | J                                 |           | -         | •               |                    |                                   |                         |          |          |

|--------------------------------|------------------------------------------|----------------------------------------------|--------------------------|-----------------------------------|-----------|-----------|-----------------|--------------------|-----------------------------------|-------------------------|----------|----------|

|                                | Static<br>PDN<br>Target                  |                                              | Dynamic PDN Ta           | argets                            |           | Capacit   | Numb<br>ors Per | er of De<br>Supply | ecoupli<br>/ <sup>(1) (2) (</sup> | <b>ng</b><br>3) (4) (5) | (6) (9)  |          |

| Supply<br>Name <sup>(10)</sup> | Max R <sub>eff</sub> (mΩ) <sup>(7)</sup> | Dec Cap<br>Max LL<br>(nH) <sup>(6) (8)</sup> | Max<br>Impedance<br>(mΩ) | Frequency<br>of Interest<br>(MHz) | 100<br>nF | 220<br>nF | 470<br>nF       | 1<br>µF            | 2.2<br>µF                         | 4.7<br>μF               | 10<br>μF | 22<br>µF |

| VDD_CORE                       | 27                                       | 2                                            | 87                       | ≤50                               | 6         | 1         | 1               | 1                  | 1                                 | 1                       |          |          |

| VDD_MPU                        | 10                                       | 2                                            | 57                       | ≤20                               | 8         | 1         | 1               | 1                  | 1                                 | 1                       |          | 1        |

| VDD_DSP<br>VDD_GPU<br>VDD_IVA  | 13                                       | 2.5                                          | 54                       | ≤20                               | 8         | 1         | 1               | 1                  | 1                                 | 1                       | 1        | 1        |

| VDDS_DDR1                      | 10                                       | 2.5                                          | 200                      | ≤100                              | 8         | 4         |                 | 2                  |                                   | 2                       |          | 1        |

| CAP_VBBLDO_DSP                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |                 | 1                  |                                   |                         |          |          |

| CAP_VBBLDO_GPU                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |                 | 1                  |                                   |                         |          |          |

| CAP_VBBDLO_IVA                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |                 | 1                  |                                   |                         |          |          |

| CAP_VBBLD0_MPU                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |                 | 1                  |                                   |                         |          |          |

| CAP_VDDRAM_CORE1               | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |                 | 1                  |                                   |                         |          |          |

| CAP_VDDRAM_CORE3               | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |                 | 1                  |                                   |                         |          |          |

| CAP_VDDRAM_CORE4               | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |                 | 1                  |                                   |                         |          |          |

| CAP_VDDRAM_DSP                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |                 | 1                  |                                   |                         |          |          |

| CAP_VDDRAM_GPU                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |                 | 1                  |                                   |                         |          |          |

| CAP_VDDRAM_IVA                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |                 | 1                  |                                   |                         |          |          |

| CAP_VDDRAM_MPU                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |                 | 1                  |                                   |                         |          |          |

- (1) For more information on peak-to-peak noise values, see the *Recommended Operating Conditions* table in the device-specific data manual.

- (2) ESL must be as low as possible and not exceed 0.5 nH.

- (3) The power delivery network (PDN) impedance characteristics are defined versus the device activity (that runs at different frequency) based on the Recommended Operating Conditions table in the Specifications chapter of the device-specific data manual.

- (4) The static drop requirement drives the maximum acceptable PCB resistance between the PMIC or the external SMPS and the processor power balls.

- (5) Assuming that the external SMPS (power IC) feedback sense is taken close to processor power balls.

- (6) High-frequency (30 MHz 70 MHz) PCB decoupling capacitors.

- (7) Maximum R<sub>eff</sub> from VRM/SMPS/PMIC to processor.

- (8) Maximum loop inductance for decoupling capacitor.

- (9) Decoupling capacitor counts and values are provided as a baseline recommendation only. TI recommends that all PCB designs be simulated prior fabrication to ensure that the processor PDN requirements are met.

- (10) Ganged rails must meet all requirements of each member rail.

Dk / Df 4.71 / 0.0330 3.95 / 0.0210

4.33 / 0.0210

4.07 / 0.0210

4.40 / 0.0210

3.95 / 0.0210

4.40 / 0.0210

3.94 / 0.0210

4.57 / 0.0190

3.94 / 0.0210

4.40 / 0.0210

3.94 / 0.0210

4.40 / 0.0210

4.06 / 0.0210

4.33 / 0.0210

3.95 / 0.0210 4.71 / 0.0330

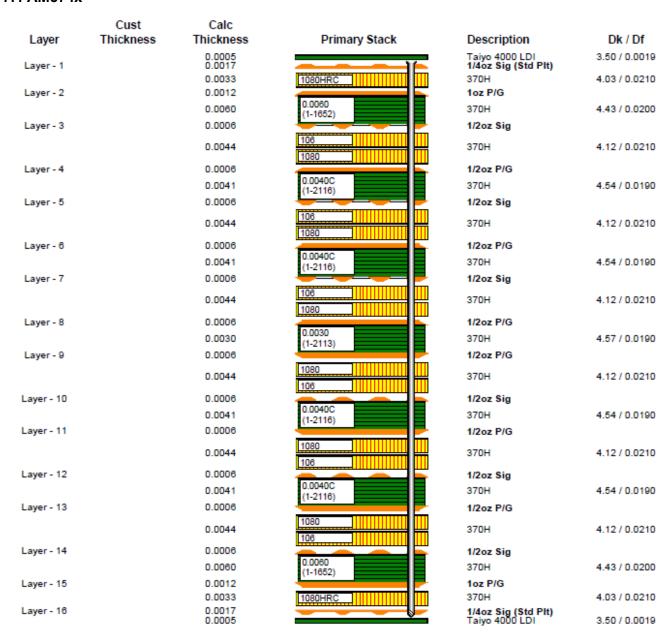

#### 7.3 AM572x

| Layer      | Calc<br>Thickness | Primary Stack              | Description                          |

|------------|-------------------|----------------------------|--------------------------------------|

| Layer - 1  | 0.0005<br>0.0017  |                            | Taiyo 4000-BN<br>1/4oz Mix (Std Pit) |

|            | 0.0039            | 106                        | 370H                                 |

| Layer - 2  | 0.0025            |                            | 2oz P/G                              |

|            | 0.0060            | 0.0060A<br>(1-2113/1-1080) | 370H                                 |

| Layer - 3  | 0.0006            |                            | 1/2oz Mix                            |

|            | 0.0047            | 106                        | 370H                                 |

| Layer - 4  | 0.0006            |                            | 1/20Z P/G                            |

|            | 0.0035            | 0.0035A<br>(1-2113)        | 370H                                 |

| Layer - 5  | 0.0006            | (12,10)                    | 1/2oz Mix                            |

|            | 0.0039            | 106                        | 370H                                 |

| Layer - 6  | 0.0006            |                            | 1/20Z P/G                            |

|            | 0.0035            | 0.0035A<br>(1-2113)        | 370H                                 |

| Layer - 7  | 0.0006            |                            | 1/2oz Mix                            |

|            | 0.0040            | 106                        | 370H                                 |

| Layer - 8  | 0.0006            |                            | 1/20Z P/G                            |

|            | 0.0030            | 0.0030 (1-2113)            | 370H                                 |

| Layer - 9  | 0.0006            |                            | 1/20Z P/G                            |

|            | 0.0040            | 106                        | 370H                                 |

| Layer - 10 | 0.0006            |                            | 1/2oz Mix                            |

|            | 0.0035            | 0.0035A<br>(1-2113)        | 370H                                 |

| Layer - 11 | 0.0006            |                            | 1/20Z P/G                            |

|            | 0.0040            | 106                        | 370H                                 |

| Layer - 12 | 0.0006            |                            | 1/2oz Mix                            |

|            | 0.0035            | 0.0035A<br>(1-2113)        | 370H                                 |

| Layer - 13 | 0.0006            |                            | 1/20z P/G                            |

|            | 0.0048            | 1080                       | 370H                                 |

| Layer - 14 | 0.0006            |                            | 1/2oz Mix                            |

|            | 0.0060            | 0.0060A<br>(1-2113/1-1080) | 370H                                 |

| Layer - 15 | 0.0025            |                            | 2oz P/G                              |

|            | 0.0039            | 106                        | 370H                                 |

| Layer - 16 | 0.0017<br>0.0005  |                            | 1/4oz Mix (Std Plt)<br>Taiyo 4000-BN |

Materials: Isola 370H High-Tg FR4

| Requirement              | Req. Thickness | Tol +  | Tol -  | Calc Thick |

|--------------------------|----------------|--------|--------|------------|

| Incl. Plating & Mask     | 0.0800         | 0.0080 | 0.0080 | 0.0788     |

| Incl. Mask over Laminate | 0.0766         | 0.0077 | 0.0077 | 0.0754     |

| Incl. Plating            | 0.0790         | 0.0079 | 0.0079 | 0.0778     |

| After Lamination         | 0.0762         | 0.0038 | 0.0038 | 0.0750     |

| Over Laminate            | 0.0756         | 0.0076 | 0.0076 | 0.0744     |

| Impedance Type        | Layer | Design  | Actual | Pitch    | Plane | Target | Tol<br>(ohms) | Predict         |

|-----------------------|-------|---------|--------|----------|-------|--------|---------------|-----------------|

| Surface MS            | L1    | 0.0050  | 0.0060 |          |       |        | 1983          | ****            |

|                       |       |         |        | *        | L2    | 50     | 5             | 51.11           |

| 2 EC Microstrip       | L1    | 0.00440 | 0.0052 | 0.0105   | 1     |        |               |                 |

|                       | 1 372 | 0.00440 | 0.0052 |          | L2    | 90     | 9             | 90.68           |

| 3 EC Microstrip       | L1    | 0.00380 | 0.0048 | 0.0120   | i i   | 1200   | 1987          |                 |

|                       |       | 0.00380 | 0.0048 |          | L2    | 100    | 10            | 99.26           |

| Stripline             | L3    | 0.00450 | 0.0045 | *        | L2    | 5 888  | 100           | 101112          |

|                       |       |         |        |          | L4    | 50     | 5             | 50.37           |

| EC Stripline          | L3    | 0.0050  | 0.0050 | 0.0120   | L2    |        |               |                 |

|                       |       | 0.0050  | 0.0050 |          | L4    | 90     | 9             | 90.45           |

| Stripline             | L5    | 0.0040  | 0.0033 |          | L4    | 2251   | 1 8483        | TO POST TO SEC. |

|                       | 940   | -       | 2.     | -        | L6    | 50     | 5             | 48.65           |

| Stripline             | L7    | 0.00330 | 0.0033 |          | L6    | 1 85   |               |                 |

|                       | 100   | 155     |        |          | L8    | 50     | 5             | 48.96           |

| Stripline             | L10   | 0.00330 | 0.0033 | 2        | L9    | 17000  | 100000        | N. NOVEMBER DE  |

|                       |       |         | -      | -        | L11   | 50     | 5             | 48.96           |

| Stripline             | L12   | 0.0040  | 0.0033 |          | L11   | 1998   | 9207          | 550000          |

|                       | (*)   |         | 10.00  |          | L13   | 50     | 5             | 48.96           |

| 0 Stripline           | L14   | 0.00450 | 0.0045 | *        | L13   |        |               |                 |

| - N                   | 3.00  | 1089    | 55     | 8        | L15   | 50     | 5             | 50.71           |

| 1 Surface MS          | L16   | 0.0050  | 0.0060 | _ 8      | L15   | 200    | 20032         | 14201000        |

| and the second second | 1.40  | (4-1    | -      |          | -     | 50     | 5             | 51.11           |

| 2 EC Microstrip       | L16   | 0.00350 | 0.0044 | 0.0105   | L15   |        |               |                 |

|                       | 350   | 0.00350 | 0.0044 | <b>*</b> |       | 100    | 10            | 99.49           |

| 3 EC Microstrip       | L1    | 0.00380 | 0.0038 | 0.0120   | 1 2   | ij.    |               | on nothing      |

|                       | -     | 0.00380 | 0.0038 | -        | L2    |        |               | 110.77          |

| 4 EC Microstrip       | L1    | 0.0060  | 0.0060 | 0.0120   |       |        |               | 100000          |

|                       | -     | 0.0060  | 0.0060 |          | L2    |        |               | 87.59           |

| 5 EC Microstrip       | L16   | 0.0060  | 0.0060 | 0.0120   | L15   |        |               |                 |

|                       | (*)   | 0.0060  | 0.0060 | *        |       | 1      |               | 87.60           |

Table 7-3. AM572x PDN Targets and Decoupling Example

|                                | Static<br>PDN<br>Target                  |                                              | Dynamic PDN Ta           | argets                            |           | Capacit   | Numbe     | er of De<br>Supply | coupli<br>(1) (2) (3 | <b>ng</b><br>3) (4) (5) | (6) (9)  |          |

|--------------------------------|------------------------------------------|----------------------------------------------|--------------------------|-----------------------------------|-----------|-----------|-----------|--------------------|----------------------|-------------------------|----------|----------|

| Supply<br>Name <sup>(10)</sup> | Max R <sub>eff</sub> (mΩ) <sup>(7)</sup> | Dec Cap<br>Max LL<br>(nH) <sup>(6) (8)</sup> | Max<br>Impedance<br>(mΩ) | Frequency<br>of Interest<br>(MHz) | 100<br>nF | 220<br>nF | 470<br>nF | 1<br>µF            | 2.2<br>μF            | 4.7<br>μF               | 10<br>μF | 22<br>µF |

| VDD_CORE                       | 27                                       | 2                                            | 87                       | ≤50                               | 6         | 1         | 1         | 1                  | 1                    | 1                       |          |          |

| VDD_MPU                        | 10                                       | 2                                            | 57                       | ≤20                               | 12        | 2         | 2         | 3                  | 1                    | 1                       |          | 1        |

| VDD_DSPEVE                     | 13                                       | 2.5                                          | 54                       | ≤20                               | 8         | 1         | 1         | 2                  | 1                    | 1                       | 1        |          |

| VDD_IVA                        | 48                                       | 2                                            | 800                      | ≤100                              | 5         |           | 1         |                    |                      | 1                       |          |          |

| VDD_GPU                        | 18                                       | 2.5                                          | 207                      | ≤50                               | 6         | 1         | 1         | 1                  | 1                    | 1                       |          |          |

| VDDS_DDR1                      | 10                                       | 2.5                                          | 200                      | ≤100                              | 8         | 4         |           | 2                  |                      | 2                       |          | 1        |

| VDDS_DDR2                      | 10                                       | 2.5                                          | 200                      | ≤100                              | 8         | 4         |           | 2                  |                      | 2                       |          | 1        |

| CAP_VBBLDO_DSPEVE              | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           | 1                  |                      |                         |          |          |

| CAP_VBBLDO_GPU                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           | 1                  |                      |                         |          |          |

| CAP_VBBDLO_IVA                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           | 1                  |                      |                         |          |          |

| CAP_VBBLD0_MPU                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           | 1                  |                      |                         |          |          |

| CAP_VDDRAM_CORE1               | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           | 1                  |                      |                         |          |          |

| CAP_VDDRAM_CORE2               | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           | 1                  |                      |                         |          |          |

| CAP_VDDRAM_CORE3               | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           | 1                  |                      |                         |          |          |

| CAP_VDDRAM_CORE4               | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           | 1                  |                      |                         |          |          |

| CAP_VDDRAM_CORE5               | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           | 1                  |                      |                         |          |          |

| CAP_VDDRAM_DSPEVE1             | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           | 1                  |                      |                         |          |          |

| CAP_VDDRAM_DSPEVE2             | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           | 1                  |                      |                         |          |          |

| CAP_VDDRAM_GPU                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           | 1                  |                      |                         |          |          |

| CAP_VDDRAM_IVA                 | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           | 1                  |                      |                         |          |          |

| CAP_VDDRAM_MPU1                | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           | 1                  |                      |                         |          |          |

| CAP_VDDRAM_MPU2                | N/A                                      | 6                                            | N/A                      | N/A                               |           |           |           |                    |                      |                         |          |          |

- (1) For more information on peak-to-peak noise values, see the *Recommended Operating Conditions* table in the device-specific data manual.

- (2) ESL must be as low as possible and not exceed 0.5 nH.

- (3) The power delivery network (PDN) impedance characteristics are defined versus the device activity (that runs at different frequency) based on the *Recommended Operating Conditions* table in the *Specifications* chapter of the device-specific data manual.

- (4) The static drop requirement drives the maximum acceptable PCB resistance between the PMIC or the external SMPS and the processor power balls.

- (5) Assuming that the external SMPS (power IC) feedback sense is taken close to processor power balls.

- (6) High-frequency (30 MHz 70 MHz) PCB decoupling capacitors.

- (7) Maximum R<sub>eff</sub> from VRM/SMPS/PMIC to processor.

- (8) Maximum loop inductance for decoupling capacitor.

- (9) Decoupling capacitor counts and values are provided as a baseline recommendation only. TI recommends that all PCB designs be simulated prior fabrication to ensure that the processor PDN requirements are met.

- (10) Ganged rails must meet all requirements of each member rail.

#### 7.4 AM574x

| Requirement              | Req. Thickness | Tol +  | Tol -  | Calc Thick |

|--------------------------|----------------|--------|--------|------------|

| Incl. Plating & Mask     | 0.0800         | 0.0080 | 0.0080 | 0.0784     |

| Incl. Mask over Laminate | 0.0766         | 0.0077 | 0.0077 | 0.0750     |

| Incl. Plating            | 0.0790         | 0.0079 | 0.0079 | 0.0774     |

| After Lamination         | 0.0762         | 0.0038 | 0.0038 | 0.0746     |

| Impedance Type   | Layer | Design  | Actual | Plotted | Pitch  | Plane | Target | Tol<br>(ohms) | Predict |

|------------------|-------|---------|--------|---------|--------|-------|--------|---------------|---------|

| 1 Surface MS     | L1    | 0.00520 | 0.0052 | 0.00558 | -      | -     |        |               |         |

|                  | -     | -       | -      | -       | -      | L2    | 50     | 5             | 49.67   |

| 2 EC Microstrip  | L1    | 0.00390 | 0.0039 | 0.00428 | 0.0105 | -     | 400    | 40            | 00.00   |

| -                | -     | 0.00390 | 0.0039 | 0.00428 | -      | L2    | 100    | 10            | 99.86   |

| 3 EC Microstrip  | L1    | 0.00540 | 0.0054 | 0.00578 | 0.0120 | -     | 07     | 8.7           | 87.08   |

|                  | -     | 0.00540 | 0.0054 | 0.00578 | -      | L2    | 87     | 0.1           | 07.00   |

| 4 Stripline      | L3    | 0.00430 | 0.0043 | 0.0048  | -      | L2    | E0.    | 5             | E0.00   |

|                  | -     | -       | ı      | -       | -      | L4    | 50     | 5             | 50.09   |

| 5 EC Stripline   | L3    | 0.00350 | 0.0035 | 0.0040  | 0.0090 | L2    | 100    | 10            | 100.69  |

|                  | -     | 0.00350 | 0.0035 | 0.0040  | -      | L4    | 100    | 10            | 100.69  |

| 6 Stripline      | L5    | 0.00350 | 0.0035 | 0.0040  | -      | L4    | 50     | 5             | 50.05   |

|                  | -     | -       | 1      | -       | -      | L6    | 50     | 5             | 50.05   |

| 7 Stripline      | L7    | 0.00350 | 0.0035 | 0.0040  | -      | L6    | E0.    | _             | E0.0E   |

|                  | -     | -       | -      | -       | -      | L8    | 50     | 5             | 50.05   |

| 8 Stripline      | L10   | 0.00350 | 0.0035 | 0.0040  | -      | L9    | 50     | 5             | 50.05   |

|                  | -     | -       | -      | -       | -      | L11   | 50     | 5             | 50.05   |

| 9 Stripline      | L12   | 0.00350 | 0.0035 | 0.0040  | -      | L11   | 50     | 5             | 50.05   |

|                  | -     | -       | -      | -       | -      | L13   | 30     | ,             | 30.03   |

| 10 EC Stripline  | L12   | 0.00340 | 0.0034 | 0.0039  | 0.0120 | L11   | 400    | 40            | 00.46   |

|                  | -     | 0.00340 | 0.0034 | 0.0039  | -      | L13   | 100    | 10            | 99.46   |

| 11 Stripline     | L14   | 0.00430 | 0.0043 | 0.0048  | -      | L13   | 50     | 5             | 50.09   |

|                  | -     | -       | ı      | -       | -      | L15   | 50     | 5             | 50.09   |