For most current data sheet and other product information, visit www.burr-brown.com

# Low Voltage, Low Power, 16-Bit, Mono Sound VOICE/MODEM CODEC

### **FEATURES**

- 16-BIT DELTA-SIGMA DAC AND ADC

- DESIGNED FOR MODEM ANALOG FRONT END: Supports up to 56kbps Operation

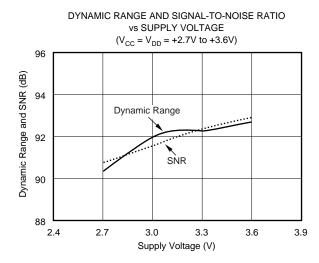

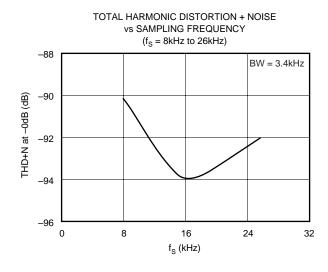

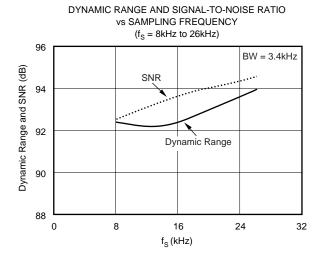

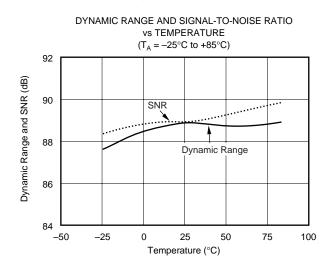

- ANALOG PERFORMANCE: Sampling Frequency: 7.2kHz to 26kHz Dynamic Range: 88dB (typ) at f<sub>S</sub> = 8kHz, f<sub>IN</sub> = 1kHz

- SYSTEM CLOCK: 512f<sub>S</sub>

- MASTER OR SLAVE OPERATION

- ON-CHIP CRYSTAL OSCILLATOR CIRCUIT

- ADC-TO-DAC LOOP-BACK MODE

- TIME SLOT MODE SUPPORTS UP TO FOUR CODECs ON A SINGLE SERIAL INTERFACE

- POWER-DOWN MODE: 60µA (typ)

### POWER SUPPLY: Single +2.7V to +3.6V

● SMALL PACKAGE: SSOP-24

### DESCRIPTION

The PCM3500 is a low cost, 16-bit CODEC designed for modem Analog Front End (AFE) and speech processing applications. The PCM3500's low power operation from +2.7V to +3.6V power supplies, along with an integrated power-down mode, make it ideal for portable applications.

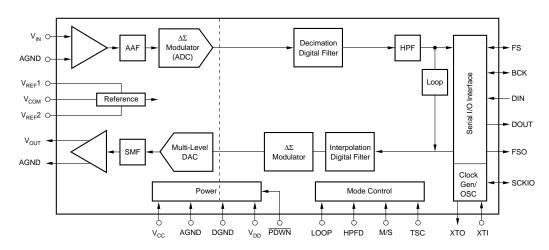

The PCM3500 integrates all of the functions needed for a modem or voice CODEC, including delta-sigma

### **APPLICATIONS**

- SOFTWARE MODEMS FOR: Personal Digital Assistant Notebook and Hand-Held PCs Set-Top Box Digital Television Embedded Systems

- PORTABLE VOICE RECORDER/PLAYER

- SPEECH RECOGNITION/SYNTHESIS

- TELECONFERENCING PRODUCTS

digital-to-analog and analog-to-digital converters, input anti-aliasing filter, digital high-pass filter for DC blocking, and an output low-pass filter. The synchronous serial interface provides for a simple, or glue-free interface to popular DSP and RISC processors. The serial interface also supports Time Division Multiplexing (TDM), allowing up to four CODECs to share a single 4-wire serial bus.

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111

Twx: 910-952-1111 • Internet: http://www.burr-brown.com/ • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

### **SPECIFICATIONS**

All specifications at +25°C,  $V_{DD} = V_{CC} = 3.3V$ ,  $f_S = 8kHz$ , and nominal system clock (XTI) =  $512f_S$ , unless otherwise noted. Measurement band is 100Hz to  $0.425f_S$ .

|                                                                                   |                                                         |                       | PCM3500E              |                       |                      |

|-----------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------|-----------------------|-----------------------|----------------------|

| PARAMETER                                                                         | CONDITIONS                                              | MIN                   | TYP                   | MAX                   | UNITS                |

| RESOLUTION                                                                        | CONDITIONS                                              |                       | 16                    | III) OX               | Bits                 |

| DATA FORMAT                                                                       |                                                         | +                     | 10                    |                       | טונס                 |

| Serial Data Interface Format                                                      |                                                         |                       | DSP Format            |                       |                      |

| Serial Data Bit Length                                                            |                                                         |                       | 16                    |                       | Bits                 |

| Serial Data Format                                                                |                                                         | MSB-Firs              | ।<br>st, Binary Two's | Complement            |                      |

| Sampling Frequency, f <sub>S</sub>                                                | ADC and DAC                                             | 7.2                   | 8                     | 26                    | kHz                  |

| System Clock Frequency, 512f <sub>S</sub>                                         |                                                         | 3.686                 | 4.096                 | 13.312                | MHz                  |

| DIGITAL INPUT/OUTPUT                                                              |                                                         |                       |                       |                       |                      |

| Logic Family                                                                      |                                                         |                       | CMOS                  |                       |                      |

| Input Logic Level: V <sub>IH</sub> <sup>(1)</sup>                                 |                                                         | 0.7 • V <sub>DD</sub> |                       |                       | VDC                  |

| V <sub>IL</sub> (1)                                                               |                                                         |                       |                       | 0.3 • V <sub>DD</sub> | VDC                  |

| Input Logic Current: I <sub>IN</sub> <sup>(2)</sup>                               |                                                         |                       |                       | ±1                    | μA                   |

| I <sub>IN</sub> (3)                                                               | 1 1 2 2 2                                               | V 0.2                 |                       | 100                   | μA<br>VDC            |

| Output Logic Level: V <sub>OH</sub> <sup>(4)</sup> V <sub>OL</sub> <sup>(4)</sup> | $I_{OUT} = -1mA$ $I_{OUT} = +1mA$                       | $V_{DD} - 0.3$        |                       | 0.3                   | VDC                  |

| <del></del>                                                                       | IOUT = TITIA                                            |                       |                       | 0.3                   | V DC                 |

| ADC CHARACTERISTICS                                                               |                                                         |                       | T .                   | ı                     |                      |

| DC ACCURACY                                                                       |                                                         |                       | 0.01/                 |                       | 1/2                  |

| Input Voltage Gain Error                                                          |                                                         |                       | 0.6 V <sub>CC</sub>   |                       | Vp-p<br>% of FSR     |

| Offset Error                                                                      | High-Pass Filter Disabled                               |                       | ±2<br>±2              | ±5                    | % of FSR<br>% of FSR |

| Input Resistance                                                                  | High-Pass Filler Disabled                               |                       | 50                    |                       | % 01 F3K<br>kΩ       |

| •                                                                                 |                                                         |                       | 30                    |                       | 1/22                 |

| AC ACCURACY THD+N                                                                 | f _ 1kHz \/ _ 0.5dP                                     |                       | -85                   | 90                    | dD                   |

| Dynamic Range                                                                     | $f_{IN} = 1kHz, V_{IN} = -0.5dB$<br>Without A-Weighting | 82                    | -85<br>88             | -80                   | dB<br>dB             |

| Signal-to-Noise Ratio                                                             | Without A-Weighting                                     | 82                    | 88                    |                       | dB                   |

| Crosstalk                                                                         | DAC Channel Idle, 0dB Input                             | 80                    | 85                    |                       | dB                   |

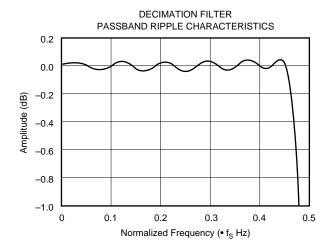

| Passband Ripple (internal HPF enabled)                                            | 0.0002f <sub>S</sub> to 0.425f <sub>S</sub>             |                       | ±0.05                 |                       | dB                   |

| Passband Ripple (internal HPF disabled)                                           | 0f <sub>S</sub> to 0.425f <sub>S</sub>                  |                       | ±0.05                 |                       | dB                   |

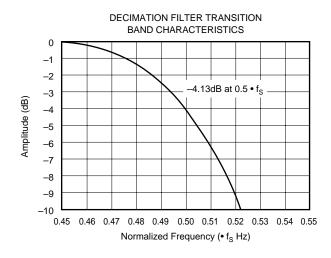

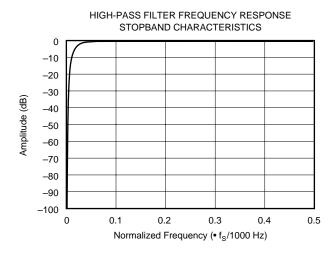

| Roll-Off at 0.00002f <sub>S</sub>                                                 | High-Pass Filter Enabled                                |                       | -3                    |                       | dB                   |

| Roll-Off at 0.56f <sub>S</sub>                                                    | High-Pass Filter Enabled                                |                       | -30                   |                       | dB                   |

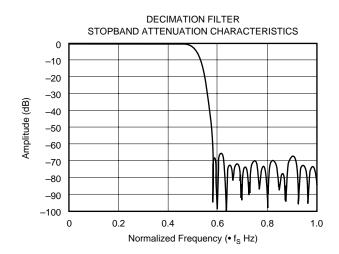

| Stopband Rejection                                                                | 0.58f <sub>S</sub> to f <sub>S</sub>                    |                       | -65                   |                       | dB                   |

| Group Delay                                                                       |                                                         |                       | 18/f <sub>S</sub>     | 4m                    | sec                  |

| DAC CHARACTERISTICS                                                               |                                                         |                       |                       |                       |                      |

| DC ACCURACY                                                                       |                                                         |                       |                       |                       |                      |

| Output Voltage                                                                    |                                                         |                       | 0.6 V <sub>CC</sub>   |                       | Vp-p                 |

| Gain Error                                                                        |                                                         |                       | ±1                    | ±5                    | % of FSR             |

| Offset Error                                                                      | High Pass Filter Disabled                               |                       | ±1                    |                       | % of FSR             |

| Load Resistance                                                                   |                                                         | 10                    |                       |                       | kΩ                   |

| AC ACCURACY                                                                       |                                                         |                       |                       | 6.5                   | ,,,                  |

| THD+N<br>Dynamic Range                                                            | f <sub>IN</sub> = 1kHz, V <sub>OUT</sub> = 0dB          | 9.4                   | -90<br>02             | -82                   | dB<br>dB             |

| Signal-to-Noise Ratio                                                             | Without A-Weighted Without A-Weighted                   | 84<br>84              | 92<br>92              |                       | dB<br>dB             |

| Crosstalk                                                                         | ADC Channel Idle, 0dB Input                             | 84                    | 92                    |                       | dВ                   |

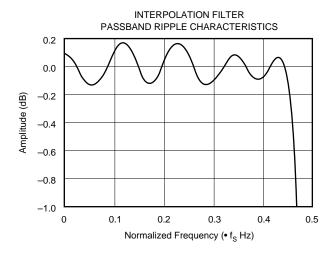

| Passband Ripple                                                                   | 0f <sub>S</sub> to 0.425f <sub>S</sub>                  |                       | ±0.4                  |                       | dB                   |

| Group Delay                                                                       | 2 3 11 3                                                |                       | 12/f <sub>S</sub>     | 4m                    | sec                  |

| POWER SUPPLY REQUIREMENTS                                                         |                                                         | 1                     |                       |                       |                      |

| Voltage Range                                                                     | $V_{CC}$ , $V_{DD}$                                     | 2.7                   | 3.3                   | 3.6                   | VDC                  |

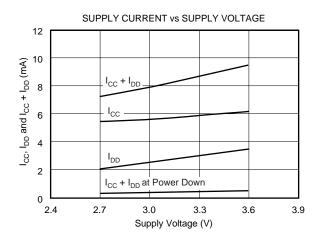

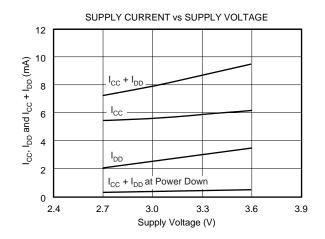

| Supply Current, I <sub>CC</sub> + I <sub>DD</sub>                                 | $V_{CC} = 3.3V$                                         |                       | 9                     | 12                    | mA                   |

| Total Supply Current in Power-Down Mode                                           | $V_{CC} = V_{DD} = 3.3V$ , XTI Stopped                  |                       | 60                    |                       | μΑ                   |

| Total Power Dissipation                                                           | $V_{CC} = V_{DD} = 3.3V$                                |                       | 30                    | 40                    | mW                   |

| TEMPERATURE RANGE                                                                 |                                                         |                       |                       |                       |                      |

| Operating                                                                         |                                                         | -25<br>-5             |                       | +85                   | °C                   |

| Storage Thermal Resistance, $\Theta_{JA}$                                         |                                                         | <b>–</b> 55           | 100                   | +125                  | °C/W                 |

|                                                                                   |                                                         |                       |                       |                       | J, 11                |

NOTES: (1) Pins 6, 7, 8, 9, 10, 15, 17, 18, 19, 20 (M/S, TSC, BCK, FS, DIN, SCKIO, XTI, HPFD, LOOP, PDWN). (2) Pins 8, 9, 10, 15, 17 (BCK, FS, DIN, SCKIO (Schmitt-Trigger input) XTI. (3) Pins 6, 7, 18, 19, 20 (M/S, TSC, HPFD, LOOP, PDWN; Schmitt-Trigger input with internal pull-down). (4) Pins 8, 9, 11, 12, 15, 16 (BCK, FS, DOUT, FSO, SCKIO, XTO).

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, +V <sub>DD</sub> , +V <sub>CC</sub> | +6.5V           |

|-----------------------------------------------------|-----------------|

| Supply Voltage Differences                          | ±0.1V           |

| GND Voltage Differences                             |                 |

| Input Current (any pins except supply)              | ±10mA           |

| Power Dissipation                                   | 300mW           |

| Operating Temperature Range                         | 25°C to +85°C   |

| Storage Temperature                                 | –55°C to +125°C |

| Junction Temperature                                | 150°C           |

| Lead Temperature (soldering, 5s)                    | +260°C          |

| (reflow, 10s)                                       | +235°C          |

|                                                     |                 |

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION

| PRODUCT  | PACKAGE      | PACKAGE SPECIFIED DRAWING TEMPERATURE NUMBER RANGE |                | PACKAGE<br>MARKING | ORDERING<br>NUMBER <sup>(1)</sup> | TRANSPORT<br>MEDIA     |  |

|----------|--------------|----------------------------------------------------|----------------|--------------------|-----------------------------------|------------------------|--|

| PCM3500E | 24-Lead SSOP | 338                                                | –25°C to +85°C | PCM3500E           | PCM3500E<br>PCM3500E/2K           | Rails<br>Tape and Reel |  |

NOTES: (1) Models with a slash (/) are available only in Tape and Reel in the quantities indicated (e.g., /2K indicates 2000 devices per reel). Ordering 2,000 pieces of "PCM3500E/2K" will get a single 2000-piece Tape and Reel.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

#### **PIN CONFIGURATION**

| Top View |      |                      |                     |  | S |

|----------|------|----------------------|---------------------|--|---|

|          | _    |                      |                     |  |   |

|          |      | O PCM3500            |                     |  |   |

|          | 1    | V <sub>COM</sub>     | V <sub>CC</sub> 24  |  |   |

|          | 2    | V <sub>REF</sub> 1 A | GND 23              |  |   |

|          | 3    | V <sub>REF</sub> 2   | V <sub>OUT</sub> 22 |  |   |

|          | 4    | V <sub>IN</sub> A    | GND 21              |  |   |

|          | 5    | AGND PI              | DWN 20              |  |   |

|          | 6    | M/S L                | OOP 19              |  |   |

|          | 7    | TSC H                | PFD 18              |  |   |

|          | 8 E  | ВСК                  | XTI 17              |  |   |

|          | 9 F  | FS                   | XTO 16              |  |   |

|          | 10   | DIN SO               | CKIO 15             |  |   |

|          | 11 [ | DOUT D               | GND 14              |  |   |

|          | 12 F | FSO                  | V <sub>DD</sub> 13  |  |   |

|          | _    |                      |                     |  |   |

#### **PIN ASSIGNMENTS**

| PIN | NAME               | I/O | DESCRIPTION                                                                                                                                                                                                        |

|-----|--------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>COM</sub>   | OUT | Common-Mode Voltage (0.5V <sub>CC)</sub> . This pin should be connected to ground through a capacitor.                                                                                                             |

| 2   | V <sub>REF</sub> 1 | _   | Decouple Pin for Reference Voltage 1 (0.99V <sub>CC</sub> ). This pin should be connected to ground through a capacitor.                                                                                           |

| 3   | V <sub>REF</sub> 2 | _   | Decouple Pin for Reference Voltage 2 (0.2V <sub>CC</sub> ). This pin should be connected to ground through a capacitor.                                                                                            |

| 4   | $V_{IN}$           | IN  | Analog Input for the ADC.                                                                                                                                                                                          |

| 5   | AGND               | _   | Analog Ground for the ADC Input Signal.                                                                                                                                                                            |

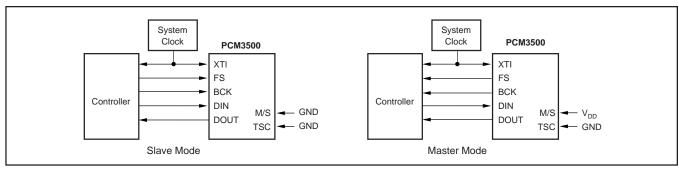

| 6   | M/S                | IN  | Master/Slave Select. This pin is used to determine the operating mode for the serial interface. A logic '0' on this pin selects the Slave Mode. A logic '1' on this pin selects the Master Mode. (2)               |

| 7   | TSC                | IN  | Time Slot Mode Control. This pin is used to select the time slot operating mode. A logic '0' on this pin disables Time Slot Mode. A logic '1' on this pin enables Time Slot Mode. <sup>(2)</sup>                   |

| 8   | BCK                | I/O | Bit Clock. This pin serves as the bit (or shift) clock for the serial interface. This pin is an input in Slave Mode and an output in Master Mode. <sup>(1)</sup>                                                   |

| 9   | FS                 | I/O | Frame Sync. This pin serves as the frame synchronization clock for the serial interface. This pin is an input in Slave Mode and an output in Master Mode. <sup>(1)</sup>                                           |

| 10  | DIN                | IN  | Serial Data Input. This pin is used to write 16-bit data to the DAC. <sup>(1)</sup>                                                                                                                                |

| 11  | DOUT               | OUT | Serial Data Output. The ADC outputs 16-bit data on this pin. <sup>(3)</sup>                                                                                                                                        |

| 12  | FSO                | OUT | Frame Sync Output. Active only when Time Slot Mode is enabled. This pin is set to a high impedance state when Time Slot mode is disabled (TSC = 0).                                                                |

| 13  | $V_{DD}$           | _   | Digital Power Supply. Used to power the digital section of the ADC and DAC, as well as the serial interface and mode control logic. This pin is not internally connected to V <sub>CC</sub> .                      |

| 14  | DGND               | _   | Digital Ground. Internally connected through the substrate to analog ground.                                                                                                                                       |

| 15  | SCKIO              | I/O | System Clock Input/Output. This pin is a system clock output when using the crystal oscillator or XTI as the system clock input; when XTI is connected to ground, this pin is a system clock input. <sup>(1)</sup> |

| 16  | XTO                | OUT | Crystal Oscillator Output.                                                                                                                                                                                         |

| 17  | XTI                | IN  | Crystal Oscillator Input or an External System Clock Input.                                                                                                                                                        |

| 18  | HPFD               | IN  | High-Pass Filter Disable. When this pin is set to a logic '1', the HPF function in the ADC is disabled. (2)                                                                                                        |

| 19  | LOOP               | IN  | ADC-to-DAC Loop-Back Control. When this pin is set to logic '1', the ADC data is fed to the DAC input. (2)                                                                                                         |

| 20  | PDWN               | IN  | Power Down and Reset Control. When this pin is logic '0', Power-Down Mode is enabled. The PCM3500 is reset on the rising edge of this signal. <sup>(2)</sup>                                                       |

| 21  | AGND               | _   | Analog Ground for the DAC Output Signal.                                                                                                                                                                           |

| 22  | V <sub>OUT</sub>   | OUT | Analog Output from the DAC Output Filter.                                                                                                                                                                          |

| 23  | AGND               | _   | Analog Ground. This is the ground for the internal analog circuitry.                                                                                                                                               |

| 24  | V <sub>CC</sub>    | _   | Analog Power Supply. Used to power the analog circuitry of the ADC and DAC.                                                                                                                                        |

NOTES: (1) Schmitt-Trigger input. (2) Schmitt-Trigger input with an internal pull-down resistor. (3) Tri-state output in Time Slot Mode.

### TYPICAL PERFORMANCE CURVES

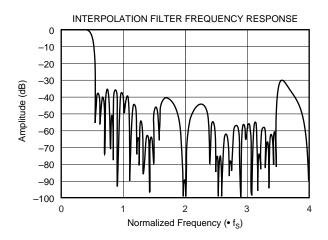

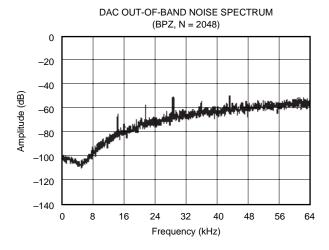

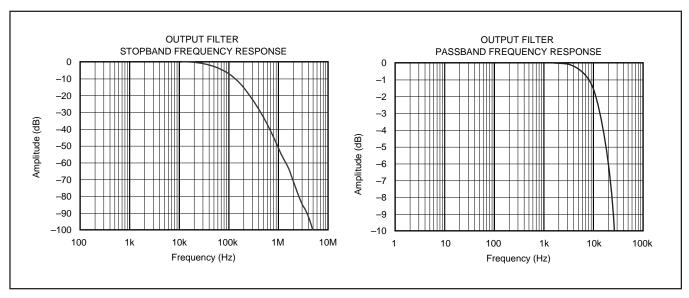

### **DAC SECTION**

**DIGITAL FILTER**

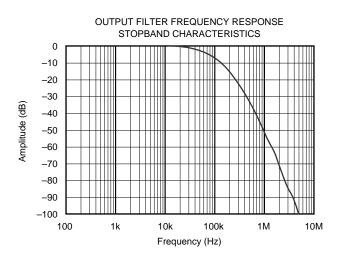

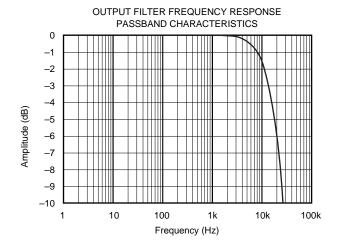

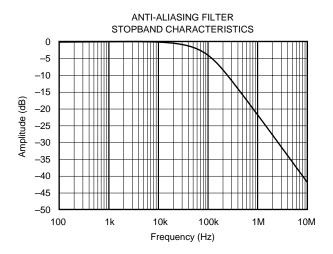

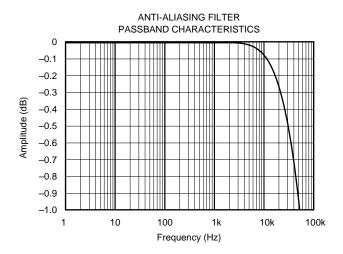

#### **ANALOG FILTER**

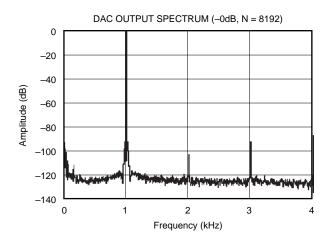

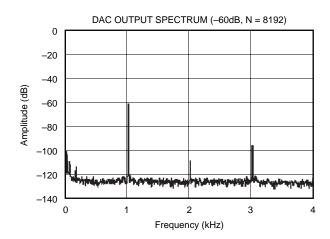

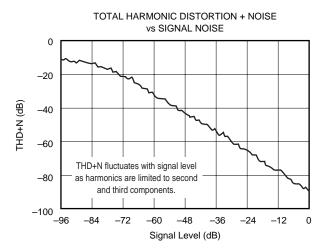

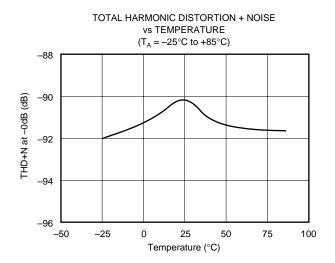

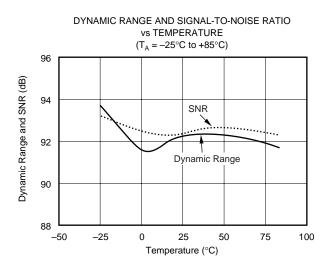

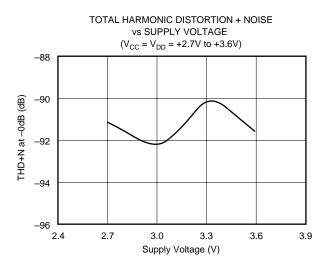

$T_{A}$  = +25°C,  $V_{CC}$  =  $V_{DD}$  = +3.3V,  $f_{S}$  = 8kHz, and  $f_{SIGNAL}$  = 1kHz, unless otherwise specified.

### DAC SECTION

#### **DAC OUTPUT SPECTRA**

### **DAC SECTION**

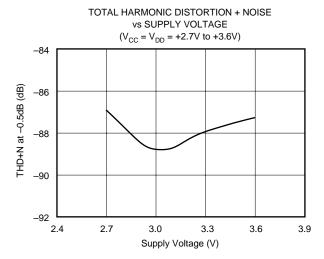

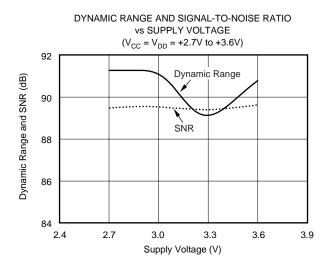

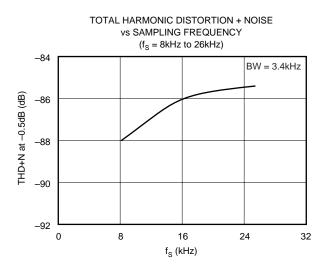

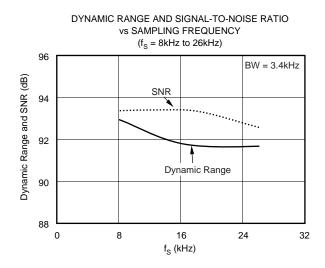

### DAC CHARACTERISTICS vs TEMPERATURE, SUPPLY, AND SAMPLING FREQUENCY

### **TYPICAL PERFORMANCE CURVES**

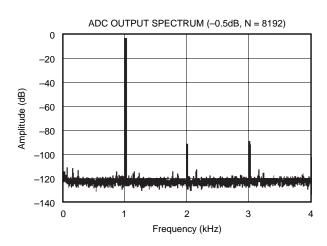

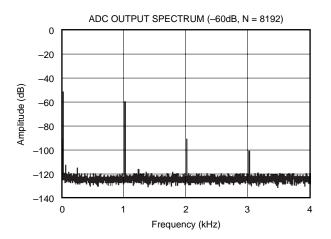

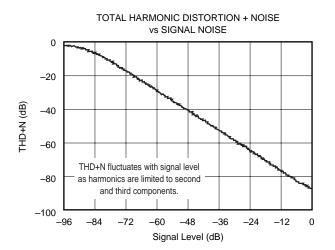

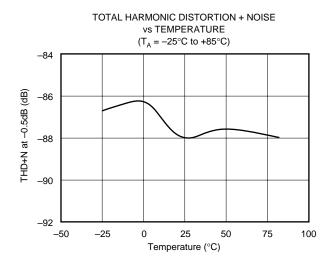

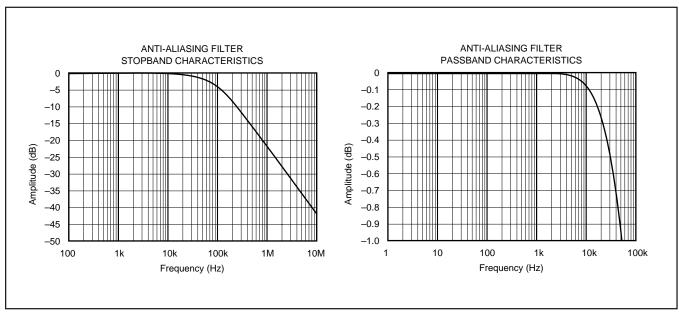

### **ADC SECTION**

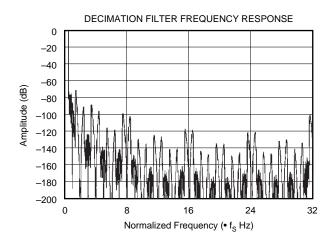

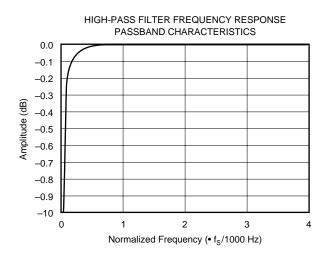

**DIGITAL FILTER**

$T_A$  = +25°C,  $V_{CC}$  =  $V_{DD}$  = +3.3V,  $f_S$  = 8kHz, and  $f_{SIGNAL}$  = 1kHz, unless otherwise specified.

### **ADC SECTION**

#### **ANALOG FILTER**

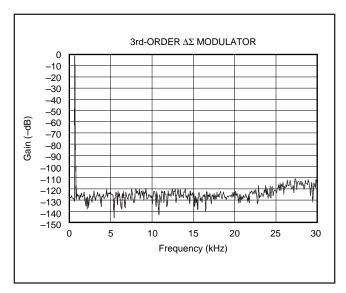

#### **ADC OUTPUT SPECTRA**

$T_A$  = +25°C,  $V_{CC}$  =  $V_{DD}$  = +3.3V,  $f_S$  = 8kHz, and  $f_{SIGNAL}$  = 1kHz, unless otherwise specified.

### **ADC SECTION**

#### ADC CHARACTERISTICS vs TEMPERATURE, SUPPLY AND SAMPLING FREQUENCY

$T_A$  = +25°C,  $V_{CC}$  =  $V_{DD}$  = +3.3V,  $f_S$  = 8kHz, and  $f_{SIGNAL}$  = 1kHz, unless otherwise specified.

#### SUPPLY CURRENT vs SUPPLY VOLTAGE AND SAMPLING FREQUENCY

### SYSTEM CLOCK AND RESET/ POWER DOWN

#### SYSTEM CLOCK INPUT AND OUTPUT

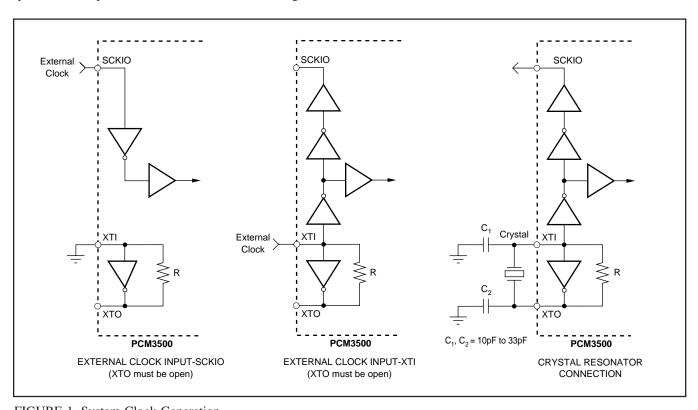

The PCM3500 requires a system clock for operating the digital filters and delta-sigma data converters.

The system clock may be supplied from an external master clock or generated using the on-chip crystal oscillator circuit. Figure 1 shows the required connections for external and crystal clock operation. The system clock must operate at 512 times the sampling frequency,  $f_S$ , with sampling frequencies from 7.2kHz to 26kHz. This gives an effective system clock frequency range of 3.6864MHz to 13.312MHz.

Table I shows system clock frequencies for common sampling frequencies.

For external clock operation, XTI (pin 17) or SCKIO (pin 15) is driven by a master clock source. If SCKIO is used as the system clock input, then XTI must be connected to ground.

| SAMPLING FREQUENCY (kHz) | SYSTEM CLOCK FREQUENCY (MHz) |

|--------------------------|------------------------------|

| 8                        | 4.096                        |

| 11.025                   | 5.6448                       |

| 16                       | 8.192                        |

| 22.05                    | 11.2896                      |

| 24                       | 12.288                       |

TABLE I. System Clock Frequencies for Common Sampling Frequencies.

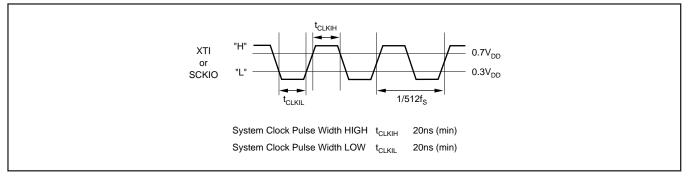

For either case, XTO (pin 16) should be left open. The system clock source should be free of noise and exhibit low phase jitter in order to obtain optimal dynamic performance from the PCM3500. Figure 2 shows the system clock timing requirements associated with an external master clock.

For crystal oscillator operation, a crystal is connected between XTI (pin 17) and XTO (pin 16), along with the necessary load capacitors (10pF to 33pF per pin, as shown in Figure 1). A fundamental-mode, parallel resonant crystal is required.

FIGURE 1. System Clock Generation.

FIGURE 2. External System Clock Timing Requirements.

#### Reset and Power Down

The PCM3500 supports power-on reset, external reset, and power-down operations. Power-on reset is performed by internal circuitry automatically at power up, while the external reset is initiated using the PDWN input (pin 20).

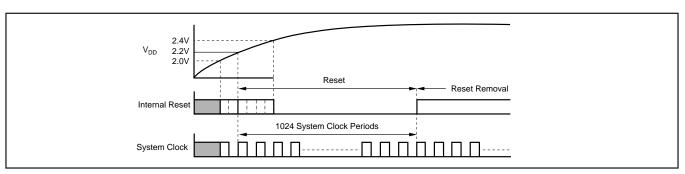

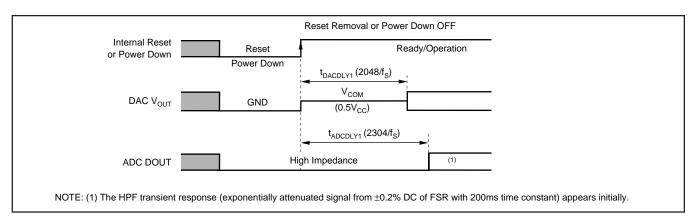

Power-on reset occurs when power and system clock are initially applied to the PCM3500. The internal reset circuitry requires that the system clock be active at power up, with at least three system clock cycles occurring prior to  $V_{\rm DD} = 2.2 \, \rm V$ . When  $V_{\rm DD}$  exceeds 2.2V, the power-on reset comparator enables the initialization sequence, which requires 1024 system clock periods for completion. During the initialization sequence, the DAC output is forced to AGND, and the ADC output is forced to a high impedance state. After the initialization sequence has completed, the DAC and ADC outputs experience a delay before they output a valid signal or data. Refer to Figures 3 and 5 for power-on reset and post-reset delay timing.

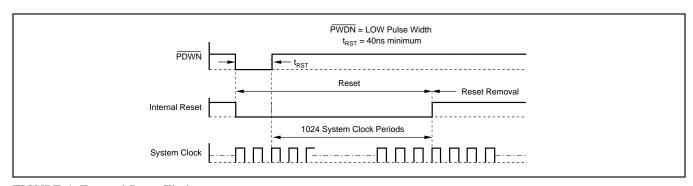

External reset is performed by first setting  $\overline{PDWN}$  = '0' and then setting  $\overline{PDWN}$  = '1'. The LOW to HIGH transition on

PDWN causes the reset initialization sequence to start. During the initialization sequence, the DAC output is forced to AGND, and the ADC output is forced to a high impedance state. After the initialization sequence has completed, the DAC and ADC outputs experience a delay before they output a valid signal or data. Refer to Figures 4 and 5 for external reset and post-reset delay timing.

Power-down mode is enabled by setting  $\overline{PDWN}$  = '0'. During power-down mode, minimum current is drawn when the system clock is removed, resulting in  $60\mu A$  (typical) power supply current. The  $\overline{PDWN}$  input includes an internal pull-down resistor, which places the PCM3500 in power-down mode at power-up if the  $\overline{PDWN}$  pin is left unconnected. Ideally, the  $\overline{PDWN}$  input should be driven by active logic in order to control reset and power-down operation. If the  $\overline{PDWN}$  pin is to be unused in the system application, it should be connected to  $V_{DD}$  to enable normal operation. By setting  $\overline{PDWN}$  = '1' when exiting power-down mode, the PCM3500 will initiate an external reset as described earlier in this section.

FIGURE 3. Power-On Reset Timing

FIGURE 4. External Reset Timing.

FIGURE 5. DAC and ADC Output for Reset and Power Down.

#### SERIAL INTERFACE

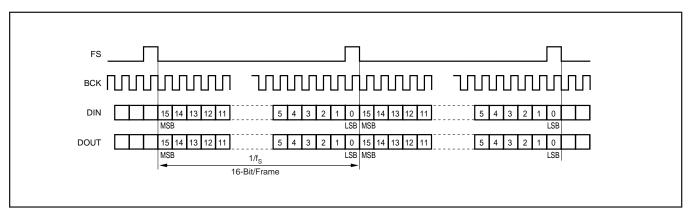

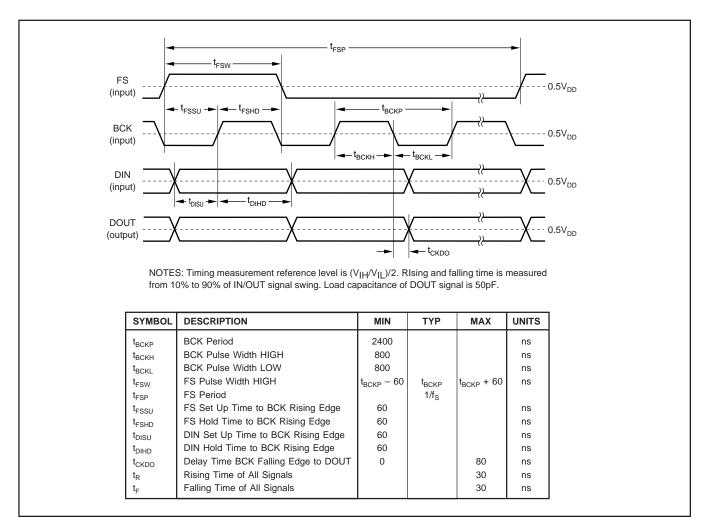

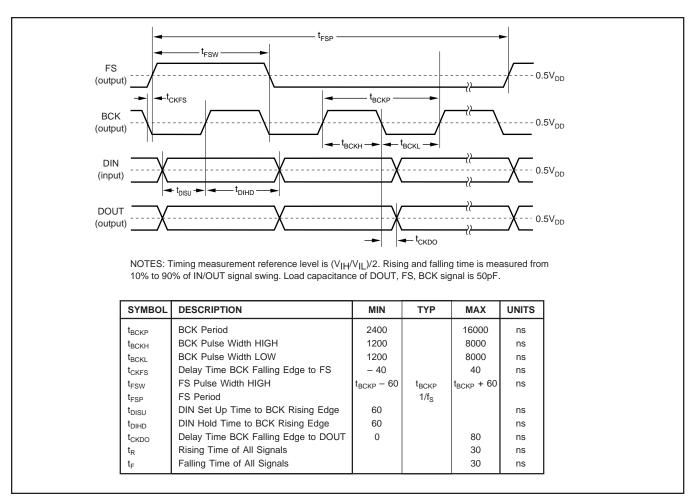

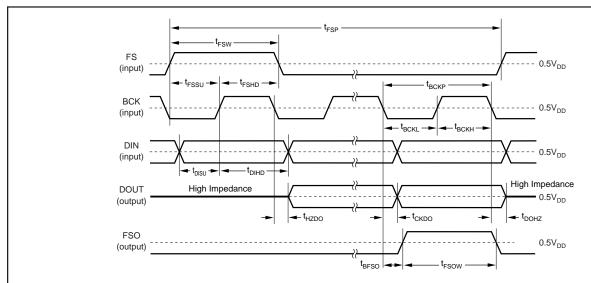

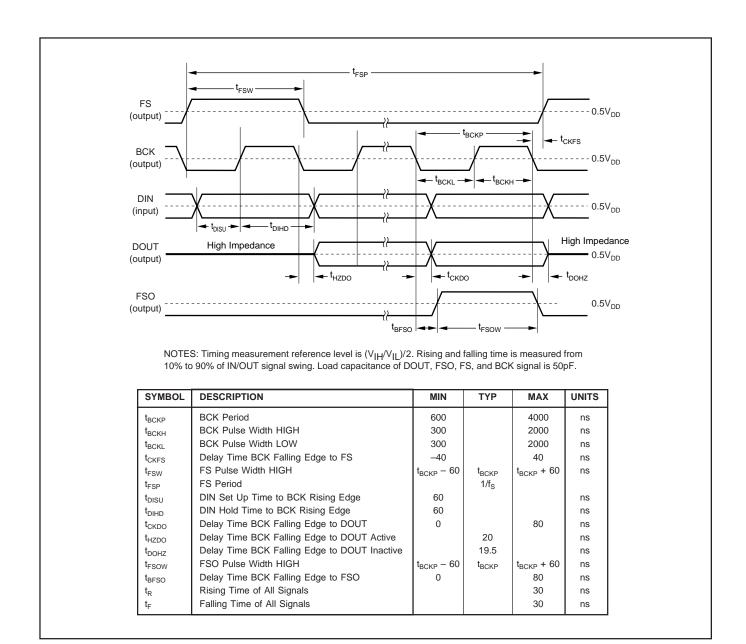

The serial interface of the PCM3500 is a 4-wire synchronous serial port. It includes FS (pin 9), BCK (pin 8), DIN (pin 10) and DOUT (pin 11). FS is the frame synchronization clock, BCK is the serial bit or shift clock, DIN is the serial data input for the DAC, and DOUT is the serial data output for the ADC.

The frame sync, FS, operates at the sampling frequency ( $f_S$ ). The bit clock, BCK, operates at  $16f_S$  for normal operation. DIN and DOUT also operate at the bit clock rate. Both FS and BCK must be synchronous with the system clock (guar-

anteed in Master Mode). Data for DIN is clocked into the serial interface on the rising edge of BCK, while data for DOUT is clocked out of the serial interface on the falling edge of BCK.

Figure 6 shows the serial interface format for the PCM3500. The serial data for DIN and DOUT must be in Binary Two's Complement, MSB-first format. Figures 7 and 8 show the timing specifications for the serial interface when used in Slave and Master Modes.

FIGURE 6. Serial Interface Format.

FIGURE 7. Serial Interface Timing for Slave Mode.

FIGURE 8. Serial Interface Timing for Master Mode.

15

FIGURE 9. Slave and Master Mode Connections.

#### **MASTER/SLAVE OPERATION**

The serial interface supports both Slave and Master Mode operation. The mode is selected by the M/S input (pin 6). Table II shows mode and pin settings corresponding to the M/S input selection. Figure 9 shows connections for Slave and Master mode operation.

| M/S (PIN 6) | SERIAL<br>INTERFACE<br>MODE | FS (PIN) | BCK (PIN 8) |  |  |

|-------------|-----------------------------|----------|-------------|--|--|

| 0           | Slave                       | Input    | Input       |  |  |

| 1           | Master                      | Output   | Output      |  |  |

TABLE II. Master/Slave Mode Selection.

#### Slave Mode Operation

In Slave Mode, the FS and BCK pins are inputs to the PCM3500. Both FS and BCK should be derived from the system clock signal (XTI or SCKIO) to ensure proper synchronization. Slave Mode is best suited for applications where the DSP or controller is capable of generating the FS, BCK, and system clocks using an on-chip serial port and/or timing generator.

#### **Master Mode Operation**

In Master Mode operation, both FS and BCK are clock outputs generated by the PCM3500 from the system clock input (XTI, SCKIO, or a crystal). In Master Mode, the timing and phase relationships between system clock, FS, and BCK are managed internally to provide optimal synchronization.

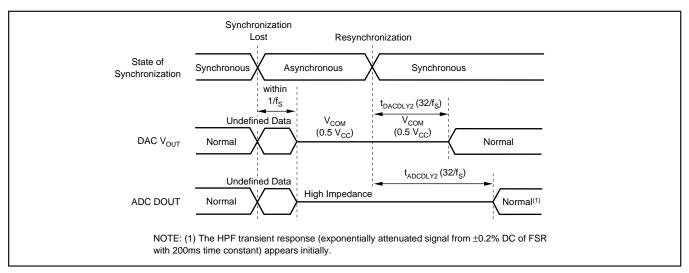

#### SYNCHRONIZATION REQUIREMENTS

The PCM3500 requires that FS and BCK be synchronous with the system clock. Internal circuitry is included to detect a loss of synchronization between FS and the system clock input. If the phase relationship between FS and the system clock varies more than  $\pm$  1.5 BCK periods, the PCM3500 will detect a loss of synchronization. Upon detection, the DAC output is forced to  $0.5 \rm V_{CC}$  and the DOUT pin is forced to a high impedance state. This occurs within one sampling clock (FS) period of initial detection. Figure 10 shows the loss of synchronization operation and the DAC and ADC output delays associated with it.

#### TIME SLOT OPERATION

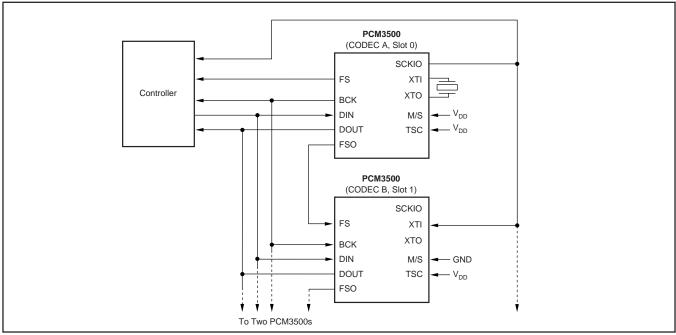

The PCM3500 serial interface supports Time Division Multiplexing (TDM) using the Time Slot Mode. Up to four PCM3500s may be connected on the same 4-wire serial

interface bus. This is useful for system applications that require multiple modem or voice channels. Figure 11 shows examples of Time Slot Mode connections.

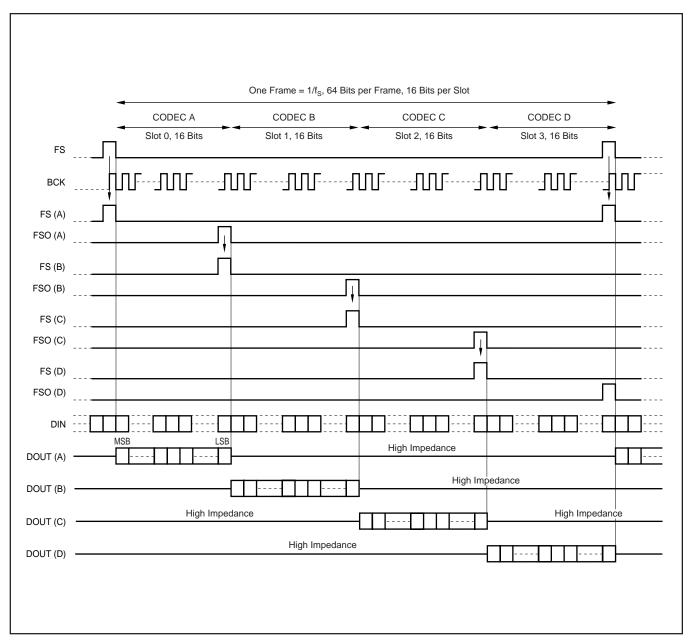

Time Slot Mode defines a 64-bit long frame, composed of four time slots. Each slot is 16 bits long and corresponds to one of four CODECs. The FS pin on the first PCM3500 (CODEC A, Slot 0) is used as the master frame sync, and operates at the sampling frequency,  $f_S$ . The bit clock, BCK, operates at  $64f_S$ . DIN and DOUT of each CODEC also operate at  $64f_S$ . Figure 12 shows the operation of the Time Slot Mode.

Time Slot operation is enabled or disabled using the TSC input (pin 7). The state of the TSC pin is updated at power-on reset, or on the rising edge of PWDN input (if using external reset or power-down mode). A forced reset is required when changing from Slave to Master Mode, or visa versa, in real time.

FIGURE 10. Loss of Synchronization Operation and Timing.

FIGURE 11. Time Slot Mode Connections.

16

FIGURE 12. Time Slot Mode Operation.

17

Table III shows the TSC pin settings and corresponding mode selections. When Time Slot Mode is enabled, FSO (pin 12) is used as a frame sync output, which is connected to the FS input of the next PCM3500 in the Time Slot sequence. Figures 13 and 14 provide detailed timing for Time Slot Mode operation.

| TSC (PIN 7) | TIME SLOT MODE                            |

|-------------|-------------------------------------------|

| 0           | Time Slot Mode Disabled, Normal Operation |

| 1           | Time Slot Operation Enable                |

TABLE III. Time Slot Mode Selection.

#### ADC-TO-DAC LOOP BACK

The PCM3500 includes a Loop-Back Mode, which directly feeds the ADC data to the DAC input. This mode is designed for diagnostic testing and system adjustment. Loop-Back Mode is enabled and disabled using the LOOP input (pin 19). Table IV shows the LOOP pin settings and corresponding mode selections. The serial interface continues to oper-

ate in Loop-Back Mode, allowing the host to read the ADC data at the DOUT pin.

| LOOP (PIN 19) | LOOP-BACK MODE                            |

|---------------|-------------------------------------------|

| 0             | Loop-Back Mode Disabled, Normal Operation |

| 1             | Loop-Back Mode Enabled                    |

TABLE IV. Loop-Back Mode Selection.

#### **HIGH-PASS FILTER**

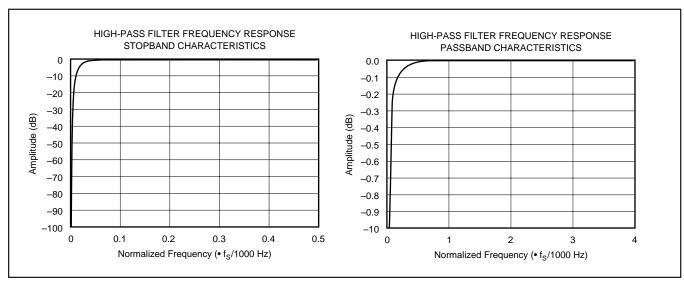

The PCM3500 includes a digital high-pass filter in the ADC which may be used to remove the DC offset created by the analog front-end (AFE) section. The high-pass filter response is shown in Figure 15. The high-pass filter may be enabled or disabled using the HPFD input (pin 18). Table V shows the HPFD pin settings and corresponding mode selections.

| HPFD (PIN 18) | HIGH-PASS FILTER MODE |

|---------------|-----------------------|

| 0             | High-Pass Filter On   |

| 1             | High-Pass Filter Off  |

TABLE V. High-Pass Filter Mode Selection.

NOTES: Timing measurement reference level is  $(V_{IH}/V_{IL})/2$ . Rising and falling time is measured from 10% to 90% of IN/OUT signal swing. Load capacitance of DOUT, and FSO signal is 50pF.

| SYMBOL            | DESCRIPTION                                  | MIN                    | TYP              | MAX                    | UNITS |

|-------------------|----------------------------------------------|------------------------|------------------|------------------------|-------|

| t <sub>BCKP</sub> | BCK Period                                   | 600                    |                  |                        | ns    |

| t <sub>BCKH</sub> | BCK Pulse Width HIGH                         | 200                    |                  |                        | ns    |

| t <sub>BCKL</sub> | BCK Pulse Width LOW                          | 200                    |                  |                        | ns    |

| t <sub>FSW</sub>  | FS Pulse Width HIGH                          | t <sub>BCKP</sub> - 60 | $t_{BCKP}$       | t <sub>BCKP</sub> + 60 | ns    |

| t <sub>FSP</sub>  | FS Period                                    |                        | 1/f <sub>S</sub> |                        |       |

| t <sub>FSSU</sub> | FS Set Up TIme to BCK Rising Edge            | 60                     |                  |                        | ns    |

| t <sub>FSHD</sub> | FS Hold Time to BCK Rising Edge              | 60                     |                  |                        | ns    |

| t <sub>DISU</sub> | DIN Set Up Time to BCK Rising Edge           | 60                     |                  |                        | ns    |

| t <sub>DIHD</sub> | DIN Hold Time to BCK Rising Edge             | 60                     |                  |                        | ns    |

| t <sub>CKDO</sub> | Delay Time BCK Falling Edge to DOUT          | 0                      |                  | 80                     | ns    |

| t <sub>HZDO</sub> | Delay Time BCK Falling Edge to DOUT Active   |                        | 20               |                        | ns    |

| t <sub>DOHZ</sub> | Delay Time BCK Falling Edge to DOUT Inactive |                        | 19.5             |                        | ns    |

| t <sub>FSOW</sub> | FSO Pulse Width HIGH                         | t <sub>BCKP</sub> - 60 | $t_{BCKP}$       | t <sub>BCKP</sub> + 60 | ns    |

| t <sub>BFSO</sub> | Delay Time BCK Falling Edge to FSO           | 0                      |                  | 80                     | ns    |

| t <sub>R</sub>    | Rising Time of All Signals                   |                        |                  | 30                     | ns    |

| t <sub>F</sub>    | Falling Time of All Signals                  |                        |                  | 30                     | ns    |

FIGURE 13. Serial Interface Timing for Time Slot Mode Operation (Slave Mode).

FIGURE 14. Serial Interface Timing for Time Slot Mode Operation (Master Mode).

19

FIGURE 15. High-Pass Filter Response.

#### APPLICATIONS INFORMATION

#### **BASIC CIRCUIT CONNECTIONS**

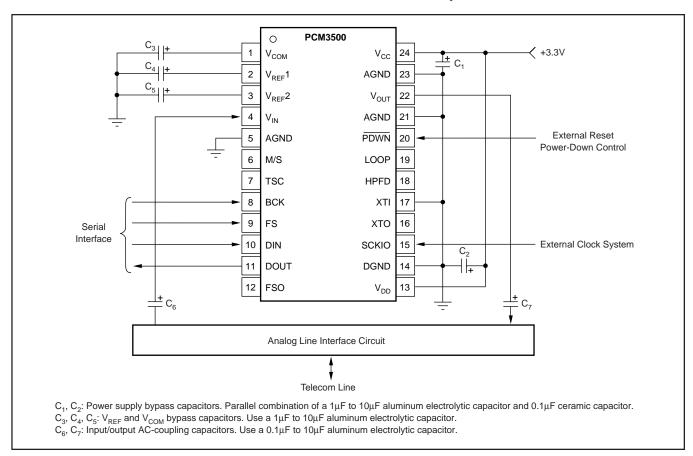

The basic connection diagram for the PCM3500 is shown in Figure 16. Included are the required power supply bypass and reference decoupling capacitors. The DAC output,  $V_{OUT}$ , and the ADC input,  $V_{IN}$ , should be AC-coupled to external circuitry.

#### **Reference Pin Connections**

The  $V_{COM}$  voltage is used internally to bias the input and output amplifier stages of the PCM3500. It is brought out

unbuffered on pin 1 for decoupling. A  $1\mu F$  to  $10\mu F$  aluminum electrolytic or tantalum capacitor is recommended for decoupling purposes. This capacitor should be located as close as possible to pin 1.

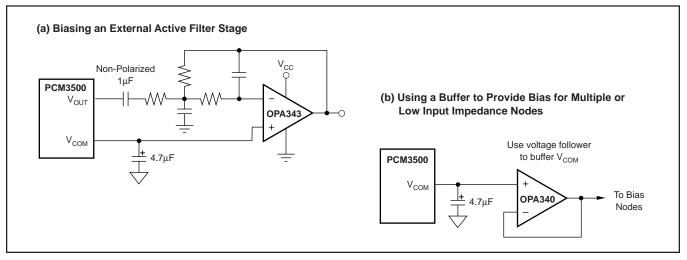

The  $V_{COM}$  voltage is typically equal to  $V_{CC}/2$ , and may be used to bias external input and output circuitry. However, since the  $V_{COM}$  pin is not a buffered output, it must drive a high impedance load to avoid excessive loading. Buffering the  $V_{COM}$  pin with an external op amp configured as a voltage follower is recommended when driving multiple bias nodes. Figure 17 shows examples of using  $V_{COM}$  with external circuitry.

FIGURE 16. Basic Connection Diagram.

FIGURE 17. Using V<sub>COM</sub> to Bias External Circuitry.

$V_{REF}1$  (pin 2) and  $V_{REF}2$  (pin 3) are reference voltages used by the delta-sigma modulators. They are brought out strictly for decoupling purposes.  $V_{REF}1$  and  $V_{REF}2$  are not to be used to bias external circuits. A  $1\mu F$  to  $10\mu F$  aluminum electrolytic or tantalum capacitor is recommended for decoupling on each pin. These capacitors should be located as close as possible to pins 2 and 3.

#### **Power Supplies and Grounding**

$V_{CC}$  (pin 24) and  $V_{DD}$  (pin 13) should be connected directly to the +2.7V to +3.6V analog power supply, as shown in Figure 16. The AGNDs (pins 5, 21, and 23) and DGND (pin 14) should be connected directly to the analog ground. Power supply bypass capacitors should be located as close to the power supply pins as possible in order to ensure a low impedance connection. A combination of a  $10\mu F$  aluminum electrolytic or tantalum capacitor in parallel with a  $0.1\mu F$  ceramic capacitor is recommended for both  $V_{CC}$  and  $V_{DD}$ .

$V_{\rm DD}$  and  $V_{\rm CC}$  should not be connected to separate digital and analog power supplies. This can lead to an SCR latch-up condition, which can cause either degraded device performance or catastrophic failures.

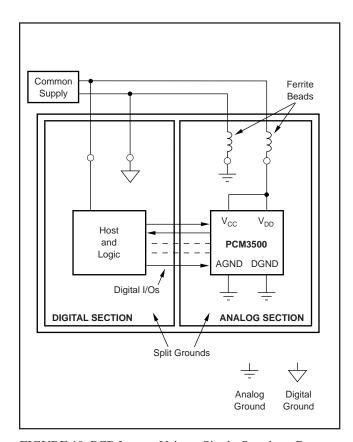

#### **PCB LAYOUT GUIDELINES**

The recommended PCB layout technique is shown in Figure 18. The analog and digital section of the board are separated

Digital Power Analog Power Supply Supply Common +3 3V +3.3V Connection  $V_{DD}$  $V_{CC}$ Host and PCM3500 Logic AGND DGND Digital I/Os **DIGITAL SECTION** ANALOG SECTION Split Grounds Analog Digital Ground Ground

FIGURE 18. Recommended PCB Layout Technique.

by a split ground plane, with the PCM3500 positioned entirely over the analog section of the board. The AGNDs (pins 5, 20, and 23) and DGND (pin 14) are connected directly to the analog ground plane. The power supply pins,  $V_{\rm CC}$  (pin 13) and  $V_{\rm DD}$  (pin 24), are routed directly to the +2.7V to +3.6V analog power supply using wide copper traces (100 mils or wider recommended) or a power plane. Power supply bypass and reference decoupling capacitors are shown located as close as possible to the PCM3500.

The PCM3500 is oriented so that the digital pins are facing the ground plane split. Digital connections should be made as short and direct as possible to limit high frequency radiation and coupling. Series resistors (from  $20\Omega$  to  $100\Omega$ ) may be put in series with the system clock, FS, BCK, and FSO lines to reduce or eliminate overshoot on clock edges, further reducing radiated emissions. The split ground plane should be connected at one point by a trace, wire, or ferrite bead. Often the board will be designed to have several jumper points for the common ground connection, so that the best performance can be derived through experimentation.

An alternative technique, using a single power supply or battery, is shown in Figure 19. This technique is more suitable for portable applications.

FIGURE 19. PCB Layout Using a Single-Supply or Battery.

#### **OUTPUT FILTER CIRCUITS FOR THE DAC**

The PCM3500's DAC uses delta-sigma conversion techniques. It uses oversampling and noise shaping to improve in-band ( $f = f_S/2$ ) signal-to-noise performance at the expense of increased out-of-band noise. The DAC output must be low-pass filtered to attenuate the out-of-band noise to a reasonable level.

The PCM3500 includes a low-pass filter in the on-chip output amplifier circuit. The frequency response for this filter is shown in Figure 20. Although this filter helps to lower the out-of-band noise, it is not adequate for many applications. This is especially true for applications where the sampling frequency is below 16kHz, since the out-of-band noise above  $f_{\rm S}/2$  is in the audio spectrum. An external filter circuit, either passive or active, is required to provide additional attenuation of the out-of-band noise. The low-pass filter order will be dependent upon the out-of-band

noise requirements for a particular system. Generally, a 2nd-order or better low-pass circuit will be required, with the cut-off frequency set to  $f_8/2$  or less.

Burr-Brown Application Bulletin AB-034 provides information for designing both Multiple Feedback and Sallen-Key active filter circuits using software available from Burr-Brown's web site. Another excellent reference for both passive and active filter design is the "Electronic Filter Design Handbook, Third Edition" by Williams and Taylor, published by McGraw-Hill.

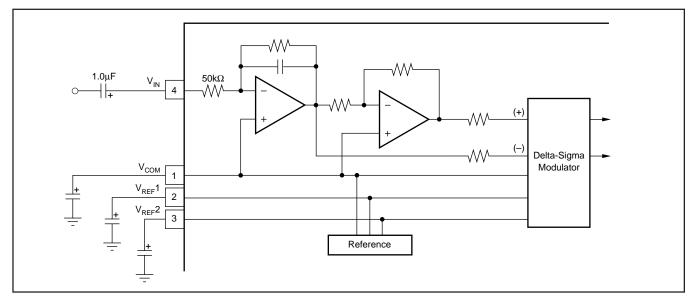

#### ON-CHIP ANALOG FRONT END FOR THE ADC

The PCM3500 A/D converter includes a fully differential input delta-sigma modulator. In order to simplify connection for single-ended applications, an analog front end (AFE) circuit has been included on the PCM3500 just prior to the modulator. The AFE circuit is shown in Figure 21.

FIGURE 20. DAC Output Amplifier Filter Response.

FIGURE 21. On-Chip AFE Circuit for the ADC.

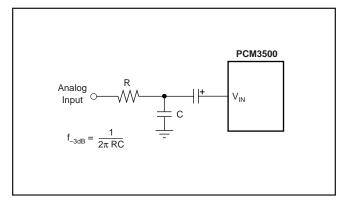

The AFE circuit consists of a single-ended-to-differential converter, with the first stage of the circuit doubling as a low-pass, anti-alias filter. The frequency response for the filter is shown in Figure 22. Since the delta-sigma modulator oversamples the input at  $64f_S$ , the anti-alias filter requirements are relaxed, with only a single-pole filter being required. If an application requires further band limiting of the input signal, a simple RC filter at the  $V_{\rm IN}$  input (pin 4) can be used, as shown in Figure 23.

## SOFTWARE MODEM APPLICATIONS

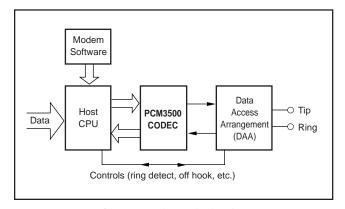

The PCM3500 was designed to meet the requirements for software-based analog modems, supporting up to 56kbps<sup>(1)</sup>. In a software modem application, the PCM3500 is paired with a Data Access Arrangement (DAA) and a host CPU to

provide the complete modem function. Figure 24 shows a simplified block diagram of a software modem using the PCM3500.

The DAA provides the interface between the CODEC and two-wire telephone line. The DAA provides numerous functions, including two-to-four wire conversion, modem-side to line-side isolation, ring detection, hook switch control, line current compensation, and overvoltage protection.

The host CPU provides the data pump and supervisory functions for the software modem application. The host executes modem software code, which includes the necessary routines for transmit and receive functions, error detection and correction, echo cancellation, and CODEC/DAA control and supervision.

NOTE: (1) Data transmission is limited to 53kbps over standard telephone lines. Actual transmission rates vary depending upon the quality of the lines and switching equipment for a given connection.

FIGURE 22. Anti-Alias Filter Frequency Response.

FIGURE 23. Optional External Low-Pass Filter for the ADC.

FIGURE 24. Software Modem Block Diagram.

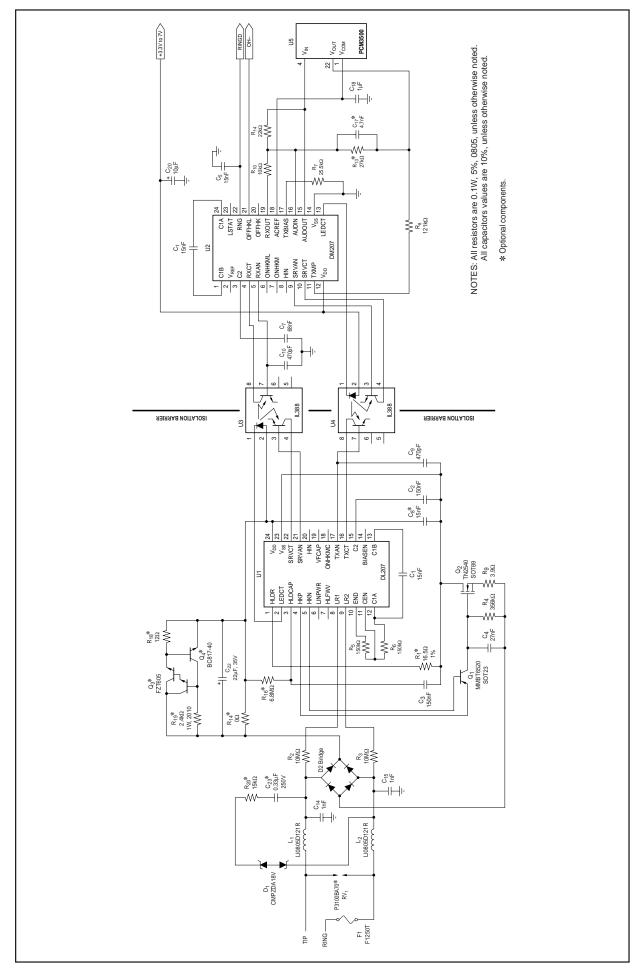

FIGURE 25. Modem AFE Application Circuit.

#### Software Modem AFE Application Circuit

Figure 25 shows an applications circuit which utilizes the PCM3500 and the DAA2000 from Infineon Technologies (Siemens) to implement a complete modem AFE. The DAA2000 provides modem-side (DM207) and line-side (DL207) interfaces, with optical isolation separating the functions. The PCM3500 is connected to the modem-side of the DAA2000. The PCM3500's serial interface and hardware mode controls are connected to the host CPU.

#### THEORY OF OPERATION

#### **ADC SECTION**

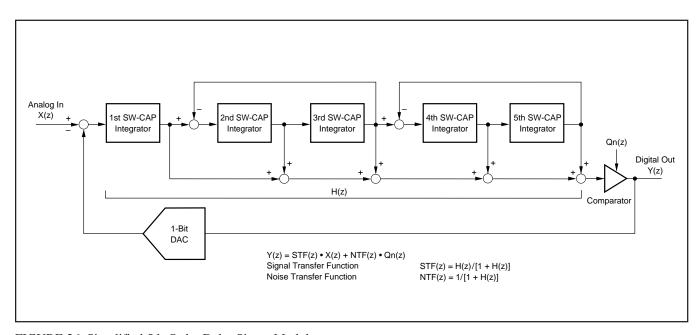

The PCM3500 A/D converter consists of two reference circuits, a mono single-to-differential converter, a fully differential 5th-order delta-sigma modulator, a decimation filter (including digital high pass), and a serial interface circuit. The block diagram on the front page of this data sheet illustrates the architecture of the ADC section, Figure 21 shows the single-to-differential converter, and Figure 26 illustrates the architecture of the 5th-order delta-sigma modulator and transfer functions.

An internal reference circuit with three external capacitors provides all reference voltages which are required by the ADC, which defines the full-scale range for the converter. The internal single-to-differential voltage converter saves the design, space and extra parts needed for external circuitry required by many delta-sigma converters. The internal full-differential signal processing architecture provides a

wide dynamic range and excellent power supply rejection performance. The input signal is sampled at a 64x oversampling rate, eliminating the need for a sample-and-hold circuit, and simplifying anti-alias filtering requirements. The 5th-order delta-sigma noise shaper consists of five integrators which use a switched-capacitor topology, a comparator, and a feedback loop consisting of a one-bit DAC. The delta-sigma modulator shapes the quantization noise, shifting it out of the audio band in the frequency domain. The high order of the modulator enables it to randomize the modulator outputs, reducing idle tone levels.

The  $64f_S$  one-bit data stream from the modulator is converted to  $1f_S$ , 16-bit data words by the decimation filter, which also acts as a low-pass filter to remove the shaped quantization noise. The DC components can be removed by a high-pass filter function contained within the decimation filter.

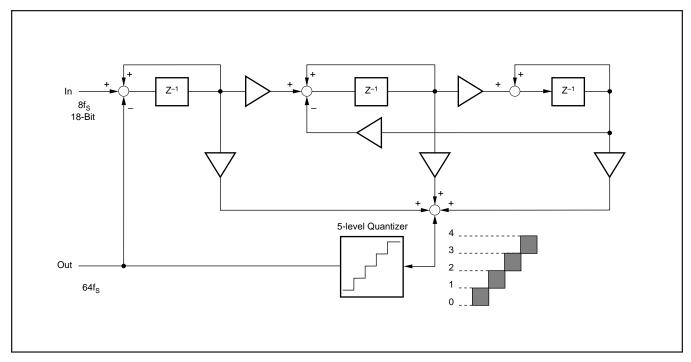

#### DAC SECTION

The delta-sigma DAC section of PCM3500 is based on a 5-level amplitude quantizer and a 3rd-order noise shaper. This section converts the oversampled input data to 5-level delta-sigma format. A block diagram of the 5-level delta-sigma modulator is shown in Figure 27. This 5-level delta-sigma modulator has the advantage of stability and clock jitter sensitivity over the typical one-bit (2 level) delta-sigma modulator. The combined oversampling rate of the delta-sigma modulator and the internal 8x interpolation filter is  $64f_{\rm S}$  for a  $512f_{\rm S}$  system clock. The theoretical quantization noise performance of the 5-level delta-sigma modulator is shown in Figure 28.

FIGURE 26. Simplified 5th-Order Delta-Sigma Modulator.

FIGURE 27. 5-Level Delta-Sigma Modulator Block Digram.

FIGURE 28. Quantization Noise Spectrum.

www.ti.com 17-Sep-2022

#### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------------|---------|

|                  |            |              |                    |      |                |              | (6)                           |                    |              |                      |         |

| PCM3500E         | ACTIVE     | SSOP         | DB                 | 24   | 58             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -25 to 85    | PCM3500E             | Samples |

| PCM3500E/2K      | ACTIVE     | SSOP         | DB                 | 24   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -25 to 85    | PCM3500E             | Samples |

| PCM3500EG4       | ACTIVE     | SSOP         | DB                 | 24   | 58             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -25 to 85    | PCM3500E             | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

### **PACKAGE OPTION ADDENDUM**

www.ti.com 17-Sep-2022

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

### **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Jan-2022

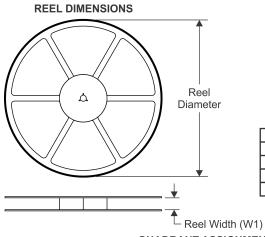

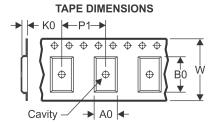

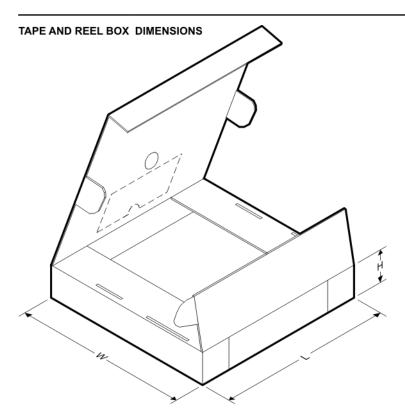

#### TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

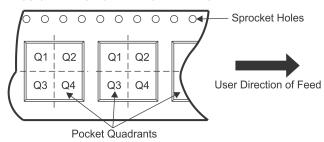

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| PCM3500E/2K | SSOP            | DB                 | 24 | 2000 | 330.0                    | 17.4                     | 8.5        | 8.6        | 2.4        | 12.0       | 16.0      | Q1               |

www.ti.com 5-Jan-2022

#### \*All dimensions are nominal

|   | Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---|-------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| I | PCM3500E/2K | SSOP         | DB              | 24   | 2000 | 336.6       | 336.6      | 28.6        |  |

### PACKAGE MATERIALS INFORMATION

www.ti.com 5-Jan-2022

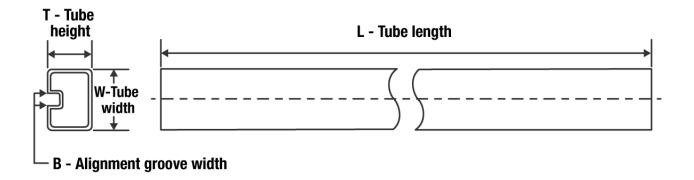

#### **TUBE**

#### \*All dimensions are nominal

| Device     | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| PCM3500E   | DB           | SSOP         | 24   | 58  | 500    | 10.6   | 500    | 9.6    |

| PCM3500EG4 | DB           | SSOP         | 24   | 58  | 500    | 10.6   | 500    | 9.6    |

#### **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated