# TLV320ADCx140 Sampling Rates and Programmable Processing Blocks Supported

Diljith Thodi

#### **ABSTRACT**

This document describes the available processing blocks in the decimation filter chain of the TLV320ADCx140 family of devices. It also explains which configurations of the processing blocks are supported as a function of the sample rate and number of channels.

|                  | Contents                                                                   |   |

|------------------|----------------------------------------------------------------------------|---|

| 1<br>2<br>3<br>4 | Introduction                                                               | 5 |

|                  | List of Figures                                                            |   |

| 1                | TLV320ADCx140 Channel Signal Chain Processing Flow Chart                   | 2 |

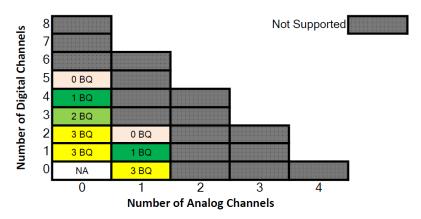

| 2                | Supported Channel Combinations for 8 kHz to 48 kHz Sample Rates            | 5 |

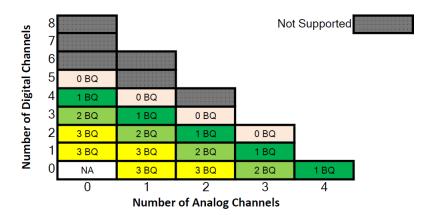

| 3                | Channel Combinations for 96 kHz with DRE/AGC Enabled                       | 6 |

| 4                | Channel Combinations for 96 kHz with DRE/AGC Disabled                      | 6 |

| 5                | Channel Combinations for 192 kHz Linear Phase Filter with AGC/DRE Enabled  | 7 |

| 6                | Channel Combinations for 192 kHz Linear Phase Filter with AGC/DRE Disabled | 7 |

|                  | List of Tables                                                             |   |

| 1                | Decimation Filter Mode Selection for the Record Channel                    | 2 |

| 2                | Maximum Channel Count for Decimation Filters                               | 3 |

| 3                | AGC Selection Register Field Description                                   | 3 |

| 4                | Number of Analog Channels Supported with AGC/DRE Enabled                   | 3 |

| 5                | Channel Summing Mode and Digital Mixer Programmable Settings               | 2 |

| 6                | Bi-quad Configuration Settings                                             | 2 |

| 7                | Processing Block Assignments Across Input Channels                         | Ę |

#### 1 Introduction

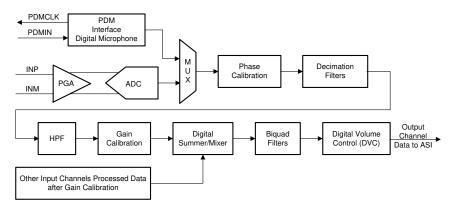

The TLV320ADCx140 is a family of quad-channel, audio analog-to-digital converters that includes a highly flexible signal chain with programmable digital processing blocks, making it suitable for a wide variety of applications. The data sheet provides the overview for all of the device features. Figure 1 shows the signal processing chain. The device can support four analog microphone channels, 8 digital PDM microphone channels, or a combination of analog and digital microphones channels. The decimation filters, digital summer and mixer block, and bi-quad filters shown in Figure 1 are highly configurable, so it can suit different application scenarios. In addition, the device also supports an Automatic Gain Controller (AGC) block and Dynamic Range Enhancer (DRE) block on the analog microphone channels. These digital features all share the same fixed processing resources. Therefore, the number of channels enabled, the nature of each channel (analog or digital), and the sample-rate determine the configuration possibilities for the processing blocks and filters.

Figure 1. TLV320ADCx140 Channel Signal Chain Processing Flow Chart

The TLV320ADCx140 device family supports two sets of sample rates. One set of sample rates cover the nine submultiples and multiples of 48 kHz, from 8 kHz to 768 kHz. The other set of sample rates cover the sample rates from 7.35 kHz to 705.6 kHz, which are submultiples and multiples of 44.1 kHz. This application note only refers to the set of 48 kHz sample rates, but they are applicable to the corresponding sample rate from the set of 44.1 kHz sample rates. For example, features supported for the 8 kHz sample rate are also supported for 7.35 kHz.

The next section reviews the processing blocks, configuration options and input channels they are supported on, and the supported sample rates. The subsequent section reviews the channel combinations that are supported for different sample rates, and the processing blocks that are supported for the given channel combination.

# 2 Processing Blocks of TLV320ADCx140

The following sections describe the device configurations required to use:

- Decimation filters

- AGC or DRE

- Programmable biquads

- Summers

- Digital mixers

### 2.1 Decimation Filter Response

The decimation filter processes the oversampled data from either the multi-bit delta-sigma modulator of the analog channels or the oversampled PDM stream from the digital microphones, and generates the output PCM samples at the FSYNC rate. The decimation filter option is selected by configuring the DECI\_FILT, P0\_R107\_D[5:4] register bits. Table 1 shows the configuration register setting for the decimation filter mode selection for the record channel. It can be set to linear phase, low latency, or ultra-low latency.

Table 1. Decimation Filter Mode Selection for the Record Channel

| P0_R107_D[5:4] : DECI_FILT[1:0] | DECIMATION FILTER MODE SELECTION                          |

|---------------------------------|-----------------------------------------------------------|

| 00 (default)                    | Linear phase decimation filters                           |

| 01                              | Low-latency approximately linear phase decimation filters |

| 10                              | Ultra-low latency decimation filters                      |

| 11                              | Reserved                                                  |

2

NA

### 2.1.1 Supported Sample Rates

The response of the default decimation filter is linear phase. It is supported for all sample rates from 8 kHz to 768 kHz. The low latency and ultra-low latency responses are supported for a subset of the sample rates as shown in Table 2. Unsupported filters are marked as 'NA'. For supported filters, Table 2 lists the maximum channel count. Note that to support the channel count shown in Table 2, certain processing blocks may have to be disabled, as shown in Section 3.

**SAMPLE RATE (kHz) LINEAR PHASE LOW LATENCY ULTRA-LOW LATENCY** 8 8 8 NA 16 8 8 8 24 8 8 32 8 8 8 48 8 8 8 96 4 4 4 192 4 3 3

NA

NA

2

1

**Table 2. Maximum Channel Count for Decimation Filters**

### 2.2 AGC or DRE

384

768

Analog channels include two additional processing blocks:

- Automatic Gain Control (AGC) is an algorithm that dynamically controls the gain of the ADC channel to maintain a nominally constant output level. AGC is available on all TLV320ADCx140 device variants.

- Dynamic Range Enhancer (DRE) is an algorithm that dynamically adjusts the PGA gain of the ADC channel to enhances the dynamic range. DRE is available on the TLV320ADC5140 and TLV320AD6140 devices.

Only one of these blocks can be enabled at a time. These blocks are enabled by setting the AGC\_SEL bit in DSP\_CFG1 (P0\_R106\_D[3]) to 1. Table 3 shows the AGC\_SEL definition.

Table 3. AGC Selection Register Field Description

| P0_R106_D[3] : AGC_SEL[1:0] | AGC or DRE SELECTION                                                       |

|-----------------------------|----------------------------------------------------------------------------|

| 0 (default)                 | AGC is not selected (DRE is selected for TLV320ADC5140 and TLV320ADC6140). |

| 1                           | AGC is selected (DRE is not selected).                                     |

### 2.2.1 Supported Sample Rates

AGC or DRE is supported from 16 kHz to 192 kHz sample rates. AGC or DRE is not supported for 8 kHz, 384 kHz, and 768 kHz sample rates. Do not change the value of the DRE\_AGC\_SEL bit for unsupported sample rates.

#### 2.2.2 Channel Assignment

AGC or DRE is only available for analog channels. Analog channels are assigned to input channels 1 to 4. Table 4 shows the maximum number of analog channels supported by the device when AGC or DRE is enabled.

Table 4. Number of Analog Channels Supported with AGC/DRE Enabled

| SAMPLE RATE (kHz) | NUMBER OF CHANNELS SUPPORTED WITH AGC/DRE ENABLED |  |  |  |  |

|-------------------|---------------------------------------------------|--|--|--|--|

| 16                | 4                                                 |  |  |  |  |

| 24                | 4                                                 |  |  |  |  |

| 32                | 4                                                 |  |  |  |  |

Table 4. Number of Analog Channels Supported with AGC/DRE Enabled (continued)

| SAMPLE RATE (kHz) | NUMBER OF CHANNELS SUPPORTED WITH AGC/DRE ENABLED |

|-------------------|---------------------------------------------------|

| 48                | 4                                                 |

| 96                | 2                                                 |

| 192               | 1                                                 |

### 2.3 Channel Summer, Digital Mixer, and Bi-quads

The device supports one four-channel mixer, two channel-summation modes, and up to three bi-quads per channel. These features are supported for all sample rates from 8 kHz to 192 kHz. See Table 5 for configuration details of the summer and mixer modes. The programmable mixer feature is available only if CH\_SUM[2:0] is set to 2'b00. The mixer function is only supported for input channel 1 to channel 4.

The number of bi-quad filters per channel can be set using the P0\_R108:BQ\_CFG bits, as shown in Table 6. For additional information on bi-quad filter configuration, refer to the *TLV320ADCx140* Programmable Bi-quad Filter Configuration and Applications Application Report.

Table 5. Channel Summing Mode and Digital Mixer Programmable Settings

| P0_R107_D[3:2] : CH_SUM[1:0] | CHANNEL SUMMING MODE FOR INPUT CHANNELS                                                        |  |  |  |  |

|------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|

| 00 (Default)                 | Channel summing mode is disabled (Digital Mixer is enabled).                                   |  |  |  |  |

|                              | Output channel 1 = (input channel 1 + input channel 2) / 2                                     |  |  |  |  |

| 01                           | Output channel 2 = (input channel 1 + input channel 2) / 2                                     |  |  |  |  |

| 01                           | Output channel 3 = (input channel 3 + input channel 4) / 2                                     |  |  |  |  |

|                              | Output channel 4 = (input channel 3 + input channel 4) / 2                                     |  |  |  |  |

|                              | Output channel 1 = (input channel 1 + input channel 2 + input channel 3 + input channel 4) / 4 |  |  |  |  |

| 10                           | Output channel 2 = (input channel 1 + input channel 2 + input channel 3 + input channel 4) / 4 |  |  |  |  |

| 10                           | Output channel 3 = (input channel 1 + input channel 2 + input channel 3 + input channel 4) / 4 |  |  |  |  |

|                              | Output channel 4 = (input channel 1 + input channel 2 + input channel 3 + input channel 4) / 4 |  |  |  |  |

| 11 Reserved                  |                                                                                                |  |  |  |  |

**Table 6. Bi-quad Configuration Settings**

| P0_R108_D[6:5] : BQ_CFG[1:0] | BI-QUAD CONFIGURATION                               |

|------------------------------|-----------------------------------------------------|

| 00 (Default)                 | No bi-quads per channel; bi-quads are all disabled. |

| 01                           | 1 bi-quad per channel                               |

| 10                           | 2 bi-quads per channel                              |

| 11                           | 3 bi-quads per channel                              |

Table 7 lists the processing blocks that are available for a given input channel. These assignments are fixed and cannot be changed. The two-channel summer mode is available for the first six channels, and cannot be assigned to channels 7 and 8, even if some of the other channels are disabled. Similarly, the four-channel mixer, four-channel summer, and three bi-quads per channel are available for the first four channels only. Input channels 1 to 4 support the most features, while channels 7 and 8 support the least number of features.

| POST-<br>PROCESSING<br>LOCK | 1        | 2        | 3 | 4        | 5 | 6 | 7 | 8 |

|-----------------------------|----------|----------|---|----------|---|---|---|---|

| Two-channel<br>Summer       | V        | √        | √ | √        | √ | √ | x | х |

| Four-channel<br>Summer      | <b>V</b> | √        | √ | √        | х | х | x | х |

| Four-channel<br>Mixer       | √        | <b>V</b> | √ | <b>V</b> | х | х | х | х |

| Bi-quads Available          | 3        | 3        | 3 | 3        | 2 | 2 | 1 | 1 |

Table 7. Processing Block Assignments Across Input Channels

## 3 Processing Blocks Supported for Different Sample Rates

This section describes the specific processing blocks available for different sample rates.

# 3.1 8 kHz Sample Rate

Only the linear phase (default) decimation filter response is supported for the 8 kHz sample rate. Supported processing blocks include bi-quads, digital mixer, and channel summer. The AGC or DRE block is not supported for the 8 kHz sample rate. Bi-quads, channel summers, and digital mixer blocks are supported on the respective input channels (Table 7).

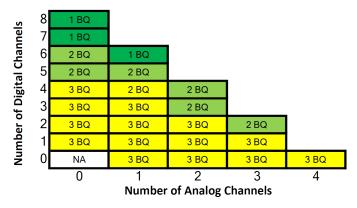

Figure 2 shows the analog-channel and digital-channel combinations that can be supported for an 8 kHz sample rate. For example, it can be seen that with two analog channels (third column), up to four digital channels can be supported, whereas with one analog channel, up to 6 digital channels can be supported. The cell entry indicates the number of bi-quads available for that channel combination. For example, with the combination of two analog and two digital microphones and three bi-quads per channel can be supported, but for two analog and three digital microphones, only two bi-quads per channel can be supported.

Figure 2. Supported Channel Combinations for 8 kHz to 48 kHz Sample Rates

### 3.2 16 kHz-48 kHz Sample Rate

All processing blocks and digital filter options are supported for the 16 kHz to 48 kHz sample rates.

The decimation filter can be configured to linear phase, low latency, or ultra-low latency. AGC or DRE is supported for all analog channels. Bi-quads, channel summers, and digital mixer blocks are supported on their respective input channels (Table 7). Figure 2 shows the channel combinations supported for an 8 kHz operation. These remain the same. For a supported channel combination, the cell entry in Figure 2 indicates the number of bi-quads available for that channel combination.

### 3.3 96 kHz Sample Rate

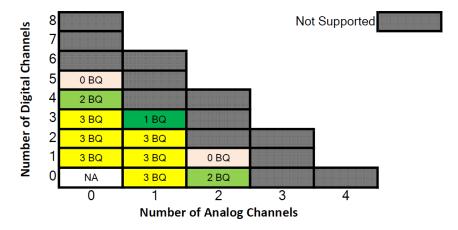

All three decimation filter options are supported for 96 kHz operation. 96 kHz mode supports AGC and DRE, but not for all channel combinations. Figure 3 shows the channel combinations supported when AGC or DRE is enabled. Figure 4 shows the channel combinations support when AGC or DRE is disabled.

Figure 3. Channel Combinations for 96 kHz with DRE/AGC Enabled

Figure 4. Channel Combinations for 96 kHz with DRE/AGC Disabled

#### 3.4 192 kHz Sample Rate

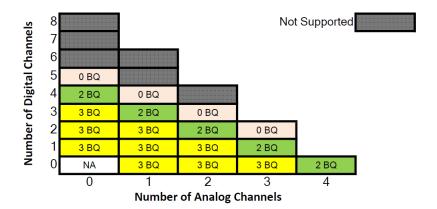

All three decimation filter options are supported for 192 kHz operation.

Figure 5 shows the channel combinations supported for 192 kHz sample rate with linear phase decimation filter response when DRE or AGC is enabled. Figure 6 shows the combinations supported without AGC or DRE. Bi-quads, channel summers, and digital mixer are supported with the linear phase decimation filter option.

Figure 5. Channel Combinations for 192 kHz Linear Phase Filter with AGC/DRE Enabled

Figure 6. Channel Combinations for 192 kHz Linear Phase Filter with AGC/DRE Disabled

For the low latency (and ultra-low latency) decimation filter response option, a maximum of three channels are supported when AGC or DRE is disabled. Only one channel is supported when AGC or DRE is enabled. Bi-quads, channel summers, and digital mixer are not supported for this mode.

### 3.5 384 kHz Sample Rate

Linear phase (DECI\_FILT = 00) and ultra-low latency (DECI\_FILT = 10) decimation filter responses are supported for the 384 kHz sample rate. AGC and DRE, bi-quads, channel summers, and digital mixer blocks are not supported for 384 kHz operation. A maximum of two channels are supported for 384 kHz and they can be analog, digital, or a combination of both.

### 3.6 768 kHz Sample Rate

Only linear phase (DECI\_FILT = 00) decimation filter response is supported for 768 kHz sample rate. AGC and DRE, bi-quads, channel summers, and digital mixer blocks are not supported. Just one channel is supported. It can be an analog channel or a digital PDM microphone.

### 4 Example Configurations

A few example device configuration scripts for different combinations are presented below.

**Example 1:** Two input channels with four output channels using digital mixer.

- 1. Differential 2-channel input

- 2. Linear phase decimation filter

- 3. 24-bit TDM mode

- 4. Enable digital mixer mode

- 5. Digital Mixer 3: Ch3 Out =  $0.5 \times \text{Ch1} + 0.5 \times \text{Ch2}$

- 6. Digital Mixer 4: Ch4 Out = 0.5xCh1 0.5xCh2

```

# Key: w 98 XX YY ==> write to I2C address 0x98, to register 0xXX, data 0xYY

# ==> comment delimiter

# Differential 2-channel 24-bit TDM mode : INP1/INM1 - Ch1, INP2/INM2 - Ch2

\# FSYNC = 48 kHz (Output Data Sample Rate), BCLK = 11.2896 MHz (BCLK/FSYNC = 256)

# Power up IOVDD and AVDD power supplies keeping SHDNZ pin voltage LOW

# Wait for IOVDD and AVDD power supplies to settle to steady state operating voltage range.

# Release SHDNZ to HIGH.

# Wait for 1ms.

w 98 00 00 # Goto Page 0

w 98 02 81 # Wake-up device by I2C write into P0_R2 using internal AREG

w 98 6B 01

# Linear Phase Decimation Filter with digital mixer

# Digital Mixer 3 Configuration

w 98 00 04

# Goto Page 4

w 98 28 40 00 00 00 # Digital Mixer 3: Channel 1 Coefficient (MIX3_CH1) = 0.5

w 98 2C 40 00 00 00 # Digital Mixer 3: Channel 2 Coefficient (MIX3_CH2) = 0.5

w 98 30 00 00 00 00 # Digital Mixer 3: Channel 3 Coefficient (MIX3_CH3) = 0.0

w 98 34 00 00 00 00 # Digital Mixer 3: Channel 4 Coefficient (MIX3_CH4) = 0.0

# Digital Mixer 4 Configuration

w 98 00 04

# Goto Page 4

w 98 38 40 00 00 00 \# Digital Mixer 4: Channel 1 Coefficient (MIX4_CH1) = 0.5

w 98 3C C0 00 00 00 # Digital Mixer 4: Channel 2 Coefficient (MIX4_CH2) = -0.5

w 98 40 00 00 00 00 # Digital Mixer 4: Channel 3 Coefficient (MIX4_CH3) = 0.0

w 98 44 00 00 00 00 # Digital Mixer 4: Channel 4 Coefficient (MIX4_CH4) = 0.0

w 98 00 00 # Goto Page 0

w 98 07 20 # TDM Mode with 24 Bits/Channel

w 98 73 c0 # Enable Ch.1 - Ch.2

w 98 74 f0 # Enable Ch.1 - Ch.4 ASI Output channels

w 98 75 e0 # Power up ADC

```

#### **Example 2:** Four input channels with channel summer.

- 1. Differential 4-channel input

- 2. Linear phase decimation filter

- 3. 32-bit TDM mode

- 4. Two-channel summer mode

www.ti.com

```

# # # Power up IOVDD and AVDD power supplies keeping SHDNZ pin voltage LOW # Wait for IOVDD and AVDD power supplies to settle to steady state operating voltage range. # Release SHDNZ to HIGH. # Wait for lms. # w 98 00 00 # Goto Page 0 w 98 02 81 # Wake-up device by I2C write into PO_R2 using internal AREG w 98 6B 05 # Linear Phase Filter with 2 channel summer mode (DSP_CFG0) w 98 00 00 # Goto Page 0 w 98 07 30 # TDM Mode with 32 Bits/Channel w 98 73 f0 # Enable Ch.1 - Ch.4 w 98 74 f0 # Enable ASI Output channels

```

### 4.1 References

w 98 75 e0 # Power up ADC

- Texas Instruments, TLV320ADC5140 Quad-Channel, 768-kHz, Burr-Brown Audio ADC Data Sheet

- Texas Instruments, TLV320ADC3140 Quad-Channel, 768-kHz, Burr-Brown Audio ADC Data Sheet

- Texas Instruments, TLV320ADCx140 Programmable Bi-quad Filter Configuration and Applications Application Report

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated