# **TPS23861** Power-On Considerations

Eric Wright

Linear Power/Power Interface

#### ABSTRACT

TPS23861 is an IEEE 802.3at compliant PSE controller containing both analog and digital circuits as well as an embedded processor. The VPWR pin supplies power to the internal analog circuits while the VDD pin supplies power for the digital circuitry and processor. Each power supply pin monitors input voltage and creates an internal power on reset for the internal circuits. Additionally, the RESET pin forces all internal registers to their default power on state. It is important for any integrated circuit with digital content to power on in a well-controlled and consistent manner in order to prevent erratic operation. This principle also applies to TPS23861 and this report discusses several proven power on methods for TPS23861.

### 1 TPS23861 Basic Power-on

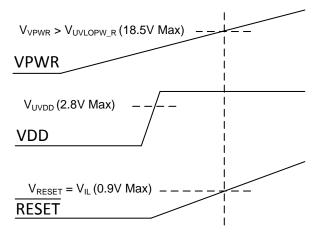

TPS23861 under-voltage lockout (UVLO) threshold at power on is 18.5 V maximum  $(V_{UVLOPW_R})$  for VPWR and 2.8 V maximum  $(V_{UVDD_R})$  for VDD. It is good engineering practice to hold the RESET pin in a low state until both VPWR and VDD have exceeded their respective UVLO rising thresholds. An example of this is shown in Figure 1.

In Figure 1, VPWR starts rising before the VDD rail which is the typical case because the VDD rail is usually derived from the VPWR rail. The VDD rail will turn on when VPWR reaches the externally programmed or internal UVLO of the VDD rail. Also of note in Figure 1 is that RESET starts rising when VDD starts rising because the RESET pin is pulled up to the VDD pin (either externally or internally using the TPS23861 internal pullup).

All trademarks are the property of their respective owners.

TPS23861 Power-on using VDD regulator UVLO > V<sub>UVLOPW R</sub>

# 2 TPS23861 Power-on using VDD regulator UVLO > V<sub>UVLOPW R</sub>

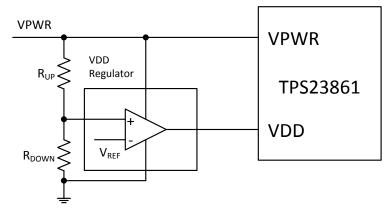

Figure 2 illustrates how the VDD regulator can be configured so that it ramps up VDD after VPWR exceeds  $V_{UVLOPW_R}$ . Resistors  $R_{UP}$  and  $R_{DOWN}$  are chosen accordingly based on the turn on threshold of the VDD regulator internal reference threshold (VREF).

Figure 2. VDD Rail Turns On When VPWR > VUVLOPW R

LM5019MRX can be used with  $R_{UP} = 200 \text{ k}\Omega$  and  $R_{DOWN} = 13.3 \text{ k}\Omega$  for a UVLO of 19.65 V and hysteresis of 4 V. Alternatively if only a single TPS23861 is used in the system then a TPS7A4001 (LDO) can be used with  $R_{UP} = 825 \text{ k}\Omega$  and  $R_{DOWN} = 32.4 \text{ k}\Omega$ .

# 3 TPS23861 Power-on Using Delayed RESET

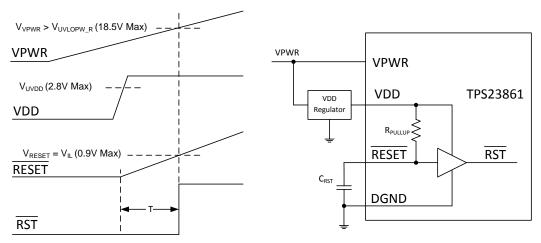

Figure 3 illustrates the use of an external capacitor ( $C_{RST}$ ) and the internal RESET pullup resistor ( $R_{PULLUP}$ ) to implement the required delay, T.

Figure 3. Using C<sub>RST</sub> for Delay

The required value for  $C_{RST}$  can be calculated using Equation 1.

$$C_{RST} = \frac{-T}{R_{PULLUP} \times LN(1 - \frac{V_{RESET}}{V_{VDD}})}$$

(1)

For example, for T = 5 ms,  $R_{PULLUP}$  = 30 k $\Omega$  ( $R_{PULLUP-MIN}$ ),  $V_{RESET}$  = 0.9 V,  $V_{VDD}$  = 3.3 V, the required  $C_{RST}$  = 523 nF. Choosing  $C_{RST}$  = 560 nF yields T with some additional margin (5.35 ms).

When more than one TPS23861 shares the same  $\overline{\text{RESET}}$  signal, the internal pullup resistors act in parallel resulting in a lower equivalent  $R_{\text{PULLUP}}$ . The required value of  $C_{\text{RST}}$  must be multiplied by the number of devices sharing the  $\overline{\text{RESET}}$  signal to yield the desired delay, T.

www.ti.com

Host Managed RESET Using a Digital Isolator

# 4 Host Managed RESET Using a Digital Isolator

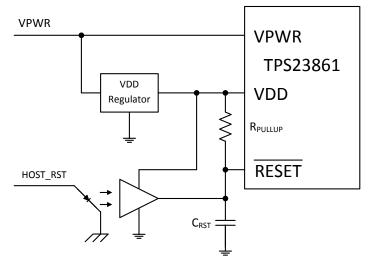

Figure 4 illustrates host side control of the RESET pin sequence through a digital isolator. The isolator can be either a simple photo-coupler or a high performance device such as the ISO72XX family of digital isolators.

Figure 4. Host Side RESET Control

The TI recommended system power up sequence starts with the host side first so that control of the HOST\_RST signal can ensure that the RESET signal is held low before VPWR and VDD power on. Host management of the RESET pin delay depends on the isolator type. Several isolator types and delay methods are described.

- Simple "photo-coupler" such as CEL PS8821-1 with open collector outputs: Since the photo-transistor does not require power from VDD, RESET can be kept low (optically) by the host until TPS23861 is powered. If additional delay is required, then C<sub>RST</sub> can be added.

- High performance isolator powered by VDD such as CEL PS9821-1 with open collector outputs: Since the RESET pin may not be held low until VDD is powered, the isolator cannot respond to the HOST\_RST signal. For this case, C<sub>RST</sub> should be used to implement the required delay.

- High performance isolator powered by VDD such as TI ISO7241C with push-pull outputs and enable inputs: Delaying the RESET pin is possible if the isolator enable and RESET driver are delayed using capacitors. For this case, a capacitor, C<sub>EN2</sub> is required on the ISO7241C EN2 pin along with C<sub>RST</sub> on the RESET pin to implement the overall delay. A VDD regulator with programmable UVLO is a simpler solution when using this isolator type.

- High performance isolator powered by VDD such as TI ISO7221B with push-pull outputs: Delaying the RESET pin is ineffective with a push-pull type output because the high side driver strength overcomes the R<sub>PULLUP</sub>. If this isolator type is used, then a VDD regulator with programmable UVLO must be used.

www.ti.com

PC Command Initialization at Power On

### 5 I<sup>2</sup>C Command Initialization at Power On

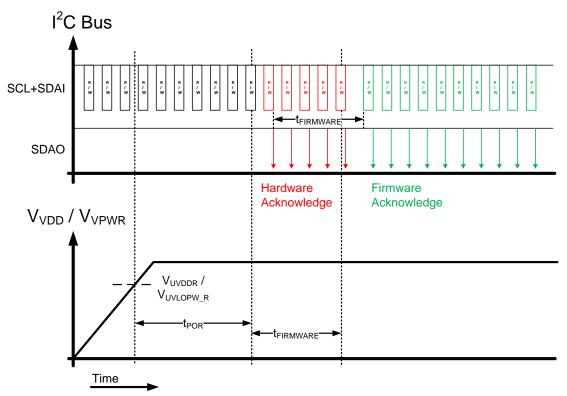

At power on, TPS23861 goes through an initialization sequence. This sequence starts after both VPWR and VDD have exceeded their respective UVLO rising thresholds. The initialization sequence is shown in Figure 5.

Figure 5. Internal Power On Initialization

After both VPWR and VDD have exceeded their respective UVLO rising thresholds, the TPS23861 device hardware initializes for  $t_{POR}$  (23 ms maximum). During  $t_{POR}$ , TPS23861 does not respond (ACK or acknowledge) to I<sup>2</sup>C commands. After  $t_{POR}$  TPS23861 accepts and acknowledge commands but does not process the commands until the internal firmware has initialized ( $t_{FIRMWARE}$ ). Firmware initialization typically takes about 20 ms.

TI recommends that the host I<sup>2</sup>C controller waits for > 43 ms after power on before sending the TPS23861 initialization command sequence for the particular application. Alternatively, the host I<sup>2</sup>C controller can ping the TPS23861 during power on (assuming that the host side controller is powered on and functional before TPS23861 is powered on) and implement a delay between the first ACK and sending the formal command sequence.

#### www.ti.com

## 6 Conclusion

Several methods of TPS23861 power up have been discussed. The simplest method (#1) uses a VDD regulator with programmable UVLO so that RESET does not require delay management.

If the VDD regulator UVLO cannot be programmed then RESET delay management using method 2 or 3 is sufficient.

- 1.  $C_{RST}$  without host control, OR

- 2. C<sub>RST</sub>, plus an open collector isolator plus host control

## 7 References

1. Data Sheet: TPS23861 IEEE 802.3at Quad Port Power-over-Ethernet PSE Controller (SLUSBX9)

5

Conclusion

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ctivity                       |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated