SLVSEA7B - DECEMBER 2019 - REVISED FEBRUARY 2022

# TPS6594-Q1 Power Management IC (PMIC) with 5 BUCKs and 4 LDOs for Safety-Relevant Automotive Applications

## 1 Features

- Qualified for automotive applications

- AEC-Q100 qualified with the following results:

- Device operates from 3 V to 5.5 V input supply

- Device temperature grade 1: –40°C to +125°C

- ambient operating temperature range

- Device HBM classification level 2

- Device CDM classification level C4A

- Functional Safety-Compliant

- Developed for functional safety applications

- Documentation available to aid ISO 26262 system design up to ASIL-D

- Documentation available to aid IEC 61508 system design up to SIL-3

- Systematic capability up to ASIL-D

- Hardware integrity up to ASIL-D

- Input supply voltage monitor and over-voltage protection

- Under/overvoltage monitors and over-current monitors on all output supply rails

- Watchdog with selectable trigger / Q&A mode

- Two error signal monitors (ESMs) with selectable level / PWM mode

- Thermal monitoring with high temperature warning and thermal shutdown

- Bit-integrity (CRC) error detection on internal configuration registers and non-volatile memory (NVM)

- Low-power consumption

- 2 µA typical shutdown current

- 7 µA typical in back up supply only mode

- 20 µA typical in low power standby mode

- Five step-down switched-mode power supply (BUCK) regulators:

- 0.3 V to 3.34 V output voltage range in 5, 10, or 20-mV steps

- One with 4 A, three with 3.5 A, and one with 2 A output current capability

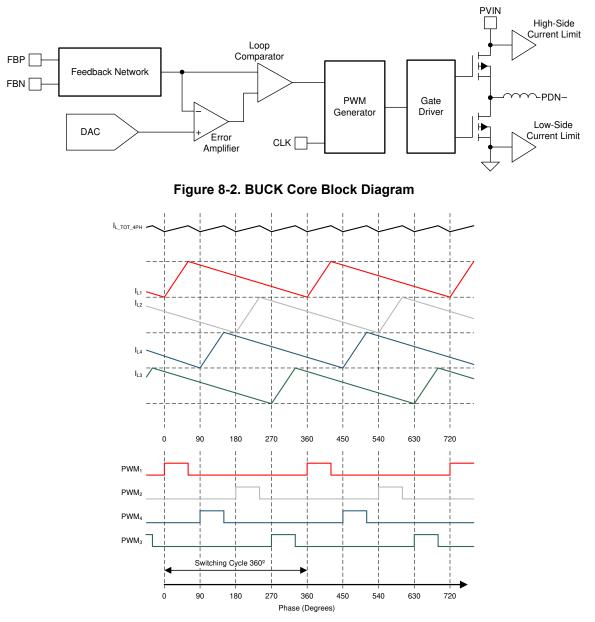

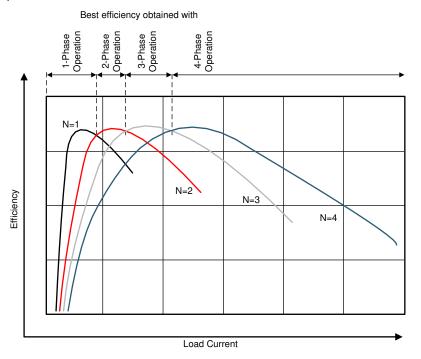

- Flexible multi-phase capability for four BUCKs: up to 14 A output current from a single rail

- Short-circuit and over-current protection

- Internal soft-start for in-rush current limitation

- 2.2 MHz / 4.4 MHz switching frequency

- Ability to synchronize to external clock input

Three low-dropout (LDO) linear regulators with configurable bypass mode

- 0.6 V to 3.3 V output voltage range with 50-mV steps in linear regulation mode

- 1.7 V to 3.3 V output voltage range in bypass mode

- 500 mA output current capability with shortcircuit and over-current protection

- One low-dropout (LDO) linear regulator with lownoise performance

- 1.2 V to 3.3 V output voltage range in 25-mV steps

- 300 mA output current capability with shortcircuit and over-current protection

- Configurable power sequence control in nonvolatile memory (NVM):

- Configurable power-up and power-down sequences between power states

- Digital output signals can be included in the power sequences

- Digital input signals can be used to trigger power sequence transitions

- Configurable handling of safety-relevant errors

- 32-kHz crystal oscillator with option to output a buffered 32-kHz clock output

- Real-time clock (RTC) with alarm and periodic wake-up mechanism

- One SPI or two I<sup>2</sup>C control interfaces, with second I<sup>2</sup>C interface dedicated for Q&A watchdog communication

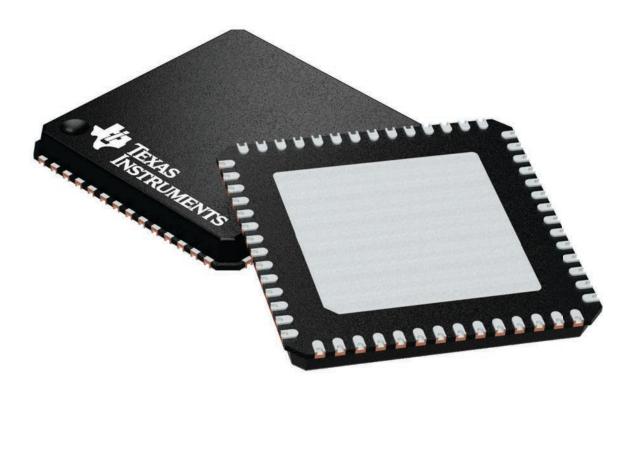

- Package option:

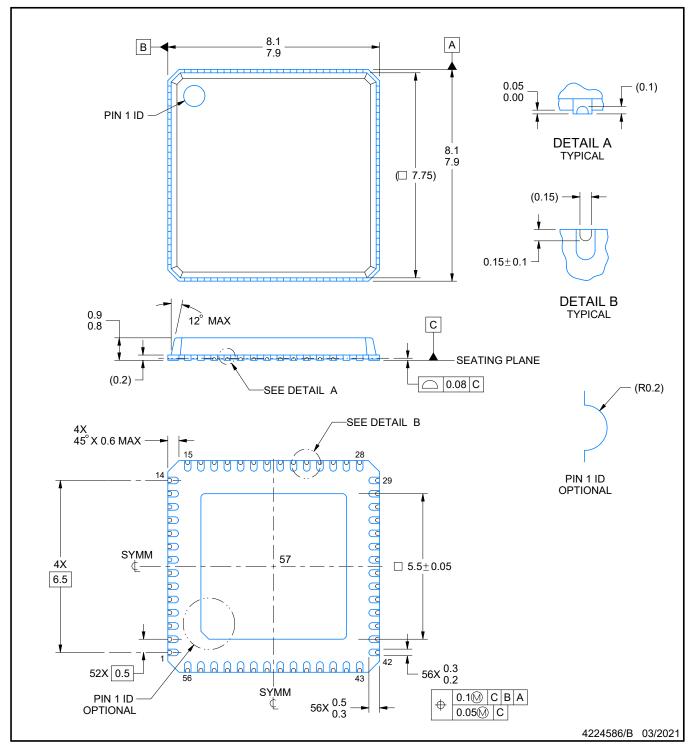

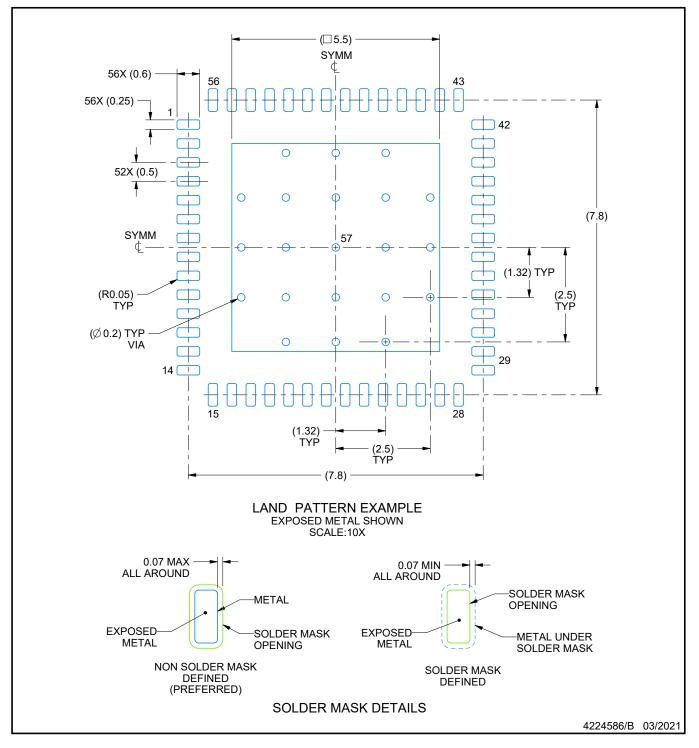

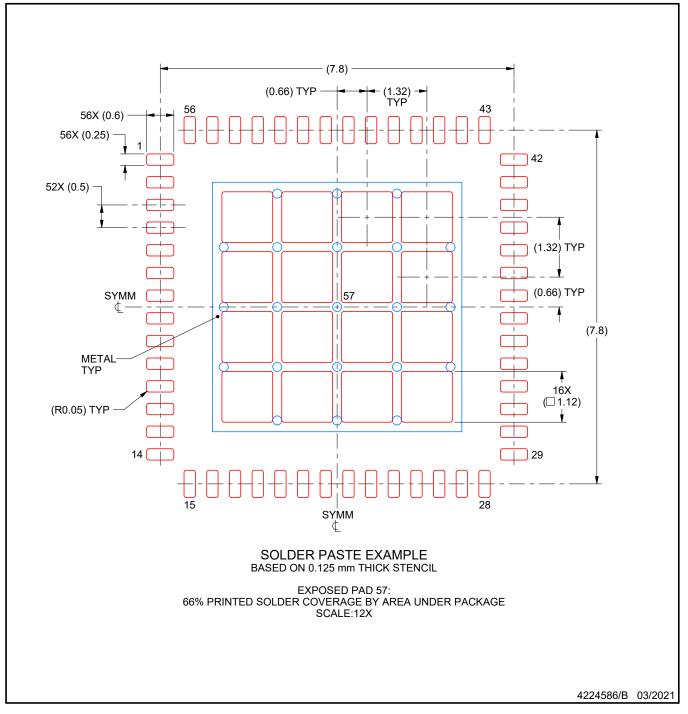

- 8-mm × 8-mm 56-pin VQFNP with 0.5-mm pitch

## 2 Applications

- Automotive infotainment and digital cluster, navigation systems, telematics, body electronics and lighting

- Advanced driver assistance system (ADAS)

- Industrial control and automation

## 3 Description

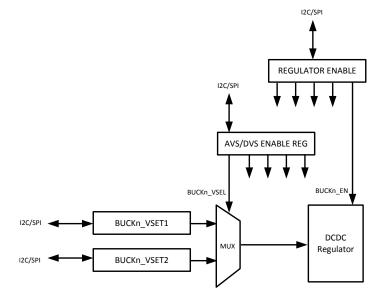

The TPS6594-Q1 device provides four flexible multiphase configurable BUCK regulators with 3.5 A output current per phase, and one additional BUCK regulator with 2 A output current.

| Table 3-1. Device Ir | nformation Table |

|----------------------|------------------|

|----------------------|------------------|

| PART NUMBER <sup>(1)</sup> | PACKAGE    | BODY SIZE (NOM)   |  |  |

|----------------------------|------------|-------------------|--|--|

| TPS6594-Q1                 | VQFNP (56) | 8.00 mm × 8.00 mm |  |  |

(1) See the orderable addendum at the end of the data sheet for all available packages.

Copyright © 2019, Texas Instruments Incorporated

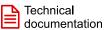

**Functional Diagram**

## **Table of Contents**

| 1 Features                                     | 1  |

|------------------------------------------------|----|

| 2 Applications                                 | 1  |

| 3 Description                                  |    |

| 4 Revision History                             | 3  |

| 5 Description (continued)                      |    |

| 6 Pin Configuration and Functions              |    |

| 6.1 Digital Signal Descriptions                |    |

| 7 Specifications                               |    |

| 7.1 Absolute Maximum Ratings                   |    |

| 7.2 ESD Ratings                                |    |

| 7.3 Recommended Operating Conditions           |    |

| 7.4 Thermal Information                        | 20 |

| 7.5 General Purpose Low Drop-Out Regulators    |    |

| (LDO1, LDO2, LDO3)                             |    |

| 7.6 Low Noise Low Drop-Out Regulator (LDO4)    | 22 |

| 7.7 Internal Low Drop-Out Regulators (LDOVRTC, |    |

| LDOVINT)                                       | 23 |

| 7.8 BUCK1, BUCK2, BUCK3, BUCK4 and BUCK5       |    |

| Regulators                                     |    |

| 7.9 Reference Generator (BandGap)              |    |

| 7.10 Monitoring Functions                      |    |

| 7.11 Clocks, Oscillators, and PLL              |    |

| 7.12 Thermal Monitoring and Shutdown           |    |

| 7.13 System Control Thresholds                 |    |

| 7.14 Current Consumption                       |    |

| 7.15 Backup Battery Charger                    |    |

| 7.16 Digital Input Signal Parameters           |    |

| 7.17 Digital Output Signal Parameters          |    |

| 7.18 I/O Pullup and Pulldown Resistance        | 39 |

|                                                |    |

| 7.19 I <sup>2</sup> C Interface                | 39  |

|------------------------------------------------|-----|

| 7.20 Serial Peripheral Interface (SPI)         | 41  |

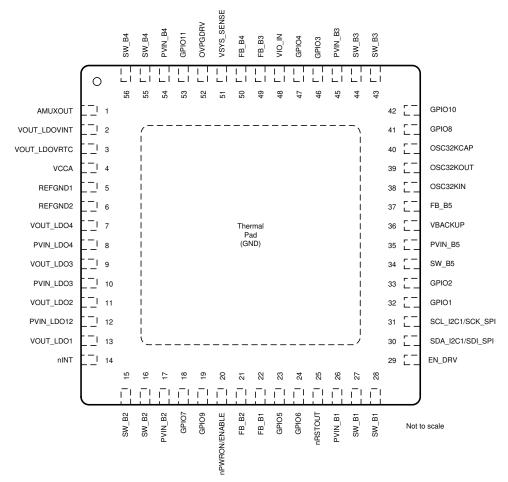

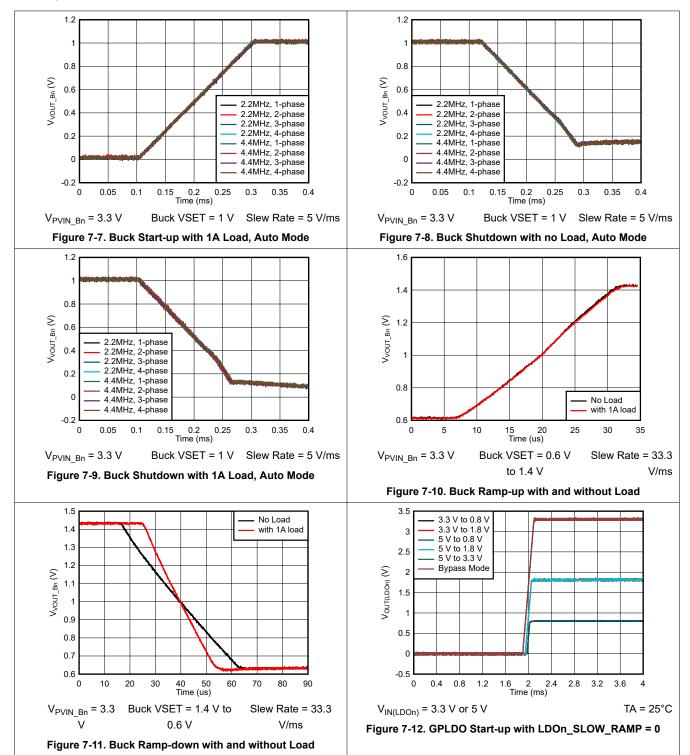

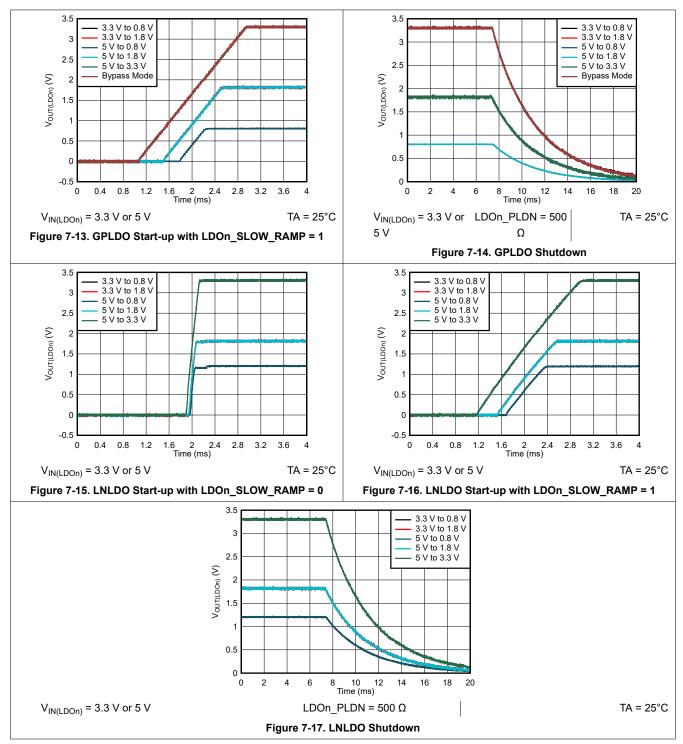

| 7.21 Typical Characteristics                   |     |

| 8 Detailed Description                         |     |

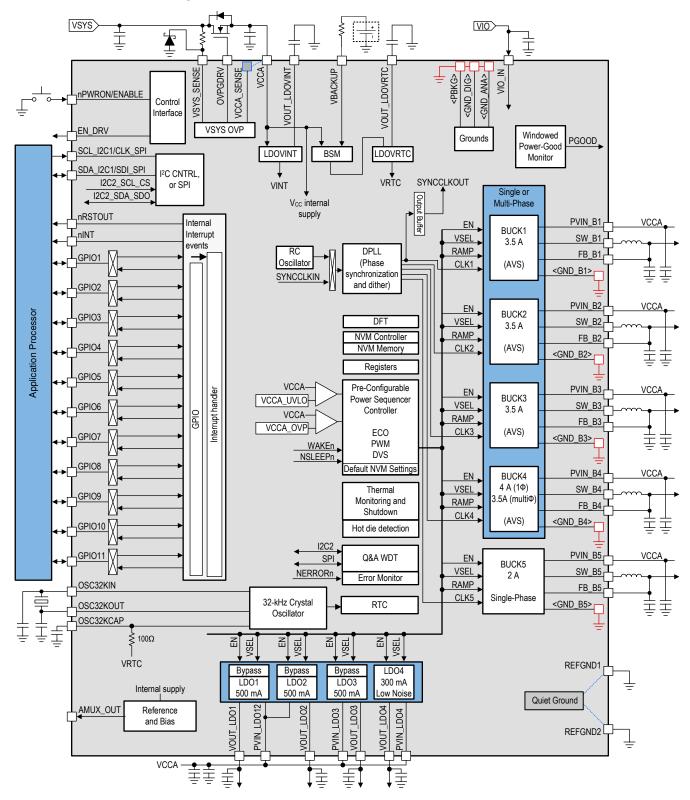

| 8.1 Overview                                   |     |

| 8.2 Functional Block Diagram                   | 46  |

| 8.3 Feature Description.                       | 47  |

| 8.4 Device Functional Modes                    | 121 |

| 8.5 Control Interfaces                         |     |

| 8.6 Configurable Registers                     | 161 |

| 8.7 Register Maps                              |     |

| 9 Application and Implementation               |     |

| 9.1 Application Information                    |     |

| 9.2 Typical Application                        |     |

| 10 Power Supply Recommendations                |     |

| 11 Layout                                      |     |

| 11.1 Layout Guidelines                         |     |

| 11.2 Layout Example                            |     |

| 12 Device and Documentation Support            |     |

| 12.1 Device Support                            |     |

| 12.2 Device Nomenclature                       |     |

| 12.3 Documentation Support                     |     |

| 12.4 Receiving Notification of Documentation U |     |

| 12.5 Support Resources                         |     |

| 12.6 Trademarks                                |     |

| 12.7 Electrostatic Discharge Caution           |     |

| 12.8 Glossary                                  |     |

| 13 Mechanical, Packaging, and Orderable        |     |

| Information                                    |     |

|                                                |     |

## **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | hanges from Revision A (April 2021) to Revision B (February 2022)                                       | Page            |

|----|---------------------------------------------------------------------------------------------------------|-----------------|

| •  | Section 8.8 Specifications - BUCK1, BUCK2, BUCK3, BUCK4 and BUCK5 Regulators: Change typical va         | lue             |

|    | for parameter 4.112 (from 300-mA to 420-mA), parameter 4.113 (from 200-mA to 100-mA), parameter 4.1     | 22              |

|    | (from 250-mA to 370-mA), parameter 4.123 (from 150-mA to 30-mA), parameter 4.131 (from 400-mA to 3      | 510-            |

|    | mA), parameter 4.132 (from 170-mA to 290-mA), parameter 4.133 (from 230-mA to 20-mA), parameter 4.      | .151            |

|    | (from 335-mA to 290-mA), parameter 4.152 (from 150-mA to 230-mA), parameter 4.153 (from 185-mA to       | 50-             |

|    | mA)                                                                                                     | 18              |

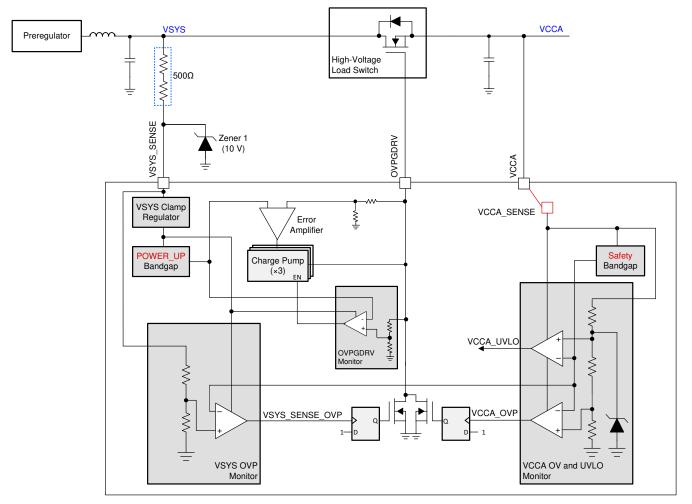

| •  | Added description about OVGDRV - VSYSSENSE relation                                                     | 47              |

| •  | BUCK Regulator Overview: added Current Limit and Short-to-Ground Detection on SW_Bx pins                | 49              |

| •  | Added section: BUCK Regulator Current Limit                                                             | 58              |

| •  | Added section: SW_Bx Short-to-Ground Detection                                                          |                 |

| •  | Added LDO1, LDO2, LDO3 Current Limit description                                                        | <mark>61</mark> |

| •  | Added LDO4 Current Limit description                                                                    |                 |

| •  | Added note about unmasking the UV/OV right before the release of the nRSTOUT resp. nRSTOUT_SoC          |                 |

|    | pins                                                                                                    | 65              |

| •  | Added note which explains the required voltage accuracy for external supply rails (including VCCA input |                 |

|    | supply) that are monitored by the TPS6594-Q1 in order to pass the ABIST                                 | 65              |

| •  | Added explanation on how to use Voltage Monitors of unused BUCK and LDO regulators                      | 65              |

| •  | Corrected Watchdog Reference Answer Calculation figure                                                  | 94              |

| •  | Added note which explains necessary system-software steps for using RUNTIME_BIST                        | 121             |

| •  | Added BOOT_BIST and RUNTIME_BIST                                                                        | .121            |

TPS6594-Q1 SLVSEA7B – DECEMBER 2019 – REVISED FEBRUARY 2022

| • | Changed all instances of legacy terminology into "controller" and "target", also in all sub-sections<br>For I2C, changed all instances of legacy terminology into "controller" and "target". For SPI, changed all<br>instances of legacy terminology into "controller" and "peripheral". For the CRC, changed all instances of<br>legacy terminology into "CRC on received data (R_CRC)", and "CRC on transmitted data" (T_CRC). The |       |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|   | changes also applies to all sub-sections.                                                                                                                                                                                                                                                                                                                                                                                            | . 154 |

| • | Bit Target CRC (T_CRC) Input                                                                                                                                                                                                                                                                                                                                                                                                         | . 154 |

| • | Added note about missing R_CRC after am I2C write                                                                                                                                                                                                                                                                                                                                                                                    |       |

| • | Added note which describes a device erratum related to COMM_FRM_ERR_INT bit                                                                                                                                                                                                                                                                                                                                                          |       |

| • | Added note which explains the I <sup>2</sup> C addresses for each register map page on the I <sup>2</sup> C bus. Added note which                                                                                                                                                                                                                                                                                                    |       |

|   | explains how each register map page is addressed when using SPI.                                                                                                                                                                                                                                                                                                                                                                     |       |

| • | Added note about writing to RESERVED bits causing a Register Map CRC error                                                                                                                                                                                                                                                                                                                                                           |       |

| • | Corrected description of register DEV_REV                                                                                                                                                                                                                                                                                                                                                                                            | .163  |

| • | Updated PDN example figure, and updated the table with the Local and POL Capacitors used for Buck U                                                                                                                                                                                                                                                                                                                                  | se    |

|   | Case Validation                                                                                                                                                                                                                                                                                                                                                                                                                      | .368  |

| • | Updated the recommendations for the Digital Signal Connections                                                                                                                                                                                                                                                                                                                                                                       |       |

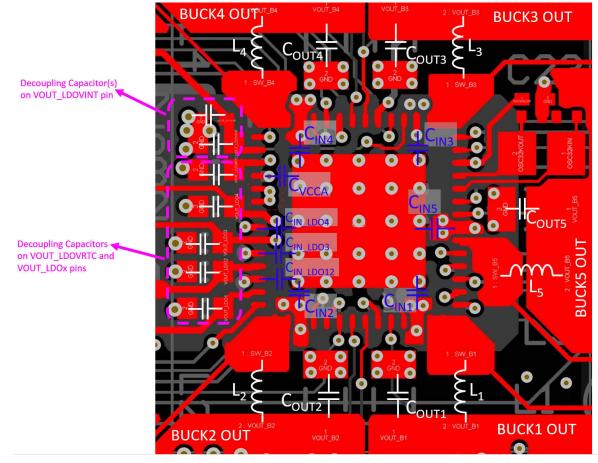

| • | Updated Layout Guidelines with respect to output capacitor on VOUT_LDOVINT pin                                                                                                                                                                                                                                                                                                                                                       |       |

| • | Updated Layout Example figure                                                                                                                                                                                                                                                                                                                                                                                                        | . 385 |

| С | hanges from Revision * (December 2019) to Revision A (April 2021)                                                                                                                                                                                                                                                                                                                                                                    | Page  |

| • | Updated the numbering format for tables, figures, and cross-references throughout the document                                                                                                                                                                                                                                                                                                                                       | 1     |

## **5** Description (continued)

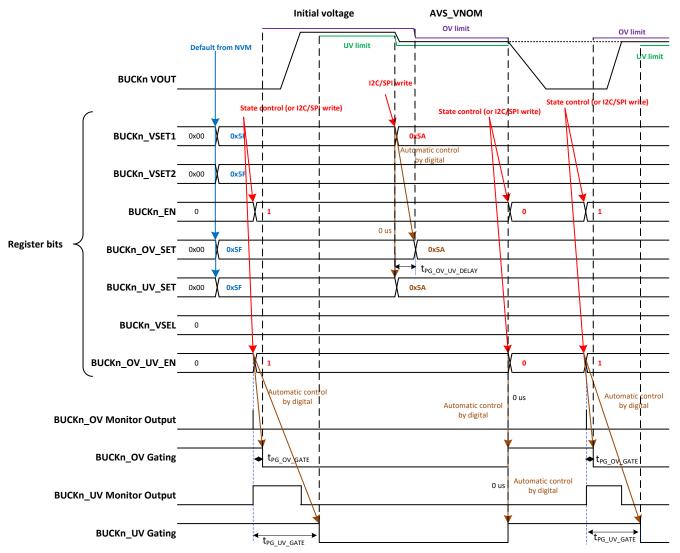

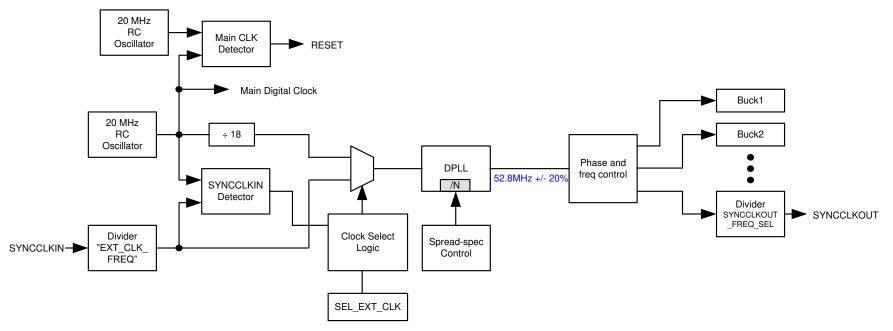

All of the BUCK regulators can be synchronized to an internal 2.2-MHz or 4.4-MHz or an external 1-MHz, 2-MHz, or 4-MHz clock signal. To improve the EMC performance, an integrated spread-spectrum modulation can be added to the synchronized BUCK switching clock signal. This clock signal can also be made available to external devices through a GPIO output pin. The device provides four LDOs: three with 500-mA capability, which can be configured as load switches; one with 300-mA capability and low-noise performance.

Non-volatile memory (NVM) is used to control the default power sequences and default configurations, such as output voltage and GPIO configurations. The NVM is pre-programmed to allow start-up without external programming. Most static configurations, stored in the register map of the device, can be changed from the default through SPI or I<sup>2</sup>C interfaces to configure the device to meet many different system needs. The NVM contains a bit-integrity-error detection feature (CRC) to stop the power-up sequence if an error is detected, preventing the system from starting in an unknown state.

The TPS6594-Q1 includes a 32-kHz crystal oscillator, which generates an accurate 32-kHz clock for the integrated RTC module. A backup-battery management provides power to the crystal oscillator and the real-time clock (RTC) module from a coin cell battery or a super-cap in the event of power loss from the main supply.

The TPS6594-Q1 device includes protection and diagnostic mechanisms such as voltage monitoring on the input supply, input over-voltage protection, voltage monitoring on all BUCK and LDO regulator outputs, register and interface CRC, current-limit, short-circuit protection, thermal pre-warning, and over-temperature shutdown. The device also includes a Q&A or trigger mode watchdog to monitor for MCU software lockup, and two error signal monitor (ESM) inputs with fault injection options to monitor the error signals from the attached SoC or MCU. The TPS6594-Q1 can notify the processor of these events through the interrupt handler, allowing the MCU to take action in response.

## **6** Pin Configuration and Functions

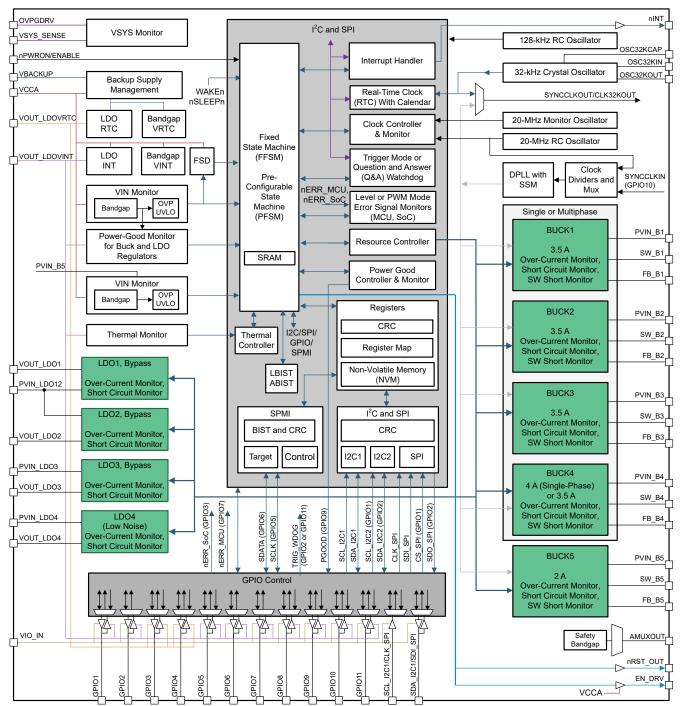

Figure 6-1 shows the 56-pin RWE plastic quad-flatpack no-lead (VQFNP) pin assignments and thermal pad.

Figure 6-1. 56-Pin RWE (VQFNP) Package, 0.5-mm Pitch, With Thermal Pad (Top View)

#### Table 6-1. Pin Attributes

| PIN<br>NAME NO.     |          | 1/0 | DESCRIPTION                                                                                                                                                      | CONNECTION IF<br>NOT USED |  |

|---------------------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|

|                     |          | 1/0 | DESCRIPTION                                                                                                                                                      |                           |  |

| STEP-DOWN CONVERTER | RS (BUCK | (s) |                                                                                                                                                                  |                           |  |

| FB_B1               | 22       | I   | Output voltage-sense (feedback) input for BUCK1 or differential voltage-<br>sense (feedback) positive input for BUCK12/123/1234 in multi-phase<br>configuration. | Ground                    |  |

| FB_B2               | 21       | I   | Output voltage-sense (feedback) input for BUCK2 or differential voltage-<br>sense (feedback) negative input for BUCK12/123/1234 in multi-phase<br>configuration. | Ground                    |  |

| FB_B3               | 49       | I   | Output voltage-sense (feedback) input for BUCK3 or differential voltage-<br>sense (feedback) positive input for BUCK34 in dual-phase configuration.              | Ground                    |  |

| FB_B4               | 50       | I   | Output voltage-sense (feedback) input for BUCK4 or differential voltage-<br>sense (feedback) negative input for BUCK34 in dual-phase configuration.              | Ground                    |  |

| FB_B5               | 37       | I   | Output voltage-sense (feedback) input for BUCK5                                                                                                                  | Ground                    |  |

| PVIN_B1             | 26       | I   | Power input for BUCK1                                                                                                                                            | VCCA                      |  |

| PVIN_B2             | 17       | I   | Power input for BUCK2                                                                                                                                            | VCCA                      |  |

| PVIN_B3             | 45       | I   | Power input for BUCK3                                                                                                                                            |                           |  |

| PVIN_B4             | 54       | I   | Power input for BUCK4 VCCA                                                                                                                                       |                           |  |

| PIN                |          |       |                                                                                                                                                                                                            | CONNECTION IF                     |  |

|--------------------|----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|

| NAME               | NO.      | I/O   | DESCRIPTION                                                                                                                                                                                                | NOT USED                          |  |

| PVIN_B5            | 35       | I     | Power input for BUCK5                                                                                                                                                                                      | VCCA                              |  |

| SW_B1              | 27       | 0     | Switch node of BUCK1                                                                                                                                                                                       | Floating                          |  |

| SW_B1              | 28       | 0     | Switch node of BUCK1                                                                                                                                                                                       | Floating                          |  |

| SW_B2              | 15       | 0     | Switch node of BUCK2                                                                                                                                                                                       | Floating                          |  |

| SW_B2              | 16       | 0     | Switch node of BUCK2                                                                                                                                                                                       | Floating                          |  |

| SW_B3              | 43       | 0     | Switch node of BUCK3                                                                                                                                                                                       | Floating                          |  |

| SW_B3              | 44       | 0     | Switch node of BUCK3                                                                                                                                                                                       | Floating                          |  |

| SW_B4              | 55       | 0     | Switch node of BUCK4                                                                                                                                                                                       | Floating                          |  |

| SW_B4              | 56       | 0     | Switch node of BUCK4                                                                                                                                                                                       | Floating                          |  |

| SW_B5              | 34       | 0     | Switch node of BUCK5                                                                                                                                                                                       | Floating                          |  |

| LOW-DROPOUT REGULA | TORS     |       |                                                                                                                                                                                                            | I                                 |  |

| PVIN_LDO3          | 10       | I     | Power input voltage for LDO3 regulator                                                                                                                                                                     | VCCA                              |  |

| PVIN_LDO4          | 8        | I     | Power input voltage for LDO4 regulator                                                                                                                                                                     | VCCA                              |  |

| PVIN_LDO12         | 12       | I     | Power input voltage for LDO1 and LDO2 regulator                                                                                                                                                            | VCCA                              |  |

| VOUT_LDO1          | 13       | 0     | LDO1 output voltage                                                                                                                                                                                        | Floating                          |  |

| VOUT_LDO2          | 11       | 0     | LDO2 output voltage                                                                                                                                                                                        | Floating                          |  |

| VOUT_LDO3          | 9        | 0     | LDO3 output voltage                                                                                                                                                                                        | Floating                          |  |

| VOUT_LDO4          | 7        | 0     | LDO4 output voltage                                                                                                                                                                                        | Floating                          |  |

| LOW-DROPOUT REGULA | TORS (IN | TERNA | L)                                                                                                                                                                                                         | I                                 |  |

| VOUT_LDOVINT       | 2        | 0     | LDOVINT output for connecting to the filtering capacitor. Not for external loading.                                                                                                                        | _                                 |  |

| VOUT_LDOVRTC       | 3        | 0     | LDOVRTC output for connecting to the filtering capacitor. Not for external loading.                                                                                                                        | _                                 |  |

| CRYSTAL OSCILLATOR |          |       |                                                                                                                                                                                                            | 1                                 |  |

| OSC32KCAP          | 40       | 0     | Filtering capacitor for the 32 KHz crystal Oscillator, connected to VRTC through an internal 100 $\Omega$ resistor.                                                                                        | Floating                          |  |

| OSC32KIN           | 38       | I     | 32-KHz crystal oscillator input                                                                                                                                                                            | Ground                            |  |

| OSC32KOUT          | 39       | 0     | 32-KHz crystal oscillator output                                                                                                                                                                           | Floating                          |  |

| SYSTEM CONTROL     |          |       |                                                                                                                                                                                                            |                                   |  |

| AMUXOUT            | 1        | 0     | Buffered bandgap output                                                                                                                                                                                    | Floating                          |  |

| EN_DRV             | 29       | 0     | Enable Drive output pin to indicate the device entering safe state (set low when ENABLE_DRV bit is '0').                                                                                                   | Floating                          |  |

|                    |          | I/O   | Primary function: General-purpose input <sup>(1)</sup> and output<br>When configured as an output pin, it can be included as part of the power<br>sequencer output signal to enable an external regulator. | Input: Ground<br>Output: Floating |  |

| GPIO1              |          | I     | Alternative function: SCL_I2C2, which is the Q&A WatchDog I <sup>2</sup> C serial clock (external pull-up).                                                                                                | Ground                            |  |

|                    |          | I     | Alternative function: CS_SPI, which is the SPI chip enable signal.                                                                                                                                         | Ground                            |  |

|                    | 32       | 0     | Alternative function: nRSTOUT_SoC, which is the SoC reset or power on output (Active Low).                                                                                                                 | Floating                          |  |

|                    |          | I     | Alternative function: nSLEEP1 or nSLEEP2, which are the sleep request signals for the device to go to lower power states (Active Low).                                                                     | Ground                            |  |

|                    |          | I     | Alternative function: WKUP1 or WKUP2, which are the wake-up request signals for the device to go to higher power states.                                                                                   | Ground                            |  |

| PIN   |     | 1/0 | DESCRIPTION                                                                                                                                                                                                 | CONNECTION IF                                                                                                                                                                                                                                                                  |                                   |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

|-------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----|----|----------------------------------------------------------------------------------------------------------------------------------------|--------|----|----|----|----|----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO. | I/O | DESCRIPTION                                                                                                                                                                                                 | NOT USED                                                                                                                                                                                                                                                                       |                                   |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

|       |     | I/O | Primary function: General-purpose input <sup>(1)</sup> and output<br>When configured as an output pin, it can be included as part of the power<br>sequencer output signal to enable an external regulator.  | Input: Ground<br>Output: Floating                                                                                                                                                                                                                                              |                                   |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

|       |     | I/O | Alternative function: SDA_I2C2, which is the Q&A WatchDog I <sup>2</sup> C serial bidirectional data (external pull-up).                                                                                    | Ground                                                                                                                                                                                                                                                                         |                                   |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

| GPIO2 | 33  | 0   | Alternative function: SDO_SPI, which is the SPI output data signal.                                                                                                                                         | Floating                                                                                                                                                                                                                                                                       |                                   |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

| 01102 | 00  | I   | Alternative function: TRIG_WDOG, which is the watchdog trigger input signal for Watchdog Trigger mode.                                                                                                      | Ground                                                                                                                                                                                                                                                                         |                                   |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

|       |     | I   | Alternative function: nSLEEP1 or nSLEEP2, which are the sleep request signals for the device to go to lower power states (Active Low).                                                                      | Ground                                                                                                                                                                                                                                                                         |                                   |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

|       |     | I   | Alternative function: WKUP1 or WKUP2, which are the wake-up request signals for the device to go to higher power states.                                                                                    | Ground                                                                                                                                                                                                                                                                         |                                   |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

|       |     | I/O | Primary function: General-purpose input <sup>(1)</sup> and output.<br>When configured as an output pin, it can be included as part of the power<br>sequencer output signal to enable an external regulator. | Input: Ground<br>Output: Floating                                                                                                                                                                                                                                              |                                   |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

|       | 46  | I   | Alternative function: nERR_SoC, which is the system error count down input signal from the SoC (Active Low).                                                                                                | Floating                                                                                                                                                                                                                                                                       |                                   |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

| GPIO3 |     | 46  | 0                                                                                                                                                                                                           | Alternative function: CLK32KOUT, which is the output of the 32 KHz crystal oscillator clock.                                                                                                                                                                                   | Floating                          |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

|       |     | I   | Alternative function: nSLEEP1 or nSLEEP2, which are the sleep request signals for the device to go to lower power states (Active Low).                                                                      | Ground                                                                                                                                                                                                                                                                         |                                   |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

|       |     |     | I                                                                                                                                                                                                           | Alternative function: LP_WKUP1 or LP_WKUP2, which are capable of processing a wake-up request for the device to go to higher power states while the device is in LP STANDBY state. They can also be used as regular WKUP1 or WKUP2 pins while the device is in mission states. | Ground                            |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

|       | 47  | 47  | I/O                                                                                                                                                                                                         | Primary function: General-purpose input <sup>(1)</sup> and output.<br>When configured as an output pin, it can be included as part of the power<br>sequencer output signal to enable an external regulator.                                                                    | Input: Ground<br>Output: Floating |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

|       |     |     | 47                                                                                                                                                                                                          | 47                                                                                                                                                                                                                                                                             | 47                                | 47 | 0   | Alternative function: CLK32KOUT, which is the output of the 32 KHz crystal oscillator clock.                                                                                                                | Floating                          |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

| GPIO4 |     |     |                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                |                                   |    | 47  | 47                                                                                                                                                                                                          | 47                                | 47 | 47 | 47                                                                                                                                     | 47     | 47 | 47 | 47 | 47 | 47 | 47  | 47                                                                                                                                                                                                |

|       |     |     | I                                                                                                                                                                                                           | Alternative function: LP_WKUP1 or LP_WKUP2, which are capable of processing a wake-up request for the device to go to higher power states while the device is in LP STANDBY state. They can also be used as regular WKUP1 or WKUP2 pins while the device is in mission states. | Ground                            |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

| GPIO5 | 23  | 23  | 23                                                                                                                                                                                                          | 23                                                                                                                                                                                                                                                                             | 23                                | 23 | I/O | Primary function: General-purpose input <sup>(1)</sup> and output.<br>When configured as an output pin, it can be included as part of the power<br>sequencer output signal to enable an external regulator. | Input: Ground<br>Output: Floating |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

|       |     |     |                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                |                                   |    | 23  | 23                                                                                                                                                                                                          | 23                                | 23 | 23 | 23                                                                                                                                     | 23     | 23 | 23 | 23 | 23 | 23 | I/O | Alternative function: SCLK_SPMI, which is the Multi-PMIC SPMI serial interface clock signal. It is an output pin for the SPMI controller device, and an input pin for the SPMI peripheral device. |

|       |     |     |                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                |                                   |    |     |                                                                                                                                                                                                             |                                   |    | I  | Alternative function: nSLEEP1 or nSLEEP2, which are the sleep request signals for the device to go to lower power states (Active Low). | Ground |    |    |    |    |    |     |                                                                                                                                                                                                   |

|       |     | I   | Alternative function: WKUP1 or WKUP2, which are the wake-up request signals for the device to go to higher power states.                                                                                    | Ground                                                                                                                                                                                                                                                                         |                                   |    |     |                                                                                                                                                                                                             |                                   |    |    |                                                                                                                                        |        |    |    |    |    |    |     |                                                                                                                                                                                                   |

| PIN   |     | I/O | DESCRIPTION                                                                                                                                                                                                 | CONNECTION IF                                                                                                                                                                                               |                                                                                                                                        |                                                                                                                                        |                                                                                                     |                                                                                                              |          |  |  |  |  |  |  |     |                                                                                                                                                                                                             |                                   |

|-------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| NAME  | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                 | NOT USED                                                                                                                                                                                                    |                                                                                                                                        |                                                                                                                                        |                                                                                                     |                                                                                                              |          |  |  |  |  |  |  |     |                                                                                                                                                                                                             |                                   |

|       |     | I/O | Primary function: General-purpose input <sup>(1)</sup> and output.<br>When configured as an output pin, it can be included as part of the power sequencer output signal to enable an external regulator.    | Input: Ground<br>Output: Floating                                                                                                                                                                           |                                                                                                                                        |                                                                                                                                        |                                                                                                     |                                                                                                              |          |  |  |  |  |  |  |     |                                                                                                                                                                                                             |                                   |

| GPIO6 | 24  | I/O | Alternative function: SDATA_SPMI, which is the Multi-PMIC SPMI serial interface bidirectional data signal.                                                                                                  | Floating                                                                                                                                                                                                    |                                                                                                                                        |                                                                                                                                        |                                                                                                     |                                                                                                              |          |  |  |  |  |  |  |     |                                                                                                                                                                                                             |                                   |

|       |     | I   | Alternative function: nSLEEP1 or nSLEEP2, which are the sleep request signals for the device to go to lower power states (Active Low).                                                                      | Ground                                                                                                                                                                                                      |                                                                                                                                        |                                                                                                                                        |                                                                                                     |                                                                                                              |          |  |  |  |  |  |  |     |                                                                                                                                                                                                             |                                   |

|       |     | I   | Alternative function: WKUP1 or WKUP2, which are the wake-up request signals for the device to go to higher power states.                                                                                    | Ground                                                                                                                                                                                                      |                                                                                                                                        |                                                                                                                                        |                                                                                                     |                                                                                                              |          |  |  |  |  |  |  |     |                                                                                                                                                                                                             |                                   |

|       |     | I/O | Primary function: General-purpose input <sup>(1)</sup> and output.<br>When configured as an output pin, it can be included as part of the power<br>sequencer output signal to enable an external regulator. | Input: Ground<br>Output: Floating                                                                                                                                                                           |                                                                                                                                        |                                                                                                                                        |                                                                                                     |                                                                                                              |          |  |  |  |  |  |  |     |                                                                                                                                                                                                             |                                   |

| GPIO7 | 18  | I   | Alternative function: nERR_MCU, which is the system error count down input signal from the MCU (Active Low).                                                                                                | Floating                                                                                                                                                                                                    |                                                                                                                                        |                                                                                                                                        |                                                                                                     |                                                                                                              |          |  |  |  |  |  |  |     |                                                                                                                                                                                                             |                                   |

|       |     | I   | Alternative function: nSLEEP1 or nSLEEP2, which are the sleep request signals for the device to go to lower power states (Active Low).                                                                      | Ground                                                                                                                                                                                                      |                                                                                                                                        |                                                                                                                                        |                                                                                                     |                                                                                                              |          |  |  |  |  |  |  |     |                                                                                                                                                                                                             |                                   |

|       |     | I   | Alternative function: WKUP1 or WKUP2, which are the wake-up request signals for the device to go to higher power states.                                                                                    | Ground                                                                                                                                                                                                      |                                                                                                                                        |                                                                                                                                        |                                                                                                     |                                                                                                              |          |  |  |  |  |  |  |     |                                                                                                                                                                                                             |                                   |

|       | 41  |     | I/O                                                                                                                                                                                                         | Primary function: General-purpose input <sup>(1)</sup> and output.<br>When configured as an output pin, it can be included as part of the power<br>sequencer output signal to enable an external regulator. | Input: Ground<br>Output: Floating                                                                                                      |                                                                                                                                        |                                                                                                     |                                                                                                              |          |  |  |  |  |  |  |     |                                                                                                                                                                                                             |                                   |

|       |     | 0   | Alternative function: SYNCCLKOUT, which is a clock output synchronized to the switching clock signals for the bucks in the device.                                                                          | Floating                                                                                                                                                                                                    |                                                                                                                                        |                                                                                                                                        |                                                                                                     |                                                                                                              |          |  |  |  |  |  |  |     |                                                                                                                                                                                                             |                                   |

| GPIO8 |     | 41  | 41                                                                                                                                                                                                          | 41                                                                                                                                                                                                          | 41                                                                                                                                     | I                                                                                                                                      | Alternative function: DISABLE_WDOG, which is the input to disable the watchdog monitoring function. | Floating                                                                                                     |          |  |  |  |  |  |  |     |                                                                                                                                                                                                             |                                   |

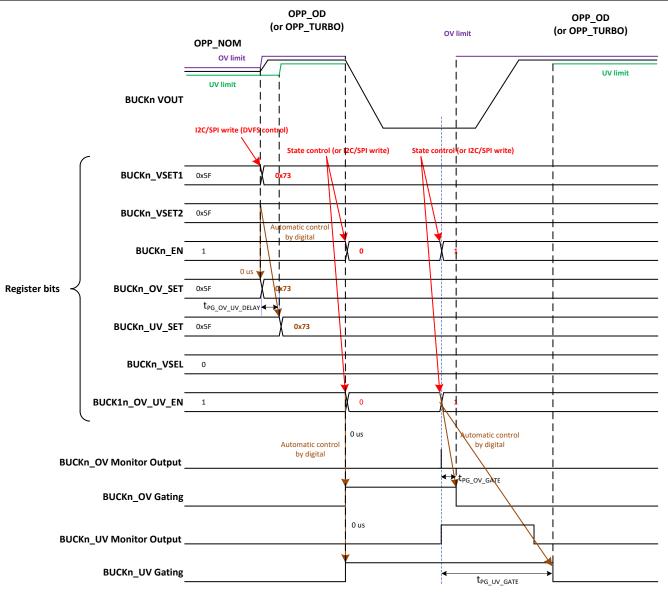

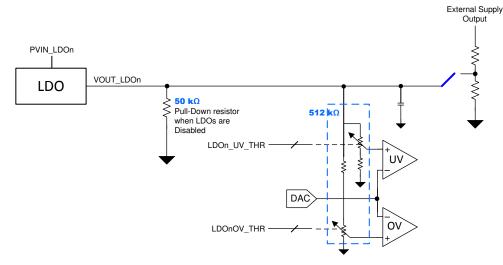

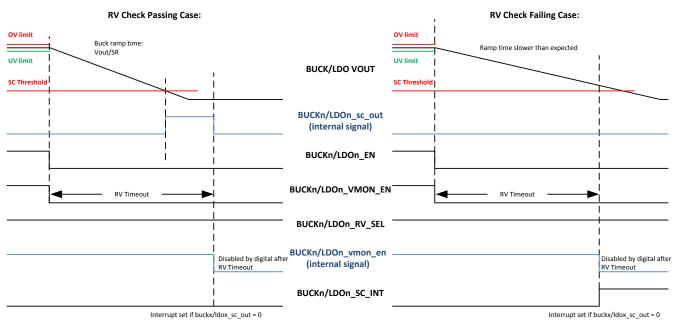

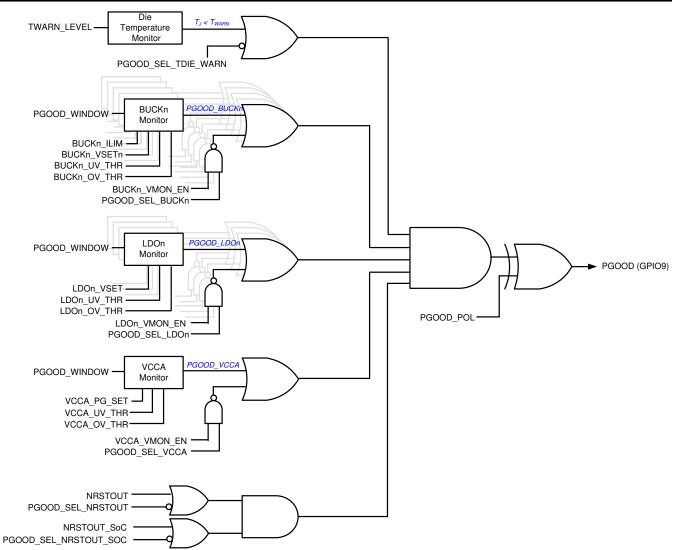

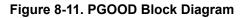

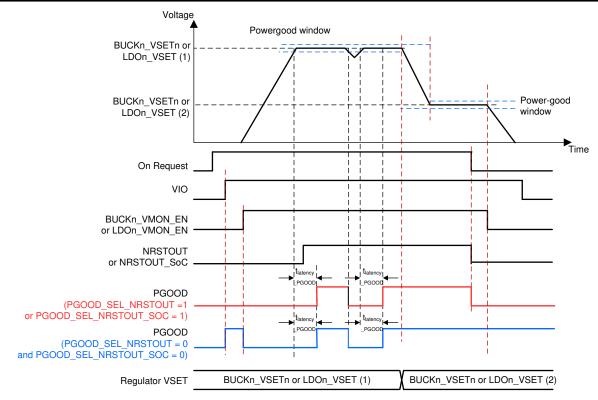

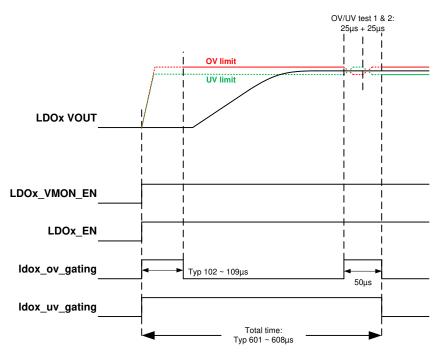

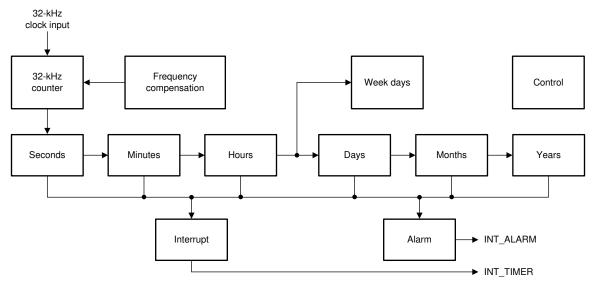

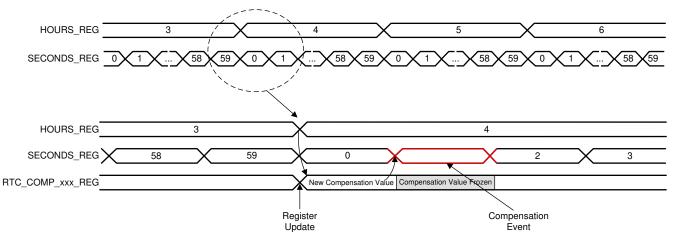

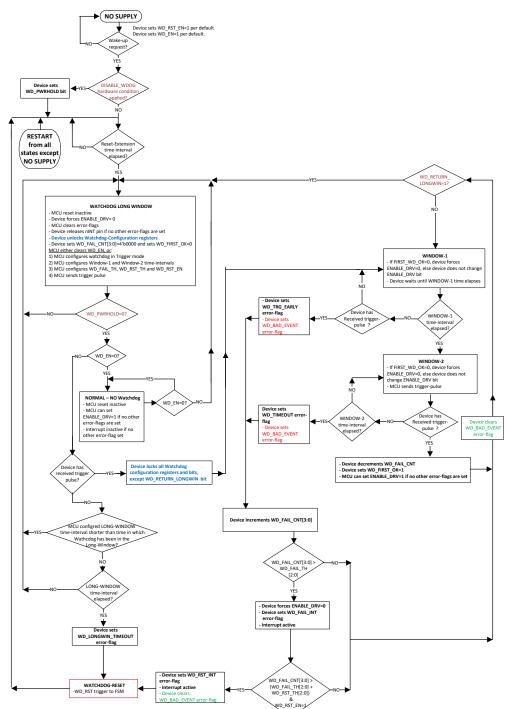

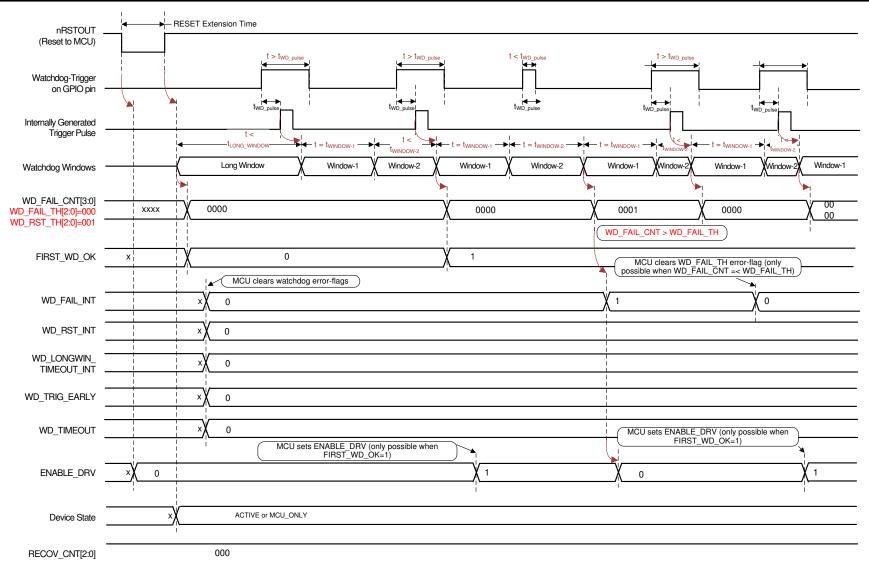

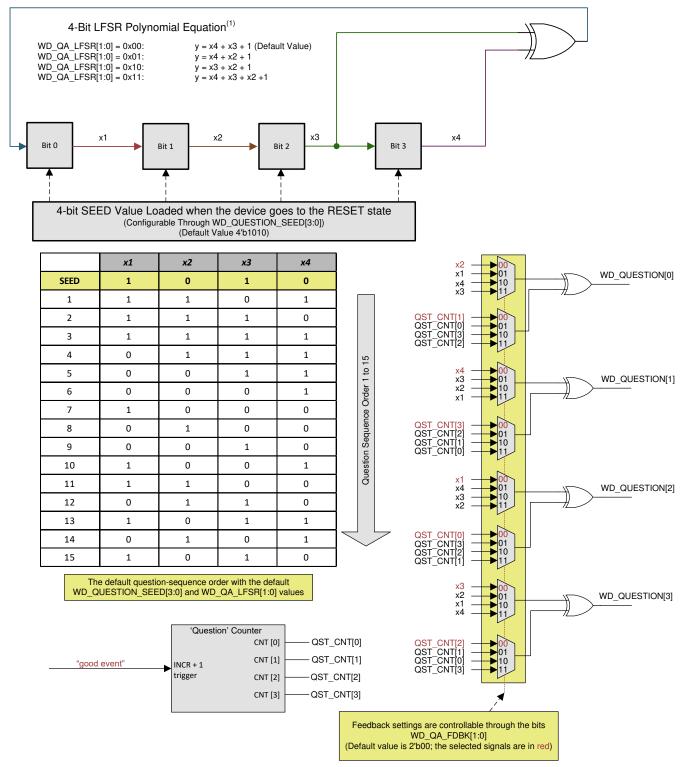

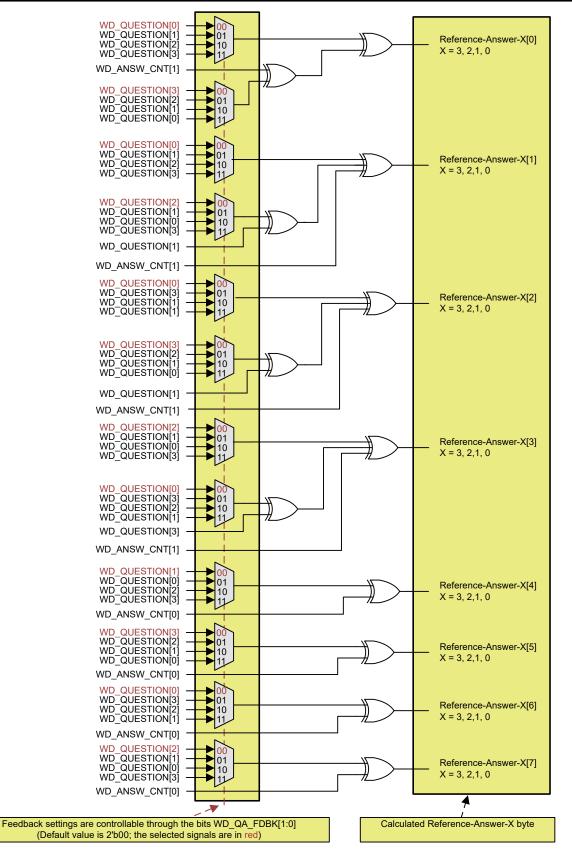

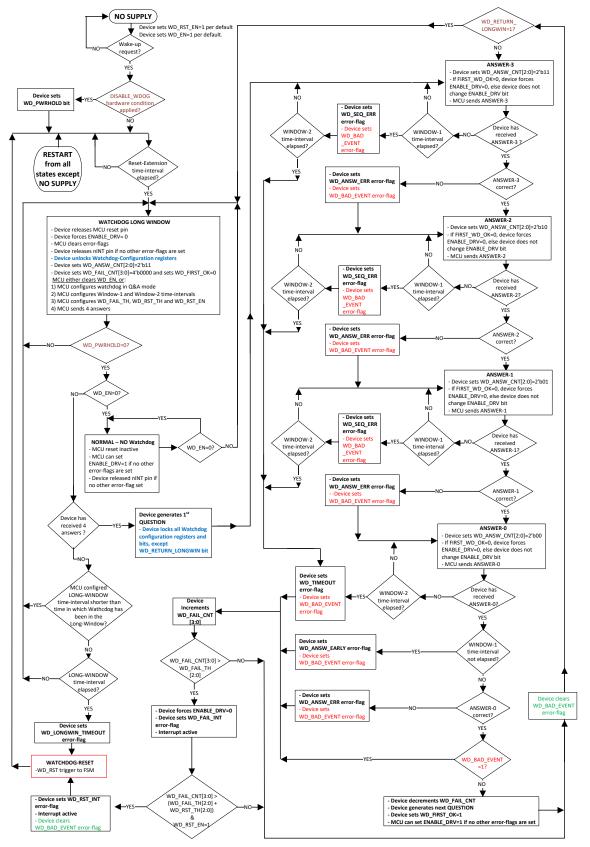

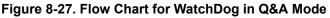

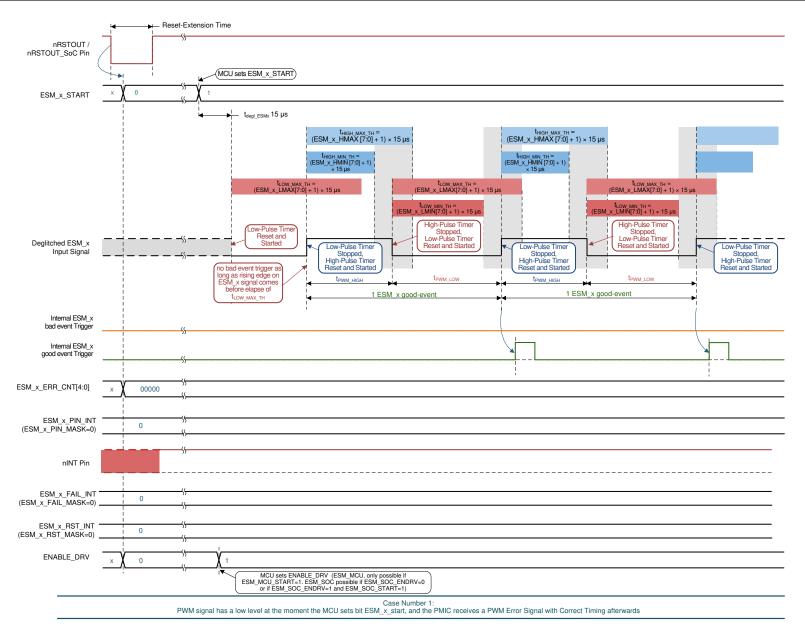

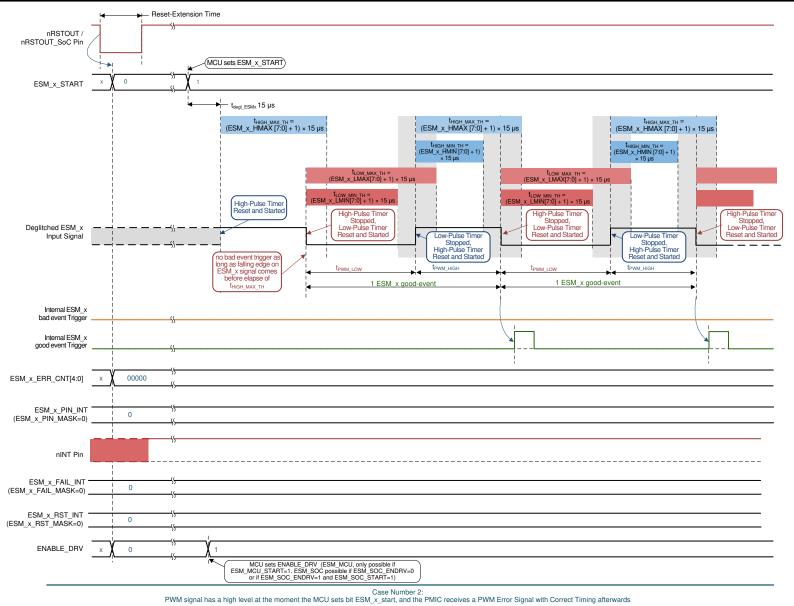

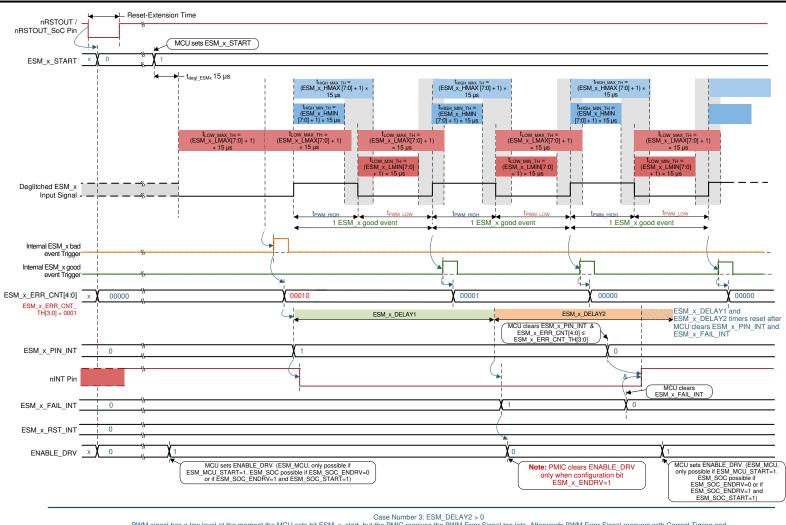

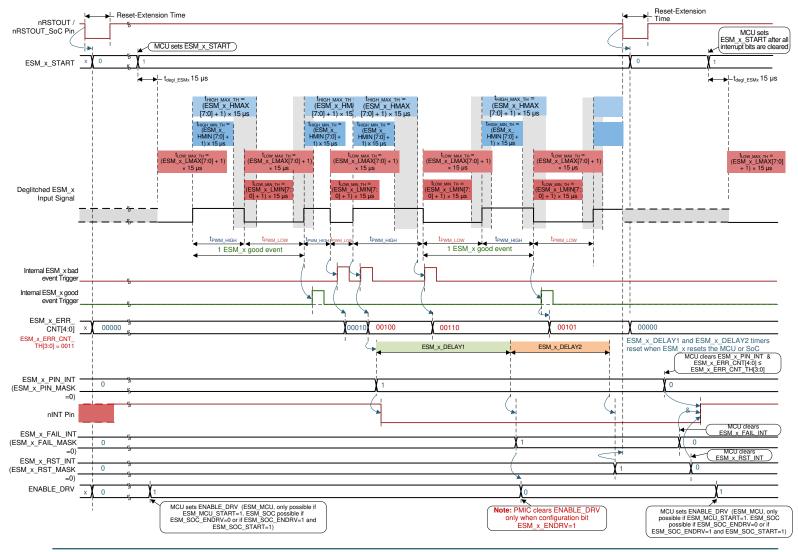

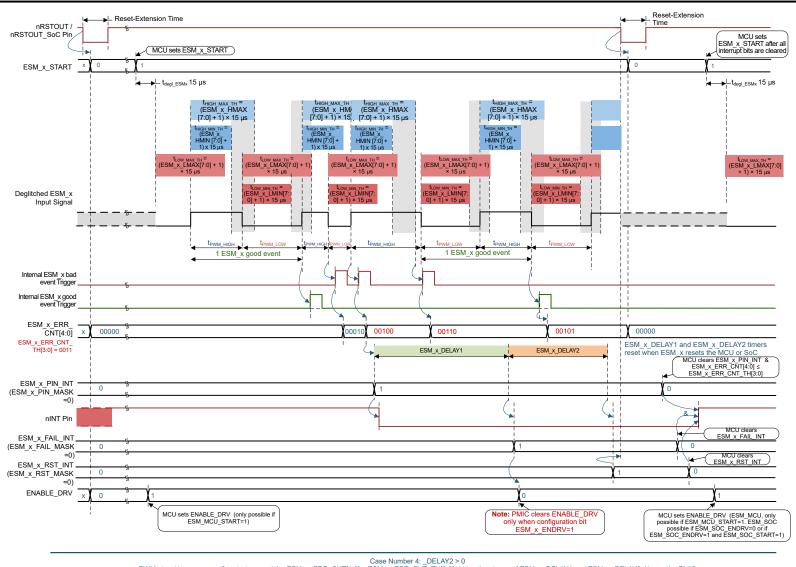

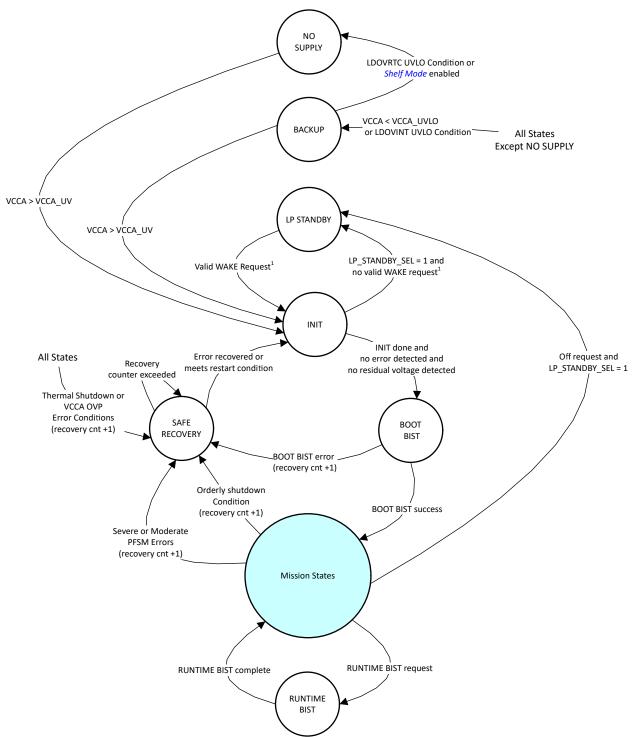

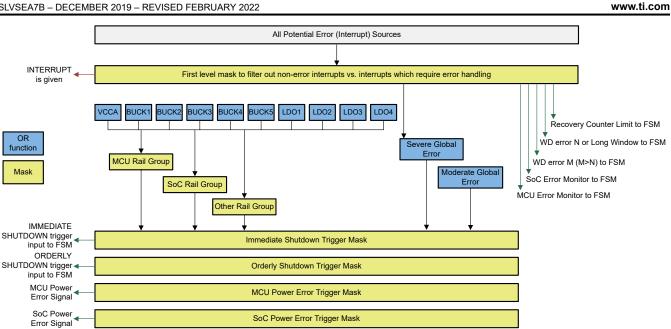

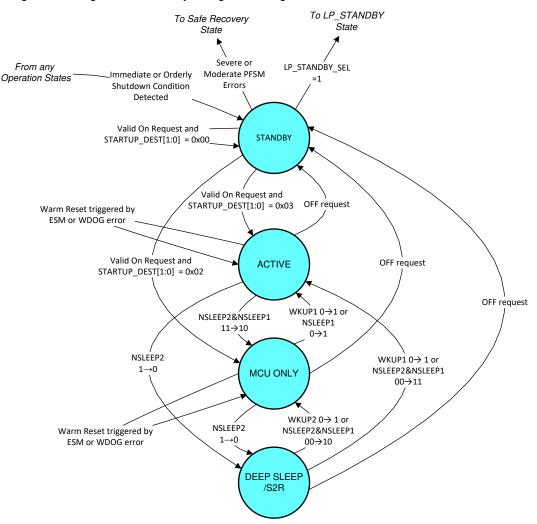

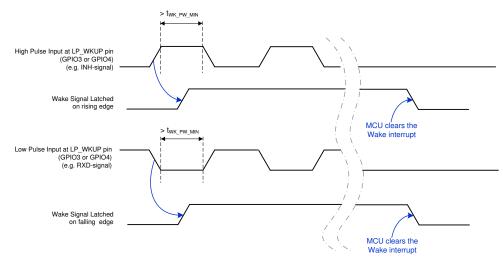

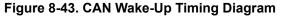

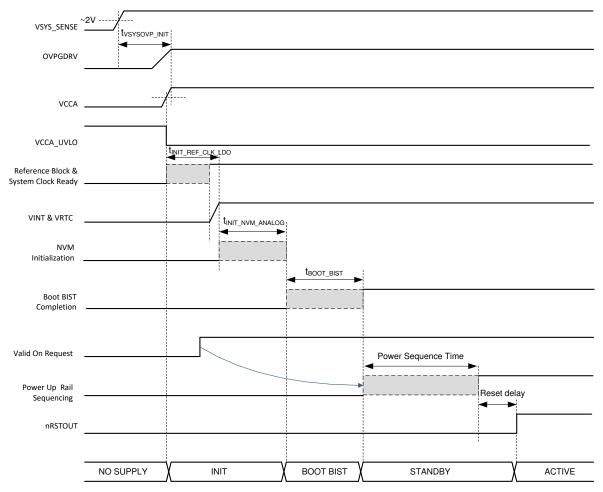

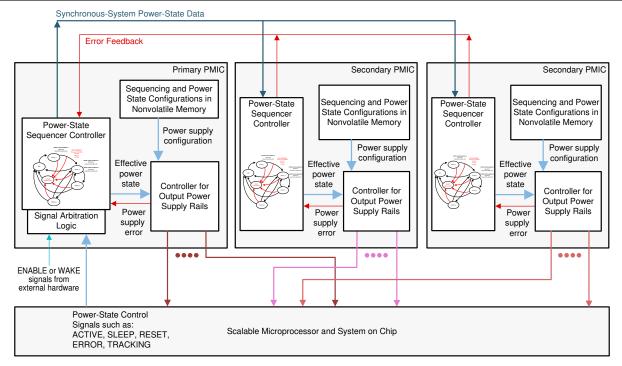

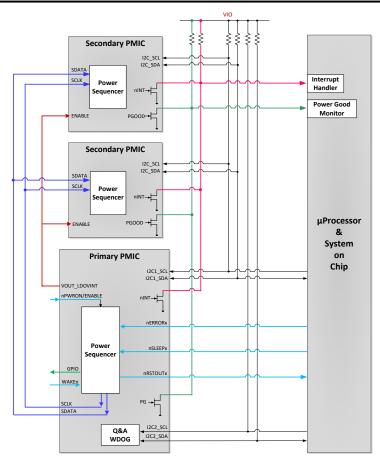

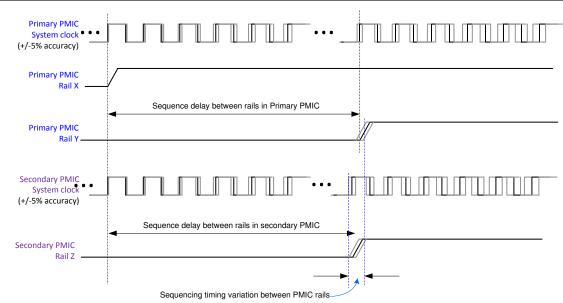

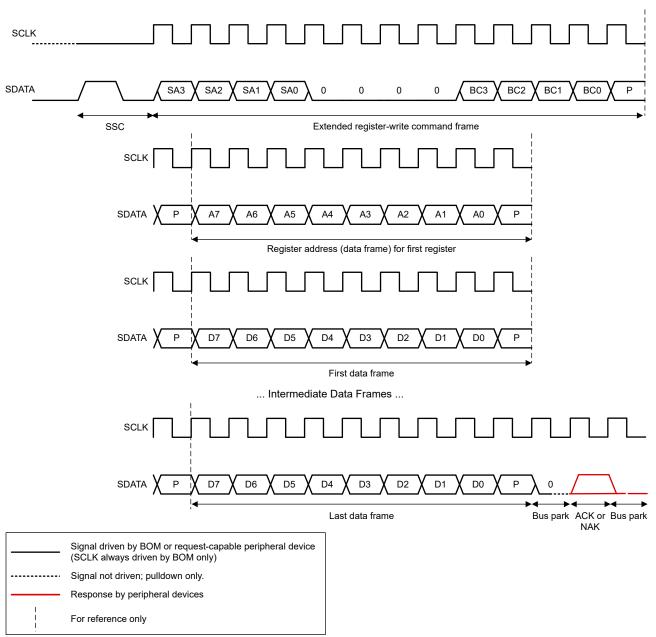

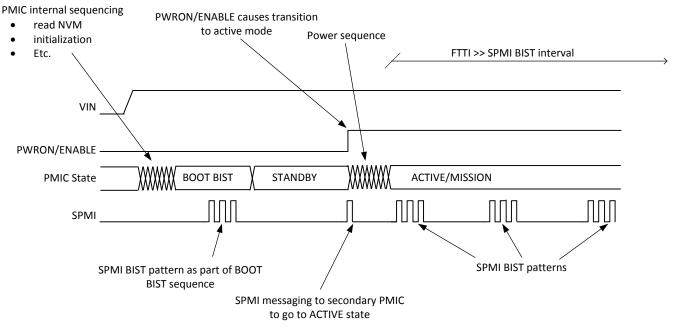

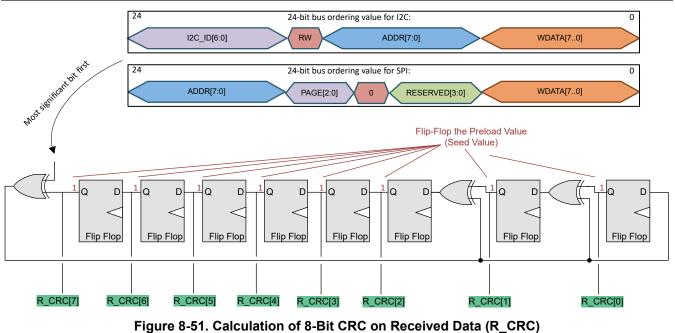

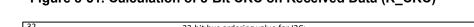

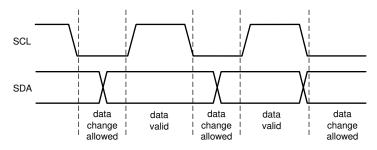

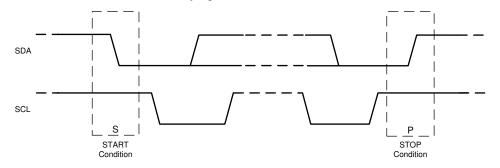

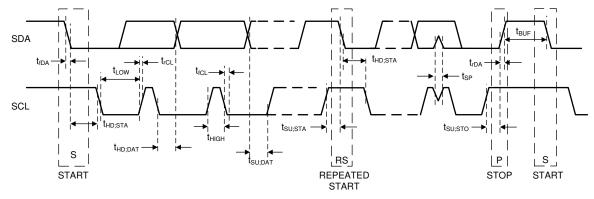

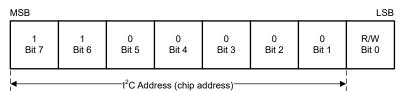

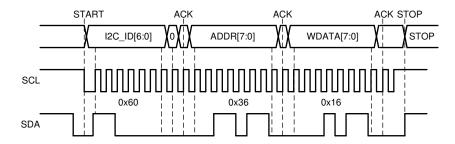

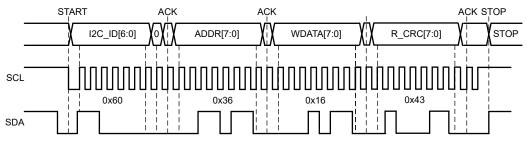

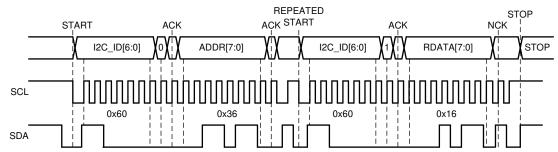

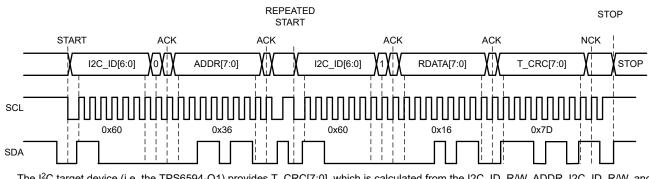

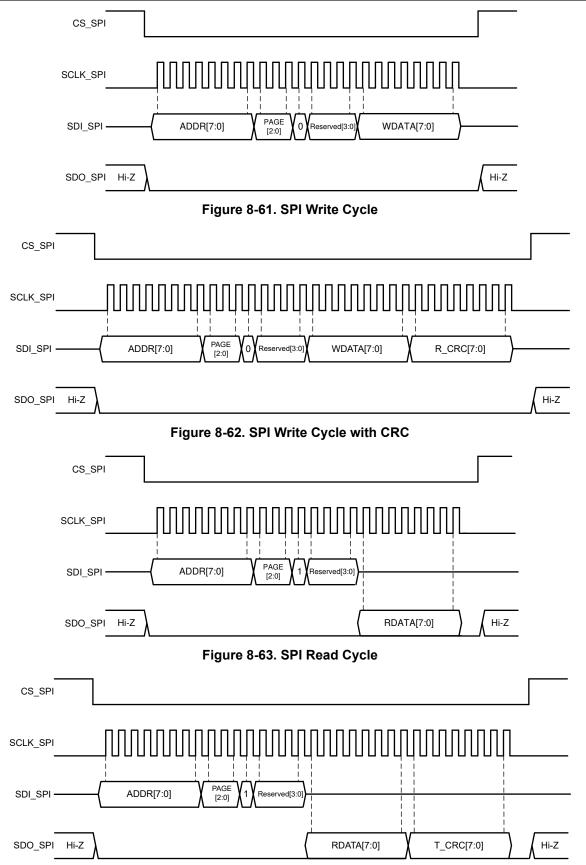

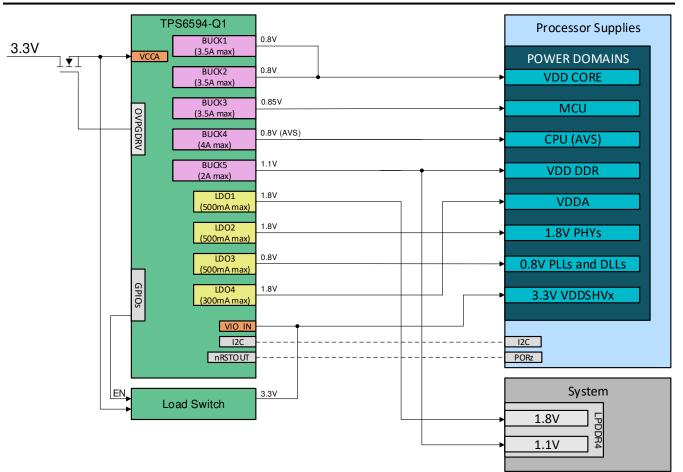

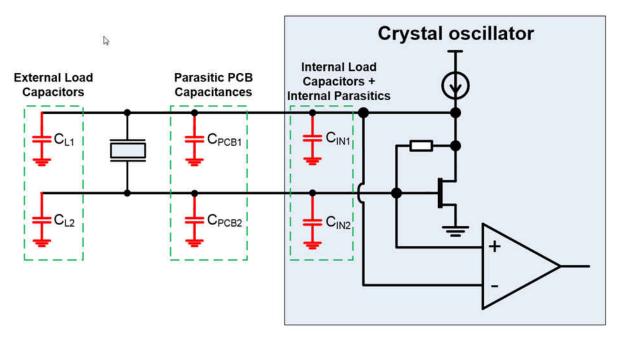

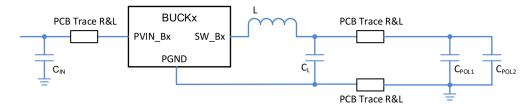

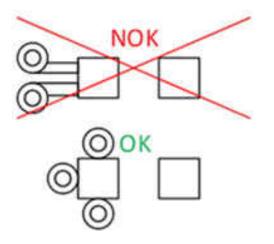

|       |     |     |                                                                                                                                                                                                             |                                                                                                                                                                                                             |                                                                                                                                        | 0                                                                                                                                      | Alternative function: CLK32KOUT, which is the output of the 32 KHz crystal oscillator clock.        | Floating                                                                                                     |          |  |  |  |  |  |  |     |                                                                                                                                                                                                             |                                   |