#### TPS7H5005-SEP, TPS7H5006-SEP, TPS7H5007-SEP, TPS7H5008-SEP SLVSGG1A - FEBRUARY 2022 - REVISED SEPTEMBER 2022

# TPS7H500x-SEP Radiation-Tolerant 2-MHz Current Mode **PWM Controllers in Space Enhanced Plastic**

#### 1 Features

- Radiation hardened:

- SEL, SEB, and SEGR immune to LET = 43 MeV-cm<sup>2</sup>/mg

- SET and SEFI characterized up to  $LET = 43 \text{ MeV-cm}^2/\text{mg}$

- TID assured for every wafer lot up to 50 krad(Si)

- Input voltage: 4 V to 14 V

- 0.613-V +0.7%/-1% voltage reference over temperature, radiation, and line and load

- Switching frequency from 100 kHz to 2 MHz

- External clock synchronization capability

- Synchronous rectification outputs

- TPS7H5005-SEP, TPS7H5006-SEP, TPS7H5007-SEP

- Adjustable dead time

- TPS7H5005-SEP, TPS7H5006-SEP

- · Adjustable leading edge blank time

- TPS7H5005-SEP, TPS7H5006-SEP, TPS7H5008-SEP

- · Configurable duty cycle limit

- TPS7H5005-SEP, TPS7H5006-SEP, TPS7H5007-SEP

- Adjustable slope compensation and soft start

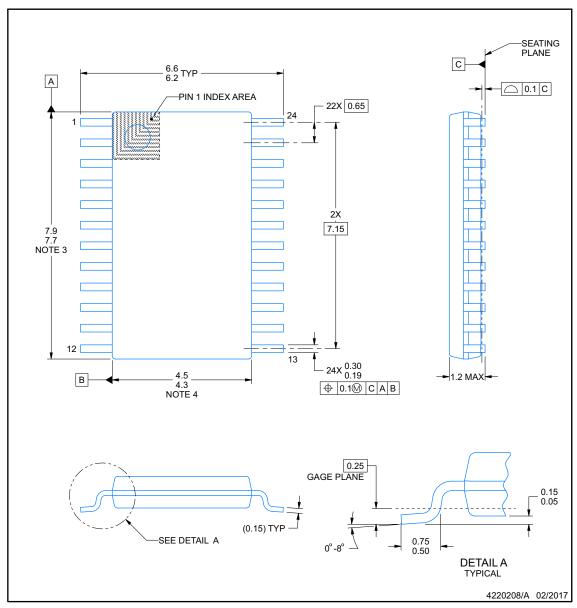

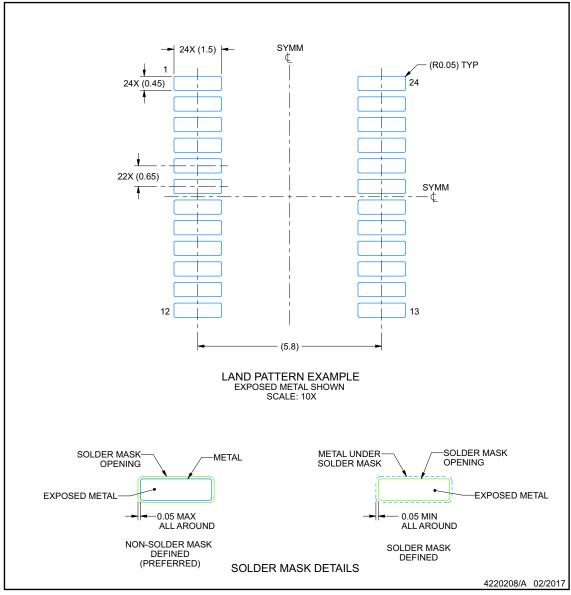

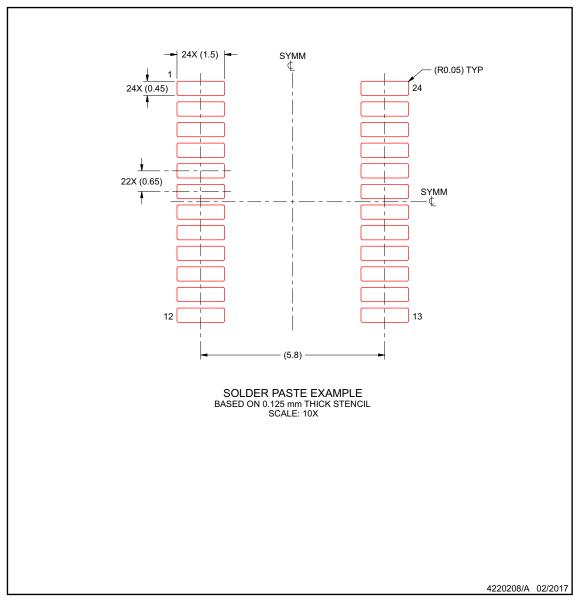

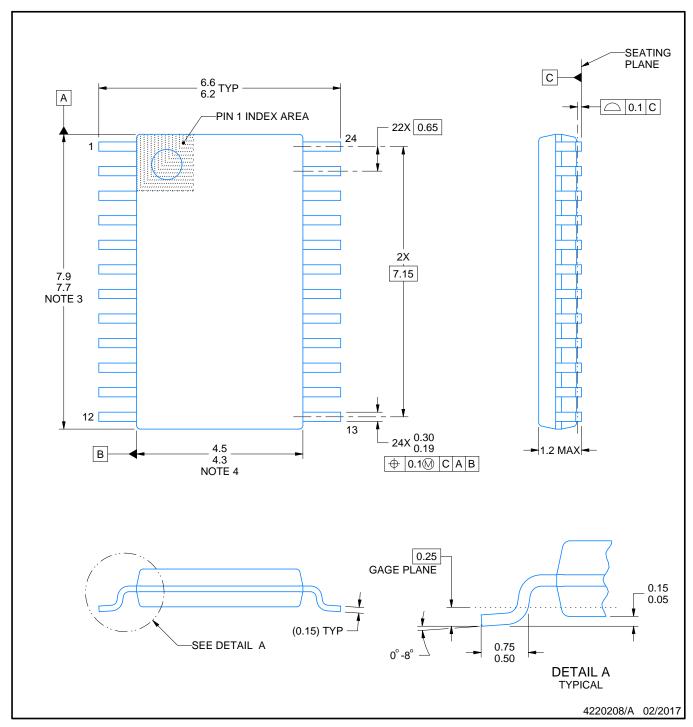

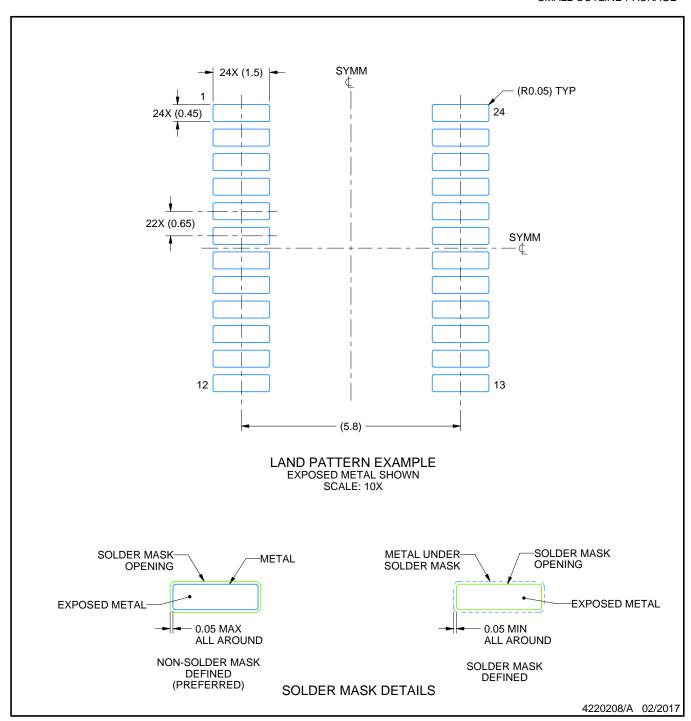

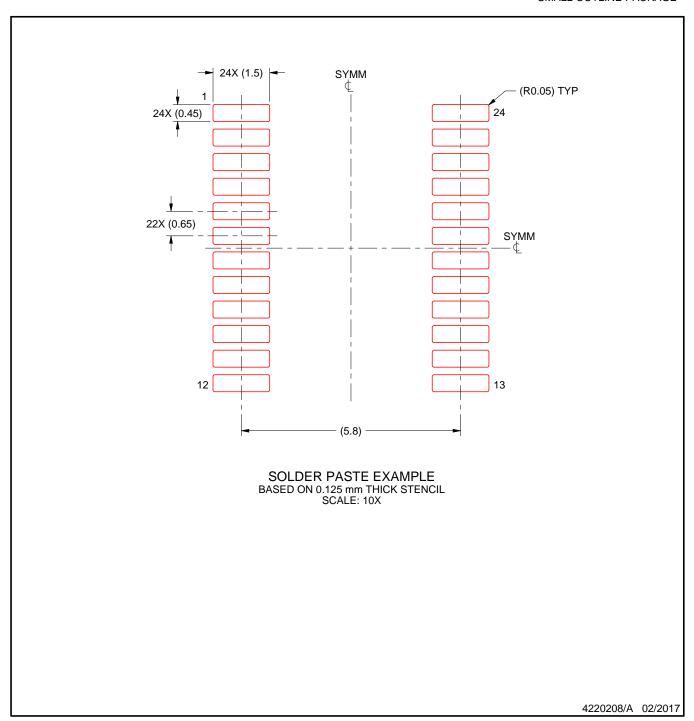

- 24-pin TSSOP package

- Space Enhanced Plastic

- Controlled baseline

- Au bondwire and NiPdAu lead finish

- Meets NASA ASTM E595 outgassing specification

- One fabrication, assembly, and test site

- Extended product life cycle

- Extended product change notification

- Product traceability

## 2 Applications

- Space satellite point of load supply for FPGAs, microcontrollers, data converters, and ASICs

- Communications payload

- Command and data handling

- Optical imaging payload

- Radar imaging payload

- Satellite electrical power system

## 3 Description

TPS7H500x-SEP series (consisting TPS7H5005-SEP, TPS7H5006-SEP, TPS7H5007-SEP, and TPS7H5008-SEP) is a family of highspeed, radiation-tolerant, PWM controllers in space enhanced plastic. The controllers provide a number of features that are beneficial for the design of DC-DC converter topologies intended for space applications. The controllers have a 0.613-V +0.7%/-1% accurate internal reference and configurable switching frequency up to 2 MHz. Each device offers programmable slope compensation and soft-start.

The TPS7H500x-SEP series can be driven using an external clock through the SYNC pin or by using the internal oscillator at a frequency programmed by the user. The controller family offers the user various options for switching outputs, synchronous rectification capability, dead time (fixed or configurable), leading edge blank time (fixed or configurable), and duty cycle limit. Each device in the TPS7H500x-SEP series has a 24-pin TSSOP package.

#### **Device Information**

| PART NUMBER <sup>(1)</sup> | GRADE            | PACKAGE                         |

|----------------------------|------------------|---------------------------------|

| TPS7H5005MPWTSEP           | 50-krad(Si) RLAT |                                 |

| TPS7H5006MPWTSEP           |                  | TSSOP (24)<br>4.40 mm × 7.80 mm |

| TPS7H5007MPWTSEP           |                  | Mass = $102.3 \text{ mg}^{(2)}$ |

| TPS7H5008MPWTSEP           |                  |                                 |

- For all available packages, see the orderable addendum at the end of the data sheet.

- Mass is accurate to ±10%.

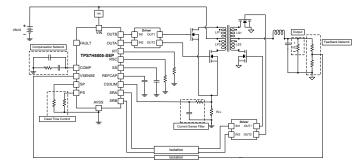

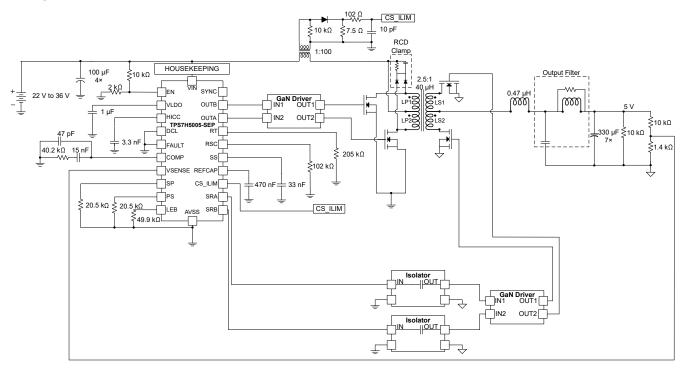

Typical Application for TPS7H5005-SEP

## **Table of Contents**

| 1 Features1                                     | 8.3 Feature Description                              | 30 |

|-------------------------------------------------|------------------------------------------------------|----|

| 2 Applications 1                                | 8.4 Device Functional Modes                          |    |

| 3 Description1                                  | 9 Application and Implementation                     |    |

| 4 Revision History2                             | 9.1 Application Information                          |    |

| 5 Device Comparison Table3                      | 9.2 Typical Application                              |    |

| 6 Pin Configuration and Functions4              | 10 Power Supply Recommendations                      |    |

| 7 Specifications7                               | 11 Layout                                            |    |

| 7.1 Absolute Maximum Ratings7                   | 11.1 Layout Guidelines                               | 60 |

| 7.2 ESD Ratings7                                | 11.2 Layout Example                                  |    |

| 7.3 Recommended Operating Conditions7           | 12 Device and Documentation Support                  | 62 |

| 7.4 Thermal Information7                        | 12.1 Documentation Support                           | 62 |

| 7.5 Electrical Characteristics: All Devices8    | 12.2 Receiving Notification of Documentation Updates | 62 |

| 7.6 Electrical Characteristics: TPS7H5005-SEP10 | 12.3 Support Resources                               | 62 |

| 7.7 Electrical Characteristics: TPS7H5006-SEP11 | 12.4 Trademarks                                      | 62 |

| 7.8 Electrical Characteristics: TPS7H5007-SEP11 | 12.5 Electrostatic Discharge Caution                 | 62 |

| 7.9 Electrical Characteristics: TPS7H5008-SEP12 | 12.6 Glossary                                        | 62 |

| 7.10 Typical Characteristics13                  | 13 Mechanical, Packaging, and Orderable              |    |

| 8 Detailed Description25                        | Information                                          | 63 |

| 8.1 Overview25                                  | 13.1 Mechanical Data                                 |    |

| 8.2 Functional Block Diagram26                  |                                                      |    |

|                                                 |                                                      |    |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Revision \* (February 2022) to Revision A (September 2022)Page• Changed device statuses from Advanced Information to Production Data1

# **5 Device Comparison Table**

## Table 5-1. TPS7H500x-SEP Device Comparison Table

| DEVICE        | PRIMARY OUTPUTS | SYNCHRONOUS<br>RECTIFIER<br>OUTPUTS | DEAD TIME<br>SETTING     | LEADING EDGE<br>BLANK TIME<br>SETTING | DUTY CYCLE LIMIT<br>OPTIONS |

|---------------|-----------------|-------------------------------------|--------------------------|---------------------------------------|-----------------------------|

| TPS7H5005-SEP | 2               | 2                                   | Resistor<br>programmable | Resistor<br>programmable              | 50%, 75%, 100%              |

| TPS7H5006-SEP | 1               | 1                                   | Resistor programmable    | Resistor programmable                 | 75%, 100%                   |

| TPS7H5007-SEP | 1               | 1                                   | Fixed (50-ns typical)    | Fixed (50-ns typical)                 | 75%, 100%                   |

| TPS7H5008-SEP | 2               | 0                                   | Not applicable           | Resistor programmable                 | 50%                         |

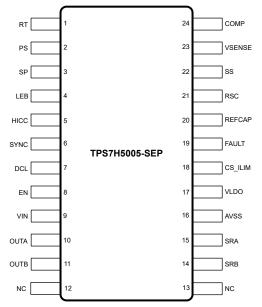

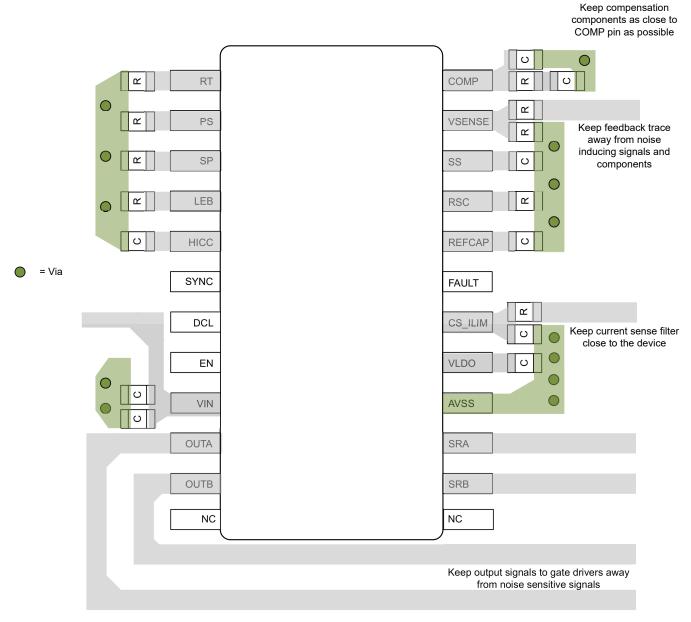

## **6 Pin Configuration and Functions**

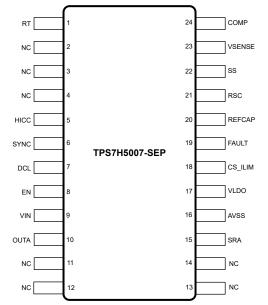

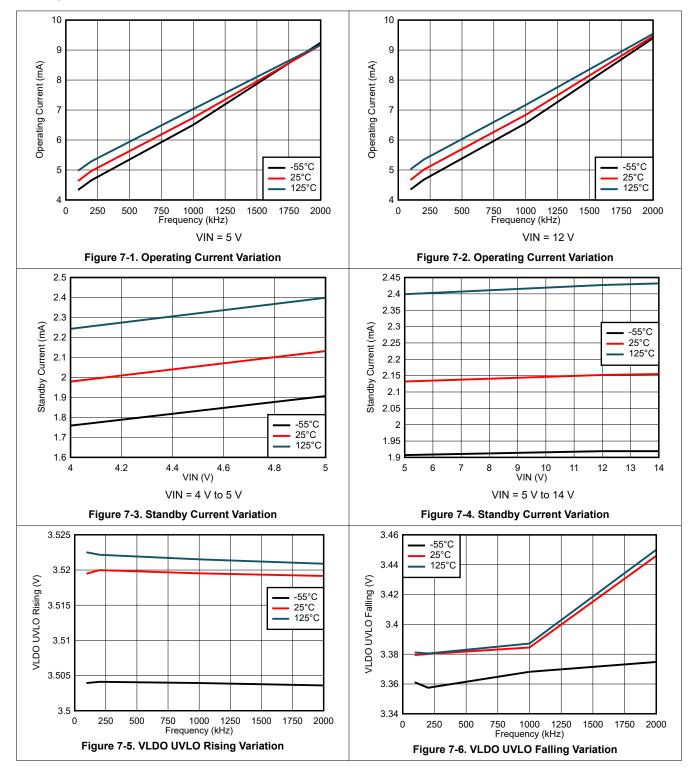

Figure 6-1. TPS7H5005-SEP PW Package 24-Pin TSSOP (Top View)

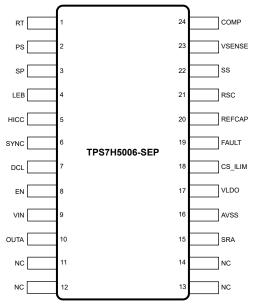

Figure 6-3. TPS7H5007-SEP PW Package 24-Pin TSSOP (Top View)

Figure 6-2. TPS7H5006-SEP PW Package 24-Pin TSSOP (Top View)

Figure 6-4. TPS7H5008-SEP PW Package 24-Pin TSSOP (Top View)

### **Table 6-1. Pin Functions**

|      | Table 6-1. Pin Functions PIN |                   |                   |                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|------|------------------------------|-------------------|-------------------|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME | TPS7H5005-<br>SEP            | TPS7H5006-<br>SEP | TPS7H5007-<br>SEP | TPS7H5008-<br>SEP | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| RT   | 1                            | 1                 | 1                 | 1                 | I/O | In internal oscillation mode, the RT pin must be populated with a resistor to AVSS. When the RT pin is floating, a 200-kHz to 4-MHz external clock is required at the SYNC pin. The frequency of the external clock must be twice the desired switching frequency.                                                                                                                                                             |  |  |

| PS   | 2                            | 2                 | _                 | _                 | I/O | Primary off to synchronous rectifier on dead-time set. Programmable through an external resistor to AVSS.                                                                                                                                                                                                                                                                                                                      |  |  |

| SP   | 3                            | 3                 | _                 | _                 | I/O | Synchronous rectifier off to primary on dead-time set. Programmable through an external resistor to AVSS.                                                                                                                                                                                                                                                                                                                      |  |  |

| LEB  | 4                            | 4                 | _                 | 4                 | I/O | Leading edge blank time set. Programmable through an external resistor to AVSS.                                                                                                                                                                                                                                                                                                                                                |  |  |

| HICC | 5                            | 5                 | 5                 | 5                 | I/O | Cycle-by-cycle current limit time delay and hiccup time setting. Delay time and hiccup time determined by capacitor from HICC to AVSS. Connecting this pin to AVSS disables hiccup mode.                                                                                                                                                                                                                                       |  |  |

| SYNC | 6                            | 6                 | 6                 | 6                 | I/O | When the RT pin is floating, SYNC is configured as an input for a 200-kHz to 4-MHz external clock. In this case, the external clock input gets inverted and the system clock will run at half the frequency of the external clock input. When the RT pin is populated with a resistor to AVSS, SYNC outputs a 200-kHz to 4-MHz clock signal at twice the device switching frequency in phase with the switching of the device. |  |  |

| DCL  | 7                            | 7                 | 7                 | 7                 | I/O | Duty cycle limit configurability. For TPS7H5005-SEP, connect to AVSS for 50% duty cycle limit, floating for 75%, and VLDO for 100%. For TPS7H5006-SEP and TPS7H5007-SEP, the DCL pin can be left floating or connected to VLDO to set the maximum duty cycle to 75% or 100%, respectively. For TPS7H5008-SEP, this pin must be connected to AVSS in order to obtain the 50% maximum duty cycle.                                |  |  |

| EN   | 8                            | 8                 | 8                 | 8                 | I   | Connecting the EN pin to the VLDO pin or external source greater than 0.6 V enables the device. In addition, input undervoltage lockout (UVLO) can be adjusted with two resistors.                                                                                                                                                                                                                                             |  |  |

| VIN  | 9                            | 9                 | 9                 | 9                 | ı   | Input supply to the device. Input voltage range is from 4 V to 14 V.                                                                                                                                                                                                                                                                                                                                                           |  |  |

| OUTA | 10                           | 10                | 10                | 10                | 0   | Primary switching output A.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| OUTB | 11                           | _                 | _                 | 11                | 0   | Primary switching output B. Active only when DCL = AVSS.                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| SRB  | 14                           | _                 | _                 | _                 | 0   | Synchronous rectifier output B. Active only when DCL = AVSS.                                                                                                                                                                                                                                                                                                                                                                   |  |  |

## **Table 6-1. Pin Functions (continued)**

|         |                   | PIN               |                            |                         |     |                                                                                                                                                                                                                                                                                                     |

|---------|-------------------|-------------------|----------------------------|-------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | TPS7H5005-<br>SEP | TPS7H5006-<br>SEP | TPS7H5007-<br>SEP          | TPS7H5008-<br>SEP       | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                         |

| SRA     | 15                | 15                | 15                         | _                       | 0   | Synchronous rectifier output A.                                                                                                                                                                                                                                                                     |

| AVSS    | 16                | 16                | 16                         | 16                      | _   | Ground of the device.                                                                                                                                                                                                                                                                               |

| VLDO    | 17                | 17                | 17                         | 17                      | 0   | Output of internal regulator. Requires at least 1-µF external capacitor to AVSS.                                                                                                                                                                                                                    |

| CS_ILIM | 18                | 18                | 18                         | 18                      | I/O | Current sense for PWM control and cycle-by-cycle overcurrent protection. An input voltage over 1.05 V on CS_ILIM will trigger an overcurrent in the PWM controller. The sensed waveform on CS_ILIM contains a 150-mV offset when compared to the COMP/2 voltage at the input of the PWM comparator. |

| FAULT   | 19                | 19                | 19                         | 19                      | ı   | Fault protection pin. When the rising threshold of the FAULT pin is exceeded, the outputs will stop switching. After the external voltage drops below the falling threshold, the device will restart after a set delay. Connect this pin to AVSS to disable FAULT.                                  |

| REFCAP  | 20                | 20                | 20                         | 20                      | 0   | 1.2-V internal reference. Requires a 470-nF external capacitor to AVSS.                                                                                                                                                                                                                             |

| RSC     | 21                | 21                | 21                         | 21                      | I/O | A resistor from RSC to AVSS sets the desired slope compensation.                                                                                                                                                                                                                                    |

| SS      | 22                | 22                | 22                         | 22                      | I/O | Soft start. An external capacitor connected to this pin sets the internal voltage reference rise time. The voltage on this pin overrides the internal reference. It can be used for tracking and sequencing.                                                                                        |

| VSENSE  | 23                | 23                | 23                         | 23                      | I   | Inverting input of the error amplifier.                                                                                                                                                                                                                                                             |

| COMP    | 24                | 24                | 24                         | 24                      | I/O | Error amplifier output. Connect frequency compensation to this pin.                                                                                                                                                                                                                                 |

| NC      | 12, 13            | 11, 12, 13, 14    | 2, 3, 4, 11, 12,<br>13, 14 | 2, 3, 12, 13, 14,<br>15 | _   | No connect. Can be connected to AVSS to avoid floating metal if desired.                                                                                                                                                                                                                            |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating temperature range (unless otherwise noted)(1)

|                  |                                              | MIN  | MAX | UNIT |

|------------------|----------------------------------------------|------|-----|------|

|                  | VIN                                          | -0.3 | 16  |      |

|                  | RT, VSENSE, SS, RSC, COMP, PS, SP, HICC, LEB | -0.3 | 3.3 |      |

| Input            | SYNC                                         | -0.3 | 7.5 | V    |

|                  | EN, FAULT                                    | -0.3 | 7.5 |      |

|                  | DCL, CS_ILIM                                 | -0.3 | 7.5 |      |

|                  | OUTA, OUTB, SRA and SRB                      | -0.3 | 7.5 |      |

| Output           | VLDO                                         | -0.3 | 7.5 | V    |

|                  | REFCAP                                       | -0.3 | 3.3 |      |

| TJ               | Junction temperature                         | -55  | 150 | °C   |

| T <sub>stg</sub> | Storage temperature                          | -65  | 150 | C    |

<sup>1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 7.2 ESD Ratings

|                                            |                         |                                                                                 | VALUE | UNIT |

|--------------------------------------------|-------------------------|---------------------------------------------------------------------------------|-------|------|

| V                                          | Clastrostatia disebarga | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>     | ±1000 | \/   |

| V <sub>(ESD)</sub> Electrostatic discharge | Electrostatic discharge | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002, all pins <sup>(2)</sup> | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating temperature range (unless otherwise noted)

|                   |                         | MIN         | NOM MAX | UNIT |

|-------------------|-------------------------|-------------|---------|------|

| VIN               | Supply voltage          | 4           | 14      | V    |

| SR <sub>VIN</sub> | Input voltage slew rate |             | 0.03    | V/µs |

| TJ                | Junction temperature    | <b>–</b> 55 | 125     | °C   |

#### 7.4 Thermal Information

|                               |                                              | TP7H500x-SEP |      |

|-------------------------------|----------------------------------------------|--------------|------|

| THERMAL METRIC <sup>(1)</sup> |                                              | TSSOP        | UNIT |

|                               |                                              | 24 PINS      |      |

| R <sub>θJA</sub>              | Junction-to-ambient thermal resistance       | 74.5         | °C/W |

| R <sub>θJB</sub>              | Junction-to-board thermal resistance         | 30.8         | °C/W |

| R <sub>θJC(top)</sub>         | Junction-to-case (top) thermal resistance    | 17.9         | °C/W |

| ΨЈТ                           | Junction-to-top characterization parameter   | 0.8          | °C/W |

| ΨЈВ                           | Junction-to-board characterization parameter | 30.3         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.5 Electrical Characteristics: All Devices

$T_J = -55^{\circ}C$  to 125°C, VIN = 4 V to 14 V (unless otherwise noted)

|                       | PARAMETER                                | TEST CONDITIONS                                                                       | MIN  | TYP   | MAX  | UNIT |  |

|-----------------------|------------------------------------------|---------------------------------------------------------------------------------------|------|-------|------|------|--|

| SUPPLY VOI            | LTAGES AND CURRENTS                      |                                                                                       |      |       |      |      |  |

| VIN                   | Operating input voltage                  |                                                                                       | 4    |       | 14   | V    |  |

|                       |                                          | f <sub>SW</sub> = 500 kHz, No load for OUTA,<br>OUTB, SRA, and SRB                    |      | 6.25  | 8    |      |  |

| IDD                   |                                          | f <sub>SW</sub> = 1 MHz, No load for OUTA,<br>OUTB, SRA, and SRB                      |      | 6.75  | 9.5  |      |  |

|                       | Operating supply current                 | f <sub>SW</sub> = 2 MHz, No load for OUTA, OUTB,<br>SRA, and SRB                      |      | 8.5   | 13.5 | mA   |  |

| טטו                   | Operating supply current                 | f <sub>SW</sub> = 500 kHz, C <sub>LOAD</sub> = 100 pF for<br>OUTA, OUTB, SRA, and SRB |      | 7.5   | 9.5  | ША   |  |

|                       |                                          | f <sub>SW</sub> = 1 MHz, C <sub>LOAD</sub> = 100 pF for OUTA, OUTB, SRA, and SRB      |      | 9     | 12   |      |  |

|                       |                                          | f <sub>SW</sub> = 2 MHz, C <sub>LOAD</sub> = 100 pF for OUTA, OUTB, SRA, and SRB      |      | 14    | 19.5 |      |  |

| $I_{DD(dis)}$         | Standby current                          | EN = 0 V                                                                              |      |       | 3    | mA   |  |

| VLDO                  | Internal linear regulator output voltage | 5 V ≤ VIN ≤ 14 V, f <sub>sw</sub> ≤ 1 MHz                                             | 4.75 | 5     | 5.2  | V    |  |

| VLDO                  | Internal linear regulator output voltage | 5 V ≤ VIN ≤ 14 V, f <sub>sw</sub> = 2 MHz                                             | 4.65 | 5     | 5.2  | V    |  |

| ENABLE AN             | D UNDERVOLTAGE LOCKOUT                   |                                                                                       |      |       | ,    |      |  |

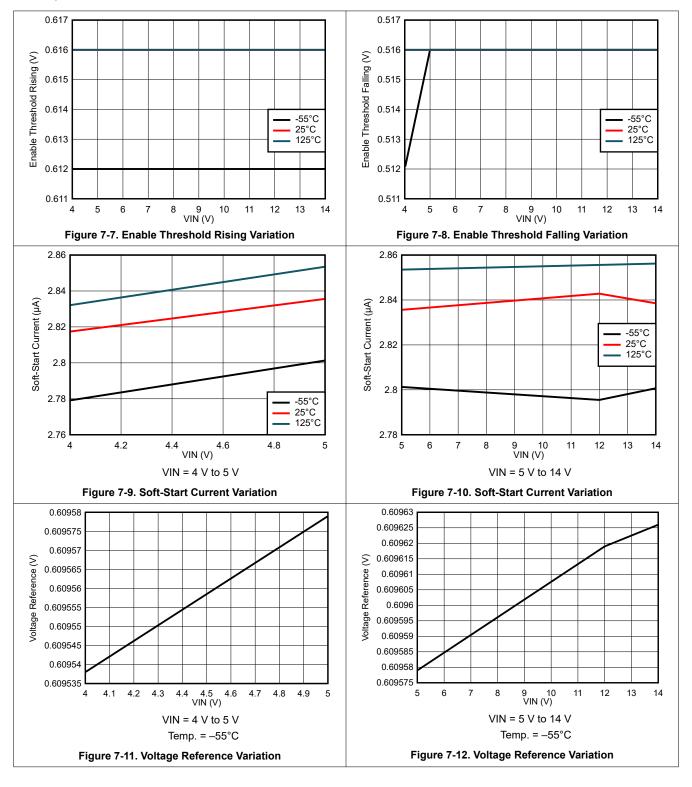

| V <sub>ENR</sub>      | EN threshold rising                      |                                                                                       | 0.57 | 0.6   | 0.65 | V    |  |

| V <sub>ENF</sub>      | EN threshold falling                     |                                                                                       | 0.47 | 0.5   | 0.55 | V    |  |

| V <sub>ENH</sub>      | EN hysteresis voltage                    |                                                                                       | 85   | 95    | 105  | mV   |  |

| I <sub>EN</sub>       | EN pin input leakage current             | VIN = 14 V, EN = 5 V                                                                  |      | 5     | 50   | nΑ   |  |

| VLDO <sub>UVLOR</sub> | VLDO UVLO rising                         |                                                                                       | 3.44 | 3.55  | 3.66 | V    |  |

| VLDO <sub>UVLOF</sub> | VLDO UVLO falling                        |                                                                                       | 3.29 | 3.4   | 3.51 | V    |  |

| VLDO <sub>UVLOH</sub> | VLDO UVLO hysteresis                     |                                                                                       | 115  | 135   | 160  | mV   |  |

| SOFT STAR             | r                                        |                                                                                       |      |       |      |      |  |

| I <sub>SS</sub>       | Soft-start current                       | SS = 0.3 V                                                                            | 1.98 | 2.7   | 3.32 | μΑ   |  |

| ERROR AME             | PLIFIER                                  |                                                                                       |      |       |      |      |  |

| EA <sub>gm</sub>      | Transconductance                         | -2 μA < I <sub>COMP</sub> < 2 μA, V <sub>(COMP)</sub> = 1 V                           | 1150 | 1800  | 2500 | μA/V |  |

| EA <sub>DC</sub>      | DC gain                                  | V <sub>SENSE</sub> = 0.6 V                                                            |      | 10000 |      | V/V  |  |

| EA <sub>ISRC</sub>    | Error amplifier source current           | V <sub>(COMP)</sub> = 1 V, 100-mV input overdrive                                     | 100  | ,     | 190  | μA   |  |

| EA <sub>ISNK</sub>    | Error amplifier sink current             | V <sub>(COMP)</sub> = 1 V, 100-mV input overdrive                                     | 100  |       | 190  | μA   |  |

| EA <sub>ro</sub>      | Error amplifier output resistance        |                                                                                       |      | 7     |      | МΩ   |  |

| EA <sub>OS</sub>      | Error amplifier input offset voltage     |                                                                                       | -2   |       | 2    | mV   |  |

| EA <sub>IB</sub>      | Error amplifier input bias current       |                                                                                       |      |       | 35   | nA   |  |

| EA <sub>BW</sub>      | Bandwidth                                |                                                                                       |      | 10    |      | MHz  |  |

| OSCILLATO             | R                                        |                                                                                       |      |       | ,    |      |  |

| 0)/10                 | OVALO in Laura Laura                     | VIN < 5 V                                                                             |      |       | 0.8  |      |  |

| SYNC <sub>IL</sub>    | SYNC in low-level                        | VIN ≥ 5 V                                                                             |      |       | 0.8  | V    |  |

| 0.410                 | OVAIO in high land                       | VIN < 5 V                                                                             | 3.5  |       |      |      |  |

| SYNC <sub>IH</sub>    | SYNC in high-level                       | VIN ≥ 5 V                                                                             | 3.5  |       |      | V    |  |

| F <sub>SYNC</sub>     | SYNC in frequency range                  |                                                                                       | 200  |       | 4000 | kHz  |  |

| D <sub>SYNC</sub>     | SYNC in duty cycle                       | Duty cycle of external clock                                                          | 40   |       | 60   | %    |  |

| SYNC <sub>RT</sub>    | SYNC out low-to-high rise time (10%/90%) | C <sub>LOAD</sub> = 25 pF                                                             |      | 6     | 15   | ns   |  |

## 7.5 Electrical Characteristics: All Devices (continued)

$T_1 = -55^{\circ}C$  to 125°C. VIN = 4 V to 14 V (unless otherwise noted)

|                              | PARAMETER                                    | TEST CONDITIONS                                                                                                                                                                                                                                    | MIN   | TYP   | MAX   | UNIT  |

|------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| SYNC <sub>FT</sub>           | SYNC out high-to-low fall time (10%/ 90%)    | C <sub>LOAD</sub> = 25 pF                                                                                                                                                                                                                          |       | 6     | 17    | ns    |

| SYNC <sub>OL</sub>           | SYNC out low level                           | I <sub>OL</sub> = 10 mA                                                                                                                                                                                                                            |       |       | 500   | mV    |

| VLDO –<br>SYNC <sub>OH</sub> | SYNC out high level (1)                      | I <sub>OH</sub> = 10 mA                                                                                                                                                                                                                            |       |       | 0.5   | V     |

| EXT <sub>DT</sub>            | Externally set frequency detection time      | RT = Open, f = 200 kHz                                                                                                                                                                                                                             |       |       | 20    | μs    |

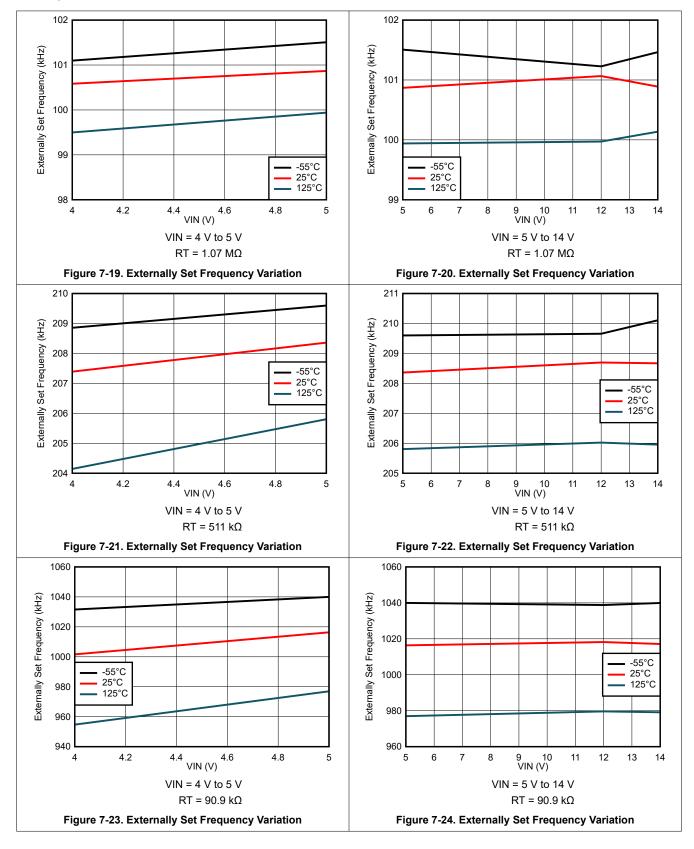

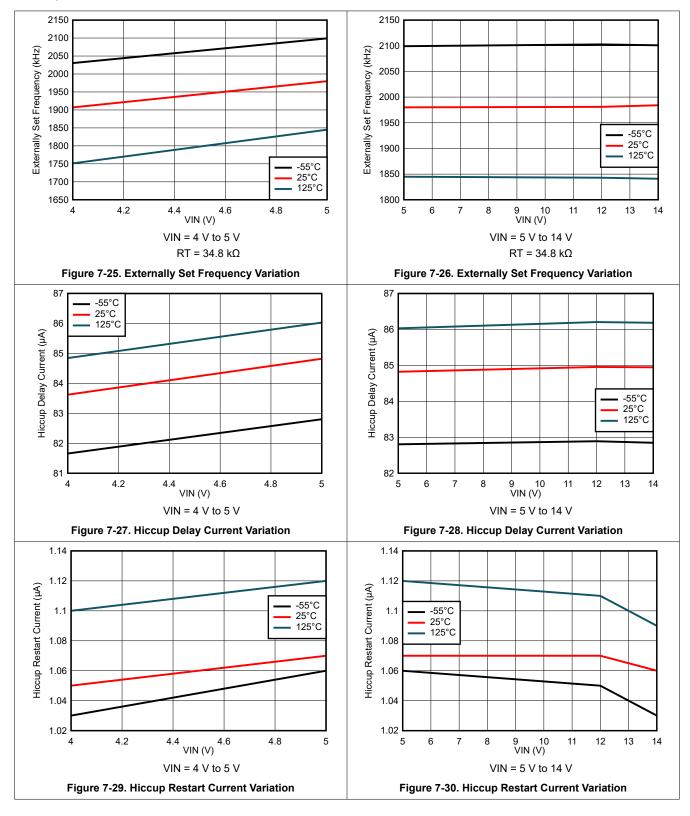

|                              |                                              | RT = 1.07 MΩ                                                                                                                                                                                                                                       | 95    | 105   | 115   |       |

| EC/A/                        | Futamath, ast for more                       | RT = 511 kΩ                                                                                                                                                                                                                                        | 190   | 210   | 230   | 1411= |

| FSW <sub>EXT</sub>           | Externally set frequency                     | RT = 90.9 kΩ                                                                                                                                                                                                                                       | 900   | 1000  | 1100  | kHz   |

|                              |                                              | RT = 34.8 kΩ                                                                                                                                                                                                                                       | 1700  | 2000  | 2300  |       |

| VOLTAGE I                    | REFERENCE                                    |                                                                                                                                                                                                                                                    |       | ·     |       |       |

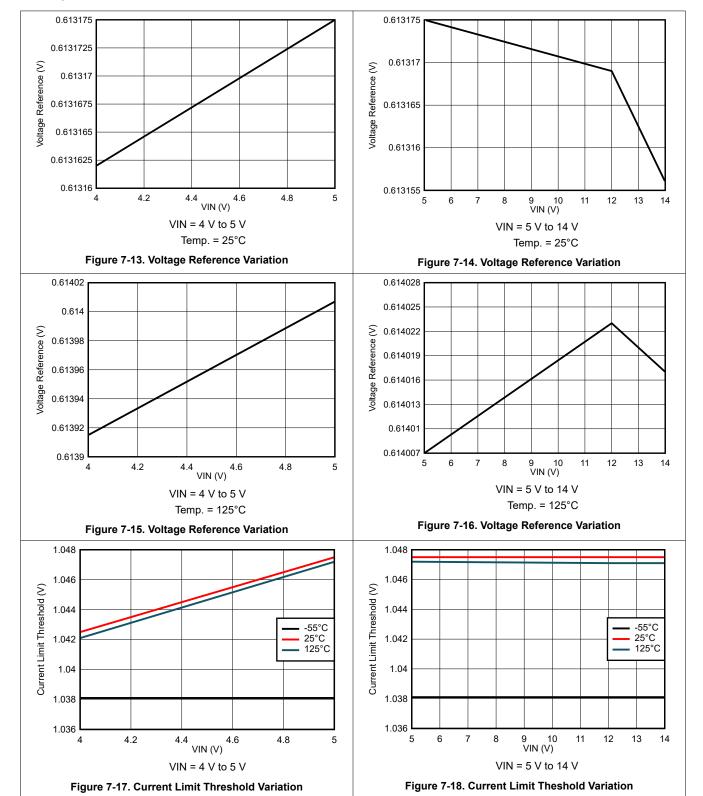

|                              | Internal voltage reference initial tolerance | Measured at COMP, 25°C                                                                                                                                                                                                                             | 0.609 | 0.613 | 0.615 |       |

| VREF                         | Internal voltage reference                   | Measured at COMP, -55°C                                                                                                                                                                                                                            | 0.607 | 0.609 | 0.612 | V     |

|                              | Internal voltage reference                   | Measured at COMP, 125°C                                                                                                                                                                                                                            | 0.611 | 0.614 | 0.617 |       |

| REFCAP                       | REFCAP voltage                               | REFCAP = 470 nF                                                                                                                                                                                                                                    | 1.213 | 1.225 | 1.237 | V     |

| CURRENT                      | SENSE, CURRENT LIMIT AND HICCUP              |                                                                                                                                                                                                                                                    |       |       |       |       |

| CCSR                         | COMP to CS_ILIM ratio                        |                                                                                                                                                                                                                                                    | 2.00  | 2.06  | 2.12  |       |

| V <sub>CS_ILIM</sub>         | Current limit (overcurrent) threshold        |                                                                                                                                                                                                                                                    |       | 1.05  | 1.09  | V     |

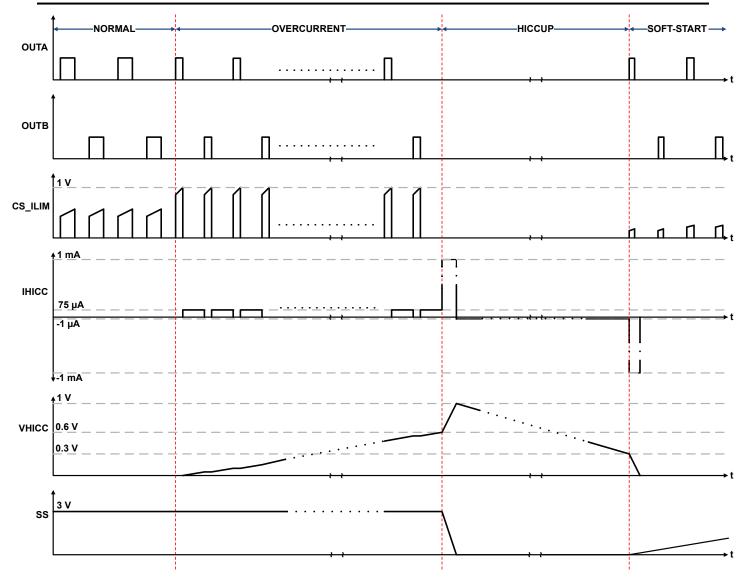

| I <sub>HICC_DEL</sub>        | Hiccup delay current                         | $\label{eq:cs_ilim} \begin{split} &\text{CS\_ILIM} = 1.3 \text{ V, COMP} = 3 \text{ V,} \\ &\text{VSENSE} = \text{REFCAP/2 V, C}_{\text{HICC}} = 3 \text{ nF,} \\ &\text{LEB} = 49.9 \text{ k}\Omega, f_{\text{sw}} = 100 \text{ kHz} \end{split}$ |       | 80    |       | μΑ    |

| I <sub>HICC_RST</sub>        | Hiccup restart current                       |                                                                                                                                                                                                                                                    |       | 1     |       | μA    |

| V <sub>HICC_PU</sub>         | Hiccup pull-up threshold                     |                                                                                                                                                                                                                                                    |       | 1.0   |       | V     |

| V <sub>HICC_SD</sub>         | Hiccup shut-down threshold                   |                                                                                                                                                                                                                                                    |       | 0.6   |       | V     |

| V <sub>HICC_RST</sub>        | Hiccup restart threshold                     |                                                                                                                                                                                                                                                    |       | 0.3   |       | V     |

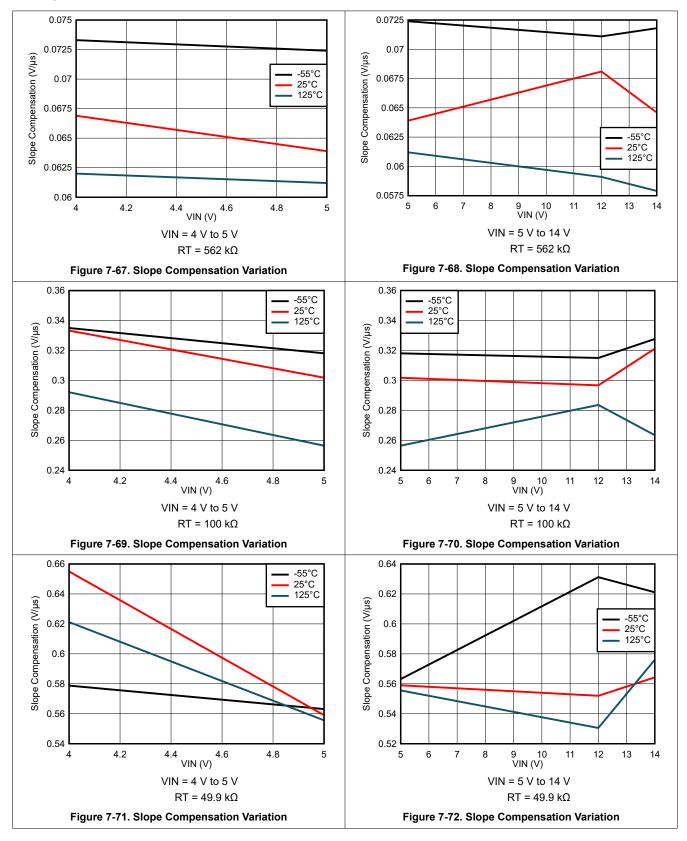

| SLOPE CO                     | MPENSATION                                   |                                                                                                                                                                                                                                                    |       |       |       |       |

|                              |                                              | $f_{SW}$ = 100 kHz, RSC = 1.18 M $\Omega$                                                                                                                                                                                                          |       | 0.033 |       |       |

|                              | Slope compensation                           | $f_{SW}$ = 200 kHz, RSC = 562 k $\Omega$                                                                                                                                                                                                           |       | 0.066 |       | V/µs  |

|                              | Slope compensation                           | $f_{SW} = 1000 \text{ kHz}, RSC = 100 \text{ k}\Omega$                                                                                                                                                                                             |       | 0.333 |       | ν/μ3  |

|                              |                                              | $f_{SW}$ = 2000 kHz, RSC = 49.9 k $\Omega$                                                                                                                                                                                                         |       | 0.666 |       |       |

| FAULT                        |                                              |                                                                                                                                                                                                                                                    |       |       |       |       |

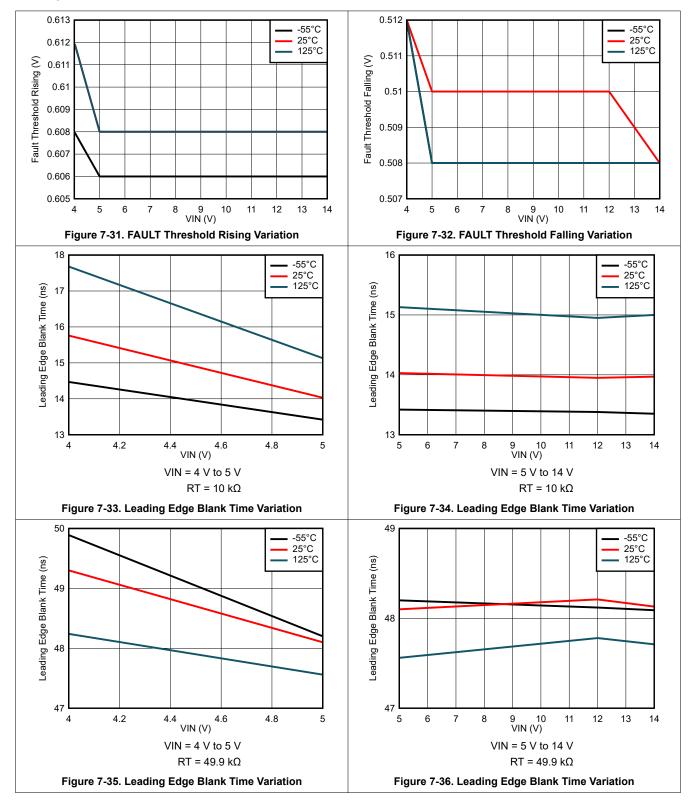

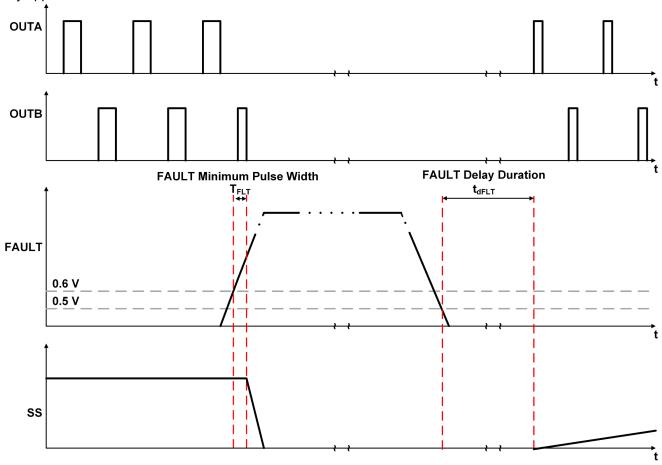

| $V_{FLTR}$                   | FLT threshold rising                         |                                                                                                                                                                                                                                                    | 0.57  | 0.6   | 0.65  | V     |

| $V_{FLTF}$                   | FLT threshold falling                        |                                                                                                                                                                                                                                                    | 0.47  | 0.5   | 0.55  | V     |

| $V_{FLTH}$                   | FLT hysteresis voltage                       |                                                                                                                                                                                                                                                    | 90    | 100   | 110   | mV    |

| T <sub>FLT</sub>             | FLT minimum pulse width                      | V <sub>FLT</sub> = 1 V                                                                                                                                                                                                                             | 0.4   |       | 1.4   | μs    |

|                              |                                              | f <sub>sw</sub> = 100 kHz                                                                                                                                                                                                                          | 140   | 152   | 169   |       |

| t <sub>DFLT</sub>            | FLT delay duration                           | f <sub>sw</sub> = 200 kHz                                                                                                                                                                                                                          | 66    | 78    | 86    | μs    |

| -DELI                        | ,,                                           | f <sub>sw</sub> = 1 MHz                                                                                                                                                                                                                            | 14    | 17    | 21    | μo    |

|                              |                                              | f <sub>sw</sub> = 2 MHz                                                                                                                                                                                                                            | 7     | 11    | 14    |       |

| THERMAL                      | SHUTDOWN                                     |                                                                                                                                                                                                                                                    |       |       |       |       |

|                              | Thermal shutdown                             |                                                                                                                                                                                                                                                    | 165   | 175   | 185   | °C    |

|                              | Thermal shutdown hysteresis                  |                                                                                                                                                                                                                                                    | 10    | 15    | 20    | °C    |

| PRIMARY A                    | AND SYNCHRONOUS RECTIFIER OUTPL              | JTS                                                                                                                                                                                                                                                |       |       |       |       |

|                              | Low-level threshold                          | I <sub>SINK</sub> = 10 mA                                                                                                                                                                                                                          |       | 0.5   |       | V     |

|                              | High-level threshold                         | I <sub>SOURCE</sub> = 10 mA                                                                                                                                                                                                                        | -     | 4.5   |       | V     |

## 7.5 Electrical Characteristics: All Devices (continued)

$T_J = -55$ °C to 125°C, VIN = 4 V to 14 V (unless otherwise noted)

| PARAMETER           |                          | TEST CONDITIONS                                              | MIN | TYP | MAX | UNIT |

|---------------------|--------------------------|--------------------------------------------------------------|-----|-----|-----|------|

|                     | Rise/fall time           | $R_{LOAD}$ = 50 k $\Omega$ , $C_{LOAD}$ = 100 pF, 10% to 90% |     | 10  | 17  | ns   |

| R <sub>SRC_P</sub>  | Output source resistance | I <sub>OUT</sub> = 20 mA, 5 V ≤ VIN ≤ 14 V                   |     | 15  |     | Ω    |

| R <sub>SINK_P</sub> | Output sink resistance   | I <sub>OUT</sub> = 20 mA, 5 V ≤ VIN ≤ 14 V                   |     | 15  |     | Ω    |

<sup>(1)</sup> Bench verified. Not tested in production.

#### 7.6 Electrical Characteristics: TPS7H5005-SEP

$T_{.I}$  = -55°C to 125°C, VIN = 4 V to 14 V (unless otherwise noted)

|                  | PARAMETER                             | TEST CONDITIONS                                                                                                                                          | MIN | TYP | MAX | UNIT |

|------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| MINIMUM          | ON-TIME AND DEAD TIME                 |                                                                                                                                                          |     |     | •   |      |

| t <sub>MIN</sub> | Minimum on-time                       | LEB = 10 kΩ, 5 V ≤ VIN ≤ 14 V                                                                                                                            |     |     | 85  | ns   |

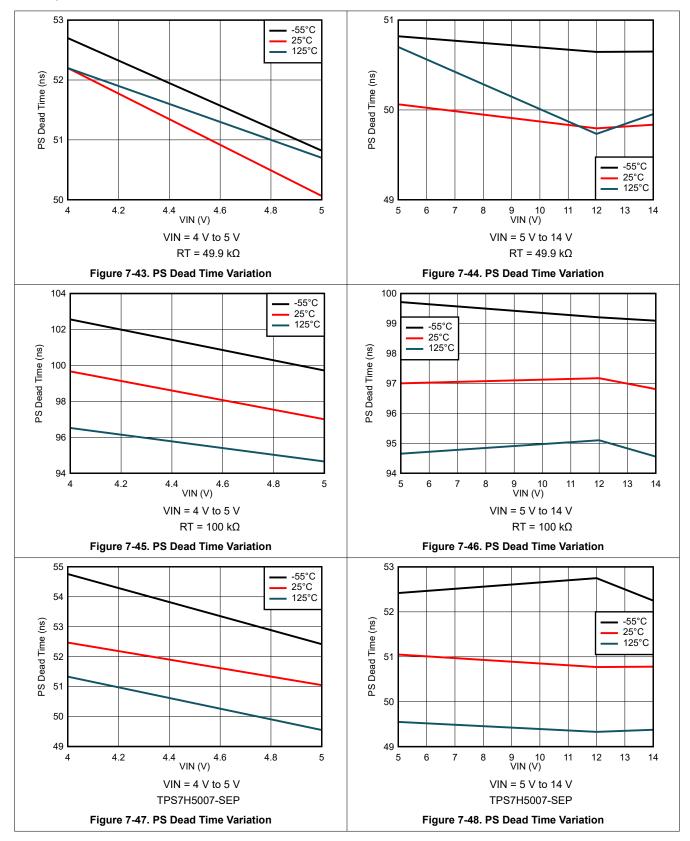

| TD <sub>PS</sub> | Primary off to secondary on dead time | PS = floating, 5 V ≤ VIN ≤ 14 V, 90% of OUTx falling to 10% of SRx rising, OUTx and SRx floating                                                         | 5   | 8   | 11  |      |

|                  |                                       | PS = $49.9 \text{ k}\Omega$ , $5 \text{ V} \le \text{VIN} \le 14 \text{ V}$ , $90\%$ of OUTx falling to $10\%$ of SRx rising, OUTx and SRx floating      | 43  | 50  | 55  | ns   |

|                  |                                       | PS = 107 k $\Omega$ , 5 V $\leq$ VIN $\leq$ 14 V, 90% of OUTx falling to 10% of SRx rising, OUTx and SRx floating                                        | 85  | 100 | 110 |      |

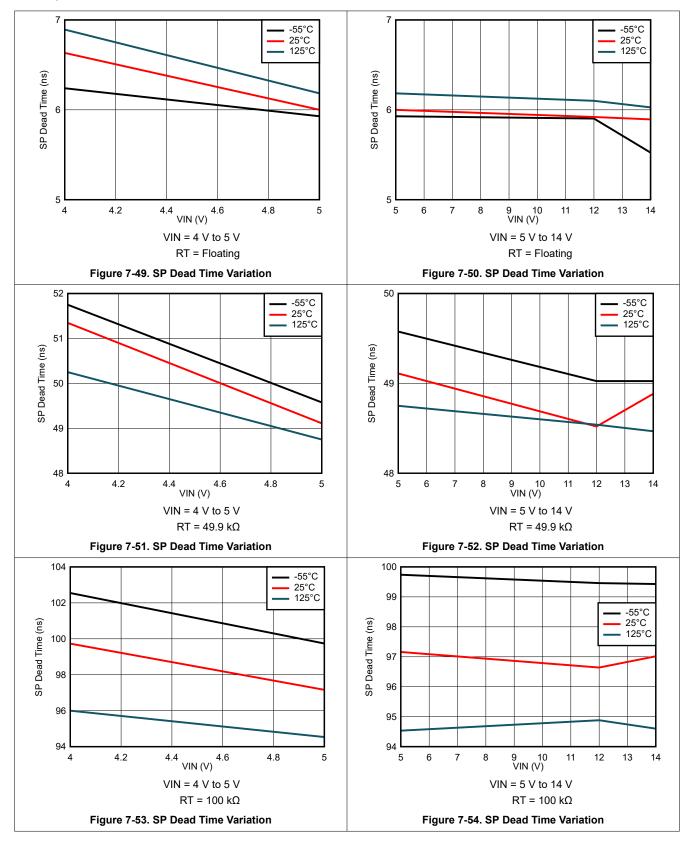

| $TD_SP$          | Secondary off to primary on dead time | SP = floating, 5 V ≤ VIN ≤ 14 V, 90% of SRx falling to 10% of OUTx rising, OUTx and SRx floating                                                         | 5   | 8   | 11  |      |

|                  |                                       | SP = $49.9 \text{ k}\Omega$ , $5 \text{ V} \le \text{VIN} \le 14 \text{ V}$ , $90\%$ of SRx falling to $10\%$ of OUTx rising edge, OUTx and SRx floating | 43  | 50  | 55  | ns   |

|                  |                                       | SP = 107 k $\Omega$ , 5 V $\leq$ VIN $\leq$ 14 V, 90% of SRx falling to 10% of OUTx rising, OUTx and SRx floating                                        | 85  | 100 | 110 |      |

| LEADING          | EDGE BLANK TIME AND DUTY CYCLE        |                                                                                                                                                          |     |     | '   |      |

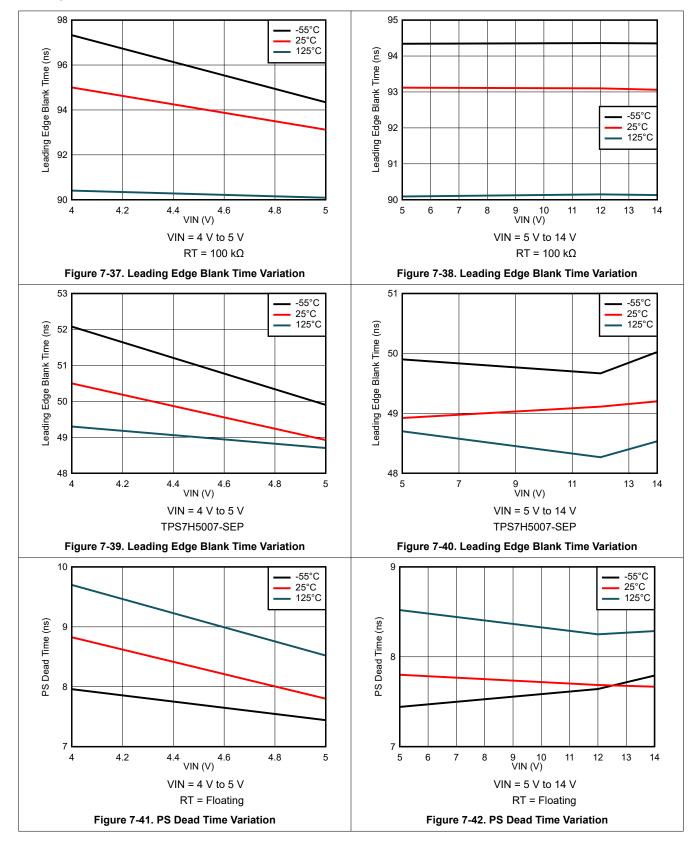

| T <sub>LEB</sub> | Leading edge blank time               | LEB = 10 kΩ, 5 V ≤ VIN ≤ 14 V                                                                                                                            | 12  | 15  | 19  |      |

|                  |                                       | LEB = 49.9 kΩ, 5 V ≤ VIN ≤ 14 V                                                                                                                          | 45  | 50  | 55  | ns   |

|                  |                                       | LEB = 110 kΩ, 5 V ≤ VIN ≤ 14 V                                                                                                                           | 85  | 100 | 110 |      |

| D <sub>MAX</sub> | Maximum duty cycle                    | DCL = AVSS                                                                                                                                               | 45  | 48  | 50  |      |

|                  |                                       | DCL = floating, clock duty cycle = 50%                                                                                                                   | 70  | 75  | 80  | %    |

|                  |                                       | DCL = VLDO                                                                                                                                               |     |     | 100 |      |

### 7.7 Electrical Characteristics: TPS7H5006-SEP

$T_J = -55$ °C to 125°C, VIN = 4 V to 14 V (unless otherwise noted)

|                  | PARAMETER                             | TEST CONDITIONS                                                                                                                                     | MIN | TYP | MAX | UNIT |

|------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| MINIMUM          | ON-TIME AND DEAD TIME                 |                                                                                                                                                     |     |     |     |      |

| t <sub>MIN</sub> | Minimum on-time                       | LEB = 10 kΩ, 5 V ≤ VIN ≤ 14 V                                                                                                                       |     |     | 85  | ns   |

| TD <sub>PS</sub> | Primary off to secondary on dead time | PS = floating, 5 V ≤ VIN ≤ 14 V, 90% of OUTx falling to 10% of SRx rising, OUTx and SRx floating                                                    | 5   | 8   | 11  |      |

|                  |                                       | PS = $49.9 \text{ k}\Omega$ , $5 \text{ V} \le \text{VIN} \le 14 \text{ V}$ , $90\%$ of OUTx falling to $10\%$ of SRx rising, OUTx and SRx floating | 43  | 50  | 55  | ns   |

|                  |                                       | PS = 107 k $\Omega$ , 5 V $\leq$ VIN $\leq$ 14 V, 90% of OUTx falling to 10% of SRx rising, OUTx and SRx floating                                   | 85  | 100 | 110 |      |

| $TD_SP$          | Secondary off to primary on dead time | SP = floating, 5 V ≤ VIN ≤ 14 V, 90% of SRx falling to 10% of OUTx rising, OUTx and SRx floating                                                    | 5   | 8   | 11  |      |

|                  |                                       | SP = 49.9 kΩ, 5 V ≤ VIN ≤ 14 V, 90% of SRx falling to 10% of OUTx rising edge, OUTx and SRx floating                                                | 43  | 50  | 55  | ns   |

|                  |                                       | SP = 107 k $\Omega$ , 5 V $\leq$ VIN $\leq$ 14 V, 90% of SRx falling to 10% of OUTx rising, OUTx and SRx floating                                   | 85  | 100 | 110 |      |

| LEADING          | EDGE BLANK TIME AND DUTY CYCLE        |                                                                                                                                                     |     |     | '   |      |

| T <sub>LEB</sub> | Leading edge blank time               | LEB = 10 kΩ, 5 V ≤ VIN ≤ 14 V                                                                                                                       | 12  | 15  | 19  |      |

|                  |                                       | LEB = 49.9 kΩ, 5 V ≤ VIN ≤ 14 V                                                                                                                     | 45  | 50  | 55  | ns   |

|                  |                                       | LEB = 110 kΩ, 5 V ≤ VIN ≤ 14 V                                                                                                                      | 85  | 100 | 110 |      |

| D <sub>MAX</sub> | Maximum duty cycle                    | DCL = floating, clock duty cycle = 50%                                                                                                              | 70  | 75  | 80  | %    |

|                  |                                       | DCL = VLDO                                                                                                                                          |     |     | 100 | %    |

### 7.8 Electrical Characteristics: TPS7H5007-SEP

$T_J = -55$ °C to 125°C, VIN = 4 V to 14 V (unless otherwise noted)

|                                        | PARAMETER                             | TEST CONDITIONS                                                                              | MIN | TYP | MAX | UNIT |  |

|----------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------|-----|-----|-----|------|--|

| MINIMUM ON-TIME AND DEAD TIME          |                                       |                                                                                              |     |     |     |      |  |

| t <sub>MIN</sub>                       | Minimum on-time                       | 5 V ≤ VIN ≤ 14 V                                                                             |     |     | 115 | ns   |  |

| TD <sub>PS</sub>                       | Primary off to secondary on dead time | 5 V ≤ VIN ≤ 14 V, 90% of OUTx falling to 10% of SRx rising, OUTx and SRx floating            | 40  | 50  | 60  | ns   |  |

| TD <sub>SP</sub>                       | Secondary off to primary on dead time | 5 V ≤ VIN ≤ 14 V, 90% of SRx falling<br>to 10% of OUTx rising edge, OUTx and<br>SRx floating | 40  | 50  | 60  | ns   |  |

| LEADING EDGE BLANK TIME AND DUTY CYCLE |                                       |                                                                                              |     |     |     |      |  |

| T <sub>LEB</sub>                       | Leading edge blank time               | 5 V ≤ VIN ≤ 14 V                                                                             | 40  | 50  | 60  | ns   |  |

| D                                      | Maximum duty cycle                    | DCL = floating, clock duty cycle = 50%                                                       | 70  | 75  | 80  | %    |  |

| D <sub>MAX</sub>                       |                                       | DCL = VLDO                                                                                   |     |     | 100 | 70   |  |

## 7.9 Electrical Characteristics: TPS7H5008-SEP

$T_{J} = -55^{\circ}C$  to 125°C, VIN = 4 V to 14 V (unless otherwise noted)

|                                        | PARAMETER               | TEST CONDITIONS                 | MIN | TYP | MAX | UNIT |  |  |

|----------------------------------------|-------------------------|---------------------------------|-----|-----|-----|------|--|--|

| MINIMUM ON-TIME                        |                         |                                 |     |     |     |      |  |  |

| t <sub>MIN</sub>                       | Minimum on-time         | LEB = 10 kΩ, 5 V ≤ VIN ≤ 14 V   |     |     | 85  | ns   |  |  |

| LEADING EDGE BLANK TIME AND DUTY CYCLE |                         |                                 |     |     |     |      |  |  |

|                                        | Leading edge blank time | LEB = 10 kΩ, 5 V ≤ VIN ≤ 14 V   | 12  | 15  | 19  |      |  |  |

| T <sub>LEB</sub>                       |                         | LEB = 49.9 kΩ, 5 V ≤ VIN ≤ 14 V | 45  | 50  | 55  | ns   |  |  |

|                                        |                         | LEB = 110 kΩ, 5 V ≤ VIN ≤ 14 V  | 85  | 100 | 110 |      |  |  |

| D <sub>MAX</sub>                       | Maximum duty cycle      | DCL = AVSS                      | 45  | 48  | 50  | %    |  |  |

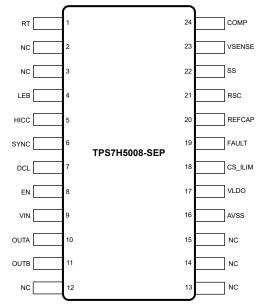

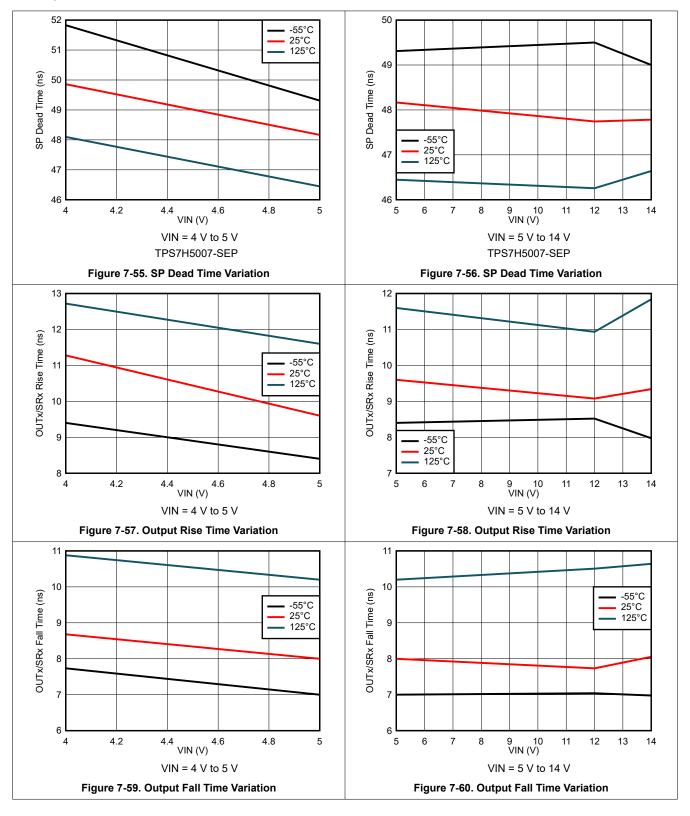

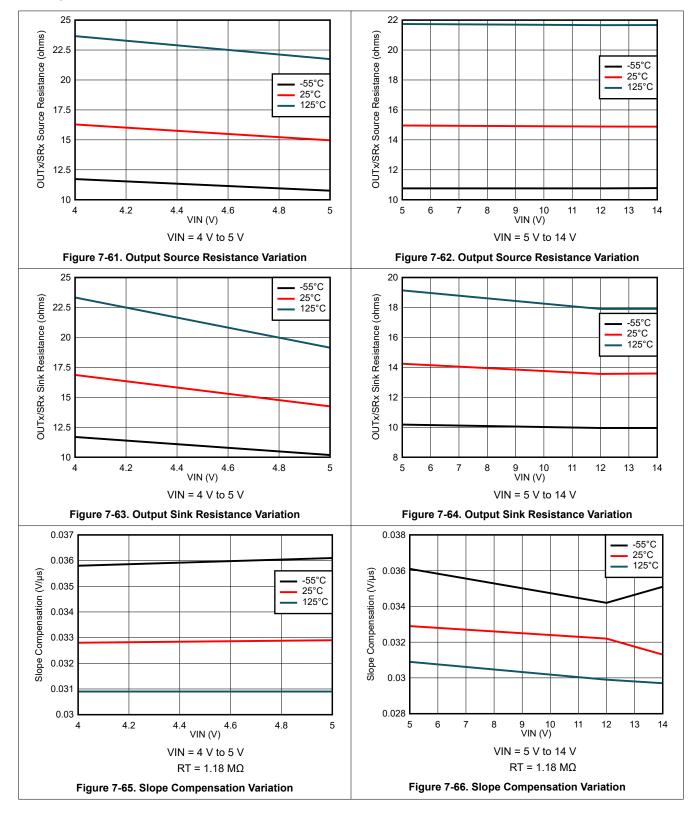

### 7.10 Typical Characteristics

## 8 Detailed Description

#### 8.1 Overview

The TPS7H500x-SEP series is a family of radiation-tolerant PWM controllers in space enhanced plastic. Each controller features a voltage reference of 0.613 V with accuracy of +0.7%/–1%. The switching frequency is configurable from 100 kHz to 2 MHz, with external clock synchronization capability. The series consists of the full-featured device TPS7H5005-SEP, as well as the three additional controllers TPS7H5006-SEP, TPS7H5007-SEP, and TPS7H5008-SEP.

The TPS7H5005-SEP is a radiation-tolerant, current mode, dual output PWM controller optimized for silicon (Si) and gallium nitride (GaN) based DC-DC converters in space applications. The switching frequency of the TPS7H5005-SEP can be configured from 100 kHz to 2 MHz while still maintaining a very low current consumption, which makes it ideal for fully exploiting the area reduction and high efficiency benefits of GaN based DC-DC converters. The device features integrated synchronous rectifier control outputs and dead-time programmability in order to target high efficiency and high performance topologies. In addition, the TPS7H5005-SEP supports single-ended converter topologies by providing the user flexibility to control the maximum duty cycle. The 0.613-V +0.7%/–1% accurate internal reference allows design of high-current buck converters for FPGA core voltages.

The TPS7H5006-SEP is a single output radiation-tolerant PWM controller that supports buck applications and single ended isolated topologies. The controller contains an integrated synchronous rectification output. Optimized for GaN power semiconductor based applications, the controller has configurable dead time and configurable leading edge blank time. The controller can be configured for maximum duty cycle of 75% or 100%. As such, the DCL pin can be left floating or connected to VLDO. Connection of the DCL pin to AVSS is not permissible for this device.

The TPS7H5007-SEP is also a single output radiation-tolerant PWM controller that contains an integrated synchronous rectification output. The dead time and leading edge blank time are fixed at 50 ns for this device. The controller can be configured for maximum duty cycle of 75% or 100%. As such, the DCL pin can be left floating or connected to VLDO. Connection of the DCL pin to AVSS is not permissible for this device.

The TPS7H5008-SEP is a dual output radiation-tolerant PWM controller suited for usage in non-synchronous push-pull and full-bridge topologies. The controller has configurable leading edge blank time. The maximum duty cycle for this device is 50% and is attained by connecting the DCL pin to AVSS.

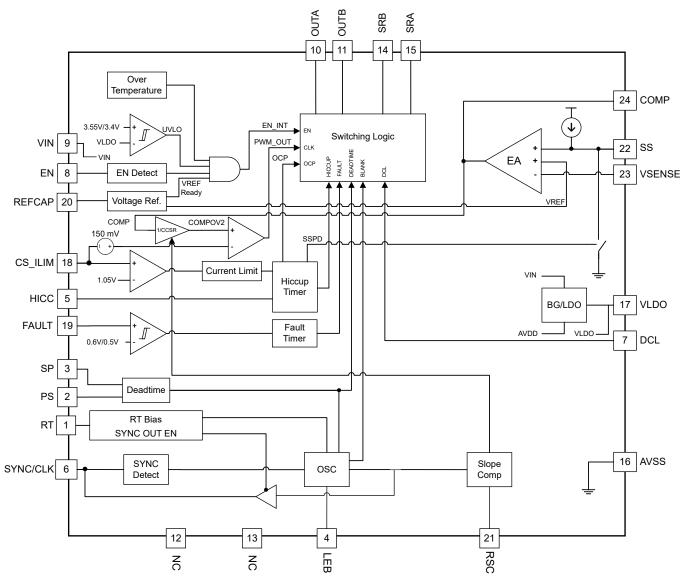

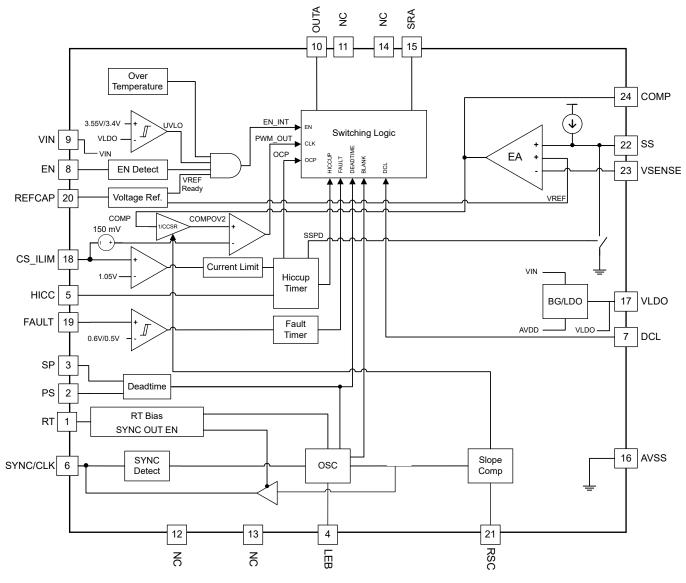

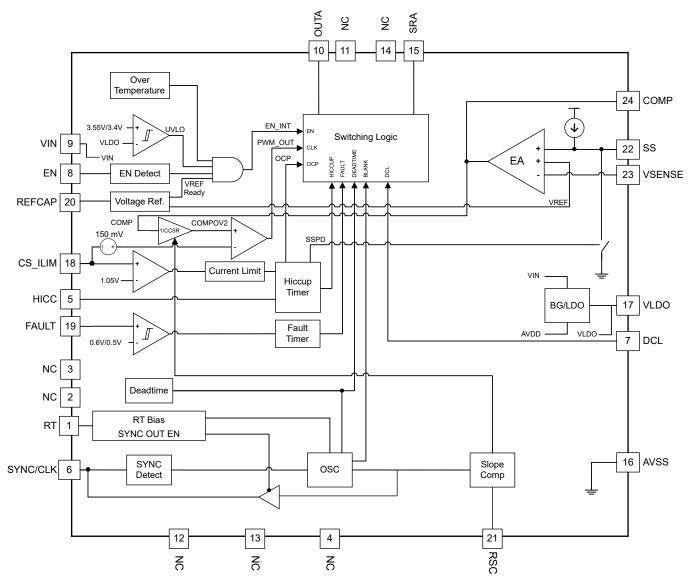

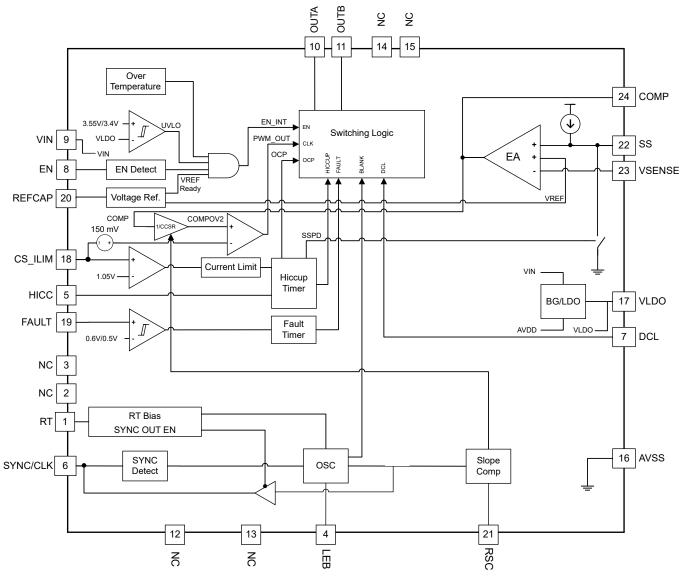

### 8.2 Functional Block Diagram

Figure 8-1. TPS7H5005-SEP Functional Block Diagram

Figure 8-2. TPS7H5006-SEP Functional Block Diagram

Figure 8-3. TPS7H5007-SEP Functional Block Diagram

Figure 8-4. TPS7H5008-SEP Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 VIN and VLDO

During steady state operation, the input voltage of the TPS7H500x-SEP must be between 4 V and 14 V. A minimum bypass capacitance of at least 0.1  $\mu$ F is needed between VIN and AVSS. The input bypass capacitors should be placed as close to the controller as possible.

The voltage applied at VIN serves as the input for the internal regulator that generates the VLDO voltage (5 V). At input voltages less than 5 V, the VLDO voltage will follow the voltage at VIN. Recommended capacitance for VLDO is 1  $\mu$ F. The EN and/or DCL pin can be tied to VLDO, but otherwise it is recommended to not externally load this pin due to limited output current capability.

A voltage divider connected between VIN and the EN pin can adjust the input voltage UVLO appropriately.

#### 8.3.2 Start-Up

Before the primary outputs of the controller will start switching, the following conditions must be met:

- VLDO exceeds the rising UVLO threshold of 3.55 V (typical)

- The internal 0.613 V reference voltage is available

- The enable signal EN is above the rising voltage threshold of 0.6 V (typical)

- The FAULT pin voltage is below the rising voltage threshold of 0.6 V (typical)

- The device junction temperature is below the thermal shutdown threshold of 175°C (typical)

Once all of the aforementioned conditions are satisfied, the soft-start process will be initiated.

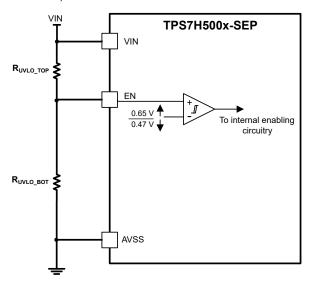

#### 8.3.3 Enable and Undervoltage Lockout (UVLO)

There are several methods to enable the TPS7H500x-SEP through the EN pin. The pin can be tied directly to VLDO, which would allow for the device to be enabled as soon as the voltage on VLDO surpasses the rising edge voltage threshold of the EN pin. The pin can also be driven with an externally generated signal or a compatible PGOOD signal for instances in which sequencing is desired. Lastly, two resistors can be used to program the controller to enable when VIN surpasses a user determined threshold, as shown in Figure 8-5. The two resistors are configured as a divider, with one between VIN and EN and the other between EN and AVSS.

Figure 8-5. Enable Pin Configuration Using Two External Resistors

Use Equation 1 to calculate the value for  $R_{UVLO\_TOP}$  for a chosen value of  $R_{UVLO\_BOT}$  based on the desired maximum start-up voltage for the device. With these selected resistors, Equation  $\frac{1}{2}$  is used to determine the minimum start-up voltage.

$$R_{\text{UVLO \_TOP}} = R_{\text{UVLO \_BOT}} \times \left( \frac{V_{\text{START ,MAX}}}{V_{\text{EN \_RISING \_MAX}}} - 1 \right)$$

(1)

$$V_{\text{START,MIN}} = V_{\text{EN\_RISING\_MIN}} \times \left(\frac{R_{\text{UVLO\_TOP}}}{R_{\text{UVLO\_BOT}}} + 1\right)$$

(2)

In the two-resistor configuration of Figure 8-5, the controller also shuts down due to undervoltage lockout when the input voltage falls below a particular threshold. This is due to the hysteresis of the EN pin. In order to determine the voltages at which shutdown is expected to occur, use Equation 3 and Equation 4.

$$V_{\text{STOP,MAX}} = V_{\text{EN_FALLING_MAX}} \times \left(\frac{R_{\text{UVLO\_TOP}}}{R_{\text{UVLO\_BOT}}} + 1\right)$$

(3)

$$V_{\text{STOP,MIN}} = V_{\text{EN\_FALLING\_MIN}} \times \left(\frac{R_{\text{UVLO\_TOP}}}{R_{\text{UVLO\_BOT}}} + 1\right)$$

(4)

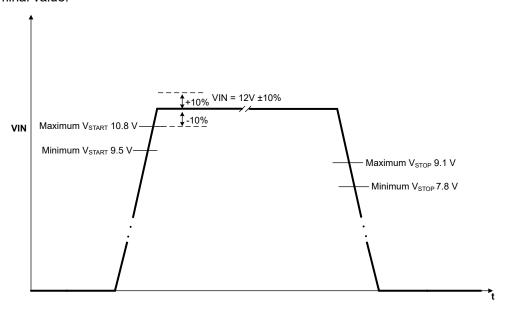

It is important to take care when selecting the values for  $R_{UVLO\_TOP}$  and  $R_{UVLO\_BOT}$ . It is recommended to optimize the selection of these resistors for start-up in order to ensure proper operation. The UVLO value must be approximately 75% or less of the input voltage in order to ensure that the device turns on as expected under all circumstances. Setting the UVLO any higher may cause issues with the turn-on of the device. Figure 8-6 shows the expected start-up and UVLO voltages on a 12-V rail where the maximum start-up voltage is 90% of the nominal input voltage. In this instance, a turn-off will occur when the input voltage falls to between 75% and 65% of its nominal value.

Figure 8-6. Start-Up and UVLO Values for Two-Resistor Configuration With VIN = 12 V

#### 8.3.4 Voltage Reference

Each device generates an internal 1.23-V bandgap reference that is utilized throughout the various control logic blocks. This is the voltage present on the REFCAP pin during steady state operation. This voltage is divided down to 0.613 V to produce the reference for the error amplifier. The error amplifier reference is measured at the COMP pin to account for offsets in the error amplifier and maintains regulation within +0.7%/–1% across line, load, temperature, and total ionizing dose (TID) as shown in Section 7. This tight reference tolerance allows for the user to design a highly accurate power converter. A 470-nF capacitor to ground is required at the REFCAP pin for proper electrical operation as well as to ensure robust SET performance of the device.

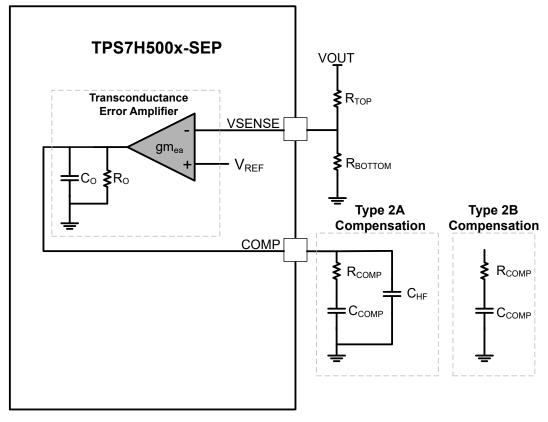

#### 8.3.5 Error Amplifier

Each TPS7H500x-SEP controller uses a transconductance error amplifier. The error amplifier compares the VSENSE pin voltage to the lower of the SS pin voltage or the internal 0.613-V voltage reference. The transconductance of the error amplifier is 1800  $\mu$ A/V during normal operation. The frequency compensation network is connected between COMP pin and AVSS. The error amplifier DC gain is typically 10,000 V/V.

#### 8.3.6 Output Voltage Programming

The output voltage of the power converter is set by using a resistor divider from  $V_{OUT}$  of the converter to the VSENSE pin. The output voltage must be divided down to nominal voltage reference of 0.613 V. Equation 5 can be used to select  $R_{BOTTOM}$ .

$$R_{BOTTOM} = \frac{V_{REF}}{V_{OUT} - V_{REF}} \times R_{TOP}$$

(5)

#### where:

- V<sub>REF</sub> is 0.613 V (typical)

- V<sub>OUT</sub> is the desired output voltage

- $R_{TOP}$  is the value of the top resistor, selected by the user (i.e. 10 k $\Omega$ )

The recommendation is to use high tolerance resistors (1% or less) for  $R_{BOTTOM}$  and  $R_{TOP}$  for improved output voltage setpoint accuracy.

#### 8.3.7 Soft Start (SS)

The soft-start circuit increases the output voltage of the converter gradually until the steady-state programmed output is reached. During soft start, the error amplifier uses the voltage on the soft-start pin as its reference until the SS pin voltage rises above  $V_{REF}$ . Once the voltage at SS pin is above  $V_{REF}$ , the soft-start period is complete. Note that the voltage at SS pin will continue to rise and once it reaches 1 V, the synchronous rectifier outputs of the controller will become active.

A capacitor between the SS pin and AVSS controls the soft-start time of the PWM controller. The following equation can be used to select the capacitor for the desired soft-start time:

$$C_{SS} = \frac{t_{SS} \times I_{SS}}{V_{REF}} \tag{6}$$

#### where:

- t<sub>SS</sub> is the desired soft-start time

- V<sub>REF</sub> is voltage reference of 0.613 V (typical)

- I<sub>SS</sub> is the soft-start charging current of 2.7 μA (typical)

#### 8.3.8 Switching Frequency and External Synchronization

Each TPS7H500x-SEP controller has three modes for setting the switching frequency of the device: internal oscillator, external synchronization, and primary-secondary. The device is placed in one of these modes through unique configurations of the RT and SYNC pins. Primary-secondary mode can be used when it is desired for two controllers to have synchronized switching without the use of the external clock.

#### 8.3.8.1 Internal Oscillator Mode

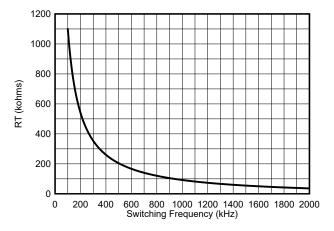

A resistor from the RT pin to AVSS sets the switching frequency of the device. The TPS7H500x-SEP controller has a switching frequency range of 100 kHz to 2 MHz. In internal oscillator mode, the RT pin must be populated or the controller will not perform any switching. Equation 7 shows the calculation determining the RT value for a desired switching frequency. The curve in Figure 8-7 shows the RT value that corresponds to a given switching frequency for the TPS7H500x-SEP.

$$RT = \frac{112000}{f_{sw}} - 19.7 \tag{7}$$

where:

- RT is in kΩ

- f<sub>sw</sub> is in kHz

Figure 8-7. RT vs Switching Frequency

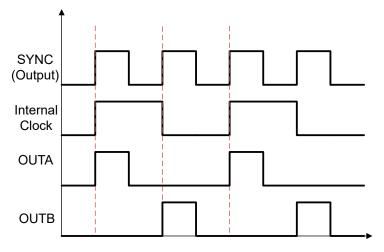

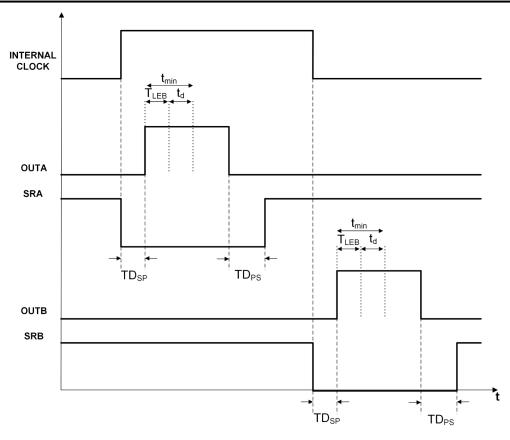

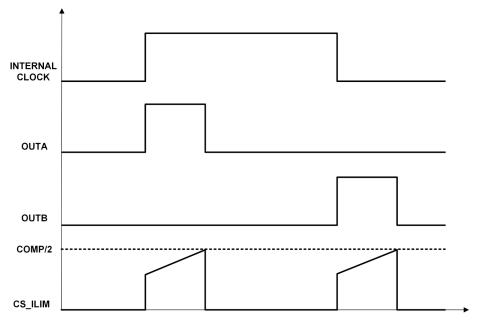

In this mode, the SYNC pin is configured as an output and produces a clock signal with a frequency that is twice that of the switching frequency set by RT. As such, this clock signal has a range of 200 kHz to 4 MHz. This SYNC output clock signal is in phase with the switching frequency of the device. Figure 8-8 shows typical waveforms for the controllers in this mode of operation. Note that the OUTB waveform is only applicable for TPS7H5005-SEP and TPS7H5008-SEP.

Figure 8-8. Switching Waveforms for Internal Oscillator Mode

### 8.3.8.2 External Synchronization Mode

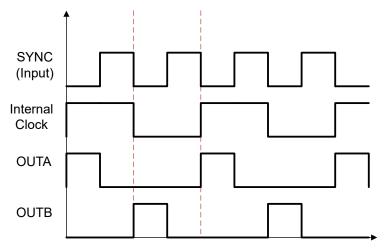

Each controller can be used in external synchronization mode by leaving the RT pin floating and applying a clock to the SYNC pin. Note than the RT pin configuration sets the oscillator mode of the controller and must be left floating for this mode of operation. The external clock that is applied must be set to twice the desired switching frequency (that is, a 1-MHz applied clock is needed for 500-kHz switching frequency). The external clock must be in the range of 200 kHz to 4 MHz with a duty cycle between 40% and 60%. It is recommended to use an external clock with 50% duty cycle. The controller will internally invert the clock signal that is applied at the SYNC pin during this mode. Since the controller does not perform any switching with RT floating, the applied clock must be present before OUTA and OUTB (where applicable) will become active for external synchronization mode. Figure 8-9 shows the switching waveforms for the controllers in external synchronization mode. Note that the OUTB waveform is only applicable for TPS7H5005-SEP and TPS7H5008-SEP.

Figure 8-9. Switching Waveforms for External Synchronization Mode

### 8.3.8.3 Primary-Secondary Mode

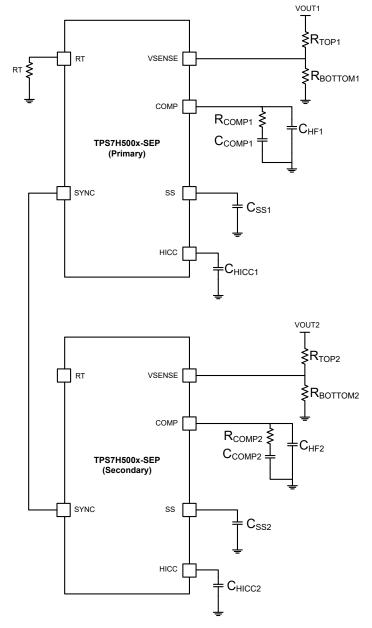

Two TPS7H500x-SEP controllers can be operated in a primary-secondary mode by utilizing the SYNC pin. As mentioned in *Internal Oscillator Mode*, when RT is selected to provide the desired switching frequency, SYNC outputs a clock signal at twice the switching frequency. As such, the clock input generated by the primary device could be used as the clock input at SYNC for the secondary controller, which would operate in external synchronization mode. This means that the RT pin of the primary device should be populated while the corresponding pin of the secondary device would be left floating.

The primary-secondary mode would be useful in a couple of scenarios. The first is for two independent converters that need to be synchronized to the same switching frequency. In this instance, the converters can be two converters can have different operating conditions or topologies. Besides the shared SYNC signal, there are no connections between the two converters.

Figure 8-10. Primary-Secondary Mode Configuration for Two Independent Converters

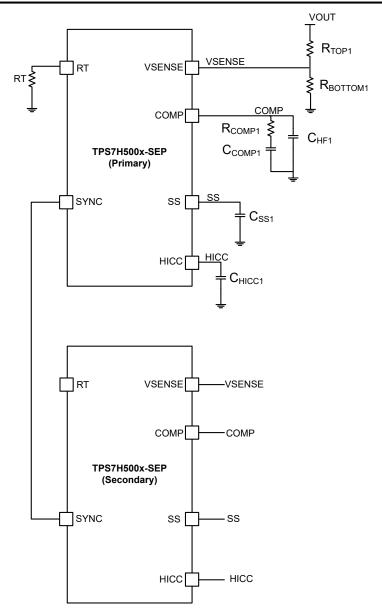

In a second scenario, two controllers can be used to design a single interleaved converter with phases in parallel. In this design, the VSENSE, COMP, SS, and HICC pins would need to be connected in addition to the shared SYNC connection.

Figure 8-11. Primary-Secondary Mode Configuration for Parallel Operation

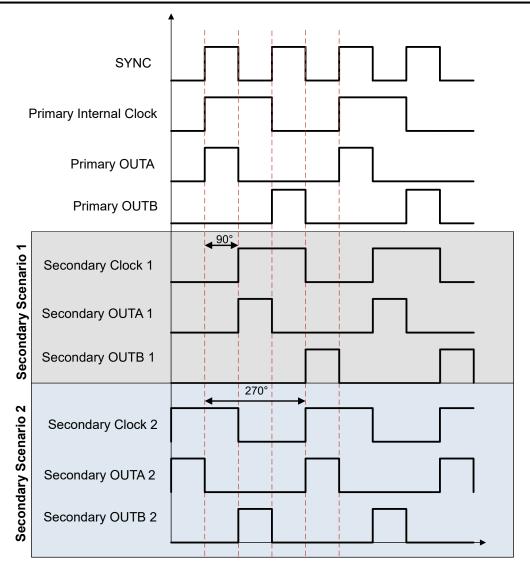

When using two controllers in primary-secondary mode, it is important to note that secondary controller will invert the clock signal that it receives from the primary controller. As such, there will be phase shift between the switching outputs of the primary and secondary controllers. This phase shift from an output (i.e. OUTA) on the primary controller to the corresponding output on the secondary controller will be 90° or 270°, depending on when the secondary device synchronizes to its clock input. Note that in Figure 8-12, the waveforms for OUTB are only applicable for TPS7H5005-SEP and TPS7H5008-SEP.

Figure 8-12. Switching Waveforms for Primary-Secondary Mode

The three operational modes for the controller are summarized in Table 8-1.

Table 8-1. Oscillator Modes and Configurations

| MODE                     | RT                                                                               | SYNC                                                                                                                                           | SWITCHING FREQUENCY                                                                                                                                            |

|--------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal oscillator      | Populated with resistor to AVSS.                                                 | Configured as output. Generates in-phase clock at twice the switching frequency.                                                               | Configurable from 100 kHz to 2 MHz depending on RT value.                                                                                                      |

| External synchronization | Floating.                                                                        | Configured as input. Accepts 200-kHz to 4-MHz external clock that is inverted internally.                                                      | Synchronized to SYNC input clock at ½ of the clock frequency. Switching is out-of-phase with external clock.                                                   |