**TPS8804**

SLVSF29C - OCTOBER 2019 - REVISED AUGUST 2021

# **TPS8804 Smoke Detector AFE**

#### 1 Features

- Photo Chamber AFE

- Dual 8-bit programmable current LED drivers

- Temperature compensation of LED current

- Ultra-low offset op-amp for photodiodes

- Programmable and bypassable gain stage

- Carbon Monoxide Sensor AFE

- Ultra-low offset gain stage

- Programmable gain and reference

- Power Management

- Programmable LDO for external microcontroller

- SLC interface transmitter and receiver

- Ultra-low power consumption

- I<sup>2</sup>C serial interface

- Wide input voltage range

# 2 Applications

Smoke and CO detector

## 3 Description

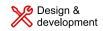

The TPS8804 integrates all of the amplifiers and drivers required for a dual-wave photoelectric smoke detection and carbon monoxide detection system. Its high flexibility is ideal for smoke detection systems where precision and power consumption are critical.

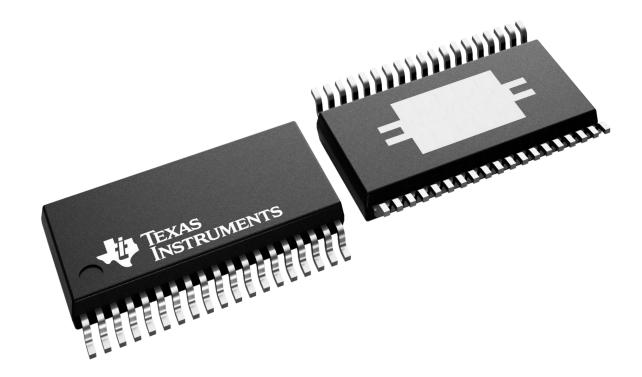

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM) |

|-------------|------------|-----------------|

| TPS8804     | TSSOP (38) | 9.7 mm x 4.4 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

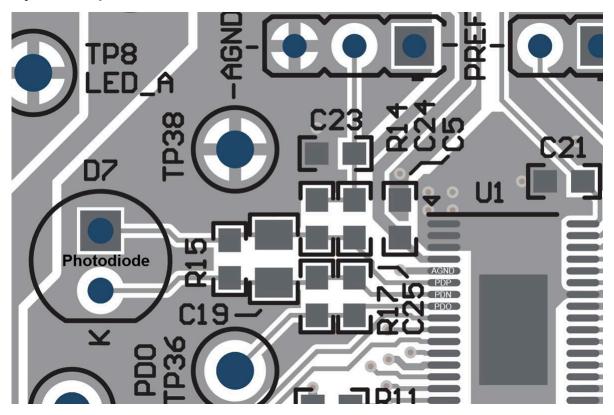

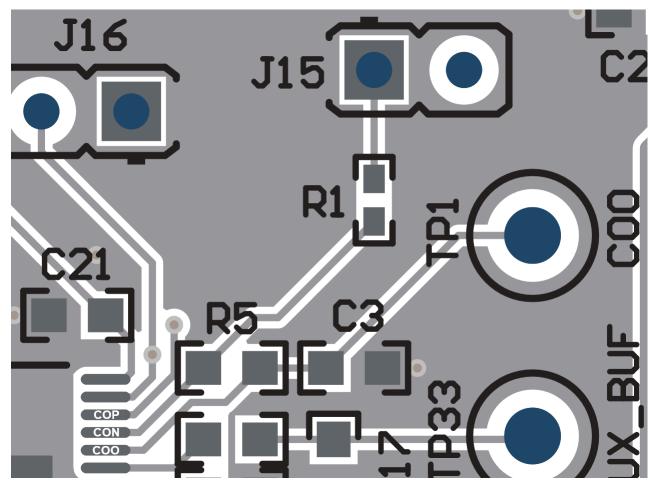

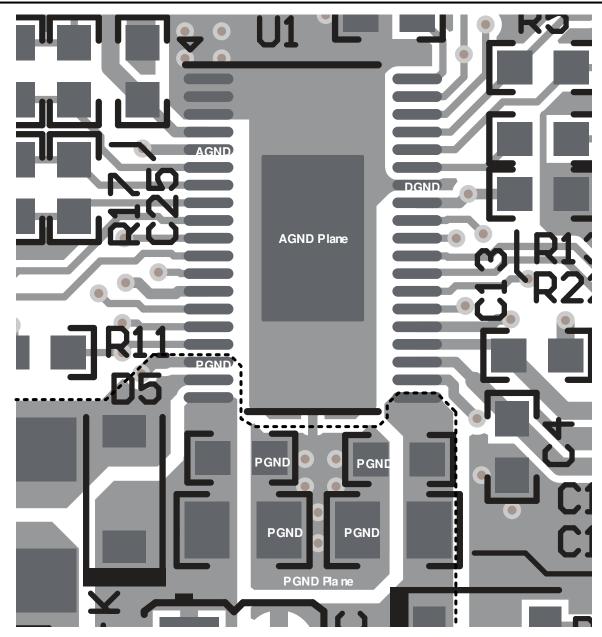

Simplified Application

# **Table of Contents**

| 1 Features                           | 1              | 7.5 Programming                                 | 30       |

|--------------------------------------|----------------|-------------------------------------------------|----------|

| 2 Applications                       | 1              | 7.6 Register Maps                               |          |

| 3 Description                        |                | 8 Application and Implementation                |          |

| 4 Revision History                   |                | 8.1 Application Information                     |          |

| 5 Pin Configuration and Functions    | 3              | 8.2 Typical Application                         | 39       |

| Pin Functions                        |                | 9 Power Supply Recommendations                  |          |

| 6 Specifications                     |                | 10 Layout                                       |          |

| 6.1 Absolute Maximum Ratings         |                | 10.1 Layout Guidelines                          |          |

| 6.2 ESD Ratings                      |                | 10.2 Layout Example                             |          |

| 6.3 Recommended Operating Conditions | <mark>5</mark> | 11 Device and Documentation Support             |          |

| 6.4 Thermal Information              | 6              | 11.1 Receiving Notification of Documentation Up | dates 47 |

| 6.5 Electrical Characteristics       | <mark>6</mark> | 11.2 Support Resources                          | 47       |

| 6.6 Typical Characteristics          | 16             | 11.3 Trademarks                                 |          |

| 7 Detailed Description               |                | 11.4 Electrostatic Discharge Caution            |          |

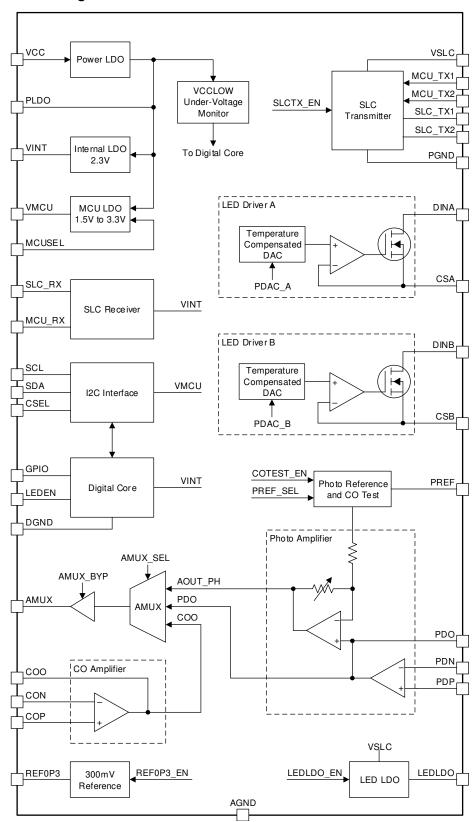

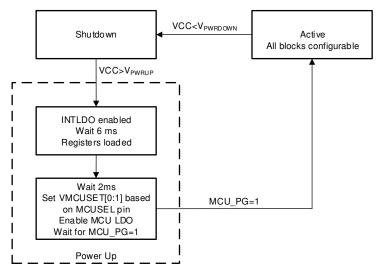

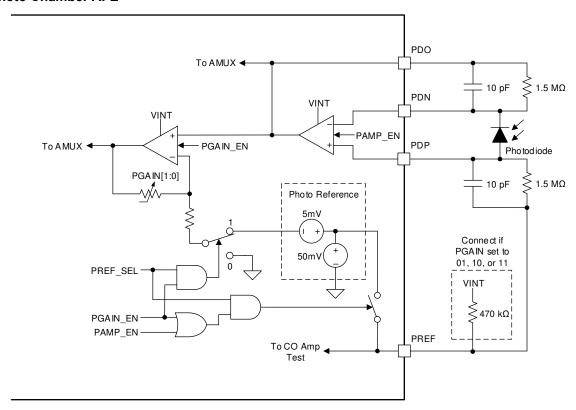

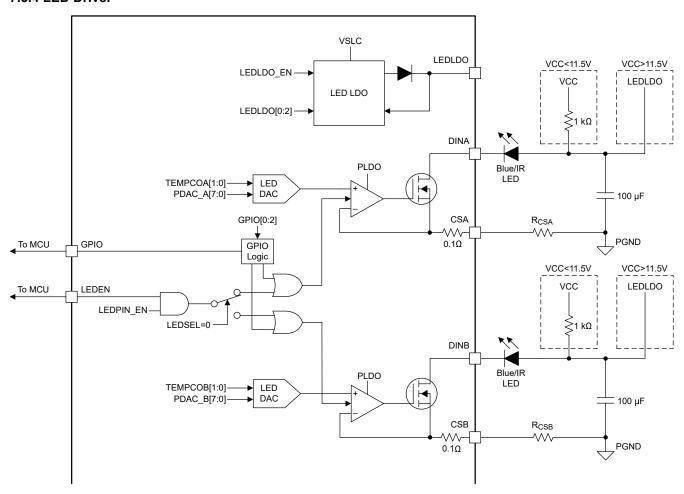

| 7.1 Overview                         | 17             | 11.5 Glossary                                   |          |

| 7.2 Functional Block Diagram         |                | 12 Mechanical, Packaging, and Orderable         |          |

| 7.3 Feature Description              |                | Information                                     | 48       |

| 7.4 Device Functional Modes          |                |                                                 |          |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision B (March 2021) to Revision C (August 2021)                                 | Page |

|--------------------------------------------------------------------------------------------------|------|

| Updated Figure 7-3                                                                               | 22   |

| <ul> <li>Added Connect a capacitor with a value between 1 μF and 100 μF to the LEDLDO</li> </ul> |      |

| Updated VCCLOW description in Section 7.6.2                                                      | 31   |

| Changes from Revision A (March 2020) to Revision B (March 2021)                                  | Page |

| Changed typical I <sub>MCULDO,Q</sub> based on measurement data                                  | 6    |

| Changed typical I <sub>CO,Q</sub> based on measurement data                                      | 6    |

| Changes from Revision * (October 2019) to Revision A (March 2020)                                | Page |

| Changed document status from Advanced Information to Production Data                             | 1    |

| Added typical value to V <sub>PDIN,OFS</sub>                                                     | 6    |

| Added typical value to V <sub>OFFS,CO</sub>                                                      | 6    |

| Added typical value to V <sub>MUX,OFFS</sub>                                                     |      |

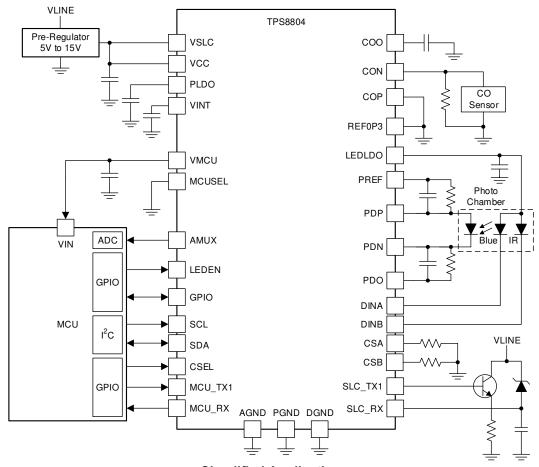

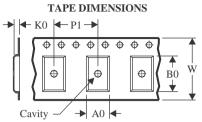

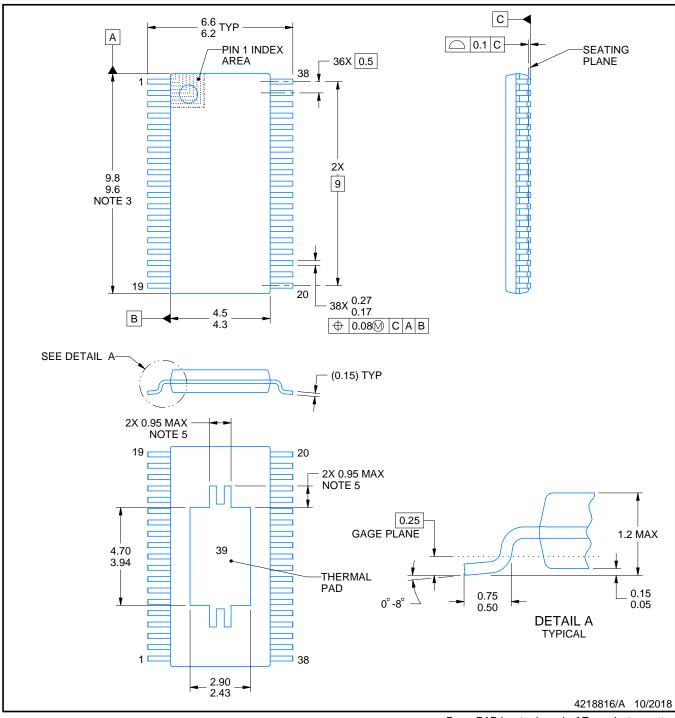

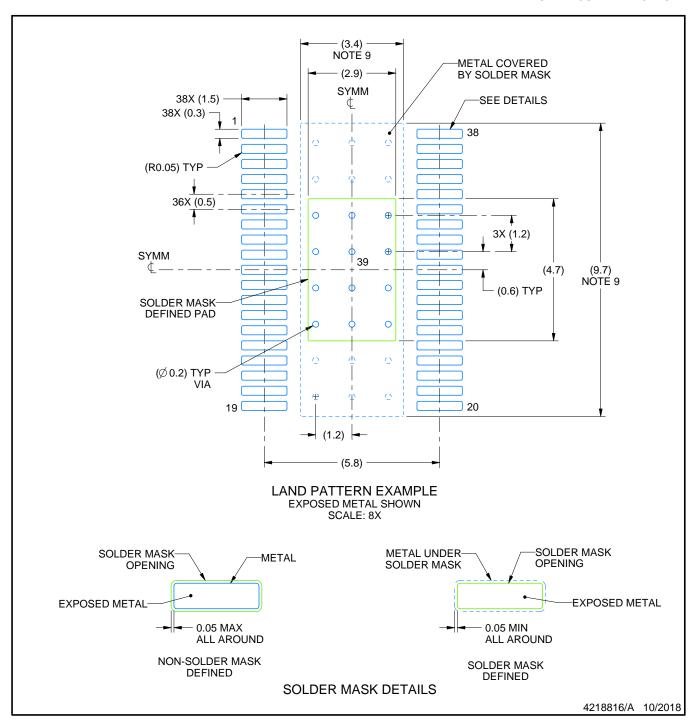

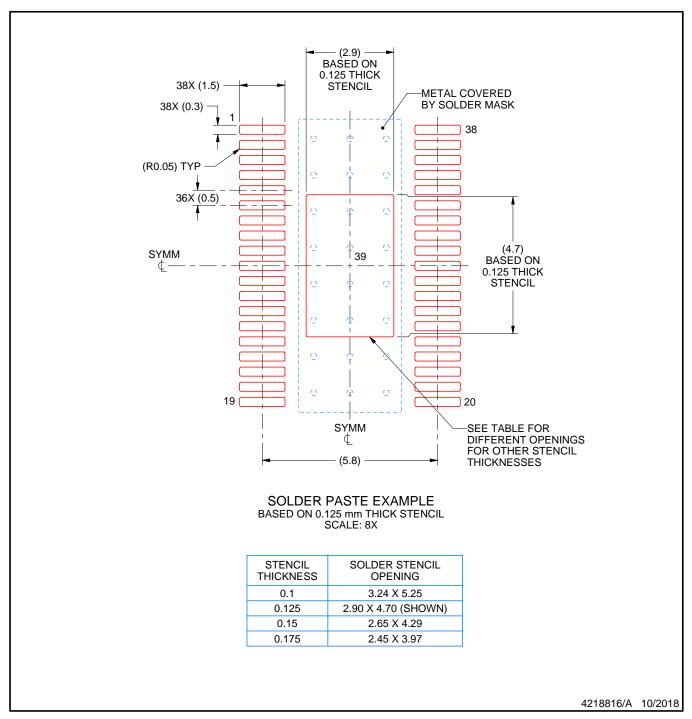

# **5 Pin Configuration and Functions**

Figure 5-1. DCP Package 38-Pin TSSOP Top View

## **Pin Functions**

| P       | IN  | 1/0 | DESCRIPTION                                                                                                                                                                              |  |

|---------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME    | NO. | I/O | DESCRIPTION                                                                                                                                                                              |  |

| AGND    | 5   | I   | Analog ground. Connect to ground plane.                                                                                                                                                  |  |

| AMUX    | 33  | 0   | Analog multiplexer output.                                                                                                                                                               |  |

| CON     | 35  | I   | Negative terminal of CO operational amplifier. Connect to GND if unused.                                                                                                                 |  |

| COO     | 34  | 0   | Output of CO operational amplifier. Connect to GND if unused.                                                                                                                            |  |

| COP     | 36  | I   | Positive terminal of CO operational amplifier. Connect to GND if unused.                                                                                                                 |  |

| CSA     | 9   | I   | LED driver A current sense.                                                                                                                                                              |  |

| CSB     | 11  | I   | LED driver B current sense. Connect to GND if unused.                                                                                                                                    |  |

| CSEL    | 29  | I   | Device address select pin for I <sup>2</sup> C serial interface. Pull to GND for I <sup>2</sup> C address 0x3F. Pull to VMCU for I <sup>2</sup> C address 0x2A. Do not leave floating.   |  |

| DGND    | 32  | I   | Digital ground. Connect to AGND.                                                                                                                                                         |  |

| DINA    | 10  | I   | LED driver A current sink. Connect to cathode of LED.                                                                                                                                    |  |

| DINB    | 12  | I   | LED driver B current sink. Connect to cathode of LED. Connect to GND if unused.                                                                                                          |  |

| GPIO    | 26  | I/O | Multi-purpose digital input and output.                                                                                                                                                  |  |

| LEDEN   | 31  | I   | LED driver enable. Do not leave floating while device is powered.                                                                                                                        |  |

| LEDLDO  | 4   | 0   | LDO output for charging LED supply capacitor. Connect to GND if unused.                                                                                                                  |  |

| MCU_RX  | 25  | 0   | SLC interface output for receiving data from VLINE.                                                                                                                                      |  |

| MCU_TX1 | 30  | I   | Primary SLC interface input for transmitting data to VLINE.                                                                                                                              |  |

| MCU_TX2 | 16  | I   | Secondary SLC interface input for transmitting data to VLINE.                                                                                                                            |  |

| MCUSEL  | 13  | I   | Default MCULDO voltage selection input. Leave floating for VMCU = 3.3 V. Tie to VINT for VMCU = 2.5 V. Tie to GND for VMCU = 1.8 V. Connect to GND with 620-Ω resistor for VMCU = 1.5 V. |  |

| PDN     | 7   | I   | Photo input amplifier negative input. Connect to cathode of photodiode.                                                                                                                  |  |

| PDO     | 8   | 0   | Photo input amplifier output pin.                                                                                                                                                        |  |

| PDP     | 6   | I   | Photo input amplifier positive Input. Connect to anode of photodiode.                                                                                                                    |  |

| PGND    | 17  | I   | Power ground connection . Connect to AGND.                                                                                                                                               |  |

| P           | IN          | I/O | DESCRIPTION                                                            |  |  |

|-------------|-------------|-----|------------------------------------------------------------------------|--|--|

| NAME        | NO.         | 1/0 | DESCRIPTION                                                            |  |  |

| PLDO        | 21          | 0   | Capacitor connection to PLDO regulator.                                |  |  |

| PREF        | 37          | 0   | Photo reference voltage and output for testing CO sensor connectivity. |  |  |

| REF0P3      | 38          | 0   | 300mV reference. Connect to GND if unused.                             |  |  |

| RESERVED    | 1, 2, 3, 18 | N/A | Connect to GND.                                                        |  |  |

| SCL         | 27          | I   | Clock input for I <sup>2</sup> C serial interface.                     |  |  |

| SDA         | 28          | I/O | Data line for I <sup>2</sup> C serial interface.                       |  |  |

| SLC_RX      | 24          | I   | SLC interface input for receiving data from VLINE.                     |  |  |

| SLC_TX1     | 14          | 0   | Primary SLC interface output for transmitting data to VLINE.           |  |  |

| SLC_TX2     | 15          | 0   | Secondary SLC interface output for transmitting data to VLINE.         |  |  |

| VCC         | 20          | I   | Input supply pin.                                                      |  |  |

| VINT        | 22          | 0   | Capacitor connection to internal supply LDO.                           |  |  |

| VMCU        | 23          | I/O | LDO supply for external microcontroller and internal IO buffers.       |  |  |

| VSLC        | 19          | I   | SLC transmitter supply.                                                |  |  |

| Thermal Pad | 39          | N/A | Metal connection for thermal dissipation. Connect to ground plane.     |  |  |

## **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                                    | PARAMETER                                             | MIN  | MAX                                         | UNIT |

|------------------------------------|-------------------------------------------------------|------|---------------------------------------------|------|

| Power IO                           | SLC_TX1, SLCTX_2, VCC, VSLC                           | -0.3 | 16.5                                        | V    |

| Analog IO                          | DINA, DINB, LEDLDO                                    | -0.3 | 12                                          | V    |

| Analog connections                 | AMUX, CON, COO, COP, PREF, MCUSEL, PDO, REF0P3        | -0.3 | VINT + 0.3 or<br>3.6, whichever<br>is lower | V    |

| LDO outputs                        | VINT, VMCU                                            | -0.3 | PLDO + 0.3 or<br>3.6, whichever<br>is lower | V    |

| LED current sense                  | CSA                                                   | -0.3 | DINA + 0.3 or<br>3.6, whichever<br>is lower | V    |

| LED current sense                  | CSB                                                   | -0.3 | DINB + 0.3 or<br>3.6, whichever<br>is lower | V    |

| Photo amplifier inputs             | PDN, PDP                                              | -0.3 | 3.6                                         | V    |

| PLDO voltage                       | PLDO                                                  | -0.3 | 7.0                                         | V    |

| SLC receiver                       | SLC_RX                                                | -0.3 | 18                                          | V    |

| Digital IO                         | CSEL, GPIO, LEDEN, MCU_RX, MCU_TX1, MCU_TX2, SCL, SDA | -0.3 | VMCU + 0.3 or<br>3.6, whichever<br>is lower | V    |

| Max operating ambient temperature  | T <sub>A</sub>                                        | -40  | 125                                         | °C   |

| Max operating junction temperature | TJ                                                    | -40  | 125                                         | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

over operating free-air temperature range (unless otherwise noted)

|                    |                         |                                                                              | Value | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>1</sup>              | ±3000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>2</sup> | ±1500 | V    |

## 6.3 Recommended Operating Conditions

|                        | PARAMETER  | MIN | MAX  | UNIT |

|------------------------|------------|-----|------|------|

| SLC transmitter supply | VSLC       | 4.5 | 15.6 | V    |

| Power supply           | vcc        | 2.6 | 15.6 | V    |

| LED driver             | DINA, DINB | 0   | 11.5 | V    |

| SLC receiver           | SLC_RX     | 0   | 17   | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>&</sup>lt;sup>2</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

|                      | PARAMETER                                             |       | MAX  | UNIT |

|----------------------|-------------------------------------------------------|-------|------|------|

| Digital IO           | CSEL, GPIO, LEDEN, MCU_RX, MCU_TX1, MCU_TX2, SCL, SDA | 0     | VMCU | V    |

| Digital IO supply    | VMCU                                                  | 1.425 | 3.6  | V    |

| Ambient temperature  | T <sub>A</sub>                                        | -40   | 85   | °C   |

| Junction temperature | TJ                                                    | -40   | 85   | °C   |

## **6.4 Thermal Information**

|                        |                                              | TPS8804 |      |

|------------------------|----------------------------------------------|---------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | DCP     | UNIT |

|                        |                                              | 38 PINS |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 29.3    | °C/W |

| R <sub>0JC(top)</sub>  | Junction-to-case (top) thermal resistance    | 20.0    | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 10.1    | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 0.3     | °C/W |

| $\Psi_{JB}$            | Junction-to-board characterization parameter | 10.0    | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 2.2     | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **6.5 Electrical Characteristics**

over operating free-air temperature range (unless otherwise noted)

|                           | PARAMETER                                                                 | TEST CONDITIONS                                                                 | MIN   | TYP  | MAX  | UNIT |

|---------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------|------|------|------|

| INPUT VOLTA               | GE AND CURRENTS                                                           |                                                                                 |       |      |      |      |

| V <sub>PWRUP</sub>        | Power up threshold. Note:<br>Device enters active state<br>when MCU_PG=1. | VCC rising                                                                      | 1.2   | 1.55 | 2.0  | V    |

| V <sub>PWRDOWN</sub>      | Power down threshold                                                      | VCC falling                                                                     | 0.932 | 1.15 | 2.0  | V    |

| V <sub>PWR, HYS</sub>     | VCC power up to power down hysteresis                                     |                                                                                 | 6.4   | 400  | 580  | mV   |

| V                         | VCC low warning reset                                                     | PLDO voltage rising                                                             | 2.35  | 2.54 | 2.7  | V    |

| V <sub>VCCLOW, RISE</sub> | threshold                                                                 | Deglitch time                                                                   | 110   | 141  | 172  | μs   |

| V                         | VCC low warning assert                                                    | PLDO voltage falling                                                            | 2.15  | 2.42 | 2.6  | V    |

| V <sub>VCCLOW, FALL</sub> | threshold                                                                 | Deglitch time                                                                   | 110   | 141  | 172  | μs   |

|                           | Standby Supply Current                                                    | All blocks that can be disabled are off, T <sub>J</sub> =27C, VCC=3V, VMCU=1.8V |       | 3.8  | 4.4  | μΑ   |

| ISTANDBY                  |                                                                           | All blocks that can be disabled are off, T <sub>J</sub> =27C, VCC=9V, VMCU=3.3V |       | 7.7  | 9.1  | μΑ   |

| POWER LDO                 |                                                                           |                                                                                 |       |      |      |      |

|                           |                                                                           | VCC = 2.0 V, I <sub>PLDO</sub> = 10 mA                                          | 1.93  | 1.96 | 1.99 | V    |

|                           |                                                                           | VCC = 2.0 V, I <sub>PLDO</sub> = 30 mA                                          | 1.8   | 1.89 | 1.95 | V    |

| $V_{PLDO}$                | Output Voltage                                                            | VCC = 3.3 V, I <sub>PLDO</sub> = 30 mA                                          | 3.1   | 3.22 | 3.3  | V    |

|                           |                                                                           | VCC = 9 V, I <sub>PLDO</sub> = 30 mA                                            | 4.1   | 4.9  | 6.7  | V    |

|                           |                                                                           | VCC = 11.5 V, I <sub>PLDO</sub> = 30 mA                                         | 4.1   | 5    | 6.7  | V    |

| C <sub>PLDO</sub>         | PLDO capacitor required for stability                                     |                                                                                 | 0.7   | 1    | 1.3  | μF   |

Product Folder Links: *TPS8804*

| · · · · · · · · · · · · · · · · · · · | ng free-air temperature range PARAMETER | TEST CONDITIONS                                                                                  | MIN   | TYP | MAX   | UNIT |

|---------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| INTERNAL L                            | DO                                      |                                                                                                  |       |     |       |      |

|                                       |                                         | I <sub>VINT</sub> < 10 mA                                                                        | 2.25  | 2.3 | 2.35  | V    |

|                                       | Output Voltage                          | I <sub>VINT</sub> < 10 uA, T>80C                                                                 | 2.25  | 2.3 | 2.40  | V    |

|                                       | DC Output Voltage Accuacy               | No external/internal load,<br>VCC = 2.6 V - 11.5 V                                               | -2    |     | 2     | %    |

|                                       | Line Regulation                         | VCC = 2.6 V-11.5 V, IOUT = 10 mA                                                                 | -2    |     | 2     | %    |

| V <sub>INTLDO</sub>                   | Load Regulation                         | I <sub>VINT</sub> = 0 mA - 10 mA, VCC = 3 V                                                      | -2    |     | 2     | %    |

|                                       |                                         | I <sub>VINT</sub> stepped from 0 mA to 10 mA in 1us                                              | -8    |     | 8     | %    |

|                                       | Transient regulation                    | I <sub>VINT</sub> stepped from 10 mA to 0 mA in 1us                                              | -5    |     | 5     | %    |

|                                       | PSRR                                    | V <sub>IN</sub> = 3.0 V, I <sub>OUT</sub> = 10 mA, f = 60 Hz (200 mVpp)                          | 50    |     |       | dB   |

| INTLDO, OUT                           | Output current range                    |                                                                                                  | 0     |     | 10    | mA   |

| INTLDO, SC                            | Short Circuit Current Limit             |                                                                                                  | 30    | 280 | 500   | mA   |

| V <sub>INTLDO, DO</sub>               | Dropout Voltage                         | From PLDO to VINT, I <sub>VINT</sub> = 10 mA, PLDO = 2.2 V                                       |       | 52  | 66    | mV   |

| ^                                     | Output Capacitor                        | Caramia                                                                                          | 0.7   | 1   | 1.3   | μF   |

| CINTLDO, OUT                          | ESR of Output Capacitor                 | - Ceramic                                                                                        |       |     | 100   | mΩ   |

| MCU LDO                               |                                         |                                                                                                  |       |     | '     |      |

|                                       |                                         | $I_{MCULDO}$ < 30 mA, $V_{CC}$ > 2.2<br>V, VMCUSET = 00 (T < 80°C for no load)                   | 1.425 | 1.5 | 1.575 | V    |

|                                       |                                         | I <sub>MCULDO</sub> < 10 uA, V <sub>CC</sub> > 2.2 V,<br>VMCUSET = 00, T > 80°C                  | 1.425 | 1.5 | 1.65  | V    |

|                                       |                                         | $I_{MCULDO}$ < 30 mA, $V_{CC}$ > 2.6 V, VMCUSET = 01 (T < 80°C for no load)                      | 1.71  | 1.8 | 1.89  | V    |

|                                       |                                         | I <sub>MCULDO</sub> < 10 uA, V <sub>CC</sub> > 2.6 V,<br>VMCUSET = 01, T > 80°C                  | 1.71  | 1.8 | 1.98  | V    |

| V <sub>MCULDO</sub>                   | Output Voltage <sup>(1)</sup>           | $I_{MCULDO}$ < 30 mA, $V_{CC}$ > 3.65 V, VMCUSET = 10 (T < 80°C for no load)                     | 2.38  | 2.5 | 2.63  | V    |

|                                       |                                         | I <sub>MCULDO</sub> < 10 uA, V <sub>CC</sub> > 3.65<br>V, VMCUSET = 10, T > 80°C                 | 2.38  | 2.5 | 2.75  | V    |

|                                       |                                         | I <sub>MCULDO</sub> < 10 mA, V <sub>CC</sub> > 3.65<br>V, VMCUSET = 11 (T < 80°C<br>for no load) | 3.13  | 3.3 | 3.47  | V    |

|                                       |                                         | I <sub>MCULDO</sub> < 10 uA, V <sub>CC</sub> > 4.5 V,<br>VMCUSET = 11, T > 80°C                  | 3.13  | 3.3 | 3.60  | V    |

|                                       |                                         | I <sub>MCULDO</sub> < 50 mA, VCC > 5.5<br>V, VMCUSET = 11                                        | 3.13  | 3.3 | 3.47  | V    |

|                                       | DC Output Voltage Accuracy              | T < 80°C                                                                                         | -5    |     | 5     | %    |

| <i>I.</i>                             | MCULDO power good                       | VMCU rising                                                                                      | 75    | 82  | 95    | %    |

| / <sub>MCULDO,PG</sub>                | threshold                               | VMCU falling                                                                                     | 65    | 78  | 85    | %    |

|                                       |                                         | V <sub>CC</sub> > 2.2 V, VMCUSET = 00                                                            | 0     |     | 30    | mA   |

|                                       |                                         | V <sub>CC</sub> > 2.6 V, VMCUSET = 01                                                            | 0     |     | 30    | mA   |

| MCULDO                                | Output Current Range                    | V <sub>CC</sub> > 3.65 V, VMCUSET = 10                                                           | 0     |     | 30    | mA   |

|                                       |                                         | V <sub>CC</sub> > 4.5 V, VMCUSET = 11                                                            | 0     |     | 50    | mA   |

|                                       |                                         |                                                                                                  |       |     |       |      |

|                              | PARAMETER                                                                                                       | TEST CONDITIONS                                                                                                                                                          | MIN  | TYP  | MAX  | UNIT |

|------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                              |                                                                                                                 | I <sub>MCULDO</sub> stepped from 0 mA to 10 mA in 1us, T < 80°C                                                                                                          | -7   |      | 7    | %    |

| V <sub>MCULDO, TR</sub>      | MCULDO load transient                                                                                           | I <sub>MCULDO</sub> stepped from 0 mA to 10 mA in 1us, T > 80°C                                                                                                          | -8   |      | 8    | %    |

| ▼MCULDO, IR                  | regulation                                                                                                      | I <sub>MCULDO</sub> stepped from 10 mA to 0 mA in 1us, T < 80°C                                                                                                          | -5   |      | 5    | %    |

|                              |                                                                                                                 | I <sub>MCULDO</sub> stepped from 10 mA to 0 mA in 1us, T > 80°C                                                                                                          | -8   |      | 8    | %    |

| MCULDO, SC                   | Short Circuit current limit                                                                                     |                                                                                                                                                                          | 72   | 162  | 253  | mA   |

| t <sub>MCULDO,</sub> PWR     | Power Up Time                                                                                                   | C <sub>MCULDO</sub> = 1µF, time from<br>VMCU=0V to 90% of target<br>voltage                                                                                              |      | 600  | 1100 | μs   |

| T <sub>MCULDO, PG</sub>      | MCULDO power good deglitch time                                                                                 |                                                                                                                                                                          | 92   | 125  | 158  | μs   |

| T <sub>MCULDO,</sub><br>MASK | MCULDO low voltage error mask time. MCULDO_ERR is masked for T_MCULDO,MASK after VMCUSET or MCU_DIS is changed. |                                                                                                                                                                          |      | 10   |      | ms   |

| I <sub>MCULDO, Q</sub>       | Quiescent Current                                                                                               | I <sub>MCULDO</sub> = 0µA                                                                                                                                                |      | 2.04 | 3    | μΑ   |

| C <sub>MCULDO</sub>          | Output Capacitor                                                                                                | Ceramic                                                                                                                                                                  | 0.7  | 1    | 10   | μF   |

| OMCULDO .                    | ESR of Output Capacitor                                                                                         | Ceramic                                                                                                                                                                  |      |      | 100  | mΩ   |

|                              | MCUSEL component requirements. Not tested in production                                                         | Pull-down resistance to set VMCUSET[1:0]=00 on powerup                                                                                                                   | 558  | 620  | 682  | Ω    |

| D                            |                                                                                                                 | Pull-down resistance to set VMCUSET[1:0]=01 on powerup                                                                                                                   | 0    |      | 10   | Ω    |

| R <sub>MCUSEL</sub>          |                                                                                                                 | Pull-up resistance to VINT to set VMCUSET[1:0]=10 on powerup                                                                                                             | 0    |      | 10   | Ω    |

|                              |                                                                                                                 | Capacitance to set VMCUSET[1:0]=11 on powerup                                                                                                                            | 300  |      | 1000 | pF   |

| PHOTO CHAI                   | MBER INPUT STAGE AMPLIFIE                                                                                       | ĒR                                                                                                                                                                       |      |      | I    |      |

| $V_{PDO}$                    | Output voltage range                                                                                            | PAMP_EN=1, Feedback<br>network: 1.5M Ω, 10pF                                                                                                                             | 0    |      | 0.5  | V    |

| f <sub>PDIN, BW</sub>        | Unity Gain Bandwidth                                                                                            |                                                                                                                                                                          | 1    |      | 5    | MHz  |

| V <sub>PDIN, OFS</sub>       | Input Offset Voltage                                                                                            |                                                                                                                                                                          | -530 | -195 | 240  | μV   |

| V <sub>PDO,</sub> ofs        | Output Offset Voltage                                                                                           | $50\text{mV}$ applied to PDP with $1.5\text{M}\Omega$ series resistor. $1.5\text{M}\Omega$ resistor connects PDN to PDO. Voltage measured between $50\text{mV}$ and PDO. | -10  |      | 10   | mV   |

| f <sub>PDIN, CHOP</sub>      | Chop Frequency                                                                                                  |                                                                                                                                                                          |      | 2    |      | MHz  |

|                              | Input amplifier settling time. Time between stepping the                                                        | Feedback network: 1.5M $\Omega$ , 10pF. 1 nA to 10 nA applied from PDN to PDP. 0V reference                                                                              | 0    | 30   | 40   | μs   |

| T <sub>PDIN,</sub> SET       | current and measuring 90% of the final value + 10% of the initial value at PDO                                  | Feedback network: 1.5MΩ,<br>5pF. 1.5MΩ connected from<br>PDP to PREF. 1 nA to 10<br>nA applied from PDN to PDP.<br>PREF_SEL=1                                            | 0    | 20   | 40   | μs   |

|                           | PARAMETER                                                                                                                                                                                                                                  | TEST CONDITIONS                                                                     | MIN   | TYP   | MAX   | UNIT |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------|-------|-------|------|

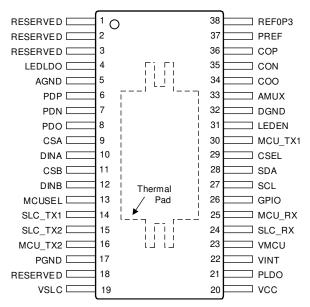

| I <sub>PDIN,</sub> ACT    | Active current. Current does not include bias block or 8 MHz oscillator.                                                                                                                                                                   |                                                                                     |       | 175   | 210   | μА   |

| РНОТО СНА                 | MBER GAIN STAGE AMPLIFIE                                                                                                                                                                                                                   | R                                                                                   |       |       |       |      |

|                           | Closed Loop                                                                                                                                                                                                                                | V <sub>PDO1</sub> =10mV, V <sub>PDO2</sub> =20mV,<br>PREF_SEL=0, PGAIN[1:0] =<br>00 | 4.75  | 4.9   | 5.05  | V/V  |

|                           | Gain Slope ( $V_{AOUT\_PH2}^-$<br>$V_{AOUT\_PH1}$ )/( $V_{SlG2}^ V_{SlG1}$ ).<br>Apply $V_{SlG1}$ from PREF                                                                                                                                | V <sub>PDO1</sub> =10mV, V <sub>PDO2</sub> =20mV,<br>PREF_SEL=0, PGAIN[1:0] =<br>01 | 10.67 | 11    | 11.33 | V/V  |

|                           | to PDO and measure<br>AOUT_PH. Apply V <sub>SIG2</sub> from<br>COTEST to PDO and                                                                                                                                                           | V <sub>PDO1</sub> =10mV, V <sub>PDO2</sub> =20mV,<br>PREF_SEL=0, PGAIN[1:0] =<br>10 | 19.4  | 20    | 20.6  | V/V  |

| C                         | measure AOUT_PH                                                                                                                                                                                                                            | V <sub>PDO1</sub> =10mV, V <sub>PDO2</sub> =20mV,<br>PREF_SEL=0, PGAIN[1:0] =<br>11 | 33.95 | 35    | 36.05 | V/V  |

| G <sub>PGAIN</sub>        | Closed Loop                                                                                                                                                                                                                                | V <sub>SIG1</sub> =10mV, V <sub>SIG2</sub> =20mV,<br>PREF_SEL=1, PGAIN[1:0] = 00    | 4.61  | 4.75  | 4.89  | V/V  |

|                           | Closed Loop Gain Slope (V <sub>AOUT_PH2</sub> -V <sub>AOUT_PH1</sub> )/(V <sub>SIG2</sub> -V <sub>SIG1</sub> ). Apply V <sub>SIG1</sub> from PREF to PDO and measure AOUT_PH. Apply V <sub>SIG2</sub> from PREF to PDO and measure AOUT_PH | $V_{SIG1}$ =10mV, $V_{SIG2}$ =20mV,<br>PREF_SEL=1, PGAIN[1:0] = 01                  | 10.09 | 10.4  | 10.71 | V/V  |

|                           |                                                                                                                                                                                                                                            | V <sub>SIG1</sub> =10mV, V <sub>SIG2</sub> =20mV,<br>PREF_SEL=1, PGAIN[1:0] =<br>10 | 17.94 | 18.5  | 19.06 | V/V  |

|                           |                                                                                                                                                                                                                                            | $V_{SIG1}$ =10mV, $V_{SIG2}$ =20mV,<br>PREF_SEL=1, PGAIN[1:0] = 11                  | 31.28 | 32.25 | 33.22 | V/V  |

| F <sub>PGAIN, BW</sub>    | Unity Gain Bandwidth                                                                                                                                                                                                                       |                                                                                     | 1     | 5     | 8     | MHz  |

| V <sub>PGAIN, OFS</sub>   | Input offset Voltage                                                                                                                                                                                                                       |                                                                                     | -6    | ,     | 5     | mV   |

| T <sub>PGAIN,</sub> SET   | Gain amplifier settling time.<br>Time between stepping the<br>voltage and measuring 90%<br>of the final value + 10% of the<br>initial value at AOUT_PH                                                                                     | PGAIN[1:0]=00. PDO<br>stepped from 3mV to 30mV.<br>PREF_SEL=0                       |       | 1.8   | 2.522 | μs   |

| PGAIN, ACT                | Active current. Current does not include bias block.                                                                                                                                                                                       | 1.0 V input voltage,<br>PGAIN[1:0] = 00, PGAIN_EN<br>= 1                            |       | 40    | 70    | μΑ   |

| LED LDO                   |                                                                                                                                                                                                                                            |                                                                                     |       |       |       |      |

| V <sub>LEDLDO</sub>       | LEDLDO output voltage range                                                                                                                                                                                                                |                                                                                     | 7.5   |       | 10    | V    |

| V <sub>LEDLDO,ACC</sub>   | LDO output accuracy                                                                                                                                                                                                                        | I_LEDLDO = 0uA to 100uA                                                             | -5    |       | 5     | %    |

| V <sub>LEDLDO, RES</sub>  | LED LDO output step size                                                                                                                                                                                                                   |                                                                                     |       | 0.5   |       | V    |

| I <sub>LEDLDO,</sub> OUT  | LDO output current limit                                                                                                                                                                                                                   |                                                                                     | 1     | 3     | 6     | mA   |

| I <sub>LEDLDO, Q</sub>    | Quiescent current. Current does not include bias block.                                                                                                                                                                                    |                                                                                     |       | 31    | 60    | μΑ   |

| V <sub>LEDLDO, DROP</sub> | LED LDO dropout voltage                                                                                                                                                                                                                    | VSLC=7V, I <sub>LEDLDO</sub> =100uA                                                 |       | 565   | 1000  | mV   |

| LED DRIVER                | Α                                                                                                                                                                                                                                          |                                                                                     |       |       |       |      |

| N <sub>PDACA, RES</sub>   | Resolution                                                                                                                                                                                                                                 |                                                                                     |       | 8     |       | Bits |

| over operating            | g free-air temperature range                       | ·                                                                                                                                            |       |       |       |       |

|---------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

|                           | PARAMETER                                          | TEST CONDITIONS                                                                                                                              | MIN   | TYP   | MAX   | UNIT  |

|                           |                                                    | T <sub>J</sub> = 27°C TEMPCOA[1:0] = 00, PDAC_A = 00, R <sub>CSA</sub> =1 kOhms, V <sub>DINA</sub> =3V                                       | 274   | 299   | 323   | mV    |

|                           |                                                    | $T_{J} = 27^{\circ}C \text{ TEMPCOA[1:0]} = \\ 00, PDAC\_A = FF, R_{CSA} = 1 \\ kOhms, V_{DINA} = 3V$                                        | 567   | 593   | 619   | mV    |

|                           |                                                    | T <sub>J</sub> = 27°C TEMPCOA[1:0] = 01, PDAC_A = 00, R <sub>CSA</sub> =1 kOhms, V <sub>DINA</sub> =3V                                       | 252   | 277   | 301   | mV    |

| √ <sub>CSA</sub>          | CSA output voltage                                 | T <sub>J</sub> = 27°C TEMPCOA[1:0] = 01, PDAC_A = FF, R <sub>CSA</sub> =1 kOhms, V <sub>DINA</sub> =3V                                       | 546   | 572   | 597   | mV    |

| V CSA                     | COA output voltage                                 | T <sub>J</sub> = 27°C TEMPCOA[1:0] =<br>10, PDAC_A = 00, R <sub>CSA</sub> =1<br>kOhms, V <sub>DINA</sub> =3V                                 | 164   | 188   | 213   | mV    |

|                           |                                                    | T <sub>J</sub> = 27°C TEMPCOA[1:0] = 10, PDAC_A = FF, R <sub>CSA</sub> =1 kOhms, V <sub>DINA</sub> =3V                                       | 458   | 484   | 510   | mV    |

|                           |                                                    | T <sub>J</sub> = 27°C TEMPCOA[1:0] = 11, PDAC_A = 00, R <sub>CSA</sub> =1 kOhms, V <sub>DINA</sub> =3V                                       | 54    | 79    | 104   | mV    |

|                           |                                                    | T <sub>J</sub> = 27°C TEMPCOA[1:0] =<br>11, PDAC_A = FF, R <sub>CSA</sub> =1<br>kOhms, V <sub>DINA</sub> =3V                                 | 350   | 376   | 403   | mV    |

|                           | DAC step size                                      |                                                                                                                                              |       | 1.18  |       | mV    |

| PDACA, STEP               | INL                                                |                                                                                                                                              | -10   |       | 10    | LSB   |

|                           | DNL                                                |                                                                                                                                              | -1.5  |       | 1.5   | LSB   |

| PDACA, SET                | Settling Time                                      |                                                                                                                                              |       | 1     | 5     | μs    |

|                           | CSA temperature compensation coefficient           | TEMPCOA[1:0] = 00,<br>PDAC_A[7:0] = 0x00, R <sub>CSA</sub> =1<br>kOhms, V <sub>DINA</sub> =3V, T <sub>J</sub> =0°C,<br>50°C                  | 0.174 | 0.347 | 0.521 | mV/°C |

|                           |                                                    | TEMPCOA[1:0] = 01,<br>PDAC_A[7:0] = 0x00, R <sub>CSA</sub> =1<br>kOhms, V <sub>DINA</sub> =3V, T <sub>J</sub> =0°C,<br>50°C                  | 0.208 | 0.416 | 0.624 | mV/°C |

| K <sub>PDACA</sub> , COMP |                                                    | TEMPCOA[1:0] = 10,<br>PDAC_A[7:0] = 0x00, R <sub>CSA</sub> =1<br>kOhms, V <sub>DINA</sub> =3V, T <sub>J</sub> =0°C,<br>50°C                  | 0.346 | 0.693 | 1.039 | mV/°C |

|                           |                                                    | TEMPCOA[1:0] = 11,<br>PDAC_A[7:0] = 0x00, R <sub>CSA</sub> =1<br>kOhms, V <sub>DINA</sub> =3V, T <sub>J</sub> =0°C,<br>50°C                  | 0.520 | 1.040 | 1.560 | mV/°C |

|                           | Dropout voltage. Voltage required between DINA and | PLDO=3.6V, R <sub>CSA</sub> =820mΩ,<br>TEMPCOA[1:0]=11,<br>PDAC_A[7:0]=0x28, T <sub>J</sub> =27°C<br>(I_LED≈158mA, 0.8% temp<br>coefficient) |       |       | 300   | mV    |

| VDINA, DROP               | CSA for current regulation.                        | PLDO=3.6V, R <sub>CSA</sub> =820mΩ,<br>TEMPCOA[1:0]=01,<br>PDAC_A[7:0]=0x79, T <sub>J</sub> =27°C<br>(I_LED≈507mA, 0.1% temp<br>coefficient) |       |       | 500   | mV    |

| DINA                      | LED current                                        |                                                                                                                                              | 0     |       | 550   | mA    |

| ED DRIVER                 | В                                                  |                                                                                                                                              |       |       |       |       |

|                           | Resolution                                         |                                                                                                                                              |       | 8     |       | Bits  |

| over operating            | g free-air temperature range                       | ·                                                                                                                                                                |       |       |       |       |

|---------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

|                           | PARAMETER                                          | TEST CONDITIONS                                                                                                                                                  | MIN   | TYP   | MAX   | UNIT  |

|                           |                                                    | $T_J$ = 27°C TEMPCOB[1:0] = 00, PDAC_B = 00, R <sub>CSB</sub> =1 kOhms, V <sub>DINB</sub> =3V                                                                    | 271   | 299   | 327   | mV    |

|                           |                                                    | $T_J$ = 27°C TEMPCOB[1:0] = 00, PDAC_B = FF, R <sub>CSB</sub> =1 kOhms, V <sub>DINB</sub> =3V                                                                    | 562   | 594   | 626   | mV    |

|                           |                                                    | $T_J$ = 27°C TEMPCOB[1:0] = 01, PDAC_B = 00, R <sub>CSB</sub> =1 kOhms, V <sub>DINB</sub> =3V                                                                    | 250   | 277   | 305   | mV    |

| $V_{CSB}$                 | CSB output voltage                                 | $T_J$ = 27°C TEMPCOB[1:0] = 01, PDAC_B = FF, R <sub>CSB</sub> =1 kOhms, V <sub>DINB</sub> =3V                                                                    | 541   | 572   | 604   | mV    |

| *CSB                      | oob output voitage                                 | T <sub>J</sub> = 27°C TEMPCOB[1:0] = 10, PDAC_B = 00, R <sub>CSB</sub> =1 kOhms, V <sub>DINB</sub> =3V                                                           | 163   | 189   | 216   | mV    |

|                           |                                                    | $T_J$ = 27°C TEMPCOB[1:0] = 10, PDAC_B = FF, R <sub>CSB</sub> =1 kOhms, V <sub>DINB</sub> =3V                                                                    | 456   | 486   | 516   | mV    |

|                           |                                                    | T <sub>J</sub> = 27°C TEMPCOB[1:0] = 11, PDAC_B = 00, R <sub>CSB</sub> =1 kOhms, V <sub>DINB</sub> =3V                                                           | 55    | 81    | 108   | mV    |

|                           |                                                    | T <sub>J</sub> = 27°C TEMPCOB[1:0] =<br>11, PDAC_B = FF, R <sub>CSB</sub> =1<br>kOhms, V <sub>DINB</sub> =3V                                                     | 350   | 379   | 408   | mV    |

|                           | DAC step size                                      |                                                                                                                                                                  |       | 1.18  |       | mV    |

| $V_{PDACB, STEP}$         | INL                                                |                                                                                                                                                                  | -10   |       | 10    | LSB   |

|                           | DNL                                                |                                                                                                                                                                  | -1.5  |       | 1.5   | LSB   |

| t <sub>PDACB, SET</sub>   | Settling time                                      |                                                                                                                                                                  |       | 1     | 5     | μs    |

|                           | CSB temperature                                    | TEMPCOB[1:0] = 00,<br>PDAC[7:0] = 0x00, R <sub>CSB</sub> =1<br>kOhms, V <sub>DINB</sub> =3V, T <sub>J</sub> =0°C,<br>50°C                                        | 0.174 | 0.347 | 0.521 | mV/°C |

| V.                        |                                                    | TEMPCOB[1:0] = 01,<br>PDAC[7:0] = 0x00, R <sub>CSB</sub> =1<br>kOhms, V <sub>DINB</sub> =3V, T <sub>J</sub> =0°C,<br>50°C                                        | 0.208 | 0.416 | 0.624 | mV/°C |

| K <sub>PDACB</sub> , COMP | compensation coefficient                           | TEMPCOB[1:0] = 10,<br>PDAC[7:0] = 0x00, R <sub>CSB</sub> =1<br>kOhms, V <sub>DINB</sub> =3V, T <sub>J</sub> =0°C,<br>50°C                                        | 0.346 | 0.693 | 1.039 | mV/°C |

|                           |                                                    | TEMPCOB[1:0] = 11,<br>PDAC[7:0] = 0x00, R <sub>CSB</sub> =1<br>kOhms, V <sub>DINB</sub> =3V, T <sub>J</sub> =0°C,<br>50°C                                        | 0.520 | 1.040 | 1.560 | mV/°C |

| V <sub>DINB,</sub> drop   | Dropout voltage. Voltage required between DINB and | PLDO=3.6V, $R_{CSA}$ =820m $\Omega$ , TEMPCOB[1:0]=11, PDAC[7:0]=0x28, TJ=27°C (I_LED $\approx$ 158mA, 0.8% temp coefficient)                                    |       |       | 300   | mV    |

|                           | CSB for current regulation.                        | $\begin{array}{l} PLDO=3.6V,R_{CSA}=820m\Omega,\\ TEMPCOB[1:0]=01,\\ PDAC[7:0]=0x79,TJ=27^{\circ}C\\ (I\_LED\approx507mA,0.1\%\ temp\\ coefficient) \end{array}$ |       |       | 500   | mV    |

| I <sub>DINB</sub>         | LED current                                        |                                                                                                                                                                  | 0     |       | 550   | mA    |

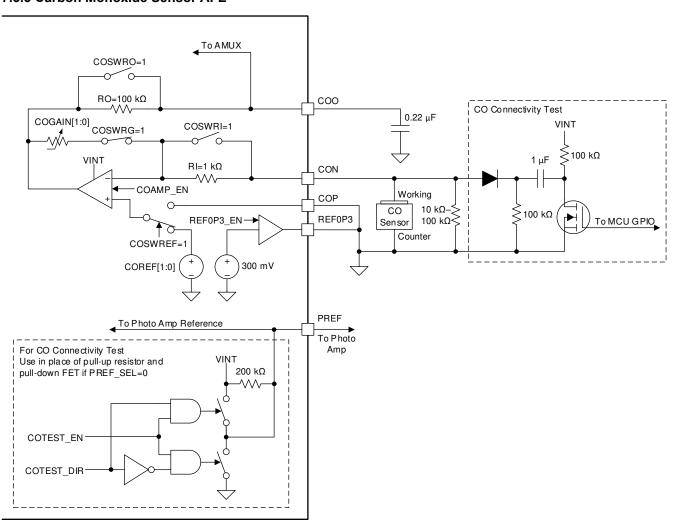

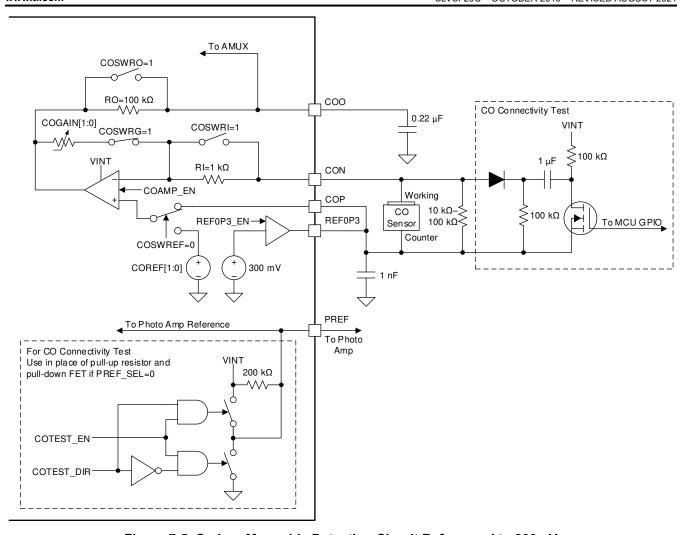

| CO TRANSIM                | PEDANCE AMPLIFIER                                  |                                                                                                                                                                  |       |       |       |       |

| R <sub>I, CO</sub>        | CO input resistance                                | COSWRI = 1                                                                                                                                                       | 0.7   | 1     | 1.5   | kΩ    |

|                           |                                                    |                                                                                                                                                                  |       |       |       |       |

| over operatin           | ng free-air temperature range         |                                                            |       |       |       |      |

|-------------------------|---------------------------------------|------------------------------------------------------------|-------|-------|-------|------|

|                         | PARAMETER                             | TEST CONDITIONS                                            | MIN   | TYP   | MAX   | UNIT |

|                         |                                       | COGAIN[1:0] = 00,<br>COSWRG = 1                            | 770   | 1100  | 1430  | kΩ   |

| R <sub>F, CO</sub>      | CO feedback resistance                | COGAIN[1:0] = 01,<br>COSWRG = 1                            | 210   | 300   | 390   | kΩ   |

| NF, CO                  | CO reeuback resistance                | COGAIN[1:0] = 10,<br>COSWRG = 1                            | 350   | 500   | 650   | kΩ   |

|                         |                                       | COGAIN[1:0] = 11, COSWRG<br>= 1                            | 560   | 800   | 1040  | kΩ   |

| V <sub>IN, COP</sub>    | CO amplifier input voltage (COP pin)  |                                                            | 0     |       | 0.6   | V    |

| V <sub>IN, CON</sub>    | CO amplifier input voltage (CON pin)  |                                                            | 0     |       | 0.6   | V    |

| V <sub>OFFS, CO</sub>   | CO amplifier input offset voltage     |                                                            | -130  | 94    | 300   | μV   |

| V <sub>OUT, COO</sub>   | CO amplifier output voltage (COO pin) |                                                            | 0.1   |       | 2     | V    |

| I <sub>CO, Q</sub>      | CO amplifier quiescent current        |                                                            |       | 0.63  | 2.1   | μΑ   |

| f <sub>CO, BW</sub>     | CO amplifier unity gain bandwidth     |                                                            | 5     | 12    | 20    | kHz  |

| f <sub>CO, CHOP</sub>   | CO amplifier chop frequency           |                                                            | 3.8   | 4     | 4.2   | kHz  |

| R <sub>COO</sub>        | CO amplifier output resistance        | COSWRO = 1                                                 | 70    | 95    | 130   | kΩ   |

|                         | CO amplifier reference voltage        | COSWREF=1, COREF[1:0] = 00, T <sub>J</sub> = 27°C          | 0.89  | 1.14  | 1.47  |      |

|                         |                                       | COSWREF=1, COREF[1:0] = 00, T <sub>J</sub> = -40°C to 85°C | 0.86  | 1.14  | 1.66  |      |

|                         |                                       | COSWREF=1, COREF[1:0] = 01, T <sub>J</sub> = 27°C          | 1.75  | 2.23  | 2.7   |      |

| V                       |                                       | COSWREF=1, COREF[1:0] = 01, T <sub>J</sub> = -40°C to 85°C | 1.7   | 2.23  | 2.95  | mV   |

| V <sub>COPREF</sub>     |                                       | COSWREF=1, COREF[1:0] = 10, T <sub>J</sub> = 27°C          | 2.6   | 3.23  | 4     | IIIV |

|                         |                                       | COSWREF=1, COREF[1:0] = 10, T <sub>J</sub> = -40°C to 85°C | 2.55  | 3.23  | 4.24  |      |

|                         |                                       | COSWREF=1, COREF[1:0] = 11, T <sub>J</sub> = 27°C          | 3.45  | 4.43  | 5.38  |      |

|                         |                                       | COSWREF=1, COREF[1:0] = 11, T <sub>J</sub> = -40°C to 85°C | 3.4   | 4.43  | 5.48  |      |

| R <sub>COTEST, PU</sub> | COTEST pull up FET resistance         |                                                            | 0.36  | 0.76  | 1.1   | kΩ   |

| R <sub>COTEST, PD</sub> | COTEST pull-down FET resistance       |                                                            | 0.25  | 0.37  | 0.82  | kΩ   |

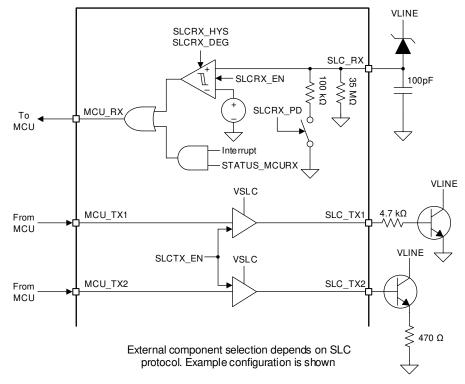

| SLC INTERFA             | ACE                                   |                                                            |       |       |       |      |

|                         |                                       | SLCRX_EN=1, SLCRX_DE<br>G[1:0]=00                          | 0     | 0     | 0.065 |      |

| t                       | SLC receiver deglitch time            | SLCRX_EN=1, SLCRX_DE<br>G[1:0]=01                          | 0.090 | 0.125 | 0.160 | ms   |

| t <sub>SLCRX, DEG</sub> | SEC receiver degritter time           | SLCRX_EN=1, SLCRX_DE<br>G[1:0]=10                          | 0.9   | 1     | 1.1   |      |

|                         |                                       | SLCRX_EN=1, SLCRX_DE<br>G[1:0]=11                          | 19.8  | 20    | 20.2  |      |

| I <sub>SLCRX, Q</sub>   | SLC receiver standby current          | SLCRX_EN = 1                                               |       | 0.25  | 0.5   | uA   |

|                          | g free-air temperature range PARAMETER                              | TEST CONDITIONS                                                                                                                 | MIN  | TYP  | MAX  | UNIT |

|--------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                          | SLC receiver input high                                             | SLCRX HYS=0                                                                                                                     | 1.3  | 2.0  | 2.7  | V    |

| / <sub>SLCRX,IHI</sub>   | threshold voltage                                                   | SLCRX HYS=1                                                                                                                     | 1.3  | 2.0  | 2.7  |      |

|                          | SLC receiver input low                                              | SLCRX_HYS=0                                                                                                                     | 0.5  | 0.8  | 1.1  | V    |

| SLCRX,ILO                | threshold voltage                                                   | SLCRX_HYS=1                                                                                                                     | 1.2  | 1.8  | 2.7  | V    |

|                          |                                                                     | SLCRX HYS=0                                                                                                                     | 0.7  | 1.2  | 1.7  | V    |

| SLCRX,HYS                | SLC receiver input hysteresis                                       | SLCRX_HYS=1                                                                                                                     | 0.01 | 0.2  | 0.3  | V    |

|                          | SLC receiver input pulldown                                         | SLCRX_PD=1                                                                                                                      | 65   | 107  | 165  | kΩ   |

| SLCRX,PD                 | resistance                                                          | SLCRX_PD=0                                                                                                                      | 3.5  | 41   | 56   | ΜΩ   |

| V <sub>SLCTXx</sub> ,OH  | SLC transmitter output high voltage                                 | VSLC=11.5V,<br>I <sub>SLC_TXx</sub> =-16mA                                                                                      | 11.0 | 11.3 | 11.5 | V    |

| / <sub>SLCTXx,OL</sub>   | SLC transmitter output low voltage                                  | VSLC=11.5V, I <sub>SLC_TXx</sub> =16mA                                                                                          | 0    | 0.1  | 0.5  | V    |

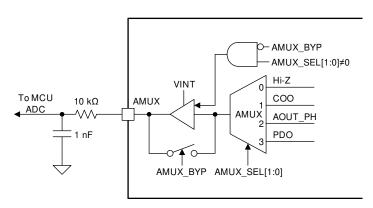

| ANALOG MU                | LTIPLEXER                                                           |                                                                                                                                 |      |      |      |      |

| / <sub>MUX</sub>         | Multiplexer buffer input signal voltage range                       | AMUX_BYP=0                                                                                                                      | 0.05 |      | 2    | V    |

| G <sub>MUX, GAIN</sub>   | Multiplexer bufffer output gain                                     | AMUX_BYP=0                                                                                                                      | 0.99 | 1    | 1.01 | V/V  |

| V <sub>MUX, OFFS</sub>   | Multiplexer buffer offset voltage                                   | AMUX_BYP=0                                                                                                                      | -8   | -0.5 | 8    | mV   |

| MUX, EN                  | Multiplexer buffer enable settling time                             | AMUX_BYP=0, AMUX_SEL stepped from 000 to 011 with PDO=2V, PAMP_EN=0. Time until AMUX reaches 99% of its final value             | 0    | 10   | 15   | us   |

| MUX, STEP                | Multiplexer buffer input step settling time                         | AMUX_BYP=0,<br>AMUX_SEL=011, PDO<br>stepped from 50mV to<br>2V, PAMP_EN=0. Time until<br>AMUX reaches 99% of its<br>final value | 0    | 10   | 15   | us   |

| MUX, BW                  | Multiplexer bandwidth                                               | AMUX_BYP=0                                                                                                                      | 0.5  | 1    | 25   | MHz  |

| MUX, OUT                 | Multiplexer output current                                          | AMUX_BYP=0                                                                                                                      | -10  |      | 10   | uA   |

| MUX, Q                   | Multiplexer quiescent current. Current does not include bias block. | AMUX_BYP=0                                                                                                                      |      | 8.3  | 50   | uA   |

| C <sub>MUX</sub>         | Multiplexer buffer output capacitor required for stability          | AMUX_BYP=0                                                                                                                      | 150  |      | 1000 | pF   |

| OSCILLATOR               | , REFERENCE SYSTEM                                                  |                                                                                                                                 |      |      |      |      |

| OSC8                     | Oscillator frequency                                                |                                                                                                                                 |      | 8    |      | MHz  |

| USU8                     | Frequency accuracy                                                  | T <sub>A</sub> = -10°C to 70°C                                                                                                  | -3   |      | 3    | %    |

| OSC32                    | Low-power Oscillator frequency                                      |                                                                                                                                 |      | 32   |      | kHz  |

|                          | Frequency accuracy                                                  | T <sub>A</sub> = -10°C to 70°C                                                                                                  | -3   |      | 3    | %    |

| Г <sub>ТІМЕОИТ</sub>     | Error timeout time                                                  |                                                                                                                                 | 0.9  | 1    | 1.1  | s    |

| REF0P3, Q                | REF0P3 buffer quiescent current                                     | VCC current difference<br>between REF0P3_EN=0 and<br>REF0P3=1. I <sub>REF0P3</sub> =0 μA                                        |      | 0.38 | 0.76 | μΑ   |

| CREF0P3                  | REF0P3 output capacitor required for stability                      |                                                                                                                                 | 0.7  | 1    | 1.5  | nF   |

| T <sub>REF0P3, SET</sub> | REF0P3 settling time                                                | From REF0P3 enabled to 99% of final output voltage. C <sub>REF0P3</sub> =1nF, I <sub>REF0P3</sub> =0 µA                         |      | 1    | 1.8  | ms   |

|                           | PARAMETER                                                                   | TEST CONDITIONS                                        | MIN                     | TYP  | MAX                    | UNIT |

|---------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------|-------------------------|------|------------------------|------|

| ,                         | DEEODO autout coltano                                                       | I <sub>REF0P3</sub> = 10 μA                            | 270                     | 300  | 330                    | mV   |

| V <sub>REF0P3</sub> , OUT | REF0P3 output voltage                                                       | I <sub>REF0P3</sub> = -25 μA                           | 270                     | 300  | 330                    | mV   |

| vcclow,q                  | VCC_LOW monitor quiescent current                                           |                                                        |                         | 0.9  | 2                      | uA   |

| O BUFFERS                 |                                                                             |                                                        |                         |      | '                      |      |

| V <sub>IO, ILO</sub>      | IO buffer input low threshold                                               | LEDEN, CSEL, MCU_TX1,<br>MCU_TX2, GPIO                 | 0.3×VMCU                |      | 0.7× VMCU              | V    |

| V <sub>IO, IHI</sub>      | IO buffer input high threshold                                              | LEDEN, CSEL, MCU_TX1,<br>MCU_TX2, GPIO                 | 0.3×VMCU                |      | 0.7× VMCU              | V    |

|                           |                                                                             | LEDEN                                                  |                         |      | 100                    | nA   |

| IO, LEAK                  | IO buffer input leakage current                                             | MCU_TX1                                                |                         | ,    | 100                    | nA   |

|                           | Current                                                                     | CSEL                                                   |                         |      | 100                    | nA   |

| V. a.                     | IO be ffer a start level and                                                | MCU_RX, GPIO. IIO = 3 mA,<br>VMCU = 1.8 V              | 0                       | 0.19 | 0.6                    | V    |

| V <sub>IO, OL</sub>       | IO buffer output low-level                                                  | MCU_RX, GPIO. IIO = 1 mA,<br>VMCU = 1.5 V              | 0                       | 0.20 | 0.6                    | V    |

| .,                        | IO buffer output high-level.                                                | MCU_RX, GPIO. I <sub>IO</sub> = -3 mA,<br>VMCU = 1.8 V | 0                       | 0.30 | 0.6                    | V    |

| V <sub>IO, OH</sub>       | Spec is the voltage drop from VMCU (i.e. VMCU - VOH)                        | MCU_RX, GPIO. I <sub>IO</sub> = -1 mA,<br>VMCU = 1.5 V | 0                       | 0.37 | 0.6                    | V    |

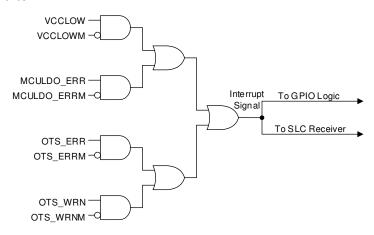

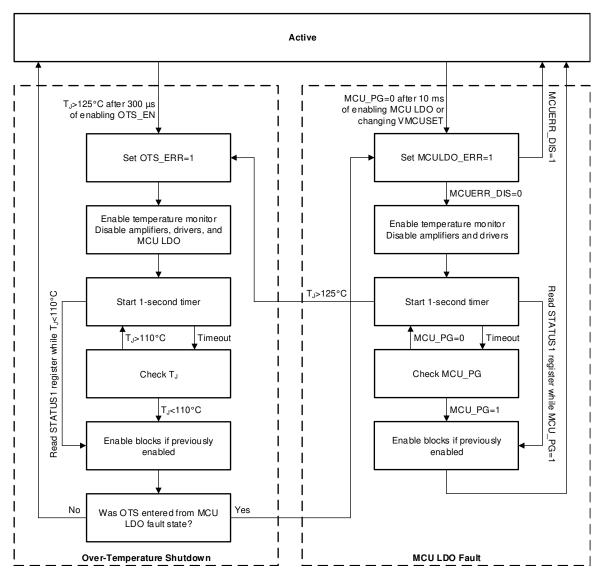

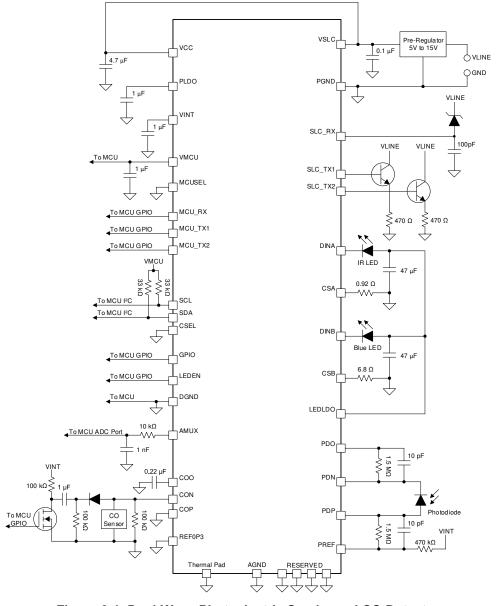

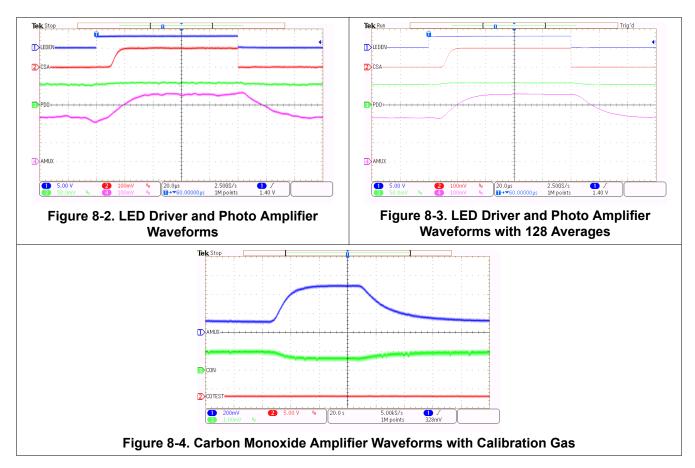

| C <sub>IN, IO</sub>       | Input capacitance                                                           | LEDEN, CSEL                                            |                         | 2    | 10                     | pF   |