Sample &

Buy

Tools &

Software

TSB81BA3E

SLLS783C - MAY 2009 - REVISED MARCH 2016

# TSB81BA3E IEEE 1394b Three-Port Cable Transceiver/Arbiter

Technical

Documents

#### 1 Features

- Fully Supports Provisions of IEEE P1394b Revision 1.33+ at 1-Gigabit Signaling Rates

- Fully Supports Provisions of IEEE 1394a-2000 and 1394-1995 Standard for High Performance Serial Bus

- Fully Interoperable With Firewire, i.LINK, and • SB1394<sup>™</sup>, Implementation of IEEE Std 1394

- Provides Three Fully Backward Compatible, • (1394a-2000 Fully Compliant) Bilingual P1394b Cable Ports at up to 800 Megabits per Second (Mbits/s)

- Provides Three 1394a-2000 Fully Compliant Cable Ports at 100/200/400 Mbits/s

- Full 1394a-2000 Support Includes:

- Connection Debounce

- Arbitrated Short Reset

- Multispeed Concatenation

- Arbitration Acceleration

- \_ Fly-By Concatenation

- Port Disable/Suspend/Resume

- Extended Resume Signaling for Compatibility With Legacy DV Devices

- Power-Down Features to Conserve Energy in **Battery Powered Applications**

- Low-Power Sleep Mode

- Fully Compliant With Open Host Controller • Interface (HCI) Requirements

- Cable Power Presence Monitoring •

- Cable Ports Monitor Line Conditions for Active Connection to Remote Node

- Register Bits Give Software Control of Contender Bit, Power Class Bits, Link Active Control Bit, and 1394a-2000 Features

- Data Interface to Link-Layer Controller Pin ٠ Selectable From 1394a-2000 Mode (2/4/8 Parallel Bits at 49.152 MHz) or 1394b Mode (8 Parallel Bits at 98.304 MHz)

- Interface to Link-Layer Controller Supports Low • Cost TI Bus-Holder Isolation

- Interoperable With Link-Layer Controllers Using 3.3-V Supplies

- Interoperable With Other 1394 Physical Layers

(PHYs) Using 1.8-V, 3.3-V, and 5-V Supplies

- Low Jitter, External Crystal Oscillator Provides Transmit and Receive Data at 100/200/400/800 Mbits/s, and Link-Layer Controller Clock at 49.152 MHz and 98.304 MHz

- Separate Bias (TPBIAS) for Each Port .

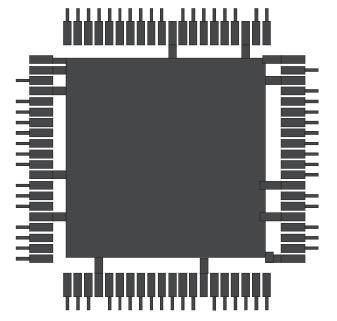

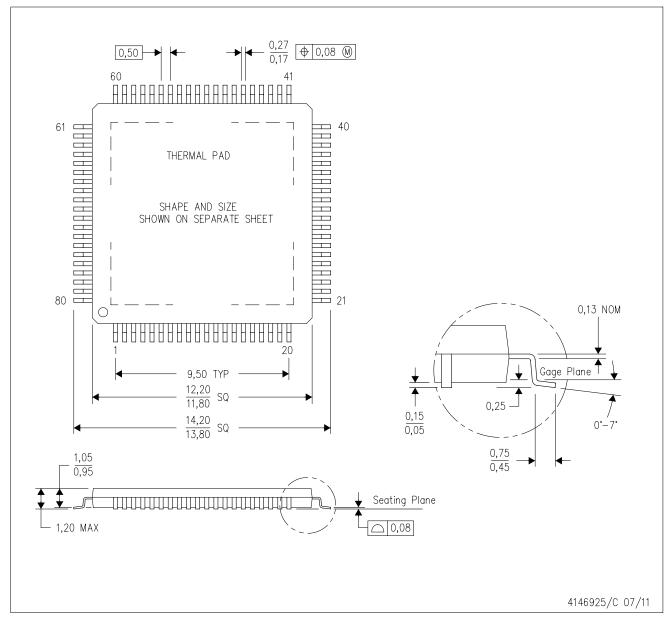

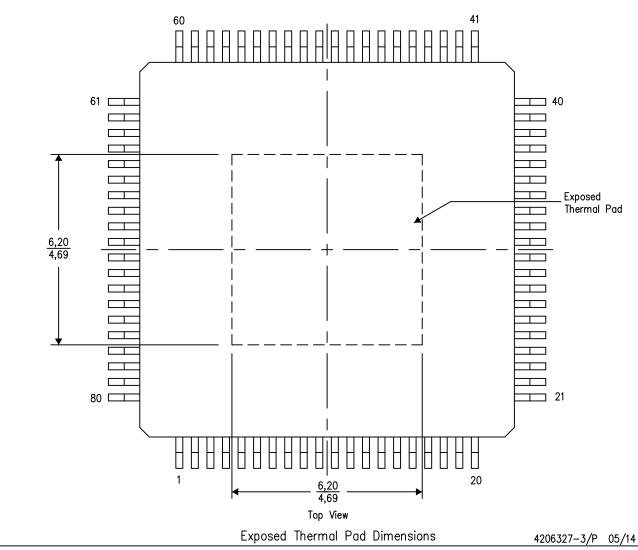

- Low Cost, High Performance 80-Pin TQFP (PFP) • Thermally Enhanced Package and 168-Pin ZAJ (BGA) Package

- Software Device Reset (SWR) ٠

- Fail-Safe Circuitry Senses Sudden Loss of Power to the Device and Disables the Ports to Ensure That the TSB81BA3E Does Not Load the TPBIAS of Any Connected Device and Blocks any Leakage From the Port Back to Power Plane

- The TSB81BA3E Has a 1394a-2000 Compliant Common-Mode Noise Filter on the Incoming Bias Detect Circuit to Filter Out Cross-Talk Noise

- The TSB81BA3E Is Port Programmable to Force 1394a Mode to Allow Use of 1394a Connectors (1394b Signaling Must Not Be Put Across 1394a Connectors or Cables)

- Internal Voltage Regulator Option

## 2 Description

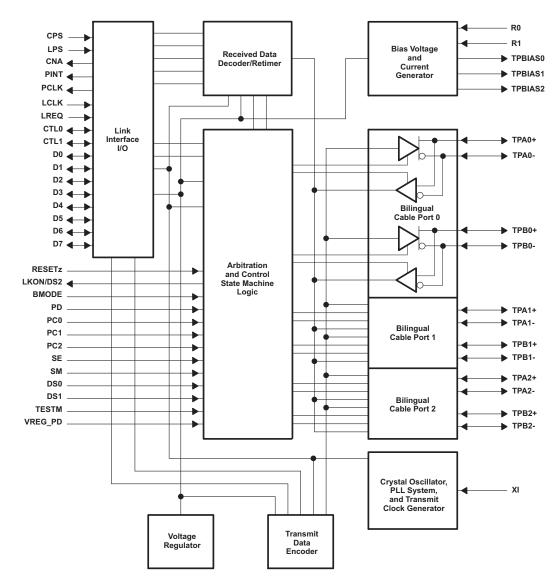

The TSB81BA3E provides the digital and analog transceiver functions needed to implement a threeport node in a cable-based IEEE 1394 network. Each port incorporates two differential cable line transceivers. The transceivers include circuitry to monitor the line conditions as needed for determining connection status, for initialization and arbitration, and packet reception and transmission. for The TSB81BA3E is designed to interface with a link-layer controller (LLC), such the TSB82AA2, as TSB12LV21, TSB12LV26, TSB12LV32, TSB42AA4, TSB42AB4, TSB12LV01B, or TSB12LV01C. It also may be connected cable port to cable port to an integrated 1394 Link + PHY layer such as the TSB43AB2.

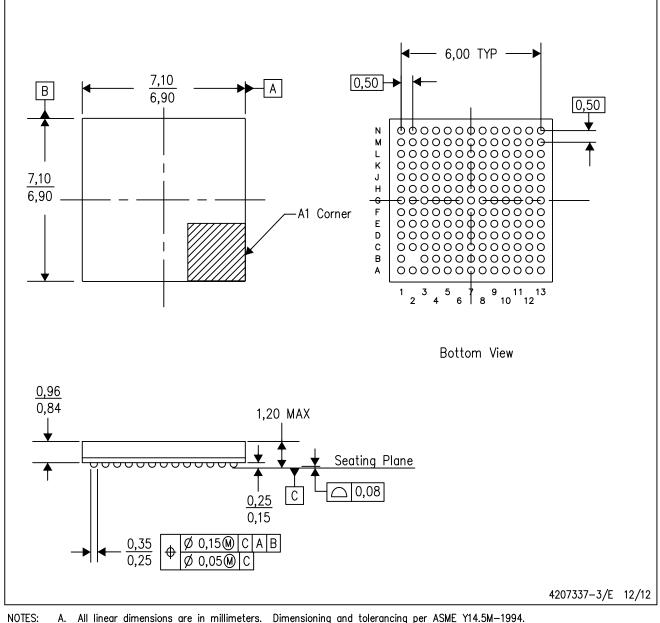

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)     |  |  |  |  |  |  |

|-------------|-------------|---------------------|--|--|--|--|--|--|

| TSB81BA3E   | HTQFP (80)  | 12.00 mm x 12.00 mm |  |  |  |  |  |  |

| ISDOIDAJE   | NFBGA (167) | 12.00 mm x 12.00 mm |  |  |  |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

## **Table of Contents**

| 1 | Feat             | tures 1                                 |  |  |  |  |  |  |  |  |

|---|------------------|-----------------------------------------|--|--|--|--|--|--|--|--|

| 2 | Des              | cription1                               |  |  |  |  |  |  |  |  |

| 3 | Revision History |                                         |  |  |  |  |  |  |  |  |

| 4 | Des              | cription Continued 3                    |  |  |  |  |  |  |  |  |

| 5 | Pin              | Configuration and Function 4            |  |  |  |  |  |  |  |  |

| 6 | Elec             | trical Specfications 10                 |  |  |  |  |  |  |  |  |

|   | 6.1              | Absolute Maximum Ratings 10             |  |  |  |  |  |  |  |  |

|   | 6.2              | Thermal Information 10                  |  |  |  |  |  |  |  |  |

|   | 6.3              | Recommended Operating Conditions 11     |  |  |  |  |  |  |  |  |

|   | 6.4              | Electrical Characteristics, Driver 12   |  |  |  |  |  |  |  |  |

|   | 6.5              | Electrical Characteristics, Receiver 12 |  |  |  |  |  |  |  |  |

|   | 6.6              | Electrical Characteristics, Device 12   |  |  |  |  |  |  |  |  |

|   | 6.7              | Switching Characteristics 13            |  |  |  |  |  |  |  |  |

| 7 | Para             | ameter Measurement Information 14       |  |  |  |  |  |  |  |  |

| 8 | Deta             | ailed Description 15                    |  |  |  |  |  |  |  |  |

|   | 8.1              | Overview 15                             |  |  |  |  |  |  |  |  |

|   | 8.2              | Functional Block Diagram 17             |  |  |  |  |  |  |  |  |

|   | 8.3              | Feature Description 17                  |  |  |  |  |  |  |  |  |

|   | 8.4              | Device Functional Modes 19              |  |  |  |  |  |  |  |  |

|    | 8.5   | Programming                           | 20 |

|----|-------|---------------------------------------|----|

|    | 8.6   | Register Maps                         | 22 |

| 9  | App   | lication and Implementation           | 28 |

|    | 9.1   | Application Information               | 28 |

|    | 9.2   | Typical Application                   | 28 |

| 10 | Pow   | ver Supply Recommendations            | 30 |

| 11 | Laye  | out                                   | 31 |

|    | 11.1  | Layout Guidelines                     | 31 |

| 12 | Dev   | ice and Documentation Support         | 35 |

|    | 12.1  | Device Support                        | 35 |

|    | 12.2  | Related Links                         | 35 |

|    | 12.3  | Community Resources                   | 35 |

|    | 12.4  | Trademarks                            | 35 |

|    | 12.5  | Electrostatic Discharge Caution       | 35 |

|    | 12.6  | Glossary                              | 35 |

| 13 | Mec   | hanical, Packaging, and Orderable     |    |

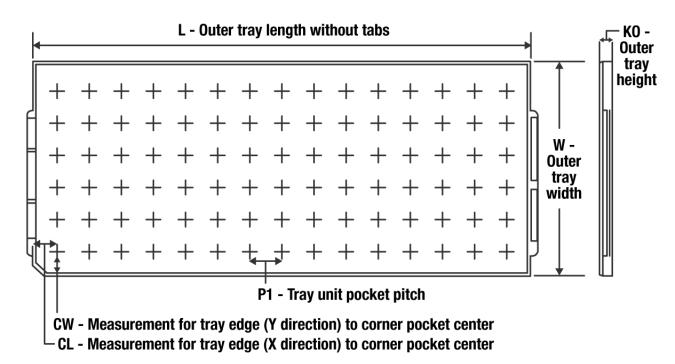

|    | Infor | mation                                | 36 |

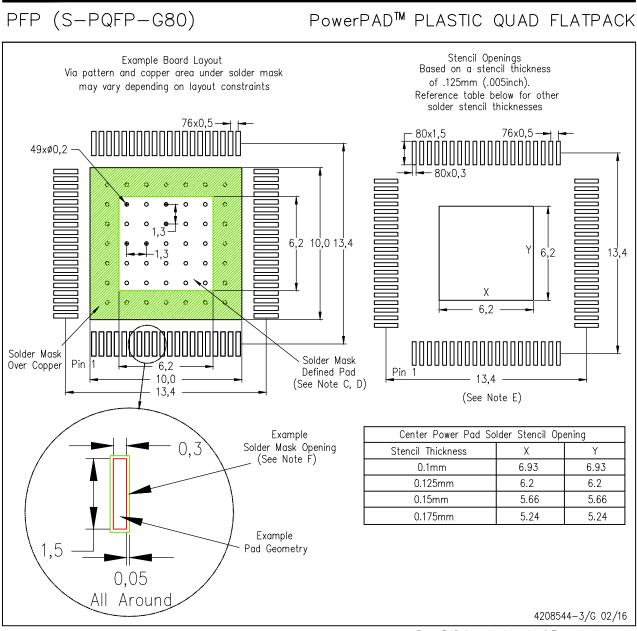

|    |       | Designing With PowerPAD™ Devices (PFP |    |

|    |       | Package Only)                         | 36 |

|    |       |                                       |    |

## 3 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cł | nanges from Revision B (October 2015) to Revision C | Page |

|----|-----------------------------------------------------|------|

| •  | Changed the ADDRESS column of Table 8               | 27   |

| •  | Changed the ADDRESS column of Table 10              | 27   |

## Changes from Revision A (May 2010) to Revision B

| • | Added Feature Description section, Device Functional Modes, Application and Implementation section, Power<br>Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical,<br>Packaging, and Orderable Information section | 1  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| • | Replaced the Dissipation Ratings with the Thermal Information                                                                                                                                                                                                          | 10 |

| • | Changed the Address column of Table 6                                                                                                                                                                                                                                  | 24 |

|   | panges from Original (May 2000) to Povision A                                                                                                                                                                                                                          |    |

|   |                                                                                                                                       | aye |

|---|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| • | Universal change of the pin name from TESTW to VREG_PD                                                                                | 1   |

| • | Deleted paragraph form the TPBIASx pins in the <i>Pin Functions</i> table "When a port is configured as a Beta-mode port (B1, B2, B4: | 9   |

## www.ti.com

## Page

## **4** Description Continued

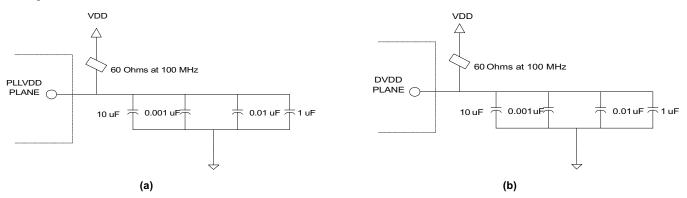

The TSB81BA3E can be powered by a single 3.3-V supply when the VREG\_PD terminal (terminal 73 on the PFP package and terminal B7 on the ZAJ package) is tied to GND. VREG\_PD enables the internal 3.3-V to 1.95-V regulator which provides the 1.95-V to the core. The When VREG\_PD is pulled high to VDD through at least a 1- $k\Omega$  resistor the TSB81BA3E internal regulator is off and the device can be powered by two separate external regulated supplies: 3.3-V for the I/Os and 1.95-V for the core. The core voltage is supplied to the PLLVDD-CORE and DVDD-CORE terminals to the requirements in the recommended operating conditions (1.95-V nominal). The PLLVDD-CORE terminals must be separated from the DVDD-CORE terminals. The PLLVDD-CORE and the DVDD-CORE terminals must be decoupled with 1 uF capacitors to stabilize the respective supply. Additional 0.10  $\mu$ F and 0.01  $\mu$ F high-frequency bypass capacitors may also be used. The separation between DVDD-CORE and PLLVDD-CORE may be implemented by separate power supply rails, or by a single power supply rail, where the DVDD-CORE and PLLVDD-CORE are separated by a filter network to keep noise from the PLLVDD-CORE supply.

The TSB81BA3E requires an external 98.304-MHz crystal oscillator to generate a reference clock. The external clock drives an internal phase-locked loop (PLL), which generates the required reference signal. This reference signal provides the clock signals that control transmission of the outbound encoded information. A 49.152-MHz clock signal is supplied to the associated LLC for synchronization of the two devices and is used for resynchronization of the received data when operating the PHY-link interface in compliance with the IEEE 1394a-2000 standard. A 98.304-MHz clock signal is supplied to the associated LLC for synchronization of the two devices when operating the PHY-link interface in compliance with the IEEE P1394b standard. The power down (PD) function, when enabled by asserting the PD terminal high, stops operation of the PLL.

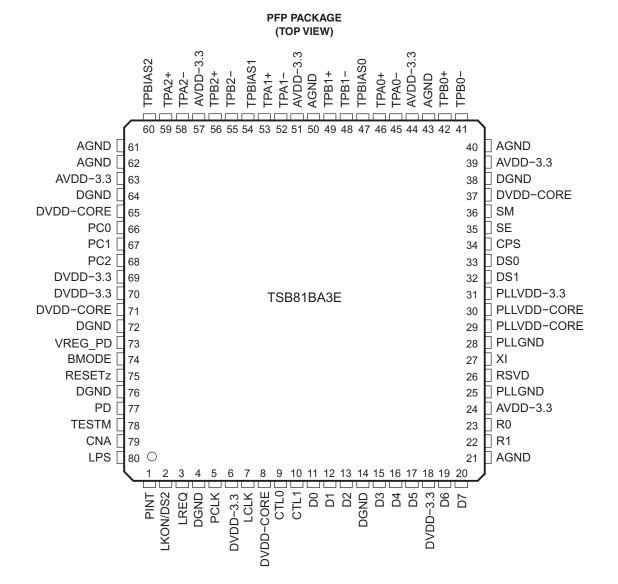

## 5 Pin Configuration and Function

www.ti.com

4

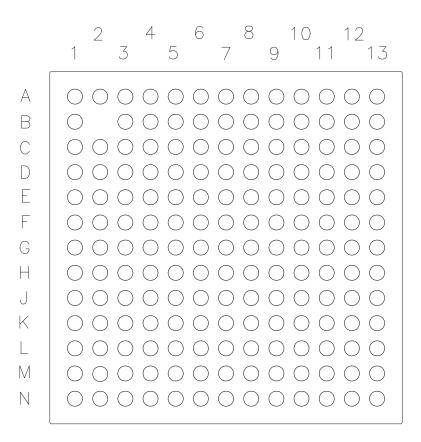

### ZAJ PACKAGE (TOP VIEW)

## TSB81BA3E

SLLS783C - MAY 2009 - REVISED MARCH 2016

www.ti.com

NSTRUMENTS

Texas

## **Pin Functions**

|                     | T)/DE  | PFP                               | ZAJ                                                                                                                   | 1/2 | DECODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|---------------------|--------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                | TYPE   | NO.                               | NO.                                                                                                                   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| AGND <sup>(1)</sup> | Supply | 21, 40, 43, 50,<br>61, 62         | See DGND                                                                                                              | _   | Analog circuit ground terminals. These terminals must be tied together to the low-<br>impedance circuit board ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| AVDD-3.3            | Supply | 24, 39, 44, 51,<br>57, 63         | M4, F10, H10,<br>J10, E10                                                                                             | _   | Analog circuit power terminals. A combination of high-frequency decoupling capacitors near each terminal is suggested, such as paralleled 0.1 $\mu$ F and 0.001 $\mu$ F. Lower frequency 10- $\mu$ F filtering capacitors are also recommended. These supply terminals are separated from the PLLVDD-CORE, PLLVDD-3.3, DVDD-CORE, and DVDD-3.3 terminals internal to the device to provide noise isolation. The PLLVDD-3.3, AVDD, and DVDD-3.3 terminals must be tied together with a low dc impedance connection on the circuit board.    |  |  |

| BMODE               | CMOS   | 74                                | B6                                                                                                                    | I   | Beta-mode input. This terminal determines the PHY-link interface connection protocol. When logic-high (asserted), the PHY-link interface complies with the 1394b-2002 B PHY-link interface. When logic-low (deasserted), the PHY-link interface complies with the legacy 1394a-2000 standard. When using an LLC such as the 1394b-2002 TSB82AA2, this terminal must be pulled high. When using an LLC such as the 1394a-2000 TSB12LV26, this terminal must be tied low.                                                                    |  |  |

|                     |        |                                   |                                                                                                                       |     | NOTE: The PHY-link interface cannot be changed between the different protocols during operation.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| CNA                 | CMOS   | 79                                | A2                                                                                                                    | 0   | Cable not active output. This terminal is asserted high when there are no ports receiving incoming bias voltage. When any port receives bias, this terminal goes low.                                                                                                                                                                                                                                                                                                                                                                      |  |  |

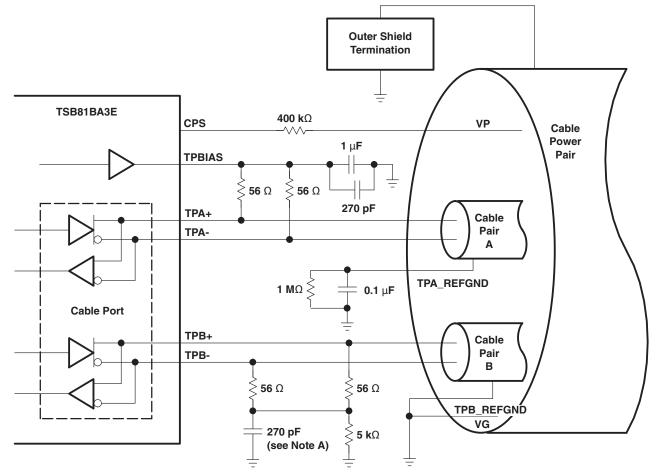

| CPS                 | CMOS   | 34                                | N9                                                                                                                    | I   | Cable-power status input. This terminal is normally connected to cable power through a 400-k $\Omega$ resistor. This circuit drives an internal comparator that detects the presence of cable power. This transition from cable power sensed to cable power not sensed can be used to generate an interrupt to the LLC.                                                                                                                                                                                                                    |  |  |

| CTL0<br>CTL1        | CMOS   | 9<br>10                           | F1<br>G1                                                                                                              | I/O | Control I/Os. These bidirectional signals control communication between the TSB81BA3E and the LLC. Bus holders are built into these terminals.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| D0-D7               | CMOS   | 11, 12, 13, 15,<br>16, 17, 19, 20 | H1, H2, J2, J1,<br>K2, K1, L1, M1                                                                                     | I/O | Data I/Os. These are bidirectional data signals between the TSB82BA3 and the LLC. Bus holders are built into these terminals.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| DGND <sup>(1)</sup> | Supply | 4, 14, 38, 64,<br>72, 76          | E5, F4, F5, F6,<br>F7, F9, G4, G5,<br>G6, G7, G8,<br>G9, G10, H4,<br>H5, H6, H7,<br>H8, J4, J5, J6,<br>J7, J8, K7, L7 | _   | Digital circuit ground terminals. These terminals must be tied together to the low-impedance circuit board ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| DS0                 | CMOS   | 33                                | N8                                                                                                                    | I   | Data-strobe-only mode for port 0. 1394a-only port 0 enable programming terminal. On hardware reset, this terminal allows the user to select whether port 0 acts like a 1394b bilingual port (terminal at logic 0) or as a 1394a-2000-only port (terminal at logic 1). Programming is accomplished by tying the terminal low through a $1 \cdot k\Omega$ or less resistor (to enable 1394b bilingual pode) or high through a $1 \cdot k\Omega$ or less resistor (to enable 1394b bilingual pode). A bus holder is built into this terminal. |  |  |

| DS1                 | CMOS   | 32                                | M7                                                                                                                    | I   | Data-strobe-only mode for port 1. 1394a-only port 1 enable programming terminal. On hardware reset, this terminal allows the user to select whether port 1 acts like a 1394b bilingual port (terminal at logic 0) or as a 1394a-2000-only port (terminal at logic 1). Programming is accomplished by tying the terminal low through a 1-k $\Omega$ or less resistor (to enable 1394b bilingual mode) or high through a 1-k $\Omega$ or less resistor (to enable 1394b bilingual mode). A bus holder is built into this terminal.           |  |  |

| DVDD-CORE           | Supply | 8, 37, 65, 71                     | D9, K9, D8                                                                                                            | -   | Digital core circuit power terminals. A combination of high-frequency decoupling capacitors near each terminal is suggested, such as paralleled 0.1 $\mu$ F and 0.001 $\mu$ F. An additional 1- $\mu$ F capacitor is required for voltage regulation. These supply terminals are separated from the DVDD-3.3, PLLVDD-CORE, PLLVDD-3.3, and AVDD terminals internal to the device to provide noise isolation.                                                                                                                               |  |  |

(1) All AGND and DGND terminals are internally tied together in the ZAJ package.

## Pin Functions (continued)

|          | TYPE   | PFP           | ZAJ        | 10  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------|--------|---------------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME     | TYPE   | NO.           | NO.        | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| DVDD-3.3 | Supply | 6, 18, 69, 70 | E4, K5, K6 | _   | Digital 3.3-V circuit power terminals. A combination of high-frequency decoupling capacitors near each terminal is suggested, such as paralleled 0.1 $\mu$ F and 0.001 $\mu$ F. Lower-frequency 10- $\mu$ F filtering capacitors are also recommended. The DVDD-3.3 terminals must be tied together at a low-impedance point on the circuit board. These supply terminals are separated from the PLLVDD-CORE, PLLVDD-3.3, DVDD-CORE, and AVDD terminals internal to the device to provide noise isolation. The PLLVDD-3.3, AVDD, and DVDD-3.3 terminals must be tied together with a low dc impedance connection on the circuit board. |  |

| LCLK     | CMOS   | 7             | G2         | I   | Link clock. Link-provided 98.304-MHz clock signal to synchronize data transfers from link to the PHY when the PHY-link interface is in the 1394b mode. A bus holder is built into this terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|          |        |               |            |     | Link-on output/Data-strobe-only input for port 2. This terminal may be connected to the link-on input terminal of the LLC through a $1-k\Omega$ resistor if the link-on input is available on the link layer.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|          |        | CMOS 2        | D2         | I/O | Data-strobe-only mode for port 2. 1394a-only port 0 enable programming terminal. On hardware reset, this terminal allows the user to select whether port 2 acts like a 1394b bilingual port (terminal at logic 0) or as a 1394a-2000-only port (terminal at logic 1). Programming is accomplished by tying the terminal low through a 1-k $\Omega$ or less resistor to enable 1394b bilingual mode or high through a 1-k $\Omega$ or less resistor to enable 1394a-2000-only mode. A bus holder is built into this terminal.                                                                                                           |  |

|          |        |               |            |     | After hardware reset, this terminal is the link-on output, which notifies the LLC or other power-up logic to power up and become active. The link-on output is a square wave signal with a period of approximately 163 ns (8 PCLK cycles) when active. The link-on output is otherwise driven low, except during hardware reset when it is high impedance.                                                                                                                                                                                                                                                                             |  |

| LKON/DS2 | CMOS   |               |            |     | The link-on output is activated if the LLC is inactive (the LPS input inactive or the LCtrl bit cleared) and when one:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|          |        |               |            |     | a. The PHY receives a link-on PHY packet addressed to this node.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|          |        |               |            |     | b. The PEI (port-event interrupt) register bit is 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|          |        |               |            |     | c. Any of the CTOI (configuration-timeout interrupt), CPSI (cable-power-status interrupt), or STOI (state-time-out interrupt) register bits is 1 and the RPIE (resuming-port interrupt enable) register bit is also 1.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|          |        |               |            |     | d. The PHY is power-cycled and the power class is 0 through 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|          |        |               |            |     | Once activated, the link-on output is active until the LLC becomes active (both the LPS input active and the LCtrl bit set). The PHY also deasserts the link-on output when a bus-reset occurs unless the link-on output is otherwise active because one of the interrupt bits is set (that is, the link-on output is active due solely to the reception of a link-on PHY packet).                                                                                                                                                                                                                                                     |  |

|          |        |               |            |     | In the case of power-cycling the PHY, the LKON signal must stop after 167 $\mu s$ if the preceding conditions have not been met.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|          |        |               |            |     | NOTE: If an interrupt condition exists, which otherwise would cause the link-<br>on output to be activated if the LLC were inactive, then the link-on output is<br>activated when the LLC subsequently becomes inactive.                                                                                                                                                                                                                                                                                                                                                                                                               |  |

TSB81BA3E SLLS783C – MAY 2009– REVISED MARCH 2016 TEXAS INSTRUMENTS

www.ti.com

## Pin Functions (continued)

| NAME              | TYPE   | PFP ZAJ        |                 | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-------------------|--------|----------------|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                   | TYPE   | NO.            | NO.             | 10  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

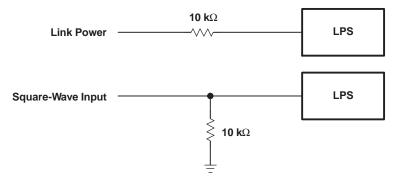

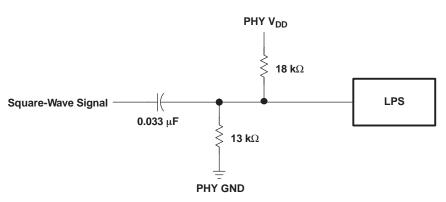

|                   |        |                |                 |     | Link power status input. This terminal monitors the active/power status of the link-layer controller (LLC) and controls the state of the PHY-LLC interface. This terminal must be connected to either the $V_{DD}$ supplying the LLC through an approximately 1-k $\Omega$ resistor or to a pulsed output that is active when the LLC is powered. A pulsed signal must be used when an isolation barrier exists between the LLC and PHY (see Figure 8). The LPS input is considered inactive if it is sampled low by the PHY for more than an LPS_RESET time (~2.6 µs), and is considered active otherwise (that is, asserted steady high or an oscillating signal with a low time less than 2.6 µs). The LPS input must be high for at least 22 ns to be observed as high by the PHY. |  |  |

| LPS               | CMOS   | 80             | D3              | 1   | When the TSB81BA3E detects that the LPS input is inactive, it places the PHY-LLC interface into a low-power reset state. In the reset state, the CTL (CTL0 and CTL1) and D (D0 to D7) outputs are held in the logic 0 state and the LREQ input is ignored; however, the PCLK output remains active. If the LPS input remains low for more than an LPS_DISABLE time (~26 $\mu$ s), then the PHY-LLC interface is put into a low-power disabled state in which the PCLK output is also held inactive.                                                                                                                                                                                                                                                                                    |  |  |

|                   |        |                |                 |     | The LLC state that is communicated in the self-ID packet is considered active only if both the LPS input is active and the LCtrl register bit is set to 1. The LLC state that is communicated in the self-ID packet is considered inactive if either the LPS input is inactive or the LCtrl register bit is cleared to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| LREQ              | CMOS   | 3              | E1              | Ι   | LLC request input. The LLC uses this input to initiate a service request to the TSB81BA3E. A bus holder is built into this terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| PC0<br>PC1<br>PC2 | CMOS   | 66<br>67<br>68 | C11<br>A9<br>B8 | I   | Power class programming inputs. On hardware reset, these inputs set the default value of the power class indicated during self-ID. Programming is done by tying the terminals high through a $1-k\Omega$ or smaller resistor or by tying directly to ground through a $1-k\Omega$ or smaller resistor. Bus holders are built into these terminals.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| PCLK              | CMOS   | 5              | F2              | 0   | PHY clock. Provides a 98.304-MHz clock signal, synchronized with data transfers, to the LLC when the PHY-link interface is operating in the 1394b mode (BMODE asserted). PCLK output provides a 49.152-MHz clock signal, synchronized with data transfers, to the LLC when the PHY-link interface is in legacy 1394a-2000 (BMODE input deasserted).                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| PD                | CMOS   | 77             | B3              | I   | Power-down input. A high on this terminal turns off all internal circuitry except the cable-active monitor circuits, which control the CNA output. Asserting the PD input high also activates an internal pulldown on the RESET terminal to force a reset of the internal control logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| PINT              | CMOS   | 1              | E3              | ο   | PHY interrupt. The PHY uses this output to serially transfer status and interrupt information to the link when PHY-link interface is in the 1394b mode. A bus holder is built into this terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| PLLGND            | Supply | 25, 28         | F8, N4          | -   | PLL circuit ground terminals. These terminals must be tied together to the low-impedance circuit board ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| PLLVDD-<br>CORE   | Supply | 29, 30         | N6              | _   | PLL core circuit power terminals. A combination of high-frequency decoupling capacitors near each terminal is suggested, such as paralleled 0.1 $\mu$ F and 0.001 $\mu$ F. An additional 1- $\mu$ F capacitor is required for voltage regulation. The PLLVDD-CORE terminals must be separate from the DVDD-CORE terminals. These supply terminals are separated from the DVDD-CORE, DVDD-3.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| PLLVDD-3.3        | Supply | 31             | N7              | _   | PLL 3.3-V circuit power terminal. A combination of high-frequency decoupling capacitors near the terminal are suggested, such as paralleled 0.1 $\mu$ F and 0.001 $\mu$ F. Lower frequency 10- $\mu$ F filtering capacitors are also recommended. This supply terminal is separated from the DVDD-CORE, DVDD-3.3, PLLVDD-CORE, and AVDD-3.3 terminals internal to the device to provide noise isolation. The DVDD-3.3 terminals must be tied together at a low-impedance point on the circuit board. The PLLVDD-3.3, AVDD-3.3, and DVDD-3.3 terminals must be tied together with a low dc impedance connection.                                                                                                                                                                        |  |  |

## Pin Functions (continued)

|                                  | TYPE    | PFP                  | ZAJ                      |       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|----------------------------------|---------|----------------------|--------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                             | TYPE    | NO.                  | NO.                      | - I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| RESET                            | CMOS    | 75                   | A6                       | I     | Logic reset input. Asserting this terminal low resets the internal logic. An internal pullup resistor to $V_{DD}$ is provided so only an external delay capacitor is required for proper power-up operation (see <i>power-up reset</i> in the <i>Applications Information</i> section).<br>The RESET terminal also incorporates an internal pulldown, which is activated when the PD input is asserted high. This input is otherwise a                                                                                                                                                                         |  |  |

| RSVD                             | Osc Out | 26                   | M5                       | 0     | standard logic input, and can also be driven by an open-drain-type driver.<br>This terminal must normally be left unconnected. When this terminal is probed, the terminal shows a 98.304-MHz signal. If this is perceived as an EMI problem, then the terminal may be pulled to ground through a $10-k\Omega$ resistor. However, this causes an increase of up to 340 µA in device current consumption.                                                                                                                                                                                                        |  |  |

| R0<br>R1                         | Bias    | 23<br>22             | N3<br>N2                 | -     | Current setting resistor terminals. These terminals are connected to a precision external resistance to set the internal operating currents and cable driver output currents. A resistance of 6.34 k $\Omega$ , ±1%, is required to meet the IEEE Std 1394-1995 output voltage limits.                                                                                                                                                                                                                                                                                                                         |  |  |

| SE                               | CMOS    | 35                   | M10                      | I     | Test control input. This input is used in the manufacturing test of the TSB81BA3E. For normal use this terminal must be pulled low either through a 1-k $\Omega$ resistor to GND or directly to GND.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| SM                               | смоѕ    | 36                   | N10                      | I     | Test control input. This input is used in the manufacturing test of the TSB81BA3E. For normal use this terminal must be pulled low either through a 1-k $\Omega$ resistor to GND or directly to GND.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| TESTM                            | CMOS    | 78                   | A3                       | I     | Test control input. This input is used in the manufacturing test of the TSB81BA3E. For normal use this terminal must be pulled high through a 1- $k\Omega$ resistor to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| VREG_PD                          | CMOS    | 73                   | B7                       | I     | Voltage regulator power-down input. When asserted logic high, this pin will power-<br>down the internal 3.3-V to 1.95-V regulator. For single 3.3-V supply operation, this pin<br>should be tied to GND. If an external regulator is used to supply the 1.95-V PLLVDD-<br>CORE and DVDD-CORE power rails this terminals should be pulled to Vcc through a<br>$1-k\Omega$ resistor to V <sub>DD</sub> .                                                                                                                                                                                                         |  |  |

| TPA0–<br>TPA0+<br>TPB0–<br>TPB0+ | Cable   | 45<br>46<br>41<br>42 | K13<br>J13<br>M13<br>L13 | I/O   | Port-0 twisted-pair differential-signal terminals. Board traces from each pair of positive and negative differential signal terminals must be kept matched and as short as possible to the external load resistors and to the cable connector. Request the S800 1394b layout recommendations document from your Texas Instruments representative.                                                                                                                                                                                                                                                              |  |  |

| TPA1–<br>TPA1+<br>TPB1–<br>TPB1+ | Cable   | 52<br>53<br>48<br>49 | F13<br>E13<br>H13<br>G13 | I/O   | Port-1 twisted-pair differential-signal terminals. Board traces from each pair of positive and negative differential signal terminals must be kept matched and as short as possible to the external load resistors and to the cable connector. Request the S800 1394b layout recommendations document from your Texas Instruments representative.                                                                                                                                                                                                                                                              |  |  |

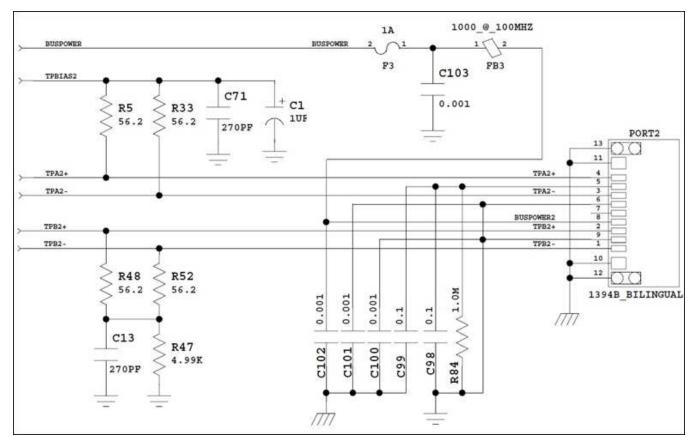

| TPA2–<br>TPA2+<br>TPB2–<br>TPB2+ | Cable   | 58<br>59<br>55<br>56 | B13<br>A13<br>D13<br>C13 | I/O   | Port-2 twisted-pair differential-signal terminals. Board traces from each pair of positive and negative differential signal terminals must be kept matched and as short as possible to the external load resistors and to the cable connector. Request the S800 1394b layout recommendations document from your Texas Instruments representative.                                                                                                                                                                                                                                                              |  |  |

| TPBIAS0<br>TPBIAS1<br>TPBIAS2    | Cable   | 47<br>54<br>60       | J12<br>E12<br>A12        | I/O   | Twisted-pair bias output and signal detect input. This provides the 1.86-V nominal bias voltage needed for proper operation of the twisted-pair cable drivers and receivers, and for signaling to the remote nodes that there is an active cable connection in 1394a-2000 mode. Each of these terminals, except for an unused port, must be decoupled with a 1- $\mu$ F capacitor to ground. For the unused port, this terminal can be left unconnected. Please request the S800 1394b layout recommendation documents from your TI representative.                                                            |  |  |

| xı                               | Osc In  | 27                   | N5                       | -     | Oscillator input. This terminal connects to a 98.304-MHz low jitter external oscillator. The XI terminal is a 1.8-V CMOS input. Oscillator jitter must be 5 ps RMS or better. If only 3.3-V oscillators can be acquired, then great care must be taken to not introduce significant jitter by the means used to level shift from 3.3 V to 1.8 V. If a resistor divider is used, then a high current oscillator and low-value resistors must be used to minimize RC time constants. If a level-shifting circuit is used, then it must introduce very little jitter. Please see layout recommendations document. |  |  |

## 6 Electrical Specfications

## 6.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                  |                                                      |             | MIN                   | MAX          | UNIT |

|------------------|------------------------------------------------------|-------------|-----------------------|--------------|------|

| $V_{DD}$         | Supply voltage range <sup>(2)</sup>                  | -0.3        | 4                     | V            |      |

| VI               | Input voltage range <sup>(2)</sup>                   | -0.5        | V <sub>DD</sub> + 0.5 | V            |      |

| Vo               | Output voltage range at any output                   | -0.5        | $V_{DD}$ + 0.5        | V            |      |

|                  | Continuous total power dissipation                   | See [       | Dissipation Ra        | atings Table |      |

| т                | Operating free air temperature                       | TSB81BA3E   | 0                     | 70           | °C   |

| T <sub>A</sub>   | Operating free-air temperature                       | -40         | 85                    | U            |      |

| T <sub>stg</sub> | Storage temperature range                            | ature range |                       |              |      |

|                  | Lead temperature 1.6 mm (1/16 in) from case for 10 s |             | 260                   | ů            |      |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values, except differential I/O bus voltages, are with respect to network ground.

## 6.2 Thermal Information

|                       |                                              |                                                                               | TSB8 <sup>2</sup> | IBA3E    |      |

|-----------------------|----------------------------------------------|-------------------------------------------------------------------------------|-------------------|----------|------|

|                       | THERMAL MET                                  | PFP<br>(HTQFP)                                                                | ZJA<br>(NFBGA)    | UNIT     |      |

|                       |                                              |                                                                               |                   | 167 PINS |      |

| $R_{\theta J A}$      | Junction-to-ambient thermal resistance       | Low K JEDEC Test Board, 1s (single signal layer), no air flow                 | 27.2              | 46.2     | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | High K JEDEC Test Board 2s2p (double signal layer, double buried power plane) | 8.9               | 23.5     | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | Cu Cold Plate Measurement Process                                             | 11.1              | 27.8     | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | EIA/JESD 51-8                                                                 | 0.3               | 0.45     | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | EIA/JESD 51-2                                                                 | 11.0              | 27.4     | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | EIA/JESD 51-6                                                                 | 0.3               | N/A      | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 6.3 Recommended Operating Conditions

|                         |                                     |                                                  | MIN                      | TYP <sup>(1)</sup> | MAX                  | UNIT |

|-------------------------|-------------------------------------|--------------------------------------------------|--------------------------|--------------------|----------------------|------|

| 221/                    | Supply voltage                      | Source power node                                | 3.0                      | 3.3                | 3.6                  | V    |

| 5.5 V <sub>DD</sub>     | Supply voltage                      | Nonsource power node                             | 3.0 <sup>(2)</sup>       | 3.3                | 3.6                  | v    |

| Core<br>V <sub>DD</sub> | Supply voltage                      |                                                  | 1.85                     | 1.95               | 2.05                 | V    |

|                         |                                     | LREQ, CTL0, CTL1, D0-D7, LCLK                    | 2.6                      |                    |                      |      |

| V <sub>IH</sub>         | High-level input voltage            | LKON/DS2, PC0, PC1, PC2, PD, BMODE               | 0.7 ×<br>V <sub>DD</sub> |                    |                      | V    |

|                         |                                     | RESETz                                           | 0.6 ×<br>V <sub>DD</sub> |                    |                      |      |

|                         |                                     | LREQ, CTL0, CTL1, D0-D7, LCLK                    |                          |                    | 1.2                  |      |

| V <sub>IL</sub>         | Low-level input voltage             | LKON/DS2, PC0, PC1, PC2, PD, BMODE               |                          |                    | $0.2 \times V_{DD}$  | V    |

|                         |                                     | RESETz                                           |                          |                    | $0.3 \times V_{DD}$  |      |

| V <sub>OD</sub>         | 1394b Differential output voltage   |                                                  |                          | 700                |                      | mV   |

| V <sub>CM</sub>         | 1394b Common-mode output voltage    |                                                  |                          | 1.5                |                      | V    |

| I <sub>DD</sub>         | Supply current in low               | V <sub>D D</sub> = 3.3 V                         |                          | 4                  |                      | mA   |

|                         | power/suspend <sup>(3)</sup>        | $V_{D D} = 3 V$                                  |                          | 3                  |                      | mA   |

| I <sub>OL/OH</sub>      | Output current                      | CTL0, CTL1, D0-D7, CNA, LKON/DS2, PINT, and PCLK | -4                       |                    | 4                    | mA   |

| I <sub>O</sub>          | Output current                      | TPBIAS outputs                                   | -5.6                     |                    | 1.3                  | mA   |

| T <sub>A</sub>          | Operating ambient temperature range | TSB81BA3E                                        | 0                        |                    | 70                   | °C   |

| TJ                      | Junction temperature <sup>(4)</sup> | TSB81BA3E                                        | 0                        |                    | 105                  | °C   |

| V <sub>ID</sub>         | 1394b Differential input voltage    | Cable inputs, during data reception              | 200                      |                    | 800                  | mV   |

| V                       | 1204a Differential input voltage    | Cable inputs, during data reception              | 118                      |                    | 260                  | mV   |

| V <sub>ID</sub>         | 1394a Differential input voltage    | Cable inputs, during arbitration                 | 168                      |                    | 265                  | mv   |

| V                       | 1394a Common-mode input             | TPB cable inputs, source power node              | 0.4706                   |                    | 2.515                | V    |

| V <sub>IC</sub>         | voltage                             | TPB cable inputs, nonsource power node           | 0.4706                   |                    | 2.015 <sup>(2)</sup> | v    |

| t <sub>pu</sub>         | Power-up reset time                 | RESETz input                                     | 2 <sup>(5)</sup>         |                    |                      | ms   |

|                         |                                     | TPA, TPB cable inputs, S100 operation            |                          |                    | ±1.08                |      |

|                         | Receive input jitter                | TPA, TPB cable inputs, S200 operation            |                          |                    | ±0.5                 | ns   |

|                         |                                     | TPA, TPB cable inputs, S400 operation            |                          |                    | ±0.315               |      |

|                         |                                     | Between TPA and TPB cable inputs, S100 operation |                          |                    | ±0.8                 |      |

|                         | Receive input skew                  | Between TPA and TPB cable inputs, S200 operation |                          |                    | ±0.55                | ns   |

|                         |                                     | Between TPA and TPB cable inputs, S400 operation |                          |                    | ±0.5                 |      |

(1) All typical values are at  $V_{DD}$  = 3.3 V and  $T_A$  = 25°C. (2) For a node that does not source power, see Section 4.2.2.2 in IEEE 1394a-2000.

(3) (4) The low power/suspend mode assumes that the device is not receiving packets and it is toning. The junction temperature reflects simulated conditions. The customer is responsible for verifying junction temperature.

Time after valid clock received at PHY XI input terminal. (5)

STRUMENTS

EXAS

## 6.4 Electrical Characteristics, Driver

over recommended ranges of operating conditions (unless otherwise noted)

|                    | PARAMETER                                         | TEST CONDITIONS                      | MIN                  | TYP MAX              | UNIT |

|--------------------|---------------------------------------------------|--------------------------------------|----------------------|----------------------|------|

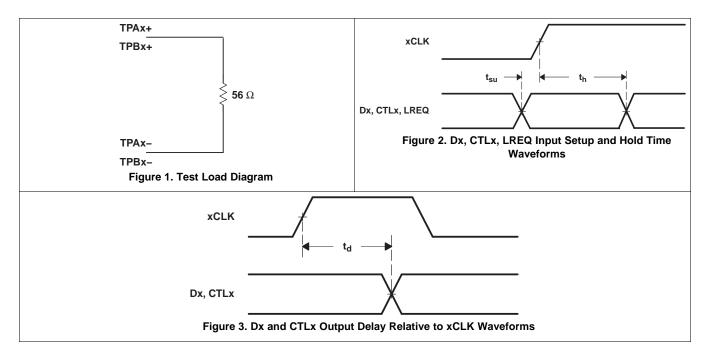

| V <sub>OD</sub>    | Differential output voltage                       | 56 Ω, See Figure 1                   | 172                  | 265                  | mV   |

| I <sub>DIFF</sub>  | Driver difference current, TPA+, TPA-, TPB+, TPB- | Drivers enabled, speed signaling off | -1.05 <sup>(1)</sup> | 1.05 <sup>(1)</sup>  | mA   |

| I <sub>SP200</sub> | Common-mode speed signaling current, TPB+, TPB–   | S200 speed signaling enabled         | -4.84 <sup>(2)</sup> | -2.53 <sup>(2)</sup> | mA   |

| I <sub>SP400</sub> | Common-mode speed signaling current, TPB+, TPB–   | S400 speed signaling enabled         | -12.4 <sup>(2)</sup> | -8.1 <sup>(2)</sup>  | mA   |

| V <sub>OFF</sub>   | Off-state differential voltage                    | Drivers disabled, See Figure 1       |                      | 20                   | mV   |

(1) Limits defined as algebraic sum of TPA+ and TPA- driver currents. Limits also apply to TPB+ and TPB- algebraic sum of driver currents.

(2) Limits defined as absolute limit of each of TPB+ and TPB- driver currents.

## 6.5 Electrical Characteristics, Receiver

|                       | PARAMETER                                         | TEST CONDITIONS                 | MIN  | TYP | MAX | UNIT |

|-----------------------|---------------------------------------------------|---------------------------------|------|-----|-----|------|

| 7                     | Differential impedance                            | Drivers disabled                | 4    | 7   |     | kΩ   |

| Z <sub>ID</sub>       | Differential impedance                            | Drivers disabled                |      |     | 4   | pF   |

| 7                     | Common-mode impedance                             | Drivers disabled                | 20   |     |     | kΩ   |

| Z <sub>IC</sub>       | Common-mode impedance                             | Drivers disabled                |      |     | 24  | pF   |

| V <sub>TH-R</sub>     | Receiver input threshold voltage                  | Drivers disabled                | -30  |     | 30  | mV   |

| V <sub>TH-CB</sub>    | Cable bias detect threshold, TPBx cable inputs    | Drivers disabled                | 0.6  |     | 1   | V    |

| V <sub>TH+</sub>      | Positive arbitration comparator threshold voltage | Drivers disabled                | 89   |     | 168 | mV   |

| V <sub>TH-</sub>      | Negative arbitration comparator threshold voltage | Drivers disabled                | -168 |     | -89 | mV   |

| V <sub>TH-SP200</sub> | Speed signal threshold                            | TPBIAS-TPA common-mode voltage, | 49   |     | 131 | mV   |

| V <sub>TH-SP400</sub> | Speed signal threshold                            | drivers disabled                | 314  |     | 396 | mV   |

## 6.6 Electrical Characteristics, Device

|                   | PARAMETER                                                                              | TEST CON                                     | IDITIONS                                 | MIN                    | TYP   | MAX  | UNIT |     |

|-------------------|----------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------|------------------------|-------|------|------|-----|

|                   | Supply surrent                                                                         | 3.3 V <sub>DD</sub>                          | (1)                                      |                        |       | 120  | 150  | ~ 1 |

| IDD               | Supply current                                                                         | Core V <sub>DD</sub>                         |                                          |                        |       | 79   |      | mA  |

| V <sub>TH</sub>   | Power status threshold, CPS input <sup>(2)</sup>                                       |                                              | 400-kΩ resistor <sup>(2)</sup>           |                        | 4.7   |      | 7.5  | V   |

| V <sub>OH</sub>   | V <sub>OH</sub> High-level output voltage, CTL0, CTL1, D0-D7, PCLK, LKON/DS2 outputs   |                                              |                                          |                        | 2.8   |      |      | V   |

| V <sub>OL</sub>   | V <sub>OL</sub> Low-level output voltage, CTL0, CTL1, D0-D7, PCLK,<br>LKON/DS2 outputs |                                              |                                          | I <sub>OL</sub> = 4 mA |       |      | 0.4  | V   |

| I <sub>BH+</sub>  | Positive peak bus holder current, D0-D7,                                               | $V_{DD} = 3.6 V,$<br>$V_{I} = 0 V to V_{DD}$ | 0.05                                     |                        | 1     | mA   |      |     |

| I <sub>BH</sub>   | Negative peak bus holder current, D0-D7<br>LREQ                                        | $V_{DD} = 3.6 V,$<br>$V_{I} = 0 V to V_{DD}$ |                                          | -1.0                   | -     | 0.05 | mA   |     |

|                   | Off-state output current, CTL0, CTL1, D0                                               | -D7, LKON/DS2                                |                                          | TSB81BA3E              |       |      | ±5   |     |

| I <sub>OZ</sub>   | <sup>oz</sup> I/Os                                                                     |                                              | $V_{O} = V_{DD} \text{ or } 0 \text{ V}$ | TSB81BA3EI             |       |      | ±20  | μA  |

| I <sub>IRST</sub> | I <sub>IRST</sub> Pullup current, RESET input                                          |                                              |                                          |                        | -90   |      | -20  | μA  |

| Vo                | TPBIAS output voltage                                                                  |                                              | At rated I <sub>O</sub> current          |                        | 1.665 | 2    | .015 | V   |

Repeat max packet (one port receiving maximum size isochronous packet–8192 bytes, sent on every isochronous interval, S800, data value of 0xCCCCCCCh; two ports repeating; all ports with beta-mode connection), V<sub>DD3.3</sub> = 3.3 V, V<sub>DDCORE</sub> = 1.95 V, T<sub>A</sub> = 25°C.

(2) Measured at cable-power side of resistor.

## 6.7 Switching Characteristics

|                 | PARAMETER                                            |                         | TEST        | CONDITIONS        | MIN | TYP | MAX | UNIT |

|-----------------|------------------------------------------------------|-------------------------|-------------|-------------------|-----|-----|-----|------|

| t <sub>r</sub>  | TP differential rise time, transmit                  |                         | 10% to 90%, | At 1394 connector | 0.5 |     | 1.2 | ns   |

| t <sub>f</sub>  | TP differential fall time, transmit                  |                         | 90% to 10%, | At 1394 connector | 0.5 |     | 1.2 | ns   |

| t <sub>su</sub> | Setup time,<br>CTL0, CTL1, D1-D7, LREQ to PCLK       | 1394a-2000              | 50% to 50%, | See Figure 2      | 2.5 |     |     | ns   |

| t <sub>h</sub>  | Hold time,<br>CTL0, CTL1, D1-D7, LREQ after PCLK     | 1394a-2000              | 50% to 50%, | See Figure 2      | 0   |     |     | ns   |

| t <sub>su</sub> | Setup time,<br>CTL0, CTL1, D1-D7, LREQ to LCLK_PMC   | 1394b                   | 50% to 50%, | See Figure 2      | 2.5 |     |     | ns   |

| t <sub>h</sub>  | Hold time,<br>CTL0, CTL1, D1-D7, LREQ after LCLK_PMC | 1394b                   | 50% to 50%, | See Figure 2      | 0   |     |     | ns   |

| t <sub>d</sub>  | Delay time,<br>PCLK to CTL0, CTL1, D1-D7, PINT       | 1394a-2000<br>and 1394b | 50% to 50%, | See Figure 3      | 0.5 | 7   |     | ns   |

TSB81BA3E SLLS783C – MAY 2009 – REVISED MARCH 2016

www.ti.com

## 8 Detailed Description

## 8.1 Overview

Data bits to be transmitted through the cable ports are received from the LLC on two-, four-, or eight-bit parallel paths (depending on the requested transmission speed and PHY-link interface mode of operation). They are latched internally, combined serially, encoded, and transmitted at 98.304, 196.608, 393.216, 491.52, or 983.04 Mbits/s (referred to as S100, S200, S400, S400B, or S800 speed, respectively) as the outbound information stream.

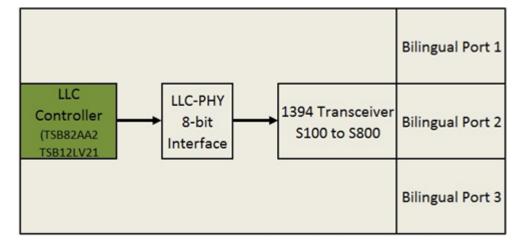

The PHY-link interface can follow either the IEEE 1394a-2000 protocol or the IEEE 1394b-2002 protocol. When using a 1394a-2000 LLC such as the TSB12LV26, the BMODE terminal must be deasserted. The PHY-link interface then operates in accordance with the legacy 1394a-2000 standard. When using a 1394b LLC such as the TSB82AA2, the BMODE terminal must be asserted. The PHY-link interface then conforms to the P1394b standard.

The cable interface can follow either the IEEE 1394a-2000 protocol or the 1394b protocol on all ports. The mode of operation is determined by the interface capabilities of the ports being connected. When any of the three ports is connected to a 1394a-2000 compliant device, the cable interface on that port operates in the 1394a-2000 data-strobe mode at a compatible S100, S200, or S400 speed. When a bilingual port is connected to a 1394b compliant node, the cable interface on that port operates per the P1394b standard at S400B or S800 speed. The TSB81BA3E automatically determines the correct cable interface connection method for the bilingual ports.

### NOTE

The BMODE terminal does not select the cable interface mode of operation. The BMODE terminal selects the PHY-link interface mode of operation and affects the arbitration modes on the cable. When the BMODE terminal is deasserted, BOSS arbitration is disabled.

During packet reception the serial data bits are split into two-, four-, or eight-bit parallel streams (depending upon the indicated receive speed and the PHY-link interface mode of operation), resynchronized to the local system clock and sent to the associated LLC. The received data is also transmitted (repeated) on the other connected and active cable ports.

During packet reception the serial data bits are split into two-, four-, or eight-bit parallel streams (depending upon the indicated receive speed and the PHY-link interface mode of operation), resynchronized to the local system clock and sent to the associated LLC. The received data is also transmitted (repeated) on the other connected and active cable ports.

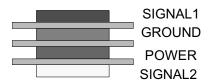

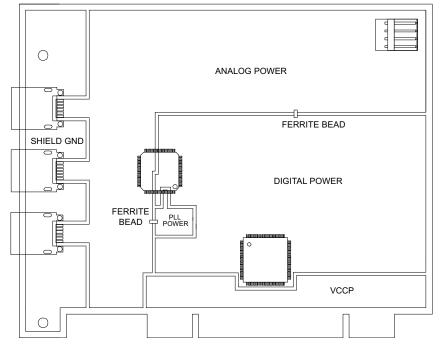

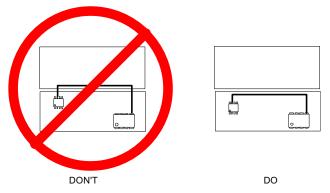

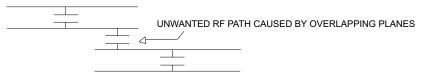

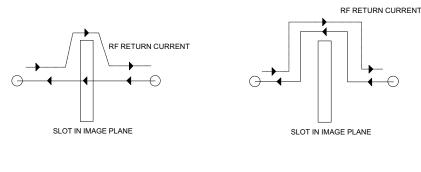

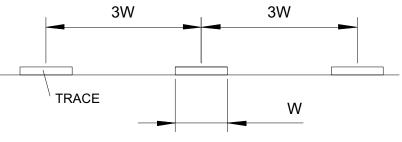

Both the twisted pair A (TPA) and the twisted pair B (TPB) cable interfaces incorporate differential comparators to monitor the line states during initialization and arbitration when connected to a 1394a-2000 compliant device. The outputs of these comparators are used by the internal logic to determine the arbitration status. The TPA channel monitors the incoming cable common-mode voltage. The value of this common-mode voltage is used during 1394a-mode arbitration and sets the speed of the next packet transmission. In addition, the TPB channel monitors the incoming cable common-mode voltage on the TPB pair for the presence of the remotely supplied twisted pair bias (TPBIAS) voltage.